CD4073B/CD4082B

CMOS AND Gate High-Voltage Types

Features

CD4073B and CD4082B AND Gates.provide the system ed Inner with

direct implementation of the AND function and supplement the

existing family of CMOS gates.

Medium-Speed Operation -TPLH, TPHL=60ns(tsp.)at VDD = 10 V

100% tested for quiescent current at 20V Maximum input current

SOP14

of 1μA at 18 V over full pack-temperature range,100 nA at 18 V and

25ºC

Noise margin (full package-temperature range)

1V at VDD=5V

2V at VDD=10V

TSSOP14

2.5V at VDD=15V

Standardized,symmetrical ou taut characteristics

5V、10Vand 15V parametric ratings

Meets all requirements of JEDEC Tentative Tankard

No.13B,Standard Specifications

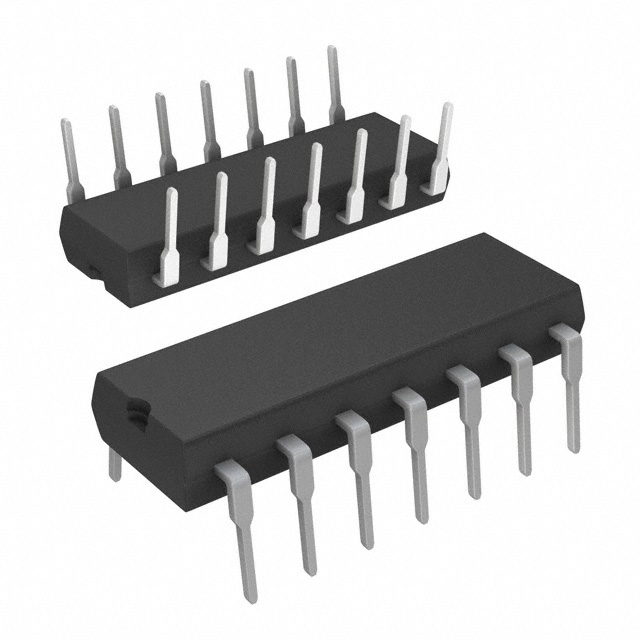

DIP14

Orderinginf Ormation

DEVICE

Package Type

MARKING

Packing

Packing Qty

CD4073BE

DIP14

CD4073BE

TUBE

1000pcs/box

CD4073BM/TR

SOP14

CD4073B

REEL

2500pcs/reel

TSSOP14

CD4073B

REEL

2500pcs/reel

CD4082BE

DIP14

CD4082BE

TUBE

1000pcs/box

CD4082BM/TR

SOP14

CD4082B

REEL

2500pcs/reel

TSSOP14

CD4082B

REEL

2500pcs/reel

CD4073BMT/TR

CD4082BMT/TR

http://www.hgsemi.com.cn

1 / 10

2019 DEC

�CD4073B/CD4082B

Logic Diagram

http://www.hgsemi.com.cn

2 / 10

2019 DEC

�CD4073B/CD4082B

*ALL INPUTS ARE PROTECTED BY

CMOS PROTECTION NETWORK

.

Fig.1 - Logic diagram for CD4073B(1 of 3 identical Gates).

Fig.2 - Logic diagram for CD4082B (1 of 2 identical gates).

http://www.hgsemi.com.cn

3 / 10

2019 DEC

�CD4073B/CD4082B

Pin Configuration

DIP/SOP/TSSOP

DIP/SOP/TSSOP

CB4073B

CB4082B

MAXIMUM RATINGS,Absolute-Maximum Values:

Condition

Min

Max

Units

Voltages reference to VSS Terminal)

-0.5

+20

V

INPUT VOLTAGE RANGE,ALLINPUTS

-0.5

+0.5

V

DC INPUT CURRENTANY ONE INPUT

-

+10

mA

-

500

mA

12

200

mW

-

100

mW

OPERATING-TEMPERATURE RANGE(TA)

-40

+85

℃

STORAGE TEMPERATURE RANGE(stag)

-65

+150

℃

-

+265

℃

DC SUPPLY-VOLTAGE RANGE,(VDD):

POWER DISSIPATION PER PACKAG-(PD):

For TA=55℃ to +100℃

For TA=+100℃ to +125℃ (Derate Lineaitry at)

DEVICE DISSIPATION PER OUTPUT TRANSISTOR:

FOR TA-FULL PACKAGE=TEMPERATURE RANGE(AI Pakage Types)

At distance 1/16±1/32inch(1.59+0.79mm)from case for 10s max

Recommendedoperatingconditions

For maximum reliability. nominal operating conditions should be selected so that operation is always

within the following ranges:

CHARACTERISTIC

MIN.

Supply-Voltage Range (for T=Full Package

LIMITS

5

Temperature Range)

UNITS

MAX.

15

V

DYNAIC ELECTRICAL CHARACTETISTICS

at TA=25ºC,Input tr,ft=20ns,and CL=50 pf,RL=200KΩ

CHARACTERISTIC

TEST CONDITIOS

VDD Volts

5

10

15

5

10

15

-

Propagation Delay Time,TPHL,TPLH

Transition Time, TPHL,TPLH

Input Capacitance,CIN

http://www.hgsemi.com.cn

Any Input

4 / 10

ALL TYPES LIMITS

TYP.

MAX.

125

60

40

100

50

40

5

250

120

90

200

100

80

7.5

UNITS

NS

NS

Pf

2019 DEC

�CD4073B/CD4082B

STATIC ELECTRICAL CHARACTERISTICS

CHARACTER.

ISTIC

CONDITIONS

VO

(V)

Quiescent Device

Current,IDD Max.

Output Low

(Sink)Current IOL Min.

Output High (Source)

Current,

IOH Min.

VIN

(V)

LIMITS AT INDICATED TEMPERATURES(℃)

UNITS

+25

VDD

(V)

-40

+85

Min

TYP

MAX

-

0.5

5

0.25

7.5

-

0.01

0.25

-

0.10

10

0.5

15

-

0.01

0.5

-

0.15

15

1

30

-

0.01

1

-

0.20

20

5

150

-

0.02

5

0.4

0.5

5

0.61

0.42

0.51

1

-

0.5

0.10

10

1.5

1.1

1.3

2.6

-

1.5

0.15

15

4

2.8

3.4

6.8

-

4.6

0.5

5

-0.61

-0.42

-0.51

-1

-

2.5

0.5

5

-1.8

-1.3

-1.6

-3.2

-

9.5

0.10

10

-1.5

-1.1

-1.3

-2.6

-

13.5

0.15

10

-4

-2.8

-3.4

-6.8

-

Output Voltage

Low-Level,

VOL Max.

-

0.5

5

0.05

-

0

0.05

-

0.10

10

0.05

-

0

0.05

-

0.15

15

0.05

-

0

0.05

Output Voltage

High-Level,

VOH Min.

-

0.5

5

1.95

4.95

5

-

-

0.10

10

9.95

9.95

10

-

-

0.15

15

14.95

14.95

15

-

0.5

-

5

1.5

-

-

1.5

1

-

10

3

-

-

3

1.5

-

15

4

-

-

4

0.5.4.5

-

5

3.5

3.5

-

-

1.9

-

10

7

7

-

-

1.5.13.5

-

15

11

11

-

-

0.18

18

-

±10-5

±0.1

Input Low Voltage,

VIL Max.

Input High Voltage,

VIH Min.

Input Current

VIN Max.

http://www.hgsemi.com.cn

±0.1

5 / 10

±1

µA

mA

V

V

µA

2019 DEC

�CD4073B/CD4082B

INPUT VOLTAGE(VIN)-V

LOAD CAPACITANCE(CL)--pf

Fig.3-Typocalvoltagetransfercharacteristic.

Fig.4 - Typical propagation delay time as a

function of load capacitance.

DRAIN-TO-SOURCE VOKTAGE(VDS)-V

DRAIN-TO-SOURCE VOLTAGE(VDS)-V

Fig.5 - Typical output low (sink)

Fig.6 - Minimum output low (sink)

Current characteristics.

Current characteristics.

Fig.7 -Minimum output high (source)current

Fig.8 - Typical

characteristics

http://www.hgsemi.com.cn

output high (source)

D

current

characteristics.

6 / 10

2019 DEC

�CD4073B/CD4082B

Fig.9 -Typical transition time as a function of

Fig.10 -Typical dynamic power diss i- Ration

load capacitance

per gate as a function

TERMINAL ASSIGNMENTS

Fig.12 - Input

Fig.11 - Quiescent device current test circuit.

current test circuit.

Fig.13 - Input-voltage test circuit.

http://www.hgsemi.com.cn

7 / 10

2019 DEC

�CD4073B/CD4082B

Physical Dimensions

DIP14

B

L1

L

E

D1

D

d

A

c

a

Dimensions In Millimeters(DIP14)

A

B

D

D1

E

L

L1

a

c

Min:

6.10

18.94

8.40

7.42

3.10

0.50

3.00

1.50

0.40

Max:

6.68

19.56

9.00

7.82

3.55

0.70

3.60

1.55

0.50

Symbol:

d

2.54 BSC

SOP14

Q

A

C

C1

B

D

A1

a

0.25

b

Dimensions In Millimeters(SOP14)

A

A1

B

C

C1

D

Min:

1.35

0.05

8.55

5.80

3.80

0.40

0°

0.35

Max:

1.55

0.20

8.75

6.20

4.00

0.80

8°

0.45

Symbol:

http://www.hgsemi.com.cn

8 / 10

Q

a

b

1.27 BSC

2019 DEC

�CD4073B/CD4082B

Physical Dimensions

TSSOP14

Dimensions In Millimeters(TSSOP14)

A

A1

B

C

C1

D

Min:

0.85

0.05

4.90

6.20

4.30

0.40

0°

0.20

Max:

0.95

0.20

5.10

6.60

4.50

0.80

8°

0.25

Symbol:

http://www.hgsemi.com.cn

9 / 10

Q

a

b

0.65 BSC

2019 DEC

�CD4073B/CD4082B

IMPORTANT STATEMENT:

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant

information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the

altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design

and machine manufacturing. You will bear all the following responsibilities: select the appropriate Huaguan Semiconductor products for your application; Design,

validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the

occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor

will not bear the consequences caused by the application of products in these fields.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network

tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed

to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance

scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this

document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly

forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages,

costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.

http://www.hgsemi.com.cn

10 / 10

2019 DEC

�