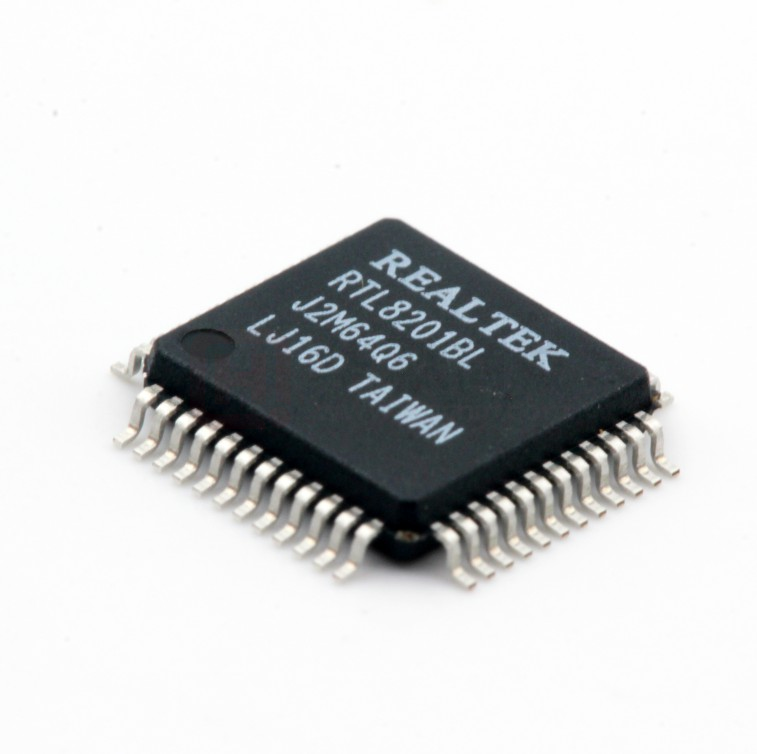

RTL8201BL

RTL8201BL-LF

SINGLE CHIP SINGLE PORT 10/100M FAST

ETHERNET PHYCEIVER

DATASHEET

Rev. 1.3

26 July 2005

Track ID: JATR-1076-21

�RTL8201BL

Datasheet

COPYRIGHT

©2005 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced,

transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any

means without the written permission of Realtek Semiconductor Corp.

DISCLAIMER

Realtek provides this document “as is”, without warranty of any kind, neither expressed nor implied,

including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in

this document or in the product described in this document at any time. This document could include

technical inaccuracies or typographical errors.

TRADEMARKS

Realtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document

are trademarks/registered trademarks of their respective owners.

USING THIS DOCUMENT

This document is intended for the hardware and software engineer’s general information on the Realtek

RTL8201BL chip.

Though every effort has been made to ensure that this document is current and accurate, more

information may have become available subsequent to the production of this guide. In that event, please

contact your Realtek representative for additional information that may help in the development process.

REVISION HISTORY

Revision

1.1

Release Date

2002/02/01

1.2

2002/03/29

Summary

Power Dissipation: Remove 2.5V power consumption

100Mbps Network Interface: R5 is changed from 5.6K to 5.9K

Reset, and Transmit Bias(RTSET): R5 is changed from 5.6K to 5.9K

Schematic Layout: R5 is changed from 5.6K to 5.9K

Reset and other pins: Add pin description for pin 32 and pin 8

Power and Ground pins: Remove pin description of pin 32 and pin 8

3.3V power supply and voltage conversion circuit: Add description:

“Strongly emphasize here, could not provide external 2.5V produced by

any other power device for PWFBOUT and PWFBIN”.

Schematic Layout:

1. Modify net label: Pin32: AVDD25 -> PWFBOUT

Pin8: DVDD25-> PWFBIN

1.3

2005/07/26

2. Add pull-high resistor for MDIO

3. Modify ResetB circuit to meet wake-on-LAN application

Cosmetic layout changes

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

ii

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

Table of Contents

1.

INTRODUCTION ...............................................................................................................................1

2.

SYSTEM APPLICATIONS................................................................................................................1

3.

FEATURES ..........................................................................................................................................2

4.

BLOCK DIAGRAM............................................................................................................................3

5.

PIN ASSIGNMENTS ..........................................................................................................................4

5.1.

6.

PIN DESCRIPTION............................................................................................................................5

6.1.

6.2.

6.3.

6.4.

6.5.

6.6.

6.7.

6.8.

7.

100MBPS MII & PCS INTERFACE ..................................................................................................5

SNI (SERIAL NETWORK INTERFACE): 10MBPS ONLY .....................................................................5

CLOCK INTERFACE .........................................................................................................................6

100MBPS NETWORK INTERFACE ....................................................................................................6

DEVICE CONFIGURATION INTERFACE.............................................................................................6

LED INTERFACE/PHY ADDRESS CONFIG ......................................................................................7

RESET AND OTHER PINS .................................................................................................................7

POWER AND GROUND PINS ............................................................................................................7

REGISTER DESCRIPTIONS............................................................................................................8

7.1.

7.2.

7.3.

7.4.

7.5.

7.6.

7.7.

7.8.

7.9.

7.10.

7.11.

7.12.

7.13.

7.14.

7.15.

7.16.

7.17.

8.

LEAD (PB)-FREE PACKAGE AND VERSION IDENTIFICATION ...........................................................4

REGISTER 0 BASIC MODE CONTROL REGISTER ..............................................................................8

REGISTER 1 BASIC MODE STATUS REGISTER .................................................................................9

REGISTER 2 PHY IDENTIFIER REGISTER 1......................................................................................9

REGISTER 3 PHY IDENTIFIER REGISTER 2......................................................................................9

REGISTER 4 AUTO-NEGOTIATION ADVERTISEMENT REGISTER(ANAR).......................................10

REGISTER 5 AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER(ANLPAR).......................10

REGISTER 6 AUTO-NEGOTIATION EXPANSION REGISTER(ANER)................................................11

REGISTER 16 NWAY SETUP REGISTER(NSR) ...............................................................................11

REGISTER 17 LOOPBACK, BYPASS, RECEIVER ERROR MASK REGISTER(LBREMR)....................12

REGISTER 18 RX_ER COUNTER(REC) ........................................................................................12

REGISTER19 10MBPS NETWORK INTERFACE CONFIGURATIONREGISTER ......................................................12

REGISTER 20 PHY 1_1 REGISTER ................................................................................................13

REGISTER 21 PHY 1_2 REGISTER ................................................................................................13

REGISTER 22 PHY 2 REGISTER ....................................................................................................13

REGISTER 23 TWISTER_1 REGISTER .............................................................................................13

REGISTER 24 TWISTER_2 REGISTER .............................................................................................13

REGISTER 25 TEST REGISTER .......................................................................................................13

FUNCTIONAL DESCRIPTION......................................................................................................14

8.1.

MII AND MANAGEMENT INTERFACE ............................................................................................14

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

iii

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.1.1.

Data Transition ....................................................................................................................14

8.1.2.

Serial Management...............................................................................................................15

8.2.

AUTO-NEGOTIATION AND PARALLEL DETECTION ........................................................................15

8.3.

FLOW CONTROL SUPPORT ............................................................................................................17

8.4.

HARDWARE CONFIGURATION AND AUTO-NEGOTIATION..............................................................17

8.5.

LED AND PHY ADDRESS CONFIGURATION .................................................................................18

8.6.

SERIAL NETWORK INTERFACE .....................................................................................................18

8.7.

POWER DOWN, LINK DOWN, POWER SAVING, ANDISOLATIONMODES..........................................................19

8.8.

MEDIA INTERFACE .......................................................................................................................19

8.8.1.

100Base-TX ..........................................................................................................................19

8.8.2.

100Base-FX Fiber Mode Operation.....................................................................................20

8.8.3.

10Base-Tx/Rx........................................................................................................................20

8.9.

REPEATER MODE OPERATION ......................................................................................................20

8.10. RESET, AND TRANSMIT BIAS (RTSET) ........................................................................................20

8.11. 3.3V POWER SUPPLY AND VOLTAGE CONVERSION CIRCUIT ........................................................21

8.12. FAR END FAULT INDICATION .......................................................................................................21

9.

ELECTRICAL CHARACTERISTICS ...........................................................................................22

9.1.

D.C. CHARACTERISTICS ...............................................................................................................22

9.1.1.

Absolute Maximum Ratings..................................................................................................22

9.1.2.

Operating Conditions ...........................................................................................................22

9.1.3.

Power Dissipation ................................................................................................................22

9.1.4.

Supply Voltage: Vcc .............................................................................................................22

9.2.

A.C. CHARACTERISTICS ...............................................................................................................23

9.2.1.

MII Timing of Transmission Cycle.......................................................................................23

9.2.2.

MII Timing of Reception Cycle ............................................................................................24

9.2.3.

SNI Timing of Transmission Cycle.......................................................................................26

9.2.4.

SNI Timing of Reception Cycle ............................................................................................27

9.2.5.

MDC/MDIO timing ..............................................................................................................28

9.2.6.

Transmission Without Collision ...........................................................................................28

9.2.7.

Reception Without Error ......................................................................................................29

9.3.

CRYSTAL AND TRANSFORMER SPECIFICATIONS ...........................................................................30

9.3.1.

Crystal Specifications...........................................................................................................30

9.3.2.

Transformer Specifications ..................................................................................................30

10.

MECHANICAL DIMENSIONS ..................................................................................................31

11.

ORDERING INFORMATION.....................................................................................................32

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

iv

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

1.

Introduction

The RTL8201BL is a single-port Phyceiver with an MII (Media Independent

Interface)/SNI(Serial Network Interface). It implements all 10/100M Ethernet

Physical-layer functions including the Physical Coding Sublayer (PCS), Physical Medium

Attachment (PMA), Twisted Pair Physical Medium Dependent Sublayer (TP-PMD),

10Base-Tx Encoder/Decoder and Twisted Pair Media Access Unit (TPMAU).

A PECL interface is supported to connect with an external 100Base-FX fiber optical

transceiver. The chip is fabricated with an advanced CMOS process to meet low voltage

and low power requirements.

The RTL8201BL can be used in a NIC, MAU, CNR, ACR, Ethernet Hub, or Ethernet

Switch. Additionally, it can be used in any embedded system with an Ethernet MAC that

needs a twisted pair physical connection or fiber PECL interface to an external

100Base-FX optical transceiver module.

2.

System Applications

LOC (LAN on Chipset)

NIC (Network Interface Card)

MAU (Media Attachment Unit)

CNR (Communication and Networking Riser)

ACR (Advanced Communication Riser)

Ethernet Hub, Ethernet Switch

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

1

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

3.

Features

The Realtek RTL8201BL is a Fast Ethernet Phyceiver with selectable MII or SNI interface

to the MAC chip. It provides the following features:

Supports MII/7-wire SNI (Serial

Network Interface) interface

Supports 10/100Mbps operation

Supports half/full duplex operation

Support of twisted pair or Fiber mode

output

Speed/duplex/auto negotiation

adjustable

3.3V operation with 5V IO signal

tolerance

Low operation power consumption and

only need single supply 3.3V

IEEE 802.3/802.3u compliant

Adaptive Equalization

Supports IEEE 802.3u clause 28 auto

25MHz crystal/oscillator as clock

negotiation

source

Supports power down mode

Multiple network status LED support

Supports operation under Link Down

Flow control ability support to co-work

Power Saving mode

Supports Base Line Wander (BLW)

with MAC (by MDC/MDIO)

48 pin LQFP package

compensation

Supports repeater mode

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

2

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

4.

Block Diagram

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

3

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

5.

Pin Assignments

5.1. Lead (Pb)-Free Package and Version Identification

Lead (Pb)-free package is indicated by an ‘L’ in the location marked ‘T’ in the figure above.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

4

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

6.

Pin Description

LI: Latched Input in power up or reset

I: Input

P: Power

I/O: Bi-directional input and output

O: Output

6.1. 100Mbps MII & PCS Interface

Symbol

Type

Pin No.

Description

TXC

O

7

TXEN

I

2

TXD[3:0]

I

3, 4, 5, 6

RXC

O

16

COL

CRS

RXDV

O

O

O

1

23

22

RXD[3:0]

O

18, 19, 20, 21

O/LI

24

Transmit Clock: This pin provides a continuous clock as a timing reference

for TXD[3:0] and TXEN.

Transmit Enable: The input signal indicates the presence of a valid nibble

data on TXD[3:0].

Transmit Data: MAC will source TXD[0..3] synchronous with TXC when

TXEN is asserted.

Receive Clock: This pin provides a continuous clock reference for RXDV

and RXD[0..3] signals. RXC is 25MHz in the 100Mbps mode and 2.5Mhz in

the 10Mbps mode.

Collision Detected: COL is asserted high when a collision is detected on the media.

Carrier Sense: This pin’s signal is asserted high if the media is not in IDEL state.

Receive Data Valid: This pin’s signal is asserted high when received data is

present on the RXD[3:0] lines; the signal is deasserted at the end of the

packet. The signal is valid on the rising of the RXC.

Receive Data: These are the four parallel receive data lines aligned on the

nibble boundaries driven synchronously to the RXC for reception by the

external physical unit (PHY).

Receive error: if any 5B decode error occurs, such as invalid J/K, T/R,

invalid symbol, this pin will go high.

Fiber/UTP Enable: During power on reset, this pin status is latched to

determine at which media mode to operate:

1: Fiber mode

0: UTP mode

An internal weak pull low resistor, sets this to the default of UTP mode. It is

possible to use an external 5.1KΩ pull high resistor to enable fiber mode.

After power on, the pin operates as the Receive Error pin.

Management Data Clock: This pin provides a clock synchronous to MDIO,

which may be asynchronous to the transmit TXC and receive RXC clocks.

The clock rate can be up to 2.5MHz.

Management Data Input/Output: This pin provides the bi-directional

signal used to transfer management information.

RXER/

FXEN

MDC

I

MDIO

I/O

25

26

6.2. SNI (Serial Network Interface): 10Mbps only

Symbol

COL

RXD0

CRS

RXC

TXD0

TXC

TXEN

Type

Pin No.

O

O

O

O

I

O

I

1

21

23

16

6

7

2

Description

Collision Detect

Received Serial Data

Carrier Sense

Receive Clock: Resolved from received data

Transmit Serial Data

Transmit Clock: Generate by PHY

Transmit Enable: For MAC to indicate transmit operation

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

5

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

6.3. Clock Interface

Symbol

X2

X1

Type

O

Pin No.

47

I

46

Description

25MHz Crystal Output: This pin provides the 25MHz crystal output. It

must be left open when X1 is driven with an external 25MHz oscillator.

25MHz Crystal Input: This pin provides the 25MHz crystal input. If a

25MHz oscillator is used, connect X1 to the oscillator’s output. Refer to

section 8.3 to obtain clock source specifications.

6.4. 100Mbps Network Interface

Symbol

Type

Pin No.

Description

TPTX+

TPTX-

O

O

34

33

RTSET

I

28

TPRX+

TPRX-

I

I

31

30

Transmit Output: Differential pair shared by 100Base-TX, 100Base-FX and

10Base-T modes. When configured as 100Base-TX, output is an MLT-3

encoded waveform. When configured as 100Base-FX, the output is

pseudo-ECL level.

Transmit Bias Resistor Connection: This pin should be pulled to GND by

a 5.9KΩ (1%) resistor to define driving current for transmit DAC. The

resistance value may be changed, depending on experimental results of the

RTL8201BL.

Receive Input: Differential pair shared by 100Base-TX, 100Base-FX, and

10Base-T modes.

6.5. Device Configuration Interface

Symbol

ISOLATE

Type

I

Pin No.

43

RPTR

I

40

SPEED

LI

39

DUPLEX

LI

38

ANE

LI

37

LDPS

I

41

LI/O

44

MII/SNIB/

RTT3(test)

Description

Set high to isolate the RTL8201BL from the MAC. This will also isolate the

MDC/MDIO management interface. In this mode, the power consumption is

minimum. This pin can be directly connected to GND or VCC.

Set high to put the RTL8201BL into repeater mode. This pin can be directly

connected to GND or VCC.

This pin is latched to input during a power on or reset condition. Set high to

put the RTL8201BL into 100Mbps operation. This pin can be directly connected

to GND or VCC.

This pin is latched to input during a power on or reset condition. Set high to

enable full duplex. This pin can be directly connected to GND or VCC.

This pin is latched to input during a power on or reset condition. Set high to

enable Auto-negotiation mode, set low to force mode. This pin can be directly

connected to GND or VCC.

Set high to put the RTL8201BL into LDPS mode. This pin can be directly

connected to GND or VCC. Refer to Section 7.7 for more information.

This pin is latched to input during a power on or reset condition. Pull high to

set the RTL8201BL into MII mode operation. Set low for SNI mode. This pin

can be directly connected to GND or VCC. In test mode, this pin is an output pin and

redefined as RTT3

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

6

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

6.6. LED Interface/PHY Address Config

These five pins are latched into the RTL8201BL during power up reset to configure PHY address [0:4] used for MII

management register interface. And then, in normal operation after initial reset, they are used as driving pins for status

indication LED. The driving polarity, active low or active high, is determined by each latched status of the PHY address [4:0]

during power-up reset. If latched status is High then it will be active low, and if latched status is Low then it will be active high.

Refer to Section 7.5 for more information.

Symbol

PHYAD0/

LED0

PAD1/

LED1

PHYAD2/

LED2

Type

LI/O

Pin No.

9

LI/O

10

LI/O

12

PHYAD3/

LED3

LI/O

13

PHYAD4/

LED4

LI/O

15

Description

PHY Address [0]

Link LED: Active when linked.

PHY Address [1]

Full Duplex LED: Active when in Full Duplex operation.

PHY Address [2]

Link 10/ACT LED: Active when linked in 10Base-T mode, and blinking

when transmitting or receiving data.

PHY Address [3]

Link 100/ACT LED: Active when linked in 100Base-TX and blinking

when transmitting or receiving data.

PHY Address [4]

Collision LED: Active when collisions occur.

6.7. Reset and Other Pins

Symbol

RESETB

Type

I

Pin No.

42

PWFBOUT

O

32

PWFBIN

NC

I

8

27

Description

Set

low

to

reset

the

chip.

For a complete reset function, this pin

RESETB:

must be asserted low for at least 10ms.

Power Feedback Output: Be sure to connect a 22uF tantalum capacitor for

frequency compensation and a 0.1uF capacitor for noise de-coupling. Then

connect this pin through a ferrite bead to PWFBIN(pin8). The connection

method is figured in section 7.11.

Power Feedback Input: see the description of PWFBOUT.

Not connection

6.8. Power and Ground Pins

Symbol

AVDD33

Type

P

Pin No.

36

AGND

DVDD33

DGND

P

P

P

29,35

14,48

11,17,45

Description

3.3V Analog power input: 3.3V power supply for analog circuit; should be

well decoupled.

Analog Ground: Should be connected to a larger GND plane

3.3V Digital Power input: 3.3V power supply for digital circuit.

Digital Ground: Should be connected to a larger GND plane.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

7

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

7.

Register Descriptions

This section will describe definitions and usage for each of the registers available in the RTL8201BL.

7.1. Register 0 Basic Mode Control Register

Address

0:

Name

Reset

0:

Loopback

0:

Spd_Set

0:

Auto

Negotiation

Enable

0:

Power Down

0:

0:

Reserved

Restart Auto

Negotiation

0:

Duplex Mode

0:

Reserved

Description/Usage

This bit sets the status and control registers of the

PHY in a default state. This bit is self-clearing.

1 = software reset

0 = normal operation

This bit enables loopback of transmit data nibbles

TXD to the receive data path.

1 = enable loopback

0 = normal operation

This bit sets the network speed.

1 = 100Mbps

0 = 10Mbps

When 100Base-FX mode is enabled, this bit=1 and is

read only.

This bit enables/disables the Nway auto-negotiation

function.

1 = enable auto-negotiation; bits 0: and 0:

will be ignored.

0 = disable auto-negotiation; bits 0: and 0:

will determine the link speed and the data transfer

mode, respectively.

When 100Base-FX mode is enabled, this bit=0 and is

read only.

This bit turns down the power of the PHY chip

including internal crystal oscillator circuit. The MDC,

MDIO is still alive for accessing the MAC.

1 = power down

0 = normal operation

Default/Attribute

0, RW

This bits allows the Nway auto-negotiation function

to be reset.

1 = re-start auto-negotiation

0 = normal operation

This bit sets the duplex mode if auto negotiation is

disabled (bit 0:=0)

1 = full duplex

0 = half duplex

After completing auto negotiation, this bit will reflect

the duplex status.(1: Full duplex, 0: Half duplex)

When 100Base-FX mode is enabled, this bit can be

set through the MDC/MDIO SMI interface or

DUPLEX pin.

0, RW

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

8

0, RW

1, RW

1, RW

0, RW

1, RW

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

7.2. Register 1 Basic Mode Status Register

Address

1:

1:

1:

1:

1:

1:

1:

1:

1:

1:

1:

1:

1:

Name

100Base-T4

Description/Usage

1 = enable 100Base-T4 support

0 = suppress 100Base-T4 support

100Base_TX_ 1 = enable 100Base-TX full duplex support

FD

0 = suppress 100Base-TX full duplex support

100BASE_TX_ 1 = enable 100Base-TX half duplex support

HD

0 = suppress 100Base-TX half duplex support

10Base_T_FD 1 = enable 10Base-T full duplex support

0 = suppress 10Base-T full duplex support

10_Base_T_HD 1 = enable 10Base-T half duplex support

0 = suppress 10Base-T half duplex support

Reserved

MF Preamble The RTL8201BL will accept management frames

Suppression

with preamble suppressed. The RTL8201BL accepts

management frames without preamble. A Minimum

of 32 preamble bits are required for the first SMI

read/write transaction after reset. One idle bit is

required between any two management transactions

as per IEEE802.3u specifications

Auto

1 = auto-negotiation process completed

Negotiation

0 = auto-negotiation process not completed

Complete

Remote Fault 1 = remote fault condition detected (cleared on read)

0 = no remote fault condition detected

When in 100Base-FX mode, this bit means an

in-band signal Far-End-Fault is detected. Refer to

Section 7.11.

Auto

1 = Link had not been experienced fail state

Negotiation

0 = Link had been experienced fail state

Link Status

1 = valid link established

0 = no valid link established

Jabber Detect 1 = jabber condition detected

0 = no jabber condition detected

Extended

1 = extended register capability

Capability

0 = basic register capability only

Default/Attribute

0, RO

1, RO

1, RO

1, RO

1, RO

1, RO

0, RO

0, RO

1, RO

0, RO

0, RO

1, RO

7.3. Register 2 PHY Identifier Register 1

Address

2:

Name

PHYID1

PHY identifier

RTL8201BL

Description/Usage

ID for software

recognize

Default/Attribute

0000, RO

7.4. Register 3 PHY Identifier Register 2

Address

3:

Name

PHYID2

Description/Usage

PHY identifier ID for software recognize RTL8201

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

9

Default/Attribute

8201, RO

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

7.5. Register 4 Auto-negotiation Advertisement Register(ANAR)

This register contains the advertised abilities of this device as they will be transmitted to its link partner during

Auto-negotiation.

Address

4:

Name

NP

4:

ACK

4:

RF

4:

4:

Reserved

Pause

4:

T4

4:

TXFD

4:

TX

4:

10FD

4:

10

4:

Selector

Description/Usage

Next Page bit.

0 = transmitting the primary capability data page

1 = transmitting the protocol specific data page

1 = acknowledge reception of link partner capability

data word

0 = do not acknowledge reception

1 = advertise remote fault detection capability

0 = do not advertise remote fault detection capability

Default/Attribute

0, RO

1 = flow control is supported by local node

0 = flow control is NOT supported by local node

1 = 100Base-T4 is supported by local node

0 = 100Base-T4 not supported by local node

1 = 100Base-TX full duplex is supported by local node

0 = 100Base-TX full duplex not supported by local node

1 = 100Base-TX is supported by local node

0 = 100Base-TX not supported by local node

1 = 10Base-T full duplex supported by local node

0 = 10Base-T full duplex not supported by local node

1 = 10Base-T is supported by local node

0 = 10Base-T not supported by local node

Binary encoded selector supported by this node.

Currently only CSMA/CD is specified. No

other protocols are supported.

0, RW

0, RO

0, RW

0, RO

1, RW

1, RW

1, RW

1, RW

, RW

7.6. Register 5 Auto-Negotiation Link Partner Ability

Register(ANLPAR)

This register contains the advertised abilities of the Link Partner as received during Auto-negotiation. The content changes

after the successful Auto-negotiation if Next-pages are supported.

Address

5:

Name

NP

5:

ACK

5:

RF

5:

5:

Reserved

Pause

5:

T4

5:

TXFD

Description/Usage

Next Page bit.

0 = transmitting the primary capability data page

1 = transmitting the protocol specific data page

1 = link partner acknowledges reception of local

node’s capability data word

0 = no acknowledgement

1 = link partner is indicating a remote fault

0 = link partner does not indicate a remote fault

Default/Attribute

0, RO

1 = flow control is supported by Link partner

0 = flow control is NOT supported by Link partner

1 = 100Base-T4 is supported by link partner

0 = 100Base-T4 not supported by link partner

1 = 100Base-TX full duplex is supported by link partner

0 = 100Base-TX full duplex not supported by link partner

0, RO

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

10

0, RO

0, RO

0, RO

0, RO

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

5:

100BASE-TX

5:

10FD

5:

10Base-T

5:

Selector

1 = 100Base-TX is supported by link partner

0 = 100Base-TX not supported by link partner

This bit will also be set after the link in 100Base is

established by parallel detection.

1 = 10Base-T full duplex is supported by link partner

0 = 10Base-T full duplex not supported by link partner

1 = 10Base-T is supported by link partner

0 = 10Base-T not supported by link partner

This bit will also be set after the link in 10Base is

established by parallel detection.

Link Partner’s binary encoded node selector

Currently only CSMA/CD is specified

1, RO

0, RO

0, RO

, RO

7.7. Register 6 Auto-negotiation Expansion Register(ANER)

This register contains additional status for NWay auto-negotiation.

Address

6:

6:

6:

6:

6:

6:

Name

Reserved

MLF

Description/Usage

This bit is always set to 0.

Status indicating if a multiple link fault has occurred.

1 = fault occurred

0 = no fault occurred

LP_NP_ABLE Status indicating if the link partner supports Next

Page negotiation.

1 = supported

0 = not supported

NP_ABLE

This bit indicates if the local node is able to send

additional Next Pages.

PAGE_RX

This bit is set when a new Link Code Word Page has

been received. It is automatically cleared when the

auto-negotiation link partner’s ability register

(register 5) is read by management.

LP_NW_ABLE 1 = link partner supports Nway auto-negotiation.

Default/Attribute

0, RO

0, RO

0, RO

0, RO

0, RO

7.8. Register 16 Nway Setup Register(NSR)

Address

16:

16:

16:

16:

16:

16:

16:

16:

Name

Reserved

ENNWLE

Testfun

NWLPBK

Reserved

FLAGABD

FLAGPDF

FLAGLSC

Description/Usage

Default/Attribute

1 = LED4 Pin indicates linkpulse

1 = Auto-neg speeds up internal timer

1 = set Nway to loopback mode.

0, RW

0, RW

0, RW

1 = Auto-neg experienced ability detect state

1 = Auto-neg experienced parallel detection fault state

1 = Auto-neg experienced link status check state

0, RO

0, RO

0, RO

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

11

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

7.9. Register 17 Loopback, Bypass, Receiver Error Mask

Register(LBREMR)

Address

17:

17:

Name

RPTR

BP_4B5B

17:

BP_SCR

17:

17:

LDPS

AnalogOFF

17:

DetectLength

17:

LB

17:

F_Link_100

17:

17:

Reserved

CODE_err

17:

PME_err

17:

LINK_err

17:

PKT_err

17:

RWPara

Description/Usage

Set to 1 to put the RTL8201BL into repeater mode

Assertion of this bit allows bypassing of the 4B/5B &

5B/4B encoder.

Assertion of this bit allows bypassing of the

scrambler/descrambler.

Set to 1 to enable Link Down Power Saving mode

Set to 1 to power down analog function of transmitter

and receiver.

Detect length OK indication. Assert low to indicate

detect length OK.

LB are register bits for loopback control as

defined below:

1) 0 0 for normal mode;

2) 0 1 for PHY loopback;

3) 1 0 for twister loopback

Used to logic force good link in 100Mbps for

diagnostic purposes.

Default/Attribute

0, RW

0, RW

Assertion of this bit causes a code error detection to

be reported.

Assertion of this bit causes a pre-mature end error

detection to be reported.

Assertion of this bit causes a link error detection to be

reported.

Assertion of this bit causes a detection of packet

errors due to 722 ms time-out to be reported.

Parameter access enable, set 1 to access register

20~24

0, RW

0, RW

0, RW

0, RW

0, RO

, RW

1, RW

0, RW

0, RW

0, RW

0, RW

7.10. Register 18 RX_ER Counter(REC)

Address

18:

Name

RXERCNT

Description/Usage

This 16-bit counter increments by 1 for each valid

packet received.

Default/Attribute

H’[0000],

RW

7.11. Register 19 10Mbps Network Interface Configuration Register

Address

19:

19:

Name

Reserved

LD

19:

19:

19:

Reserved

HBEN

JBEN

Description/Usage

Default/Attribute

This bit is the active low TPI link disable signal.

When low TPIstilltransmit link pulses and TPI stays

in good link state.

1, RW

Heart beat enable

1 = enable jabber function

0 = disable jabber function

1, RW

1, RW

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

12

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

7.12. Register 20 PHY 1_1 Register

Address

20:

Name

PHY1_1

Description/Usage

PHY 1 register (functions as RTL8139C)

Default/Attribute

R/W

7.13. Register 21 PHY 1_2 Register

Address

21:

Name

PHY1_2

Description/Usage

PHY 1 register (functions as RTL8139C)

Default/Attribute

R/W

7.14. Register 22 PHY 2 Register

Address

22

Name

PHY2_76

22:

PHY2_80

Description/Usage

PHY2 register for cable length test (functions as

RTL8139C)

PHY2 register for PLL select (functions as

RTL8139C)

Default/Attribute

RO

R/W

7.15. Register 23 Twister_1 Register

Address

23:

Name

TW_1

Description/Usage

Twister register (functions as RTL8139C)

Default/Attribute

R/W

7.16. Register 24 Twister_2 Register

Address

24:

Name

TW_2

Description/Usage

Twister register (functions as RTL8139C)

Default/Attribute

R/W

7.17. Register 25 Test Register

Address

25

25

25:

Name

Test

Reserved

PHYAD[4:0]

25

25

Test

LINK10

25

LINK100

Description/Usage

Reserved for internal testing

Default/ Attribute

R/W

Reflects the PHY address defined by external PHY

address configuration pins

Reserved for internal testing

1: Link established in 10Base OK

0: No link established in 10Base

1: Link established in 100Base OK

0: No link established in 100Base

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

13

RO

RO

RO

RO

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.

Functional Description

The RTL8201BL Phyceiver is a physical layer device that integrates 10Base-T and 100Base-TX functions and some extra

power manage features into a 48 pin single chip which is used in 10/100 Fast Ethernet applications. This device supports the

following functions:

z

z

z

z

z

z

z

z

z

z

z

z

z

z

MII interface with MDC/MDIO SMI management interface to communicate with MAC

IEEE 802.3u clause 28 Auto-Negotiation ability

Flow control ability support to cooperate with MAC

Speed, duplex, auto-negotiation ability configurable by hard wire or MDC/MDIO.

Flexible LED configuration.

7-wire SNI(Serial Network Interface) support, works only on 10Mbps mode.

Power Down mode support

4B/5B transform

Scrambling/De-scrambling

NRZ to NRZI, NRZI to MLT3

Manchester Encode and Decode for 10 BaseT operation

Clock and Data recovery

Adaptive Equalization

Far End Fault Indication (FEFI) in fiber mode

8.1. MII and Management Interface

8.1.1.

Data Transition

To set the RTL8201BL for MII mode operation, pull MII/SNIB pin high and properly set the ANE, SPEED, and DUPLEX pins.

The MII (Media Independent Interface) is an 18-signal interface which is described in IEEE 802.3u supplying a standard

interface between PHY and MAC layer. This interface operates in two frequencies – 25Mhz and 2.5Mhz to support

100Mbps/10Mbps bandwidth for both the transmit and receive function. While transmitting packets, the MAC will first assert

the TXEN signal and change byte data into 4 bits nibble and pass to the PHY by TXD[0..3]. PHY will sample TXD[0..]

synchronously with TXC — the transmit clock signal supplied by PHY – during the interval TXEN is asserted. While

receiving a packet, the PHY will assert the RXEN signal, pass the received nibble data RXD[0..3] clocked by RXC, which is

recovered from the received data. CRS and COL signals are used for collision detection and handling.

In 100Base-TX mode, when decoded signal in 5B is not IDLE, the CRS signal will assert and when 5B is recognized as IDLE

it will be de-asserted. In 10Base-T mode, CRS will assert when the 10M preamble been confirmed and will be de-asserted

when the IDLE pattern been confirmed.

The RXDV signal will be asserted when decoded 5B are /J/K/and will be deasserted if the 5B are /T/R/or IDLE in 100Mbps

mode. In 10Mbps mode, the RXDV signal is the same as the CRS signal.

The RXER (Receive Error) signal will be asserted if any 5B decode errors occur such as invalid J/K, T/R, invalid symbol, this

pin will go high for one or more clock period to indicate to the reconciliation sublayer that an error was detected somewhere in

the frame.

The RTL8201BL does not use the TXER signal and will not affect the transmit function.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

14

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.1.2.

Serial Management

The MAC layer device can use the MDC/MDIO management interface to control a maximum of 31

RTL8201BL devices, configured with different PHY addresses (00001b to 11111b). During a hardware

reset, the logic levels of pins 9,10,12,13,15 are latched into the RTL8201BL to be set as the PHY address

for serial management interface communication. Setting the PHY address to 00000b will put the

RTL8201BL into power down mode. The read and write frame structure for the management interface

follows.

MDC

MDIO

32 1s

0

Preamble

1

0

ST

1

A4

OP

A3

A2

A1

A0

R4

PHYAD[4:0]

R3

R2

R1

R0

1

REGAD[4:0]

0

D15 D14 D13 D12 D11 D10

D9

D8

TA

D7

D6

D5

D4

D3

D2

D1

D0

DATA

Idle

MDIO is sourced by MAC. Clock data into PHY on rising edge of MDC

Write Cycle

MDC

MDIO

32 1s

Preamble

0

1

ST

1

0

OP

A4

A3

A2

A1

A0

PHYAD[4:0]

R4

R3

R2

R1

REGAD[4:0]

R0

Z

0

D15 D14 D13 D12 D11 D10

D9

TA

D8

D7

D6

D5

D4

D3

D2

D1

DATA

MDIO is sourced by MAC. Clock data into PHY on rising edge of MDC

D0

Idle

MDIO is sourced by PHY. Clock data from PHY on rising edge of MDC

Read Cycle

Preamble

ST

OP

PHYAD

REGAD

TA

DATA

IDLE

32 contiguous logic '1's sent by the MAC on MDIO along with 32 corresponding cycles on MDC. This

provides synchronization for the PHY.

Start of Frame. Indicated by a 01 pattern.

Operation code. Read = 10. Write = 01.

PHY Address. Up to 31 PHYs can be connected to one MAC. This 5 bit field selects which PHY the frame is

directed to.

Register Address. This is a 5 bit field that selects which one of the 32 registers of the PHY this operation refers to.

Turnaround. This is a two bit time spacing between the register address and the data field of a frame to avoid

contention during a read transaction. For a read transaction, both the STA and the PHY shall remain in a

high-impedance state for the first bit time of the turnaround. The PHY shall drive a zero bit during the second

bit time of the turnaround of a read transaction.

Data. These are the 16 bits of Data.

Idle Condition, not actually part of the management frame. This is a high impedance state. Electrically, the

PHY's pull-up resistor will pull the MDIO line to a logic one.

8.2. Auto-negotiation and Parallel Detection

The RTL8201BL supports IEEE 802.3u clause 28 Auto-negotiation operation which can cooperate with other transceivers

supporting auto-negotiation. By this mechanism, the RTL8201BL can auto detect the link partner’s ability and determine the

highest speed/duplex configuration and transmit/receive in this configuration. If the link partner does not support

Auto-negotiation, then the RTL8201BL will enable half duplex mode and enter parallel detection. The RTL8201BL will

default to transmit FLP and wait for the link partner to respond. If the RTL8201BL receives FPL, then the auto-negotiation

process will go on. If it receives NLP, then the RTL8201BL will change to 10Mbps and half duplex mode. If it receives a

100Mbps IDLE pattern, it will change to 100Mbps and half duplex mode.

To enable the auto-negotiation mode operation on the RTL8201BL, just pull the ANE pin high. And the SPEED pin and

DUPLEX pin will set the ability content of auto-negotiation register. The auto-negotiation mode can be externally disabled by

pulling the ANE pin low. In this case, the SPEED pin and DUX pin will change the media configuration of the RTL8201BL.

Below is a list for all configurations of the ANE/SPEED/DUPLEX pins and their operation in Fiber or UTP mode.

Select Medium type and interface mode to MAC

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

15

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

FX

(pin 24)

L

L

H

MII/SNIB

(pin 44)

H

L

X

Operation mode

UTP mode and MII interface

UTP mode and SNI interface

Fiber mode and MII interface

UTP mode and MII interface

ANE

(Pin 37)

SPEED

(Pin 39)

DUPLEX

(Pin 38)

H

L

L

H

H

L

H

H

L

H

H

H

L

L

L

L

L

L

H

H

L

H

L

H

Operation

Auto-negotiation enable, the ability field does not support 100Mbps and full duplex

mode operation

Auto-negotiation enable, the ability field does not support 100Mbps operation

Auto-negotiation enable, the ability field does not support full duplex mode operation

Default setup, auto-negotiation enable, the RTL8201BL will support 10BaseT

/100BaseTX, half/full duplex mode operation

Auto-negotiation disable, force the RTL8201BL into 10BaseT and half duplex mode

Auto-negotiation disable, force the RTL8201BL into 10BaseT and full duplex mode

Auto-negotiation disable, force the RTL8201BL into 100BaseTX and half duplex mode

Auto-negotiation disable, force the RTL8201BL into 100BaseTX and full duplex mode

UTP mode and SNI interface

SNI interface to MAC. It only works in 10Base-T when the SNI interface is enabled.

ANE

(Pin 37)

X

SPEED

(Pin 39)

X

DUPLEX

(Pin 38)

L

X

X

H

Operation

The duplex pin is pulled low to support the 10Base-T half duplex function.10Base-T

half duplex is the specified default mode in the SNI interface.

The RTL8201BL also supports full duplex in SNI mode. The duplex pin is pulled high

to support 10Base-T full duplex function.

Fiber mode and MII interface

The RTL8201BL only supports 100Base-FX when Fiber mode is enabled. Ignore ANE and Speed hardwire configuration.

ANE

(Pin 37)

X

X

SPEED

(Pin 39)

X

X

DUPLEX

(Pin 38)

H

L

Operation

The duplex pin is pulled high to support 100Base-FX full duplex function.

The duplex pin is pulled low to support 100Base-FX half duplex function.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

16

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.3. Flow Control Support

The RTL8201BL supports flow control indications. The MAC can program the MII register to indicate to the PHY that flow

control is supported. When MAC supports the Flow Control mechanism, setting bit 10 of the ANAR register by MDC/MDIO

SMI interface, then the RTL8201BL will add the ability to its N-Way ability. If the Link partner also supports Flow Control,

then the RTL8201BL can recognize the Link partner’s N-Way ability by examining bit 10 of ANLPAR (register 5).

8.4. Hardware Configuration and Auto-negotiation

This section describes methods to configure the RTL8201BL and set the auto-negotiation mode. This list will show the various

pins and their setting to provide the desired result.

z

Isolate pin: Set high to isolate the RTL8201BL from the MAC. This will also isolate the MDC/MDIO

management interface. In this mode, power consumption is minimum. Please refer to the section covering Isolation mode

and Power Down mode.

z

RPTR pin: Pull high to set the RTL8201BL into repeater mode. This pin is pulled low by default. Please refer to

the section covering Repeater mode operation.

z

LDPS pin: Pull high to set the RTL8201BL into LDPS mode. This pin is pulled low by default. Please refer to the

section covering Power Down mode and Link Down Power Saving.

z

MII/SNIB: Pull high to set RTL8201BL into MII mode operation, which is the default mode for the RTL8201.

This pin pulled low will set the RTL8201BL into SNI mode operation. When set to SNI mode, the RTL8201BL will work

at 10Mbps. Please refer to the section covering Serial Network Interface for more detail information.

z

ANE pin: Pull high to enable Auto-negotiation (default). Pull low to disable auto-negotiation and activate the

parallel detection mechanism. Please refer to the section covering Auto-negotiation and Parallel Detection

z

Speed pin: When ANE is pulled high, the ability to adjust speed is setup. When ANE is pulled low, pull this pin

low to force 10Mbps operation and high to force 100Mbps operation. Please refer to the section on Auto-negotiation and

Parallel Detection.

z

DUPLEX pin: When ANE is pulled high, the ability to adjust the DUPLEX pin will be setup. When ANE is pulled

low, pull this pin low to force half duplex and high to force full duplex operation. Please refer to the section covering

Auto-negotiation and Parallel Detection.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

17

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.5. LED and PHY Address Configuration

In order to reduce the pin count on the RTL8201BL, the LED pins are duplexed with the PHY address pins. Because the

PHYAD strap options share the LED output pins, the external combinations required for strapping and LED usage must be

considered in order to avoid contention. Specifically, when the LED outputs are used to drive LEDs directly, the active state of

each output driver is dependent on the logic level sampled by the corresponding PHYAD input upon power-up/reset. For

example, as following left figure shows, if a given PHYAD input is resistively pulled high then the corresponding output will

be configured as an active low driver. As right figure shows, if a given PHYAD input is resistively pulled low then the

corresponding output will be configured as an active high driver. The PHY address configuration pins should not be connected

to GND or VCC directly, but must be pulled high or low through a resistor (ex 5.1KΩ). If no LED indications are needed, the

components of the LED path (LED+510Ω) can be removed.

VCC

PAD[0:4]/

LED[0:4]

LED

5.1K ohm

510 ohm

LED

510 ohm

5.1K ohm

PAD[0:4]/

LED[0:4]

PHY address[:] = logic 1

LED indication = active low

LED0

LED1

LED2

LED3

LED4

PHY address[:] = logic 0

LED indication = active High

Link

Full Duplex

Link 10-Activity

Link 100-Activity

Collision

LED Definitions

8.6. Serial Network Interface

The RTL8201BL also supports the traditional 7-wire serial interface to cooperate with legacy MACs or embedded systems. To

setup for this mode of operation, pull the MII/SNIB pin low and by doing so, the RTL8201BL will ignore the setup of the ANE

and SPEED pins. In this mode, the RTL8201BL will set the default to work in 10Mbps and Half-duplex mode. But the

RTL8201BL may also support full duplex mode operation if the DUPLEX pin has been pulled high.

This interface consists of 10Mbps transmit and receive clock generated by PHY, 10Mbps transmit and receive serial data,

transmit enable, collision detect, and carry sense signals.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

18

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.7. Power Down, Link Down, Power Saving, and Isolation Modes

The RTL8201BL supplies 4 kinds of Power Saving mode operation. This section will discuss all four, including how to

implement each mode. The first three modes are configured through software, and the fourth through hardware.

z

Analog off: Setting bit 11 of register 17 to 1 will put the RTL8201BL into analog off state. In analog off state, the

RTL8201BL will power down all analog functions such as transmit, receive, PLL, etc. However, the internal 25MHz

crystal oscillator will not be powered down. The digital functions in this mode are still available which allows

reacquisition of analog functions.

z

LDPS mode: Setting bit 12 of register 17 to 1 or pulling the LDPS pin high will put the RTL8201BL into LDPS

(Link Down Power Saving) mode. In LDPS mode, the RTL8201BL will detect the link status to decide whether or not to

turn off the transmit function. If the link is off, FLP or 100Mbps IDLE/10Mbps NLP will not be transmitted. However,

some signals similar to NLP will be transmitted. Once the receiver detects any leveled signals, it will stop the signal and

transmit FLP or 100Mbps IDLE/10Mbps NLP again. This may save about 60%~80% power when the link is down.

z

PWD mode: Setting bit 11 of register 0 to 1 will put the RTL8201BL into power down mode. This is the maximum

power saving mode while the RTL8201BL is still alive. In PWD mode, the RTL8201BL will turn off all analog/digital

functions except the MDC/MDIO management interface. Therefore, if the RTL8201BL is put into PWD mode and the

MAC wants to recall the PHY, it must create the MDC/MDIO timing by itself (this is done by software).

z

Isolation mode: This mode is different from the three previous software configured power saving modes. This

mode is configured by hardware pin 43. Setting pin 43 high will isolate the RTL8201BL from the Media Access Controller

(MAC) and the MDC/MDIO management interface. In this mode, power consumption is minimum.

8.8. Media Interface

8.8.1.

100Base-TX

1)

100Base-TX Transmit Function: The 100Base-TX transmit function is performed as follows:

First the transmit data in 4 bit nibbles (TXD[3:0]), clocked in 25MHz (TXC) will be transformed into

5B symbol code, called 4B/5B encoding. Scrambling, serializing and conversion to 125Mhz, and

NRZ to NRZI will then take place. After this process, the NRZI signal will pass to the MLT3 encoder,

then to the transmit line driver. The transmitter will first assert TXEN. Before transmitting the data

pattern, it will send a /J/K/ symbol (Start-of-frame delimiter), the data symbol, and finally a /T/R/

symbol known as the End-Of-Frame delimiter. The 4B/5B and the scramble process can be bypassed

by setting the PHY register. For better EMI performance consideration, the seed of the scrambler is

related to the PHY address. Therefore in a hub/switch environment, every RTL8201BL will be set

into a different PHY address so that they will use different scrambler seeds, which will spread the

output of the MLT3 signals.

2)

100Base-TX Receive Function: The 100Base-TX receive function is performed as follows:

The received signal will first be compensated by the adaptive equalizer to make up for the signal loss

due to cable attenuation and ISI. The Baseline Wander Corrector will monitor the process and

dynamically apply corrections to the process of signal equalization. The PLL will then recover the

timing information from the signals and form the receive clock. With this, the received signal may be

sampled to form NRZI data. The next steps are the NRZI to NRZ process, unscrambling of the data,

serial to parallel and 5B to 4B conversion and passing of the 4B nibble to the MII interface.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

19

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.8.2.

100Base-FX Fiber Mode Operation

RTL8201BL can be configured as 100Base-FX by hardware configuration. The priority of setting 100Base-FX is greater than

Nway. Scrambler is not needed in 100Base-FX.

z

100Base-FX Transmit Function: The 100Base-FX transmit function is performed as follows: Di-bits of TXD are

processed as 100Base-TX, except without scrambler before the NRZI stage. Instead of converting to MLT-3 signals, as in

100Base-TX, the serial data stream is driven out as NRZI PECL signals, which enter the fiber transceiver in

differential-pairs form.

z

In 100Base-FX Receive Function: The 100Base-FX receive function is performed as follows: The signal is received

through PECL receiver inputs from the fiber transceiver, and directly passed to the clock recovery circuit for data/clock

recovery. The scrambler/de-scrambler is bypassed in 100Base-FX.

8.8.3.

10Base-Tx/Rx

1)

10Base Transmit Function: The 10Base transmit function is performed as follows: The transmit

4 bits nibbles(TXD[0:3]) clocked in 2.5MHz(TXC) is first feed to parallel to serial converter, then put

the 10Mbps NRZ signal to Manchester coding. The Manchester encoder converts the 10 Mbps NRZ

data into a Manchester Encoded data stream for the TP transmitter and adds a start of idle pulse (SOI)

at the end of the packet as specified in IEEE 802.3. Then, the encoded data stream is shaped by bandlimited filter embedded in RTL8201BL and then transmitted to TP line.

2)

10Base Receive function: The 10Base receive function is performed as follows: In 10Base

receive mode, The Manchester decoder in RTL8201BL converts the Manchester encoded data stream

from the TP receiver into NRZ data by decoding the data and stripping off the SOI pulse. Then, the

serial NRZ data stream is converted to parallel 4 bit nibble signal(RXD[0:3]).

8.9. Repeater Mode Operation

Setting bit 15 of register 17 to 1 or pulling the RPTR pin high will set the RTL8201BL into repeater mode. In repeater mode,

the RTL8201BL will assert CRS high only when receiving a packet. In NIC mode, the RTL8201BL will assert CRS high both

in transmitting and receiving packets. If using the RTL8201BL in a repeater, please set the RTL8201BL to Repeater mode, and

if using the RTL8201BL in a NIC or switch application, please set the default mode. NIC/Switch mode is the default setting

and has the RPTR pin pulled low or bit 15 of register 17 is set to 0.

8.10. Reset, and Transmit Bias (RTSET)

The RTL8201BL can be reset by pulling the RESETB pin low for about 10ms, then pulling the pin high.

It can also be reset by setting bit 15 of register 0 to 1, and then setting it back to 0. Reset will clear the

registers and re-initialize them, and the media interface will first disconnect and restart the

auto-negotiation/parallel detection process.

The RTSET pin must be pulled low by a 5.9KΩ resister with 1% accuracy to establish an accurate

transmit bias, this will affect the signal quality of the transmit waveform. Keep it’s circuitry away from

other clock traces or transmit/receive paths to avoid signal interference.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

20

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

8.11. 3.3V Power Supply and Voltage Conversion Circuit

The RTL8201BL is fabricated in a 0.25um process. The core circuit needs to be powered by 2.5V , however, the circuit of

digital IO and DAC need 3.3V power supply. RTL8201BL has embedded a regulator to convert 3.3V to 2.5V. Just like many

commercial voltage conversion devices, The 2.5V output pin(PWFBOUT) of this circuit requires the use of an output

capacitor(22uF tantalum capacitor) as part of the device frequency compensation and another small capacitor(0.1uF) for high

frequency noise de-coupling. And PWFBIN is fed with the 2.5V power from PWFBOUT through a ferrite bead as below figure

shown. Strongly emphasize here, could not provide external 2.5V produced by any other power device for PWFBOUT and

PWFBIN.

The analog and digital Ground planes should be as large and intact as possible. If the ground plane is

large enough, the analog and digital grounds can be separated, which is a more ideal configuration.

However, if the total ground plane is not sufficiently large, partition of the ground plane is not a good

idea. In this case, all the ground pins can be connected together to a larger single and intact ground plane.

RTL8201B(L)

DVDD33(pin14)

AVDD33(pin36)

3.3V-drived

circuit

3.3V

Ferrite Bead

3.3V

0.1uF

0.1uF

DVDD33(pin48)

Error Amp

-

0.1uF

MOSFET P

+

PWFBOUT(pin32)

1.2V

bandgap

voltage

22uF

Ferrite Bead

0.1uF

PWFBIN(pin8)

2.5V-drived

circuit

0.1uF

8.12. Far End Fault Indication

The MII Reg.1.4 (Remote Fault) is theFar End Fault Indication (FEFI) bit when 100FX mode is enabled which

indicates that FEFI has been detected. FEFI is an alternative in-ba nd signaling method which is composed of 84

consecutive ‘1’ followed by one ‘0’. From the point of view of the RTL8201BL, when this pattern is detected

three times, Reg.1.4 is set, which means the transmit path (the Remote side’s receive path) has a problem. On the

other hand, the incoming signal failure in causing a link OK will force the RTL8201BL to start sending this

pattern, which in turn causes the remote side to detect a Far-End-Fault. This means that the receive path has a

problem from the point of view of the RTL8201BL. The FEFI mechanism is used only in 100Base-FX mode.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

21

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.

Electrical Characteristics

9.1. D.C. Characteristics

9.1.1.

Absolute Maximum Ratings

Symbol

Supply Voltage

Storage Temp.

9.1.2.

Minimum

3.0V

-55°C

Typical

3.3V

Maximum

3.6V

125°C

Minimum

3.0V

0°C

Typical

3.3V

Maximum

3.6V

70°C

Operating Conditions

Symbol

Vcc 3.3V

TA

9.1.3.

Conditions

Conditions

3.3V Supply voltage

Operating Temperature

Power Dissipation

Test condition: VCC=3.3V

Symbol

Condition

PLDPS

Link down power saving mode

PAnaOff

Analog off mode

PPWD

Power down mode

PIsolate

Isolate mode

P100F

100Base full duplex

P10F

10Base full duplex

P10TX

10Base transmit

P10RX

10Base receive

P10IDLE

10Base idle

9.1.4.

Symbol

TTL VIH

TTL VIL

TTL VOH

TTL VOL

TTL IOZ

IIN

Icc

PECL VIH

PECL VIL

PECL VOH

PECL VOL

Total Current Consumption

17 mA

13 mA

3 mA

3 mA

64 mA

82 mA

82 mA

25 mA

24 mA

Supply Voltage: Vcc

Conditions

Input High Vol.

Input Low Vol.

Output High Vol.

IOH=-8mA

Output Low Vol.

IOL=8mA

Tri-state Leakage

Vout=Vcc

GND

Input Current

Vin=Vcc

GND

Average

Operating Iout=0mA

Supply Current

PECL Input High Vol

PECL Input Low Vol.

PECL Output High Vol.

PECL Output Low Vol.

Minimum

0.5*Vcc

-0.5V

0.9*Vcc

or

-10uA

Maximum

Vcc+0.5V

0.3*Vcc

Vcc

0.1*Vcc

10uA

or

-1.0uA

1.0uA

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

Typical

200mA

Vdd-1.16V

Vdd-1.81V

Vdd-1.02V

Vdd-0.88V

Vdd-1.47V

Vdd-1.62V

22

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.2. A.C. Characteristics

9.2.1.

MII Timing of Transmission Cycle

Shown is an example transfer of a packet from MAC to PHY in MII interface.

Symbol

t1

t2

t3

t4

t5

t6

t7

Description

TXCLK high pulse width

100Mbps

Minimum

14

Typical

20

Maximum

26

Unit

ns

10Mbps

140

200

260

ns

14

140

20

200

40

400

24

26

260

ns

ns

ns

ns

ns

10

25

ns

ns

40

400

160

ns

ns

ns

ns

2000

ns

70

140

ns

100

400

170

ns

ns

ns

TXCLK low pulse width

100Mbps

10Mbps

TXCLK period

100Mbps

10Mbps

TXEN, TXD[0:3] setup to TXCLK 100Mbps

rising edge

10Mbps

TXEN, TXD[0:3] hold after 100Mbps

TXCLK rising edge

10Mbps

TXEN sampled to CRS high

100Mbps

10Mbps

TXEN sampled to CRS low

100Mbps

10

5

5

10Mbps

t8

Transmit latency

100Mbps

t9

10Mbps

Sampled TXEN inactive to end of 100Mbps

frame

10Mbps

60

t3

VIH(min

VIL(max

TXCLK

t4

t5

t1

VIH(min

VIL(max

TXD[0:3]

TXEN

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

t2

23

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

TXCLK

TXEN

TXD[0:3]

t6

t7

CRS

t8

TPTX+-

9.2.2.

t9

MII Timing of Reception Cycle

Shown is an example of transfer of a packet from PHY to MAC in MII interface

Symbol

Description

Minimum

t1

RXCLK high pulse width

100Mbps

14

10Mbps

140

t2

RXCLK low pulse width

100Mbps

14

t3

10Mbps

100Mbps

RXCLK period

t6

10Mbps

RXER, RXDV, RXD[0:3] setup to 100Mbps

RXCLK rising edge

10Mbps

RXER, RXDV, RXD[0:3] hold after 100Mbps

RXCLK rising edge

10Mbps

Receive frame to CRS high

100Mbps

t4

t5

140

Typical

20

200

20

Maximum

26

260

26

Unit

ns

ns

ns

200

40

260

ns

ns

400

ns

ns

ns

ns

10

6

10

130

ns

ns

t7

End of receive frame to CRS low

10Mbps

100Mbps

600

240

ns

ns

t8

10Mbps

Receive frame to sampled edge of 100Mbps

RXDV

10Mbps

600

150

ns

ns

3200

120

ns

ns

800

ns

t9

6

End of receive frame to sampled 100Mbps

edge of RXDV

10Mbps

t3

VIH(min

VIL(max

RXCLK

RXD[0:3]

RXDV

RXER

t4

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

t5

t1

t2

VIH(min

VIL(max

24

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

RXCLK

t8

t9

RXDV

RXD[0:3]

t6

t7

CRS

TPRX+-

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

25

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.2.3.

SNI Timing of Transmission Cycle

Shown is an example transfer of a packet from MAC to PHY in SNI interface. SNI mode only runs in 10Mbps.

Symbol

t1

t2

t3

t4

t5

t8

Description

TXCLK high pulse width

TXCLK low pulse width

TXCLK period

TXEN, TXD0 setup to TXCLK rising edge

TXEN, TXD0 hold after TXCLK rising edge

Transmit latency

Minimum

36

36

80

20

10

Typical

Maximum

120

50

Unit

ns

ns

ns

ns

ns

ns

t3

VIH(min

VIL(max

TXCLK

t4

t5

t1

t2

VIH(min

VIL(max

TXD0

TXEN

TXCLK

TXEN

TXD0

TPTX+-

t8

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

t9

26

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.2.4.

SNI Timing of Reception Cycle

Shown is an example of transfer of a packet from PHY to MAC in SNI interface. SNI mode only runs in 10Mbps.

Symbol

Description

Minimum

Typical

Maximum

t1

RXCLK high pulse width

36

t2

RXCLK low pulse width

36

t3

RXCLK period

80

120

t4

RXD0 setup to RXCLK rising edge

40

t5

RXD0 hold after RXCLK rising edge

40

t6

Receive frame to CRS high

50

t7

End of receive frame to CRS low

160

t8

Decoder acquisition time

600

1800

Unit

ns

ns

ns

ns

ns

ns

ns

ns

t3

VIH(min

VIL(max

RXCLK

t4

t5

t1

t2

VIH(min

VIL(max

RXD0

RXCLK

t8

RXD0

t6

t7

CRS

TPRX+-

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

27

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.2.5.

Symbol

t1

t2

t3

t4

t5

t6

MDC/MDIO timing

Description

MDC high pulse width

MDC low pulse width

MDC period

MDIO setup to MDC rising edge

MDIO hold time from MDC rising edge

MDIO valid from MDC rising edge

Minimum

160

160

400

10

10

0

Typical

Maximum

300

Unit

ns

ns

ns

ns

ns

ns

t3

VIH(min)

VIL(max

MDC

MDIO

sourced by

STA

t4

MDIO

sourced by

RTL8201B

9.2.6.

t5

t1

t2

VIH(min)

VIL(max

t6

VIH(min

VIL(max

Transmission Without Collision

Shown is an example transfer of a packet from MAC to PHY.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

28

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.2.7.

Reception Without Error

Shown is an example of transfer of a packet from PHY to MAC.

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

29

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

9.3. Crystal and Transformer Specifications

9.3.1.

Item

1

2

3

Crystal Specifications

Parameter

Range

Nominal Frequency

Oscillation Mode

25.000 MHz

Base wave

±50 ppm

4

Frequency Tolerance at 25℃

Temperature Characteristics

5

Operating Temperature Range

6

7

8

9

10

11

12

Equivalent Series Resistance

Drive Level

Load Capacitance

Shunt Capacitance

Insulation Resistance

Test Impedance Meter

Aging Rate A Year

-10℃ ~ +70℃

30 ohm Max.

0.1 mV

20 pF

7 pF Max.

Mega ohm Min./DC 100V

Saunders 250A

9.3.2.

±50 ppm

±0.0003%

Transformer Specifications

Parameter

Turn ratio

Inductance (min.)

Leakage inductance

Capacitance (max)

DC resistance (max)

Transmit End

1:1 CT

350 uH @ 8mA

0.05-0.15 uH

15 pF

0.4 ohm

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

Receive End

1:1

350 uH @ 8mA

0.05-0.15 uH

15 pF

0.4 ohm

30

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

10. Mechanical Dimensions

Symbo

l

A

A1

A2

b

b1

c

c1

D

D1

E

E1

e

L

L1

θ

θ1

θ2

θ3

Dimension in

inch

Min

Nom

Max

0.067

0.000

0.004

0.008

0.051

0.055

0.059

0.006

0.009

0.011

0.006

0.008

0.010

0.004

0.008

0.004

0.006

0.354 BSC

0.276 BSC

0.354 BSC

0.276 BSC

0.020 BSC

Dimension in

mm

Min

Nom

Max

1.70

0.00

0.20

0.1

1.30

1.50

1.40

0.29

0.22

0.15

0.15

0.25

0.20

0.09

0.20

0.09

0.16

9.00 BSC

7.00 BSC

9.00 BSC

7.00 BSC

0.50 BSC

0.016

0.40

0°

0°

0.024

0.031

0.039 REF

3.5°

9°

12° TYP

12° TYP

0°

0°

0.60

0.80

1.00 REF

3.5°

9°

12° TYP

12° TYP

Single Chip Single Port 10/100M Fast Ethernet Phyceiver

Notes:

1.To be determined at seating plane -c2.Dimensions D1 and E1 do not include mold protrusion.

D1 and E1 are maximum plastic body size dimensions

including mold mismatch.

3.Dimension b does not include dambar protrusion.

Dambar can not be located on the lower radius of the foot.

4.Exact shape of each corner is optional.

5.These dimensions apply to the flat section of the lead

between 0.10 mm and 0.25 mm from the lead tip.

6. A1 is defined as the distance from the seating plane to the

lowest point of the package body.

7.Controlling dimension: millimeter.

8. Reference document: JEDEC MS-026, BBC

TITLE: 48LD LQFP ( 7x7x1.4mm)

PACKAGE OUTLINE DRAWING, FOOTPRINT 2.0mm

LEADFRAME MATERIAL:

APPROVE

DOC. NO.

VERSION

1

PAGE

OF

CHECK

DWG NO.

SS048 - P1

DATE

Sept. 25.2000

REALTEK SEMI-CONDUCTOR CORP.

31

Track ID: JATR-1076-21

Rev. 1.3

�RTL8201BL

Datasheet

11. Ordering Information

Table 1. Ordering Information

Part Number

Package

RTL8201BL

48-Pin LQFP

RTL8201BL-LF

RTL8201BL with Lead (Pb)-Free package