物料型号:74HC4050

器件简介:74HC4050 是 Nexperia 公司生产的模拟多路复用器/解复用器集成电路。

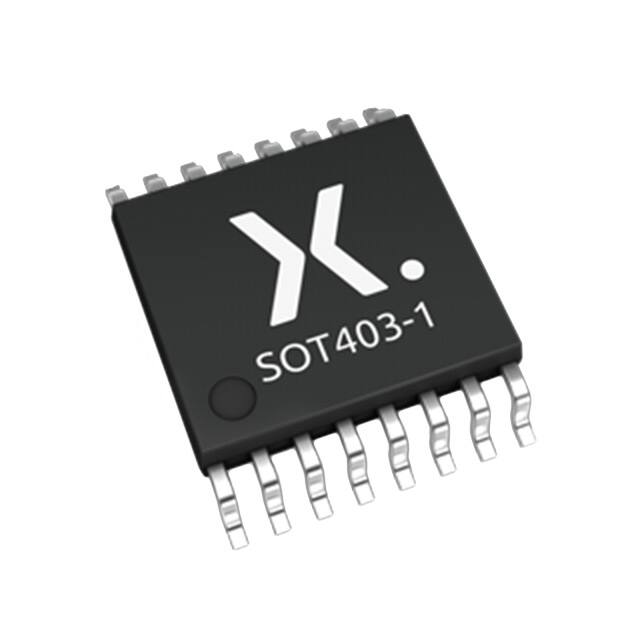

引脚分配:74HC4050 有 16 个引脚,包括电源引脚、地引脚、输入输出引脚等。

参数特性:工作电压范围为 2V 至 6V,工作温度范围为 -40°C 至 +85°C。

功能详解:74HC4050 能够实现 8 路输入到 1 路输出的信号选择,或 1 路输入到 8 路输出的信号分配。

应用信息:常用于信号分配、数据选择、多路复用等场景。

封装信息:74HC4050 有多种封装形式,如 SOIC、DIP 等。