PL-2303 USB to RS-232 Bridge Controller

Product Datasheet

Document Revision 1.4

Document Release: August, 2002

Prolific Technology Inc.

�Release Date:

July, 2002

ds_pl2303_v14

Revision History

Revision

Description

Date

1.4

•

Add Windows CE .NET support feature

August 29, 2002

1.3

•

Buffer for upstream and downstream data flow –

change from 96 to 256 bytes

August 01, 2002

1.2

•

For Chip Version H (date code 0206)

July 03, 2002

•

Add OS Support in Features Section

•

Correct default values in Table 5. Device

Configuration Register

•

Add Suspend Current in DC Characteristics Section

•

Move Operating Temperature in DC Characteristics

to new section

PL-2303 Product Datasheet

-2-

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

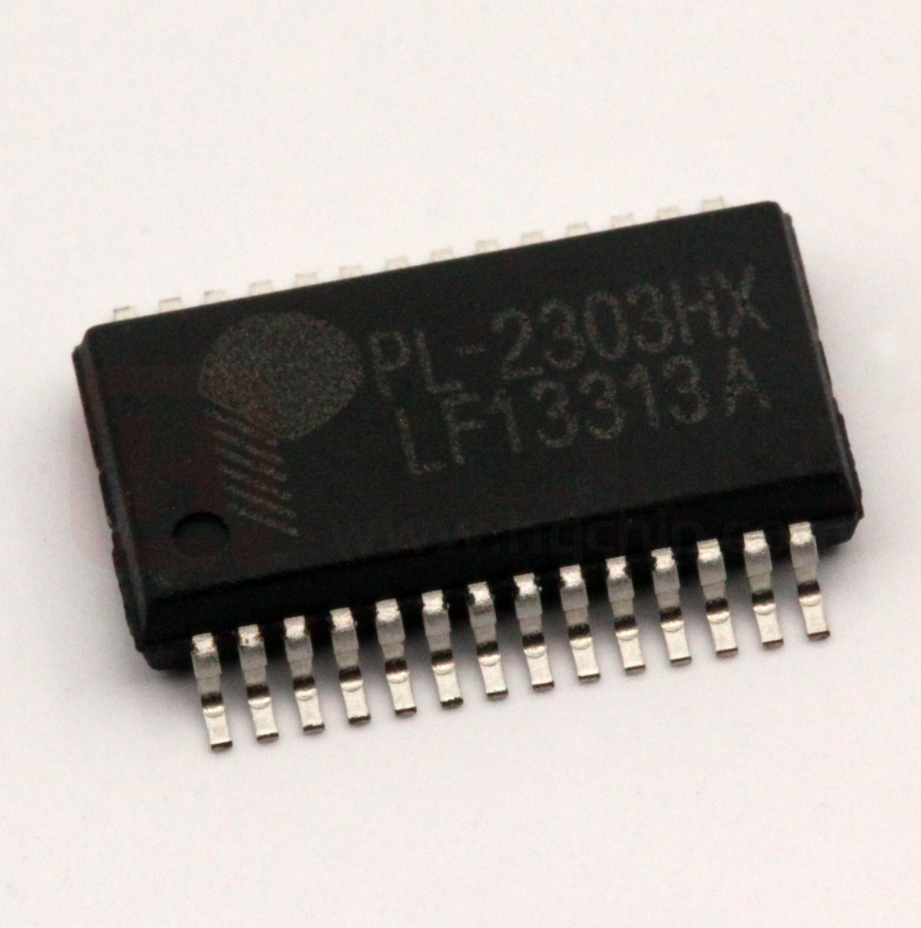

PL-2303 USB to Serial RS232 Bridge Controller

Features

�

Full compliance with the USB Specification v1.1 and USB CDC v1.1

�

Support the RS232 Serial interface

�

Support automatic handshake mode

�

Support Remote wake-up and power management

�

256 bytes buffer each for upstream and downstream data flow

�

Support default ROM or external EEPROM for device configuration

�

On chip USB transceiver

�

On chip crystal oscillator running at 12M Hz

�

Supports Windows 98/SE, ME, 2000, XP, Windows CE3.0, CE .NET, Linux, and Mac OS

�

28 Pins SOIC package

SSOP 28 PACKAGE

(TOP VIEW)

PL-2303 Product Datasheet

TXD

1

28

OSC2

DTR_N

2

27

OSC1

RTS_N

3

26

VDD_232

4

25

GND_PLL

RXD

5

24

VDD_PLL

RI_N

6

23

LD_MODE

GND

7

22

TRI_MODE

VDD

8

21

GND

DSR_N

9

20

VDD

DCD_N

10

19

RESET

PLL_TEST

CTS_N

11

18

GND_3V3

SHTD_N

12

17

VDD_3V3

EE_CLK

13

16

DM

EE_DATA

14

15

DP

-3-

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Block Diagram

USB Port

USB

Transceiver

REGISTER/

Control

USB

CONFIG/

Unit

SIE

STATUS/

CONTROL

DOWN

UP

STREAM

STREAM

BUFFER

BUFFER

CLOCK

SYNTHESIZE

RS-232 SERIAL

INTERFACE

EEPROM

OSCILLATOR

INTERFACE

Serial Port

PL-2303 Product Datasheet

-4-

I2C Bus

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Overview

The PL-2303 operates as a bridge between one USB port and one standard RS232 Serial port. The two

large on-chip buffers accommodate data flow from two different buses. The USB bulk-type data is adopted

for maximum data transfer. Automatic handshake is supported at the Serial port. With these, a much higher

baud rate can be achieved compared to the legacy UART controller.

This device is also compliant with USB power management and remote wakeup scheme. Only minimum

power is consumed from the host during Suspend. By integrating all the function in a SOIC-28 package, this

chip is suitable for cable embedding. Users just simply hook the cable into PC or hub’s USB port, and then

they can connect to any RS-232 devices.

Pin Description

Table 1. Pins Description

Pin

No.

1

2

3

4

Name

TXD

DTR_N

RTS_N

VDD_232

Type

O

O

O

P

Description

Data output to Serial port

Data Terminal Ready, active low

Request To Send, active low

RS-232 VDD. The RS-232 output signals (Pin 1 ~ Pin 3) are

designed for 5V, 3.3V or 3V operation. VDD_232 should be

connected to the same power level of the RS-232 interface.

(The RS-232 input signals are always 5V~3V tolerant.)

Note: This document version only provides 5V DC characteristic

information. Refer to future revisions for updates.

5

6

7

8

9

10

11

12

13

RXD

RI_N

GND

VDD

DSR_N

DCD_N

CTS_N

SHTD_N

EE_CLK

I

I

P

P

I

I

I

O

I/O

14

15

16

17

18

19

20

21

EE_DATA

DP

DM

VDD_3V3

GND_3V3

RESET

VDD

GND

I/O

I/O

I/O

P

P

I

P

P

PL-2303 Product Datasheet

Data input from Serial Bus

Ring Indicator, active low

Ground

Power

Data Set Ready, active low

Data Carrier Detect, active low

Clear To Send, active low

Shut Down RS232 Transceiver

During Reset, this pin is input for simulation purpose. During

normal operation, this pin is Serial ROM clock

Serial ROM data signal

USB DPLUS signal

USB DMINUS signal

3.3V power for USB transceiver

3.3V ground

System Reset

Power

Ground

-5-

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Pin

No.

22

TRI_STATE

23

LD_MD/

SHTD

24

25

26

27

28

Type:

Name

Type

I

I/O

VDD_PLL

GND_PLL

PLL_TEST

OSC1

OSC2

I – Input signal

P

P

I

I

O

Description

Tri-State

This pin is referred after reset.

High: RS-232 output inactive during Suspend.

Low: RS-232 output tri-state during Suspend.

Load Mode/SHTD

This pin is input during reset. Pull high with a 220K resistor to

indicate the heavy load USB device (500mA). Pull down with a

220K resistor to indicate the light load USB device 100mA).

After reset, this pin becomes output. It output the inverse of

SHTD_N.

5V power for PLL

Ground for PLL

PLL test mode control

Crystal oscillator input

Crystal oscillator output

O – Output signal

I/O – Bi-directional signal

P – Power/Ground

Supported Data Formats and Programmable Baud Rate Generator

The PL2303 USB-to-RS232 bridge controller supports versatile data formats and has a programmable baud

rate generator. The supported data formats are shown on Table 2. The programmable baud rate generator

supports baud rates up to 1.2M bps as shown in Table 3.

Table 2. Supported Data Formats

Description

Stop bits

Parity type

Data bits

PL-2303 Product Datasheet

1

1.5

2

None

Odd

Even

Mark

Space

5, 6, 7, 8, or 16

-6-

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Table 3. Baud Rate Setting

dwDTERate

0012C000h

000E1000h

00096000h

00070800h

00038400h

0001C200h

0000E100h

00009600h

00007080h

00004B00h

00003840h

00002580h

00001C20h

000012C0h

00000E10h

00000960h

00000708h

000004B0h

00000258h

0000012Ch

00000096h

0000004Bh

Baud Rate

1228800

921600

614400

460800

230400

115200

57600

38400

28800

19200

14400

9600

7200

4800

3600

2400

1800

1200

600

300

150

75

External EEPROM and Device Configuration

PL-2303 allows storing the configuration data in an external EEPROM. After reset, the first two bytes of

EEPROM are checked. If the value is 067Bh, the EEPROM is valid and the contents of the EEPROM are

loaded as the chip’s default parameters. Otherwise, the chip’s default setting is used. The content of

EEPROM is shown in Table 4 below.

The Device Configuration Register is used to control some vendor-specific functions. The meaning of each

bit in Device Configuration Register is shown in Table 5. Reserved and unused pins always set to the default

value.

Table 4. EEPROM Content

Bytes

1:0

Name

EECHK

3:2

5:4

7:6

10:8

VID

PID

RN

DCR

PL-2303 Product Datasheet

Description

When the EEPROM is programmed, these two bytes is configured as 067B.

After reset, they will be checked for the value. If matched, the following

information will be loaded as the default parameters.

USB Vendor ID

Product ID

Release number (BCD)

Device Configuration Register

-7-

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Table 5. Device Configuration Register

Name

Bits

23

22

RESERVED

TRI_OUT

21

RW_MODE

20

WURX

19

WUDSR

18

WURI

17

WUDCD

16

WUCTS

15

14

13

12

RESERVED

RESERVED

RESERVED

RW_INH

11:6

5:4

RESERVED

RTSM

3:1

0

RESERVED

RSPDM

Definition

Default

Reserved

RS-232 Output Tri-state:

1: RS-232 output tri-state

0: RS-232 output in output mode

Remote Wakeup Mode:

0: When engages remote wakeup, the device issues disconnect

signal

1: When engages remote wakeup, the device issues resume

signal

Enable Wake Up Trigger on RXD:

0 – Disabled;

1 – Enable Wake Up Trigger on RXD state changes.

Enable Wake Up Trigger on DSR:

0 – Disabled;

1 – Enable Wake Up Trigger on DSR state changes.

Enable Wake Up Trigger on RI:

0 – Disabled;

1 – Enable Wake Up Trigger on RI state changes.

Enable Wake Up Trigger on DCD:

0 – Disabled;

1 – Enable Wake Up Trigger on DCD state changes.

Enable Wake Up Trigger on CTS:

0 – Disabled;

1 – Enable Wake Up Trigger on CTS state changes.

Always set to one

Always set to zero

Always set to zero

Remote Wake Inhibit:

1 – Inhibit the USB Remote Wakeup function

0 – Enable the USB Remote Wakeup function

Always set to zero

RTS Control Method:

00b – RTS is controlled by ControlBitMap. Signal is active low;

01 – RTS is controlled by ControlBitMap. Signal is active high;

10 – Drive RTS active when Downstream Data Buffer is NOT

EMPTY; otherwise Drive RTS inactive.

11 – Drive RTS inactive when Downstream Data Buffer is NOT

EMPTY; otherwise Drive RTS active.

Always set to zero

RS-232 Transceiver Shut-Down Mode:

1: Shut down the transceiver when USB SUSPEND is engaged

0: Do not shut down the transceiver even when USB SUSPEND

is engaged

PL-2303 Product Datasheet

-8-

0

0

1

0

0

1

0

0

1

0

0

0

0

0

0

1

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Electrical Characteristics

Absolute Maximum Ratings

Item

Power Supply Voltage

Input Voltage

Output Voltage

Storage Temperature

Ratings

-0.3 to 6.0 V

-0.3 to VDD+0.3 V

-0.3 to VDD+0.3 V

o

-55 to 150 C

DC Characteristics

Parameter

Symbol

Min

Typ

Max

Units

Power Supply Current

Input Voltage

Low

High

Output Voltage

Low

High

1

Schmitt Trigger Threshold Voltage*

Negative going

Positive going

2

Output Voltage, 3.3V*

Low

High

Input Leakage Current

Tri-state Leakage Current

Input Capacitance

Output Capacitance

Bi-directional Buffer Capacitance

Operating Voltage Range

Suspend Current

IDD

0.5

19

24

mA

VIL

VIH

-0.7* VDD

---

0.3* VDD

--

V

V

VOL

VOH

-3.5

---

0.4

--

V

V

VtVt+

---

1.10

1.87

---

V

V

VOL

VOH

IL

Ioz

CIN

COUT

CBID

-ISUS

-2.4

-1

-10

---4.75

--

----3

3

3

5

400

0.4

-1

10

---5.25

490

V

V

uA

uA

Pf

Pf

Pf

V

uA

Units

*1. RS232 pins RXD_I, RI_I, DSR_I, DCD_I, CTS_I are 5V TTL Schmitt Trigger inputs.

*2. RS232 pins TXD, DTR_N, RTS_N are 3.3V tri-state outputs.

Temperature Characteristics

Parameter

Operating Temperature

Junction Operation Temperature

PL-2303 Product Datasheet

Symbol

Min

Typ

Max

-TJ

-40

0

-25

85

115

-9-

o

C

C

o

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

USB Transceiver Characteristics

Parameter

Symbol

Min

Typ

Max

Units

TR

TF

4

4

8

8

15

15

ns

ns

Cross Point

VCR

1.3

--

2.0

V

Output Impedance

RD

23

28

33

ohm

High Level Output

VOH

2.8

--

--

V

Low Level Output

VOL

--

--

0.7

V

High Level Input

VIH

2.0

--

--

V

Low Level Input

VIL

--

--

0.8

V

Min

Typ

Max

Units

11.976

12.000

12.024

MHz

83.1

83.3

83.5

ns

45

50

55

%

Rise and Fall Times:

(10%―90%)

(90%―10%)

•

CL: 50pf

Clock Characteristics

Parameter

Frequency of Operation

Clock Period

Duty Cycle

Package Dimensions (28-Pin SSOP)

Symbol

Min

b

E

E1

L

R1

D

A

e

L1

A1

A2

Millimeters

Nom

Max

Min

7.80

5.30

0.75

0.38

8.20

5.60

0.95

0.009

0.291

0.197

0.021

0.004

0.390

0.22

7.40

5.00

0.55

0.09

9.9

10.2

10.5

2.0

0.65

1.25

0.05

1.65

PL-2303 Product Datasheet

1.75

Inch

Nom

Max

0.307

0.209

0.030

0.015

0.323

0.220

0.037

0.402

0.413

0.079

0.0256

0.050

1.85

- 10 -

0.020

0.065

0.069

0.073

Document Revision 1.3

�Release Date:

July, 2002

ds_pl2303_v14

Outline Diagram

D

28

DETAIL A

E E1

1

DETAIL A

A2

A

R1

e

b

A1

0.25

L

R1

PL-2303 Product Datasheet

- 11 -

L1

Document Revision 1.3

�