Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

ASNT2110C-KMF

Programmable CDR DMUX 1-to-2

1:2 demultiplexer (DMUX) with integrated selectable full-rate CDR

Input data range from DC to 34.0Gb/s

Digital operational mode with DC to 34GHz external clock

CDR locking range from 25.2Gb/s to 32.5Gb/s

RZ and NRZ input data formats

Adjustable time of data sampling point for optimum BER performance

CML compliant differential input and output high-speed data and clock interfaces

LVDS compliant input reference clock interface

Full rate clock and retimed data output for 1:1 CDR operation

Half rate data outputs with toggle synchronization functionality

Signal inversion and muting capabilities in all output buffers

Single +3.3V or -3.3V power supply

Low power consumption of 1.6W at the maximum operational speed

Industrial temperature range

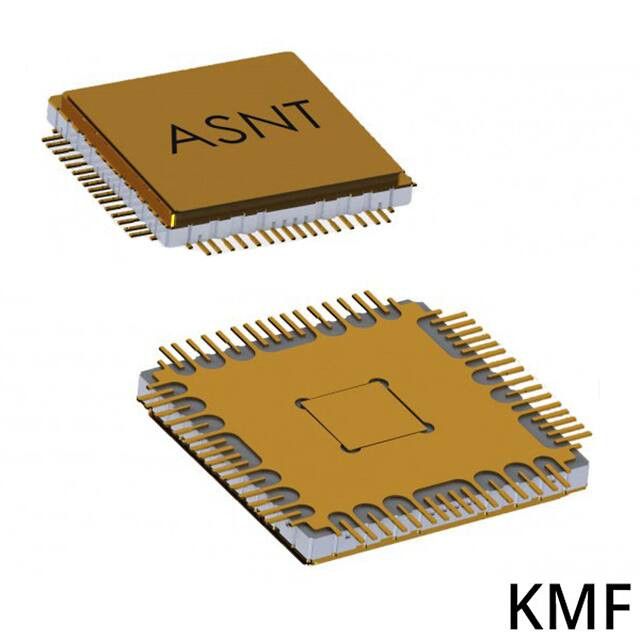

Custom CQFP 64-pin package

vee

vcc

dop

vcc

don

vcc

ondo

pol

tog

onco

vcc

c2p

vcc

c2n

vcc

vee

ASNT2110D

ASNT2110C

vee

vcc

q0p

vcc

q0n

vcc

ond2o

lolp

icph

icpl

vcc

q1p

vcc

q1n

vcc

vee

vee

vcc

cep

vcc

cen

vcc

vcos1

ftr

rngcrl/is

vcos0

vcc

c32p

vcc

c32n

vcc

vee

vee

vee

pkdtp

pkdtn

dcinp

vcc

vcc

dp

vcc

dn

vcc

vcc

dcinn

phshft

vee

vee

Rev. 1.1.2

1

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

DESCRIPTION

ondo

ce

ond2o

d

dcinp

dcinn

pkdtp

pkdtn

c32

HS

CIB

DOB

D

Data

IB

DMX

1:2

CDR

CLK

IB

do

D2OB

x2

q1

C2

lolp

fltp

phshft

icph

icpl

rngcrl/is

q0

COB

c2

vcos0

vcos1

tog

pol

onco

Fig. 1. Functional Block Diagram

ASNT2110C-KMF is a 1:2 demultiplexer (DMUX) with full-rate integrated clock and data recovery

(CDR). The IC shown in Fig. 1 can function in either CDR mode covering a wide range of input data

rates (fbit) by utilizing its three on-chip VCOs (voltage-controlled oscillators), or in a broadband digital

mode. Selection of the desired working data rate and mode is accomplished through pins vcos0 and

vcos1 (see Table 1). An external low speed system clock c32p/c32n running at 1/32 the frequency of the

active VCO must be applied to the low-speed LVDS clock input buffer (CLK IB) in CDR mode. An

external full-rate clock cep/cen must be applied to the high speed CML clock input buffer (HS CIB) for

digital operation.

The main function of the chip is to convert a RZ or NRZ input data signal dp/dn with a bit rate of fbit

accepted by CML buffer (Data IB) into 2 parallel NRZ data signals q0p/q0n and q1p/q1n running at bit

rates of fbit/2 and delivered to the outputs by CML data output buffers (D2OBx2). The clock and data are

recovered from the input data stream by the CDR. The phase of the clock recovered by the CDR can be

adjusted externally through pin phshft to locate the optimum data sampling point and achieve the lowest

system bit error rate (BER).

A full rate retimed NRZ data output signal dop/don is also available through the CML data output buffer

(DOB) allowing the part to be used as a 1:1 CDR. Half rate clock c2p/c2n delivered through the CML

clock output buffer (COB) has a tight phase alignment to the demultiplexed data output signals q0p/q0n

and q1p/q1n.

Rev. 1.1.2

2

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

Data IB can operate with either differential or single-ended input signals. It includes tuning pins

dcinp/dcinn for DC offset of the input signals in case of AC termination. When the buffer is operating

with a DC-terminated single ended input signal, a correct threshold voltage should be applied to the

unused input pin. A peak detector is also included to provide means of demodulating AM components

carried by the input data with frequency ranges of up to a few hundred KHz. The peak detector’s output

signal is delivered to the differential port pkdtp/pkdtn.

All CML I/Os provide on chip 50Ohm termination to vcc and may be used differentially, AC/DC

coupled, single-ended, or in any combination (see also POWER SUPPLY CONFIGURATION). Output

buffers DOB, COB, and D2OBx2 can be individually disabled through pins ondo, onco, and ond2o to

save power.

Utilizing pin pol, the deserializer can invert the polarity of the three output data signals. Pin tog flips the

order of q0p/q0n and q1p/q1n signals thus simplifying the interface between the DMUX and a following

ASIC. It also allows for synchronization of the bit order of two or more DMUXes working in parallel.

A loss of lock CMOS alarm signal lolp is generated by the CDR to indicate its locking state. An off chip

passive filter is required by the CDR, and should be connected to pin ftr (see CDR).

The deserializer is characterized for operation from 0°C to 125°C of junction temperature. The package

temperature resistance is 15°C /W.

Data IB

The Data Input Buffer (Data IB) can process an input CML data signal dp/dn in either RZ or NRZ format

due to its high analog bandwidth. It provides on-chip single-ended termination of 50Ohm to vcc for each

input line. The buffer can also accept a single-ended signal to one of its input ports dp or dn with a

threshold voltage applied to the unused pin in case of DC termination. In case of AC termination, tuning

pins dcinp/dcinn allow for data common mode adjustment. The tuning pins have 1KOhm terminations to

vcc and allow the user to change the slicing level before the data is sampled by the recovered clock.

Tuning voltages from vcc to vee deliver 150mV of DC voltage shift.

Also included in Data IB is an input signal peak detector that delivers its response through the output

differential signal pkdtp/pkdetn. The detector can demodulate AM component(s) carried by the input

data with frequency ranges of up to a few hundred KHz. The detector’s output impedance is 4KOhm

single ended to vcc.

HS CIB

The High-Speed Clock Input Buffer (HS CIB) can process either differential or single-ended external

CML clock signals cep/cen. In single-ended mode, the clock is applied to one of the pins together with a

threshold voltage applied to the unused pin. The buffer utilizes on-chip single-ended termination of

50Ohm to vcc for each input line.

CLK IB

The Clock Input Buffer (CLK IB) consists of a proprietary universal input buffer (UIB) that exceeds

LVDS standards IEEE Std. 1596.3-1996 and ANSI/TIA/EIA-644-1995. UIB is designed to accept

differential signals with a speed up to 1Gb/s, DC common mode voltage variation between vcc and vee,

Rev. 1.1.2

3

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

AC common mode noise with a frequency up to 5MHz, and voltage levels ranging from 0 to 2.4V. It can

also receive a DC-terminated single-ended signal with a threshold voltage between vcc and vee applied

to the unused pin. The input termination impedance is set to 100Ohm differential.

CDR

The Clock and Data Recovery Block (CDR) contains both a phase and frequency acquisition loop. The

frequency loop works in concert with low-speed clock c32p/c32n while the phase loop utilizes data

signal dp/dn. The CDR requires a single off-chip filter shown in Fig. 2 to be connected to pin ftr.

66Ohm

ftr

390pF

22nF

Fig. 2. External Loop Filter

The main function of the CDR is to frequency-lock the selected on-chip VCO to the input data signal

(clock recovery) while phase-aligning it to latch in the incoming data with minimal error (data recovery).

By default, the CDR aligns the recovered clock’s working edge in the middle of the incoming data bits. A

DC voltage from vee to vcc applied to pin phshft can be utilized to shift this position from one edge of

the data bit to the other in order to locate the optimum sampling point which provides the lowest system

BER. The recovered clock is divided down in frequency by two (C2) and utilized by DMX 1:2 for

demultiplexation of the recovered data.

By utilizing the 2.5V CMOS control pins vcos0 and vcos1, the desired working frequency of the CDR

can be selected in accordance with Table 1 below.

Table 1. CDR Mode Selection (Case Temperature from 0 to 90°C)

vcos0

vcos1

VCO Operation Frequency (GHz)

“0” (0V)

“0” (0V)

fmin≤25.2, fmax≥27.4

“0” (0V) ”1” (2.5V)

fmin≤26.3, fmax≥30.0

”1” (2.5V) “0” (0V)

fmin≤29.9, fmax≥32.5

”1” (2.5V) ”1” (2.5V)

Digital Mode, default state

The loop gain can be adjusted by two 2.5V CMOS control pins icph and icpl that control the charge pump

current as shown in Table 2.

Table 2. Charge Pump Current Control

icph

icpl

Charge Pump current, mA

“0” (0V)

“0” (0V)

Imax

“0” (0V) ”1” (2.5V)

Imax-0.04

”1” (2.5V) “0” (0V)

Imax-0.27

”1” (2.5V) ”1” (2.5V)

Imax-0.31

By utilizing the analog control pin rngcrl/is, locking frequency ranges of the three VCOs can be adjusted.

Fig. 3, Fig. 4, and Fig. 5 present locking ranges of low-frequency, middle-frequency, and high-frequency

Rev. 1.1.2

4

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

VCOs respectively. Each plot shows the dependence of minimum and maximum locking frequencies (in

GHz) on the voltage (in V above vee) of the control pin rangecrl/is.

The lock detect circuitry signals an alarm through the 2.5V CMOS signal lolp when a frequency

difference exists between an applied system reference clock c32p/c32n and a recovered full rate clock

divided-by-32 that is greater than ±1000ppm.

Fig. 3. Locking Range of Low-Frequency VCO vs. Control rngcrl/is

Fig. 4. Locking Range of Middle-Frequency VCO vs. Control rngcrl/is

Rev. 1.1.2

5

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

Fig. 5. Locking Range of High-Frequency VCO vs. Control rngcrl/is

Another feature included in the CDR is the ability to simultaneously invert the polarity of all three data

outputs through the 2.5V CMOS input pin pol (pol = “1” (default): direct; pol = “0”: inverted). The order

of the half-rate output data streams can be inverted by using the 2.5V CMOS input pin tog, which

provides means to synchronize two adjacent DMUXes operating in parallel. The synchronization process

may be accomplished by the “blind” toggling in one of the chips and leaving the task of recognizing the

“right” position to downstream components (e.g. FEC chip).

DMX1:2

The 1 to 2 Demultiplexer (DMX1:2) latches in the retimed data stream D from the CDR on both edges of

the half rate clock signal C2. The high speed data signal is subsequently demultiplexed into two half rate

NRZ data signals and delivered to D2OBx2 in parallel fashion as a 2-bit wide word with the order defined

by the tog signal.

DOB

The Data Output Buffer (DOB) receives a full rate retimed serial data stream D from the CDR and

converts it into a CML output signal dop/don. This CML buffer requires 50Ohm external termination

resistors connected between vcc and each output. The buffer can be enabled or disabled by the external

2.5V CMOS control signal ondo (ondo = “1” (default): enabled; ondo = “0”: disabled).

D2OBx2

The Half Rate Data Output Buffer (D2OBx2) receives two half rate data signals from DMX1:2 and

converts them into CML output signals q0p/q0n and q1p/q1n. The buffer requires 50Ohm external

termination resistors connected between vcc and each output. The buffer can be enabled or disabled by

the external 2.5V CMOS control signal ond2o (ond2o = “1” (default): enabled; ond2o = “0”: disabled).

Rev. 1.1.2

6

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

COB

The Clock Output Buffer (COB) receives a half rate clock signal from DMX1:2 and converts it into CML

output signal c2p/c2n. The buffer requires 50Ohm external termination resistors connected between vcc

and each output. The buffer can be enabled or disabled by the external 2.5V CMOS control signal onco

(onco = “1” (default): enabled; onco = “0”: disabled). The negative edge of the c2 signal is aligned to the

half rate output data crossing points.

POWER SUPPLY CONFIGURATION

The ASNT2110C-KMF can operate with either a negative supply (vcc = 0.0V = ground and vee = -3.3V),

or a positive supply (vcc = +3.3V and vee = 0.0V = ground). In case of a positive supply, all I/Os need

AC termination when connected to any devices with 50Ohm termination to ground. Different PCB layouts

will be needed for each different power supply combination.

All the characteristics detailed below assume vcc = 3.3V and vee = 0V (external

ground)

ABSOLUTE MAXIMUM RATINGS

Caution: Exceeding the absolute maximum ratings shown in Table 3 may cause damage to this product

and/or lead to reduced reliability. Functional performance is specified over the recommended operating

conditions for power supply and temperature only that are specified in ELECTRICAL

CHARACTERISTICS. AC and DC device characteristics at or beyond the absolute maximum ratings are

not assumed or implied. All min and max voltage limits are referenced to ground (assumed vee).

Table 3. Absolute Maximum Ratings

Parameter

Supply Voltage (vcc)

Power Consumption

Input Voltage Swing (SE)

Case Temperature*)

Storage Temperature

Operational Humidity

Storage Humidity

*) - Operating the part at temperatures over

Min

-40

10

10

Max

+3.8

1.6

1.0

+90

+100

98

98

Units

V

W

V

ºC

ºC

%

%

this value could/will damage the part. Operating at this

temperature or any temperatures above the recommended maximum value specified in ELECTRICAL

CHARACTERISTICS does not guarantee correct functionality as is stated above.

TERMINAL FUNCTIONS

Name

vcc

vee

Rev. 1.1.2

Supply and Termination Voltages

Description

Pin Number

Positive power supply (+3.3V)

2, 4, 6, 11, 13, 15, 18, 20, 22, 27, 29, 31, 34, 36,

38, 43, 45, 47, 54, 55, 57, 59, 60

Negative power supply (GND or 0V)

1, 16, 17, 32, 33, 48, 49, 50, 63, 64

7

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

TERMINAL

Name

No.

Type

High-Speed I/Os

CML differential full rate clock inputs with internal SE 50Ohm

termination to vcc

CML differential half rate data outputs. Require external SE 50Ohm

termination to vcc

cep

cen

q1p

q1n

q0p

q0n

c2p

c2n

dop

don

dp

dn

3

5

21

19

30

28

37

35

46

44

56

58

c32p

c32n

pkdtp

pkdtn

12

14

51

52

vcos1

vcos0

icpl

icph

ond2o

Controls

7

LS In.,

CDR operational mode selection, see Table 1

10 2.5V CMOS

23

Charge pump current control, see Table 2

24

26

D2OBx2 control (high, default: buffer is on; low: buffer is disabled)

onco

39

COB control (high, default: buffer is on; low: buffer is disabled)

tog

pol

ondo

lolp

40

41

42

25

Order inversion of output data signals (default: high)

Data output signal polarity (high, default: inverted data outputs)

DOB control (high, default: buffer is on; low: buffer is disabled)

CDR lock indicator (high: no lock; low: locked)

dcinp

dcinn

phshft

rngcrl/is

ftr

Rev. 1.1.2

Input

DESCRIPTION

Output

Output

Output

Input

Input

Output

CML differential half rate clock outputs. Require external SE 50Ohm

termination to vcc

CML differential full rate data outputs. Require external SE 50Ohm

termination to vcc

CML differential data inputs with internal SE 50Ohm termination to

vcc

Low-Speed I/Os

LVDS clock input with internal differential 100Ohm termination

Peak detector outputs

LS out,

2.5V CMOS

53

LS IN

Input data common mode voltage adjustment

61

62

LS IN

CDR sampling point adjustment

9

LS IN

VCO frequency range adjustment control with internal 107kOhm

termination to vcc and 213kOhm termination to vee

8

I/O

External CDR filter connection

8

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

ELECTRICAL CHARACTERISTICS

PARAMETER

TYP MAX

UNIT

COMMENTS

General Parameters

+3.0

+3.3

+3.6

V

±9%

vcc

0.0

V

vee

Ivcc

490

mA

All functions active

Power Consumption

1.6

W

Junction Temperature

-25

50

125

°C

Case temperature

75

°C

Recommended value

HS Input Data (dp/dn)

DC

34

Gbps

Digital mode

Data Rate

25.2

32.5

Gbps

CDR mode

Swing p-p (Diff or SE)

0.05

0.6

V

at 34Gbps

CM Voltage Level

vcc-0.8

vcc

V

LS Input Reference Clock (c32p/c32n)

Frequency

787.5

1015.625

MHz

Swing p-p (Diff or SE)

0.06

0.8

V

CM Voltage Level

V

vee

vcc

Duty Cycle

40

50

60

%

HS Output Full Rate Data (dop/don)

DC

34

Gbps

Digital mode

Data Rate

25.2

32.5

Gbps

CDR mode

Logic “1” level

V

vcc

Logic “0” level

vcc -0.4 vcc -0.3

V

Jitter

7

8

ps

HS Output Half Rate Data (q0p/q0n, q1p/q1n)

DC

17

Gbps

NRZ, Digital mode

Data Rate

12.6

16.25

Gbps

NRZ, CDR mode

Logic “1” level

V

vcc

Logic “0” level

vcc -0.4

V

Jitter

7

ps

HS Output Half Rate Clock (c2p/c2n)

DC

17.0

GHz

Digital mode

Clock Rate

12.6

16.25

GHz

CDR mode

Logic “1” level

V

vcc

Logic “0” level

vcc -0.4

vcc -0.15

V

Jitter

5

8

ps

Input Data Common Mode Control (dcinp/dcinn)

Input DC Voltage

V

vee

vcc

Input Data Voltage Shift

0

-150

mV

Referenced to vcc

Output of Peak Detector (pkdtp/pkdtn)

Swing p-p (Diff)

-1

1

V

Over full input range

CM Voltage Level

vcc -1.0

V

Data Sampling Point Adjustment (phshft)

Rev. 1.1.2

MIN

9

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

PARAMETER

Input DC Voltage

Phase Shift

Shift Stability

Bandwidth

Control voltage level

Logic “1” level

Logic “0” level

MIN

TYP MAX

UNIT

vcc -1.0

NC

vcc

V

-15

0

+15

ps

-2

2

ps

0.0

100

MHz

Locking Range Control (rangecrl/is)

vee + 0.7

vee + 1.7

V

CMOS Control Inputs/Outputs

2.1

2.5

V

vee +0.4

V

Timing Parameters

c2p/c2n to q0p/q0n &

q1p/q1n delay variation

2

ps

COMMENTS

NC=Not Connected

From 0°C to 125°C

Do not exceed vee+2.5V

Over the full

temperature range

PACKAGE INFORMATION

The chip die is housed in a custom 64-pin CQFP package. The dimensioned drawings are shown in Fig. 6.

The package’s leads will be trimmed to a length of 1.0mm. After trimming, the package’s leads will be

further processed as follows:

1. The lead’s gold plating will be removed per the following sections of J-STD-001D:

3.9.1 Solderability

3.2.2 Solder Purity Maintenance

3.9.2 Solderability Maintenance

3.9.3 Gold Removal

2. The leads will be tinned with Sn63Pb37 solder

The package provides a center heat slug located on its back side to be used for heat dissipation.

ADSANTEC recommends for this section to be soldered to the vcc plain, which is ground for a negative

supply, or power for a positive supply.

The part’s identification label is ASNT2110C-KMF. The first 9 characters of the name before the dash

identify the bare die including general circuit family, fabrication technology, specific circuit type, and part

version while the 3 characters after the dash represent the package’s manufacturer, type, and pin out

count.

This device complies with Commission Delegated Directive (EU) 2015/863 of 4 June 2015 amending

Annex II to Directive 2011/65/EU of the European Parliament and of the Council as regards the list of

restricted substances (Text with EEA relevance) on the restriction of the use of certain hazardous

substances in electrical and electronics equipment (RoHS Directive) in accordance with the definitions set

forth in the directives for all ten substances.

Rev. 1.1.2

10

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

Fig. 6. CQFP 64-Pin Package Drawing (All Dimensions in mm)

Rev. 1.1.2

11

February 2021

�Advanced Science And Novel Technology Company, Inc.

2790 Skypark Drive Suite 112, Torrance, CA 90505

Offices: 310-530-9400 / Fax: 310-530-9402

www.adsantec.com

REVISION HISTORY

Revision

1.1.2

Date

02-2021

1.0.2

10-2020

0.2.2

04-2020

0.1.2

0.0.2

04-2020

04-2020

Rev. 1.1.2

Changes

Corrected the description of the control rangecrl/is in the CDR

section

Corrected Terminal Functions table

Corrected Electrical Characteristics table

Corrected Power Supply Configuration section

Corrected frequency range

Corrected short description (bullets)

Corrected filter schematic

Corrected Electrical Characteristics table

Corrected main features

Corrected VCO upper frequency limit

Corrected Electrical Characteristics

Corrected data rate and clock frequency

Preliminary release

12

February 2021

�