Dat

asheet

Rochest

erEl

ect

r

oni

cs

Manuf

act

ur

edComponent

s

Rochest

er br

anded component

s ar

e

manuf

act

ur

ed usi

ng ei

t

herdi

e/

waf

er

s

pur

chased f

r

om t

he or

i

gi

nalsuppl

i

er

s

or Rochest

er waf

er

sr

ecr

eat

ed f

r

om

t

he or

i

gi

nal I

P. Al

lr

ecr

eat

i

ons ar

e

donewi

t

ht

heappr

ovaloft

heOCM.

Par

t

sar

et

est

ed usi

ngor

i

gi

nalf

act

or

y

t

estpr

ogr

amsorRochest

erdevel

oped

t

est sol

ut

i

ons t

o guar

ant

ee pr

oduct

meet

sorexceedt

heOCM dat

asheet

.

Qual

i

t

yOver

vi

ew

•I

SO9001

• AS9120cer

t

icat

i

on

• Qual

iedManuf

act

ur

er

sLi

st(

QML)MI

LPRF35835

•Cl

assQ Mi

l

i

t

ar

y

•Cl

assVSpaceLevel

• Qual

iedSuppl

i

er

sLi

stofDi

st

r

i

but

or

s(

QSLD)

•Rochest

eri

sacr

i

t

i

calsuppl

i

ert

oDLA and

meet

sal

li

ndust

r

yandDLA st

andar

ds.

Rochest

erEl

ect

r

oni

cs,LLC i

scommi

t

t

edt

o

suppl

yi

ngpr

oduct

st

hatsat

i

sf

ycust

omerexpect

at

i

onsf

orqual

i

t

yandar

eequalt

ot

hoseor

i

gi

nal

l

y

suppl

i

edbyi

ndust

r

ymanuf

act

ur

er

s.

Theor

i

gi

nalmanuf

act

ur

er

’

sdat

asheetaccompanyi

ngt

hi

sdocumentr

e ect

st

heper

f

or

mance

andspecicat

i

onsoft

heRochest

ermanuf

act

ur

edver

si

onoft

hi

sdevi

ce.Rochest

erEl

ect

r

oni

csguar

ant

eest

heper

f

or

manceofi

t

ssemi

conduct

orpr

oduct

st

ot

heor

i

gi

nalOEM specicat

i

ons.‘

Typi

cal

’val

uesar

ef

orr

ef

er

encepur

posesonl

y.Cer

t

ai

nmi

ni

mum ormaxi

mum r

at

i

ngs

maybebasedonpr

oductchar

act

er

i

zat

i

on,desi

gn,si

mul

at

i

on,orsampl

et

est

i

ng.

© 2013Roc

hes

t

erEl

ec

t

r

oni

c

s

,LLC.Al

lRi

ght

sRes

er

v

ed07112013

Tol

ear

nmor

e,pl

eas

ev

i

s

i

twww.

r

oc

el

ec

.

c

om

�MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

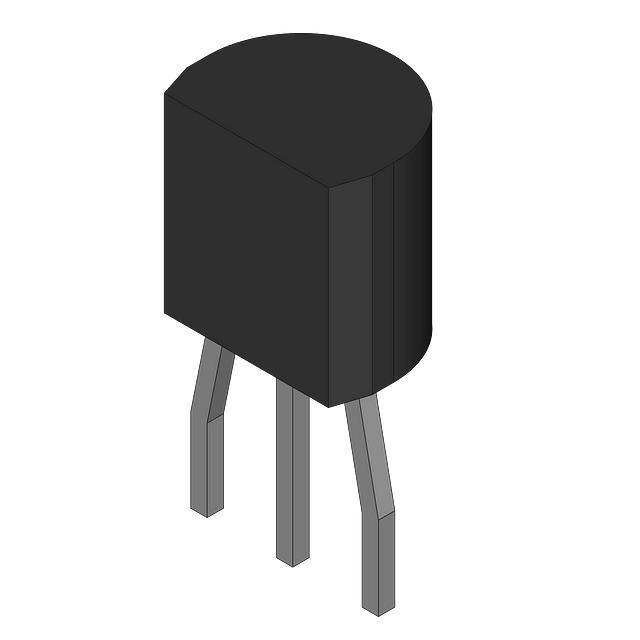

General Purpose Transistors

2N4123

2N4124

NPN Silicon

COLLECTOR

3

2

BASE

1

EMITTER

1

2

3

MAXIMUM RATINGS

Rating

Symbol

2N4123

2N4124

Unit

Collector – Emitter Voltage

VCEO

30

25

Vdc

Collector – Base Voltage

VCBO

40

30

Vdc

Emitter – Base Voltage

VEBO

5.0

Vdc

Collector Current — Continuous

IC

200

mAdc

Total Device Dissipation @ TA = 25°C

Derate above 25°C

PD

625

5.0

mW

mW/°C

Total Device Dissipation @ TC = 25°C

Derate above 25°C

PD

1.5

12

Watts

mW/°C

TJ, Tstg

– 55 to +150

°C

Symbol

Max

Unit

Operating and Storage Junction

Temperature Range

CASE 29–04, STYLE 1

TO–92 (TO–226AA)

THERMAL CHARACTERISTICS

Characteristic

Thermal Resistance, Junction to Ambient

RqJA

200

°C/W

Thermal Resistance, Junction to Case

RqJC

83.3

°C/W

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted)

Symbol

Min

Max

30

25

—

—

40

30

—

—

V(BR)EBO

5.0

—

Vdc

Collector Cutoff Current

(VCB = 20 Vdc, IE = 0)

ICBO

—

50

nAdc

Emitter Cutoff Current

(VEB = 3.0 Vdc, IC = 0)

IEBO

—

50

nAdc

Characteristic

Unit

OFF CHARACTERISTICS

Collector – Emitter Breakdown Voltage(1)

(IC = 1.0 mAdc, IE = 0)

Collector – Base Breakdown Voltage

(IC = 10 mAdc, IE = 0)

Emitter – Base Breakdown Voltage

(IE = 10 mAdc, IC = 0)

V(BR)CEO

2N4123

2N4124

Vdc

V(BR)CBO

2N4123

2N4124

Vdc

1. Pulse Test: Pulse Width = 300 ms, Duty Cycle = 2.0%.

2–14

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�2N4123 2N4124

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted) (Continued)

Characteristic

Symbol

Min

Max

2N4123

2N4124

50

120

150

360

2N4123

2N4124

25

60

—

—

Unit

ON CHARACTERISTICS

DC Current Gain(1)

(IC = 2.0 mAdc, VCE = 1.0 Vdc)

hFE

(IC = 50 mAdc, VCE = 1.0 Vdc)

—

Collector – Emitter Saturation Voltage(1)

(IC = 50 mAdc, IB = 5.0 mAdc)

VCE(sat)

—

0.3

Vdc

Base – Emitter Saturation Voltage(1)

(IC = 50 mAdc, IB = 5.0 mAdc)

VBE(sat)

—

0.95

Vdc

250

300

—

—

SMALL– SIGNAL CHARACTERISTICS

Current – Gain — Bandwidth Product

(IC = 10 mAdc, VCE = 20 Vdc, f = 100 MHz)

fT

MHz

2N4123

2N4124

Input Capacitance

(VEB = 0.5 Vdc, IC = 0, f = 1.0 MHz)

Cibo

—

8.0

pF

Collector–Base Capacitance

(IE = 0, VCB = 5.0 V, f = 1.0 MHz)

Ccb

—

4.0

pF

50

120

200

480

2N4123

2N4124

2.5

3.0

—

—

2N4123

2N4124

50

120

200

480

—

—

6.0

5.0

Small–Signal Current Gain

(IC = 2.0 mAdc, VCE = 10 Vdc, RS = 10 k ohm, f = 1.0 kHz)

Current Gain — High Frequency

(IC = 10 mAdc, VCE = 20 Vdc, f = 100 MHz)

hfe

2N4123

2N4124

—

|hfe|

(IC = 2.0 mAdc, VCE = 10 V, f = 1.0 kHz)

(IC = 2.0 mAdc, VCE = 10 V, f = 1.0 kHz)

Noise Figure

(IC = 100 µAdc, VCE = 5.0 Vdc, RS = 1.0 k ohm,

f = 1.0 kHz)

—

NF

dB

2N4123

2N4124

1. Pulse Test: Pulse Width = 300 ms, Duty Cycle = 2.0%.

200

10

100

5.0

TIME (ns)

CAPACITANCE (pF)

7.0

Cibo

3.0

ts

70

50

td

30

tf

Cobo

2.0

VCC = 3 V

IC/IB = 10

VEB(off) = 0.5 V

10.0

7.0

1.0

0.1

tr

20

0.2 0.3

0.5 0.7 1.0

2.0 3.0 5.0 7.0 10

REVERSE BIAS VOLTAGE (VOLTS)

20 30 40

Figure 1. Capacitance

Motorola Small–Signal Transistors, FETs and Diodes Device Data

5.0

1.0

2.0 3.0

5.0 7.0 10

20 30 50 70 100

IC, COLLECTOR CURRENT (mA)

200

Figure 2. Switching Times

2–15

�2N4123 2N4124

AUDIO SMALL–SIGNAL CHARACTERISTICS

NOISE FIGURE

(VCE = 5 Vdc, TA = 25°C)

Bandwidth = 1.0 Hz

12

f = 1 kHz

SOURCE RESISTANCE = 200 W

IC = 0.5 mA

8

6

SOURCE RESISTANCE = 1 kΩ

IC = 50 mA

4

2

0

0.1

SOURCE RESISTANCE = 500 W

IC = 100 mA

0.2

0.4

1

2

4

10

f, FREQUENCY (kHz)

IC = 1 mA

12

NF, NOISE FIGURE (dB)

10

NF, NOISE FIGURE (dB)

14

SOURCE RESISTANCE = 200 W

IC = 1 mA

IC = 0.5 mA

10

IC = 50 mA

8

IC = 100 mA

6

4

2

20

40

0

0.1

100

0.2

0.4

Figure 3. Frequency Variations

40

1.0 2.0

4.0

10

20

RS, SOURCE RESISTANCE (kΩ)

100

Figure 4. Source Resistance

h PARAMETERS

(VCE = 10 V, f = 1 kHz, TA = 25°C)

100

hoe, OUTPUT ADMITTANCE (m mhos)

hfe , CURRENT GAIN

300

200

100

70

50

50

20

10

5

2

1

30

0.1

0.2

0.5

1.0

2.0

IC, COLLECTOR CURRENT (mA)

5.0

10

0.1

0.2

Figure 5. Current Gain

h re , VOLTAGE FEEDBACK RATIO (X 10 –4 )

hie , INPUT IMPEDANCE (kΩ )

10

5.0

10

10

10

5.0

2.0

1.0

0.5

7.0

5.0

3.0

2.0

1.0

0.7

0.5

0.1

0.2

0.5

1.0

2.0

IC, COLLECTOR CURRENT (mA)

Figure 7. Input Impedance

2–16

5.0

Figure 6. Output Admittance

20

0.2

0.5

1.0

2.0

IC, COLLECTOR CURRENT (mA)

5.0

10

0.1

0.2

0.5

1.0

2.0

IC, COLLECTOR CURRENT (mA)

Figure 8. Voltage Feedback Ratio

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�2N4123 2N4124

STATIC CHARACTERISTICS

h FE, DC CURRENT GAIN (NORMALIZED)

2.0

TJ = +125°C

1.0

VCE = 1 V

+25°C

0.7

– 55°C

0.5

0.3

0.2

0.1

0.1

0.2

0.3

0.5

0.7

1.0

2.0

3.0

5.0 7.0 10

IC, COLLECTOR CURRENT (mA)

20

30

50

70

100

200

VCE, COLLECTOR EMITTER VOLTAGE (VOLTS)

Figure 9. DC Current Gain

1.0

TJ = 25°C

0.8

IC = 1 mA

10 mA

30 mA

100 mA

0.6

0.4

0.2

0

0.01

0.02

0.03

0.05

0.07

0.1

0.2

0.3

0.5

IB, BASE CURRENT (mA)

0.7

1.0

2.0

3.0

5.0

7.0

10

Figure 10. Collector Saturation Region

θV, TEMPERATURE COEFFICIENTS (mV/°C)

1.2

TJ = 25°C

VBE(sat) @ IC/IB = 10

V, VOLTAGE (VOLTS)

1.0

0.8

VBE @ VCE = 1 V

0.6

0.4

VCE(sat) @ IC/IB = 10

0.2

0

1.0

2.0

50

5.0

10

20

IC, COLLECTOR CURRENT (mA)

100

200

Figure 11. “On” Voltages

Motorola Small–Signal Transistors, FETs and Diodes Device Data

1.0

0.5

+25°C to +125°C

qVC for VCE(sat)

0

– 55°C to +25°C

– 0.5

– 55°C to +25°C

– 1.0

+25°C to +125°C

qVB for VBE(sat)

– 1.5

– 2.0

0

20

40

60

80 100 120 140 160

IC, COLLECTOR CURRENT (mA)

180 200

Figure 12. Temperature Coefficients

2–17

�EMBOSSED TAPE AND REEL

SOT-23, SC-59, SC-70/SOT-323, SC–90/SOT–416, SOT-223 and SO-16 packages are available only in

Tape and Reel. Use the appropriate suffix indicated below to order any of the SOT-23, SC-59,

SC-70/SOT-323, SOT-223 and SO-16 packages. (See Section 6 on Packaging for additional information).

SOT-23:

available in 8 mm Tape and Reel

Use the device title (which already includes the “T1” suffix) to order the 7 inch/3000 unit reel.

Replace the “T1” suffix in the device title with a “T3” suffix to order the 13 inch/10,000 unit reel.

SC-59:

available in 8 mm Tape and Reel

Use the device title (which already includes the “T1” suffix) to order the 7 inch/3000 unit reel.

Replace the “T1” suffix in the device title with a “T3” suffix to order the 13 inch/10,000 unit reel.

SC-70/

SOT-323:

available in 8 mm Tape and Reel

Use the device title (which already includes the “T1” suffix) to order the 7 inch/3000 unit reel.

Replace the “T1” suffix in the device title with a “T3” suffix to order the 13 inch/10,000 unit reel.

SOT-223:

available in 12 mm Tape and Reel

Use the device title (which already includes the “T1” suffix) to order the 7 inch/1000 unit reel.

Replace the “T1” suffix in the device title with a “T3” suffix to order the 13 inch/4000 unit reel.

SO-16:

available in 16 mm Tape and Reel

Add an “R1” suffix to the device title to order the 7 inch/500 unit reel.

Add an “R2” suffix to the device title to order the 13 inch/2500 unit reel.

RADIAL TAPE IN FAN FOLD BOX OR REEL

TO-92 packages are available in both bulk shipments and in Radial Tape in Fan Fold Boxes or Reels.

Fan Fold Boxes and Radial Tape Reel are the best methods for capturing devices for automatic insertion in

printed circuit boards.

TO-92:

available in Fan Fold Box

Add an “RLR” suffix and the appropriate Style code* to the device title to order the Fan Fold box.

available in 365 mm Radial Tape Reel

Add an “RLR” suffix and the appropriate Style code* to the device title to order the Radial Tape

Reel.

*Refer to Section 6 on Packaging for Style code characters and additional information on ordering

*requirements.

DEVICE MARKINGS/DATE CODE CHARACTERS

SOT-23, SC-59, SC-70/SOT-323, and the SC–90/SOT–416 packages have a device marking and a date

code etched on the device. The generic example below depicts both the device marking and a representation of the date code that appears on the SC-70/SOT-323, SC-59 and SOT-23 packages.

ABC D

The “D” represents a smaller alpha digit Date Code. The Date Code indicates the actual month in which the

part was manufactured.

2–2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�Tape and Reel Specifications

and Packaging Specifications

Embossed Tape and Reel is used to facilitate automatic pick and place equipment feed requirements. The tape is used as the

shipping container for various products and requires a minimum of handling. The antistatic/conductive tape provides a secure

cavity for the product when sealed with the “peel–back” cover tape.

•

•

•

•

• SOD–123, SC–59, SC–70/SOT–323, SC–70ML/SOT–363,

SOT–23, TSOP–6, in 8 mm Tape

• SOT–223 in 12 mm Tape

• SO–14, SO–16 in 16 mm Tape

Two Reel Sizes Available (7″ and 13″)

Used for Automatic Pick and Place Feed Systems

Minimizes Product Handling

EIA 481, –1, –2

Use the standard device title and add the required suffix as listed in the option table on the following page. Note that the individual

reels have a finite number of devices depending on the type of product contained in the tape. Also note the minimum lot size is

one full reel for each line item, and orders are required to be in increments of the single reel quantity.

SOD–123

SC–59, SC–70/SOT–323, SOT–23

8 mm

8 mm

SOT–223

SC–70ML/SOT–363, TSOP–6

T1 ORIENTATION

8 mm

SO–14, 16

12 mm

16 mm

SC–70ML/SOT–363

T2 ORIENTATION

DIRECTION

8 mm

OF FEED

EMBOSSED TAPE AND REEL ORDERING INFORMATION

Devices Per Reel

and Minimum

Order Quantity

Device

Suffix

(7)

3,000

T1

178

330

(7)

(13)

3,000

10,000

T1

T3

8.0 ± 0.1 (.315 ± .004)

178

330

(7)

(13)

500

2,500

R1

R2

16

16

8.0 ± 0.1 (.315 ± .004)

178

330

(7)

(13)

500

2,500

R1

R2

SOD–123

8

8

4.0 ± 0.1 (.157 ± .004)

178

330

(7)

(13)

3,000

10,000

T1

T3

SOT–23

8

8

4.0 ± 0.1 (.157 ± .004)

178

330

(7)

(13)

3,000

10,000

T1

T3

SOT–223

12

12

8.0 ± 0.1 (.315 ± .004)

178

330

(7)

(13)

1,000

4,000

T1

T3

SC–70ML/SOT–363

8

8

4.0 ± 0.1 (.157 ± .004)

178

178

(7)

(7)

3,000

3,000

T1

T2

TSOP–6

8

4.0 ± 0.1 (.157 ± .004)

178

(7)

3,000

T1

Package

Tape Width

(mm)

Pitch

mm

(inch)

SC–59

8

4.0 ± 0.1 (.157 ± .004)

178

SC–70/SOT–323

8

8

4.0 ± 0.1 (.157 ± .004)

SO–14

16

16

SO–16

Tape and Reel Specifications

6–2

Reel Size

mm

(inch)

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�EMBOSSED TAPE AND REEL DATA FOR DISCRETES

CARRIER TAPE SPECIFICATIONS

P0

K

P2

D

t

10 Pitches Cumulative Tolerance on Tape

± 0.2 mm

(± 0.008″)

E

Top Cover

Tape

A0

K0

B1

F

W

B0

See

Note 1

P

For Machine Reference Only

Including Draft and RADII

Concentric Around B0

D1

For Components

2.0 mm x 1.2 mm and Larger

Center Lines

of Cavity

Embossment

User Direction of Feed

* Top Cover Tape

Thickness (t1)

0.10 mm

(.004″) Max.

Bar Code Label

R Min

Tape and Components

Shall Pass Around Radius “R”

Without Damage

Bending Radius

10°

Embossed Carrier

100 mm

(3.937″)

Maximum Component Rotation

Embossment

1 mm Max

Typical Component

Cavity Center Line

Tape

1 mm

(.039″) Max

Typical Component

Center Line

250 mm

(9.843″)

Camber (Top View)

Allowable Camber To Be 1 mm/100 mm Nonaccumulative Over 250 mm

DIMENSIONS

Tape

Size

B1 Max

D

D1

E

F

K

P0

P2

R Min

T Max

W Max

8 mm

4.55 mm

(.179″)

1.0 Min

(.039″)

1.75 ± 0.1 mm

(.069 ± .004″)

3.5 ± 0.05 mm

(.138 ± .002″)

2.4 mm Max

(.094″)

4.0 ± 0.1 mm

(.157 ± .004″)

2.0 ± 0.1 mm

(.079 ± .002″)

25 mm

(.98″)

0.6 mm

(.024″)

8.3 mm

(.327″)

12 mm

8.2 mm

(.323″)

1.5 + 0.1 mm

– 0.0

( 0 9 + .004″

004

(.059

– 0.0)

5.5 ± 0.05 mm

(.217 ± .002″)

6.4 mm Max

(.252″)

16 mm

12.1 mm

(.476″)

7.5 ± 0.10 mm

(.295 ± .004″)

7.9 mm Max

(.311″)

16.3 mm

(.642″)

24 mm

20.1 mm

(.791″)

11.5 ± 0.1 mm

(.453 ± .004″)

11.9 mm Max

(.468″)

24.3 mm

(.957″)

1.5 mm Min

(.060″)

30 mm

(1.18″)

12 ± .30 mm

(.470 ± .012″)

Metric dimensions govern — English are in parentheses for reference only.

NOTE 1: A0, B0, and K0 are determined by component size. The clearance between the components and the cavity must be within .05 mm min. to .50 mm max.,

NOTE 1: the component cannot rotate more than 10° within the determined cavity.

NOTE 2: If B1 exceeds 4.2 mm (.165) for 8 mm embossed tape, the tape may not feed through all tape feeders.

NOTE 3: Pitch information is contained in the Embossed Tape and Reel Ordering Information on pg. 5.12–3.

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Tape and Reel Specifications

6–3

�EMBOSSED TAPE AND REEL DATA FOR DISCRETES

T Max

Outside Dimension

Measured at Edge

1.5 mm Min

(.06″)

A

13.0 mm ± 0.5 mm

(.512″ ± .002″)

20.2 mm Min

(.795″)

50 mm Min

(1.969″)

Full Radius

G

Size

A Max

8 mm

330 mm

(12.992″)

8.4 mm + 1.5 mm, – 0.0

(.33″ + .059″, – 0.00)

14.4 mm

(.56″)

12 mm

330 mm

(12.992″)

12.4 mm + 2.0 mm, – 0.0

(.49″ + .079″, – 0.00)

18.4 mm

(.72″)

16 mm

360 mm

(14.173″)

16.4 mm + 2.0 mm, – 0.0

(.646″ + .078″, – 0.00)

22.4 mm

(.882″)

24 mm

360 mm

(14.173″)

24.4 mm + 2.0 mm, – 0.0

(.961″ + .070″, – 0.00)

30.4 mm

(1.197″)

G

Inside Dimension

Measured Near Hub

T Max

Reel Dimensions

Metric Dimensions Govern — English are in parentheses for reference only

Tape and Reel Specifications

6–4

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�TO–92 EIA, IEC, EIAJ

Radial Tape in Fan Fold

Box or On Reel

TO–92

RADIAL

TAPE IN

FAN FOLD

BOX OR

ON REEL

Radial tape in fan fold box or on reel of the reliable TO–92 package are

the best methods of capturing devices for automatic insertion in printed

circuit boards. These methods of taping are compatible with various

equipment for active and passive component insertion.

•

•

•

•

•

•

Available in Fan Fold Box

Available on 365 mm Reels

Accommodates All Standard Inserters

Allows Flexible Circuit Board Layout

2.5 mm Pin Spacing for Soldering

EIA–468, IEC 286–2, EIAJ RC1008B

Ordering Notes:

When ordering radial tape in fan fold box or on reel, specify the style per

Figures 3 through 8. Add the suffix “RLR” and “Style” to the device title, i.e.

MPS3904RLRA. This will be a standard MPS3904 radial taped and

supplied on a reel per Figure 9.

Fan Fold Box Information — Order in increments of 2000.

Reel Information — Order in increments of 2000.

US/European Suffix Conversions

US

EUROPE

RLRA

RL

RLRE

RL1

RLRM

ZL1

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Packaging Specifications

6–5

�TO–92 EIA RADIAL TAPE IN FAN FOLD BOX OR ON REEL

H2A

H2A

H2B

H2B

H

W2

H4 H5

T1

L1

H1

W1 W

L

T

T2

F1

F2

P2

P2

P1

D

P

Figure 1. Device Positioning on Tape

Specification

Inches

Symbol

Item

Millimeter

Min

Max

Min

Max

D

Tape Feedhole Diameter

0.1496

0.1653

3.8

4.2

D2

Component Lead Thickness Dimension

0.015

0.020

0.38

0.51

Component Lead Pitch

0.0945

0.110

2.4

2.8

.059

.156

1.5

4.0

0.3346

0.3741

8.5

9.5

Deflection Left or Right

0

0.039

0

1.0

Deflection Front or Rear

0

0.051

0

1.0

Feedhole to Bottom of Component

0.7086

0.768

18

19.5

Feedhole to Seating Plane

0.610

0.649

15.5

16.5

F1, F2

H

H1

H2A

H2B

H4

H5

L

Bottom of Component to Seating Plane

Feedhole Location

Defective Unit Clipped Dimension

0.3346

0.433

8.5

11

L1

Lead Wire Enclosure

0.09842

—

2.5

—

P

Feedhole Pitch

0.4921

0.5079

12.5

12.9

P1

Feedhole Center to Center Lead

0.2342

0.2658

5.95

6.75

P2

First Lead Spacing Dimension

0.1397

0.1556

3.55

3.95

0.06

0.08

0.15

0.20

T

Adhesive Tape Thickness

T1

Overall Taped Package Thickness

—

0.0567

—

1.44

T2

Carrier Strip Thickness

0.014

0.027

0.35

0.65

W

Carrier Strip Width

0.6889

0.7481

17.5

19

W1

Adhesive Tape Width

0.2165

0.2841

5.5

6.3

W2

Adhesive Tape Position

.0059

0.01968

.15

0.5

NOTES:

1. Maximum alignment deviation between leads not to be greater than 0.2 mm.

2. Defective components shall be clipped from the carrier tape such that the remaining protrusion (L) does not exceed a maximum of 11 mm.

3. Component lead to tape adhesion must meet the pull test requirements established in Figures 5, 6 and 7.

4. Maximum non–cumulative variation between tape feed holes shall not exceed 1 mm in 20 pitches.

5. Holddown tape not to extend beyond the edge(s) of carrier tape and there shall be no exposure of adhesive.

6. No more than 1 consecutive missing component is permitted.

7. A tape trailer and leader, having at least three feed holes is required before the first and after the last component.

8. Splices will not interfere with the sprocket feed holes.

Packaging Specifications

6–6

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�TO–92 EIA RADIAL TAPE IN FAN FOLD BOX OR ON REEL

FAN FOLD BOX STYLES

ÇÇÇÇÇÇÇ

ÇÇÇÇÇÇÇ

ÇÇÇÇÇÇÇ

ÇÇÇÇÇÇÇ

ADHESIVE TAPE ON

TOP SIDE

FLAT SIDE

ADHESIVE TAPE ON

TOP SIDE

ROUNDED SIDE

CARRIER

STRIP

CARRIER

STRIP

Figure 2. Style M

252 mm

9.92”

FLAT SIDE OF TRANSISTOR

AND ADHESIVE TAPE VISIBLE.

Style M fan fold box is equivalent to styles E and F of

reel pack dependent on feed orientation from box.

330 mm

13”

MAX

ROUNDED SIDE OF TRANSISTOR AND

ADHESIVE TAPE VISIBLE.

Style P fan fold box is equivalent to styles A and B of

reel pack dependent on feed orientation from box.

Figure 3. Style P

MAX

58 mm

2.28”

MAX

Figure 4. Fan Fold Box Dimensions

ADHESION PULL TESTS

500 GRAM PULL FORCE

70 GRAM

PULL FORCE

100 GRAM

PULL FORCE

16 mm

16 mm

HOLDING

FIXTURE

The component shall not pull free with a 300 gram

load applied to the leads for 3 ± 1 second.

Figure 5. Test #1

HOLDING

FIXTURE

The component shall not pull free with a 70 gram

load applied to the leads for 3 ± 1 second.

Figure 6. Test #2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

HOLDING

FIXTURE

There shall be no deviation in the leads and

no component leads shall be pulled free of

the tape with a 500 gram load applied to the

component body for 3 ± 1 second.

Figure 7. Test #3

Packaging Specifications

6–7

�TO–92 EIA RADIAL TAPE IN FAN FOLD BOX OR ON REEL

REEL STYLES

CORE DIA.

82mm ± 1mm

ARBOR HOLE DIA.

30.5mm ± 0.25mm

MARKING NOTE

HUB RECESS

76.2mm ± 1mm

RECESS DEPTH

9.5mm MIN

365mm + 3, – 0mm

38.1mm ± 1mm

48 mm

MAX

Material used must not cause deterioration of components or degrade lead solderability

Figure 8. Reel Specifications

ADHESIVE TAPE ON REVERSE SIDE

CARRIER STRIP

CARRIER STRIP

ROUNDED

SIDE

FLAT SIDE

ADHESIVE TAPE

FEED

FEED

Rounded side of transistor and adhesive tape visible.

Flat side of transistor and carrier strip visible

(adhesive tape on reverse side).

Figure 9. Style A

Figure 10. Style B

ADHESIVE TAPE ON REVERSE SIDE

CARRIER STRIP

CARRIER STRIP

FLAT SIDE

ROUNDED

SIDE

ADHESIVE TAPE

FEED

FEED

Flat side of transistor and adhesive tape visible.

Figure 11. Style E

Packaging Specifications

6–8

Rounded side of transistor and carrier strip visible

(adhesive tape on reverse side).

Figure 12. Style F

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�INFORMATION FOR USING SURFACE MOUNT PACKAGES

RECOMMENDED FOOTPRINTS FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total

design. The footprint for the semiconductor packages must

be the correct size to ensure proper solder connection inter-

face between the board and the package. With the correct

pad geometry, the packages will self align when subjected to

a solder reflow process.

POWER DISSIPATION FOR A SURFACE MOUNT DEVICE

PD =

TJ(max) – TA

RθJA

The values for the equation are found in the maximum

ratings table on the data sheet. Substituting these values into

the equation for an ambient temperature TA of 25°C, one can

calculate the power dissipation of the device. For example,

for a SOT–223 device, PD is calculated as follows.

PD = 150°C – 25°C = 800 milliwatts

156°C/W

The 156°C/W for the SOT–223 package assumes the use

of the recommended footprint on a glass epoxy printed circuit

board to achieve a power dissipation of 800 milliwatts. There

are other alternatives to achieving higher power dissipation

from the surface mount packages. One is to increase the

area of the drain/collector pad. By increasing the area of the

drain/collector pad, the power dissipation can be increased.

Although the power dissipation can almost be doubled with

this method, area is taken up on the printed circuit board

which can defeat the purpose of using surface mount

technology. For example, a graph of RθJA versus drain pad

area is shown in Figure 1.

Another alternative would be to use a ceramic substrate or

an aluminum core board such as Thermal Clad. Using a

board material such as Thermal Clad, an aluminum core

board, the power dissipation can be doubled using the same

footprint.

RθJA , THERMAL RESISTANCE, JUNCTION

TO AMBIENT (°C/W)

The power dissipation for a surface mount device is a function of the drain/collector pad size. These can vary from the

minimum pad size for soldering to a pad size given for

maximum power dissipation. Power dissipation for a surface

mount device is determined by TJ(max), the maximum rated

junction temperature of the die, RθJA, the thermal resistance

from the device junction to ambient, and the operating

temperature, TA. Using the values provided on the data

sheet, PD can be calculated as follows:

160

140

Board Material = 0.0625″

G–10/FR–4, 2 oz Copper

TA = 25°C

0.8 Watts

120

1.25 Watts*

1.5 Watts

100

80

0.0

*Mounted on the DPAK footprint

0.2

0.4

0.6

A, AREA (SQUARE INCHES)

0.8

1.0

Figure 1. Thermal Resistance versus Drain Pad

Area for the SOT–223 Package (Typical)

SOLDER STENCIL GUIDELINES

Prior to placing surface mount components onto a printed

circuit board, solder paste must be applied to the pads.

Solder stencils are used to screen the optimum amount.

These stencils are typically 0.008 inches thick and may be

made of brass or stainless steel. For packages such as the

Surface Mount Information

7–10

SOT–23, SC–59, SC–70/SOT–323, SC–90/SOT–416,

SOD–123, SOT–223, SOT–363, SO–14, SO–16, and

TSOP–6 packages, the stencil opening should be the same

as the pad size or a 1:1 registration.

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�SOLDERING PRECAUTIONS

The melting temperature of solder is higher than the rated

temperature of the device. When the entire device is heated

to a high temperature, failure to complete soldering within a

short time could result in device failure. Therefore, the

following items should always be observed in order to minimize the thermal stress to which the devices are subjected.

• Always preheat the device.

• The delta temperature between the preheat and soldering

should be 100°C or less.*

• When preheating and soldering, the temperature of the

leads and the case must not exceed the maximum

temperature ratings as shown on the data sheet. When

using infrared heating with the reflow soldering method,

the difference should be a maximum of 10°C.

• The soldering temperature and time should not exceed

260°C for more than 10 seconds.

• When shifting from preheating to soldering, the maximum

temperature gradient shall be 5°C or less.

• After soldering has been completed, the device should be

allowed to cool naturally for at least three minutes.

Gradual cooling should be used since the use of forced

cooling will increase the temperature gradient and will

result in latent failure due to mechanical stress.

• Mechanical stress or shock should not be applied during

cooling.

* Soldering a device without preheating can cause excessive

thermal shock and stress which can result in damage to the

device.

TYPICAL SOLDER HEATING PROFILE

For any given circuit board, there will be a group of control

settings that will give the desired heat pattern. The operator

must set temperatures for several heating zones and a figure

for belt speed. Taken together, these control settings make

up a heating “profile” for that particular circuit board. On

machines controlled by a computer, the computer remembers these profiles from one operating session to the next.

Figure 2 shows a typical heating profile for use when

soldering a surface mount device to a printed circuit board.

This profile will vary among soldering systems, but it is a

good starting point. Factors that can affect the profile include

the type of soldering system in use, density and types of

components on the board, type of solder used, and the type

of board or substrate material being used. This profile shows

temperature versus time. The line on the graph shows the

STEP 1

PREHEAT

ZONE 1

“RAMP”

200°C

STEP 2 STEP 3

VENT

HEATING

“SOAK” ZONES 2 & 5

“RAMP”

DESIRED CURVE FOR HIGH

MASS ASSEMBLIES

actual temperature that might be experienced on the surface

of a test board at or near a central solder joint. The two

profiles are based on a high density and a low density board.

The Vitronics SMD310 convection/infrared reflow soldering

system was used to generate this profile. The type of solder

used was 62/36/2 Tin Lead Silver with a melting point

between 177 –189°C. When this type of furnace is used for

solder reflow work, the circuit boards and solder joints tend to

heat first. The components on the board are then heated by

conduction. The circuit board, because it has a large surface

area, absorbs the thermal energy more efficiently, then

distributes this energy to the components. Because of this

effect, the main body of a component may be up to 30

degrees cooler than the adjacent solder joints.

STEP 4

HEATING

ZONES 3 & 6

“SOAK”

STEP 5

HEATING

ZONES 4 & 7

“SPIKE”

STEP 6

VENT

STEP 7

COOLING

205° TO 219°C

PEAK AT

SOLDER JOINT

170°C

160°C

150°C

150°C

100°C

140°C

100°C

SOLDER IS LIQUID FOR

40 TO 80 SECONDS

(DEPENDING ON

MASS OF ASSEMBLY)

DESIRED CURVE FOR LOW

MASS ASSEMBLIES

50°C

TIME (3 TO 7 MINUTES TOTAL)

TMAX

Figure 2. Typical Solder Heating Profile

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Surface Mount Information

7–11

�Footprints for Soldering

0.037

0.95

0.037

0.95

0.037

0.95

0.037

0.95

0.094

2.4

0.079

2.0

0.039

1.0

0.035

0.9

inches

0.031

0.8

0.031

0.8

mm

mm

SOT–23

0.025

0.025

0.65

0.65

ÉÉÉ

ÉÉÉ

ÉÉÉ

0.075

0.5 min. (3x)

1.9

0.035

0.9

0.028

1.4

inches

0.7

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

0.5

0.5 min. (3x)

1

SC–59

inches

mm

SC–70/SOT–323

SOT 416/SC–90

0.15

3.8

0.060

1.52

0.079

2.0

0.091

2.3

0.248

6.3

0.091

2.3

0.079

2.0

0.275

7.0

0.155

4.0

0.024

0.6

0.059

1.5

0.059

1.5

0.059

1.5

0.050

1.270

inches

inches

mm

mm

SOT–223

Surface Mount Information

7–12

SO–14, SO–16

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

2.36

0.093

4.19

0.165

1.22

0.048

0.4 mm (min)

ÉÉÉÉ

ÉÉÉÉ

ÉÉÉÉ

ÉÉÉÉ

0.91

0.036

mm

inches

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

ÉÉÉ

0.65 mm 0.65 mm

0.5 mm (min)

1.9 mm

SOD–123

SOT–363

(SC–70 6 LEAD)

0.094

2.4

0.037

0.95

0.074

1.9

0.037

0.95

0.028

0.7

0.039

1.0

inches

mm

TSOP–6

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Surface Mount Information

7–13

�Package Outline Dimensions

Dimensions are in inches unless otherwise noted.

A

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. CONTOUR OF PACKAGE BEYOND DIMENSION R

IS UNCONTROLLED.

4. DIMENSION F APPLIES BETWEEN P AND L.

DIMENSION D AND J APPLY BETWEEN L AND K

MINIMUM. LEAD DIMENSION IS UNCONTROLLED

IN P AND BEYOND DIMENSION K MINIMUM.

B

R

P

L

F

SEATING

PLANE

K

DIM

A

B

C

D

F

G

H

J

K

L

N

P

R

V

D

X X

G

J

H

V

C

SECTION X–X

1

N

N

STYLE 1:

PIN 1. EMITTER

2. BASE

3. COLLECTOR

STYLE 14:

PIN 1. EMITTER

2. COLLECTOR

3. BASE

STYLE 2:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

STYLE 15:

PIN 1. ANODE 1

2. CATHODE

3. ANODE 2

STYLE 3:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 4:

PIN 1. CATHODE

2. CATHODE

3. ANODE

STYLE 17:

PIN 1. COLLECTOR

2. BASE

3. EMITTER

STYLE 21:

PIN 1. COLLECTOR

2. EMITTER

3. BASE

STYLE 5:

PIN 1. DRAIN

2. SOURCE

3. GATE

STYLE 22:

PIN 1. SOURCE

2. GATE

3. DRAIN

INCHES

MIN

MAX

0.175

0.205

0.170

0.210

0.125

0.165

0.016

0.022

0.016

0.019

0.045

0.055

0.095

0.105

0.015

0.020

0.500

–––

0.250

–––

0.080

0.105

–––

0.100

0.115

–––

0.135

–––

MILLIMETERS

MIN

MAX

4.45

5.20

4.32

5.33

3.18

4.19

0.41

0.55

0.41

0.48

1.15

1.39

2.42

2.66

0.39

0.50

12.70

–––

6.35

–––

2.04

2.66

–––

2.54

2.93

–––

3.43

–––

STYLE 7:

PIN 1. SOURCE

2. DRAIN

3. GATE

STYLE 30:

PIN 1. DRAIN

2. GATE

3. SOURCE

CASE 029–04

(TO–226AA) TO–92

PLASTIC

A

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. CONTOUR OF PACKAGE BEYOND DIMENSION R

IS UNCONTROLLED.

4. DIMENSION F APPLIES BETWEEN P AND L.

DIMENSIONS D AND J APPLY BETWEEN L AND K

MIMIMUM. LEAD DIMENSION IS UNCONTROLLED

IN P AND BEYOND DIMENSION K MINIMUM.

B

R

SEATING

PLANE

P

L

F

K

X X

DIM

A

B

C

D

F

G

H

J

K

L

N

P

R

V

D

G

H

J

V

1 2 3

N C

SECTION X–X

N

STYLE 1:

PIN 1. EMITTER

2. BASE

3. COLLECTOR

STYLE 14:

PIN 1. EMITTER

2. COLLECTOR

3. BASE

INCHES

MIN

MAX

0.175

0.205

0.290

0.310

0.125

0.165

0.018

0.022

0.016

0.019

0.045

0.055

0.095

0.105

0.018

0.024

0.500

–––

0.250

–––

0.080

0.105

–––

0.100

0.135

–––

0.135

–––

MILLIMETERS

MIN

MAX

4.44

5.21

7.37

7.87

3.18

4.19

0.46

0.56

0.41

0.48

1.15

1.39

2.42

2.66

0.46

0.61

12.70

–––

6.35

–––

2.04

2.66

–––

2.54

3.43

–––

3.43

–––

STYLE 22:

PIN 1. SOURCE

2. GATE

3. DRAIN

CASE 029–05

(TO–226AE) TO–92

1–WATT PLASTIC

Package Outline Dimensions

8–2

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�PACKAGE OUTLINE DIMENSIONS (continued)

B

NOTES:

1. PACKAGE CONTOUR OPTIONAL WITHIN DIA B

AND LENGTH A. HEAT SLUGS, IF ANY, SHALL BE

INCLUDED WITHIN THIS CYLINDER, BUT SHALL

NOT BE SUBJECT TO THE MIN LIMIT OF DIA B.

2. LEAD DIA NOT CONTROLLED IN ZONES F, TO

ALLOW FOR FLASH, LEAD FINISH BUILDUP,

AND MINOR IRREGULARITIES OTHER THAN

HEAT SLUGS.

D

K

F

A

DIM

A

B

D

F

K

F

K

MILLIMETERS

MIN

MAX

5.84

7.62

2.16

2.72

0.46

0.56

–––

1.27

25.40

38.10

INCHES

MIN

MAX

0.230

0.300

0.085

0.107

0.018

0.022

–––

0.050

1.000

1.500

All JEDEC dimensions and notes apply.

CASE 51–02

(DO–204AA)

DO–7

A

B

R

SEATING

PLANE

ÉÉ

ÉÉ

D

P

L

F

K

J

SECTION X–X

X X

D

G

H

V

1

2

C

N

N

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. CONTOUR OF PACKAGE BEYOND ZONE R IS

UNCONTROLLED.

4. DIMENSION F APPLIES BETWEEN P AND L.

DIMENSIONS D AND J APPLY BETWEEN L AND K

MINIMUM. LEAD DIMENSION IS UNCONTROLLED

IN P AND BEYOND DIM K MINIMUM.

DIM

A

B

C

D

F

G

H

J

K

L

N

P

R

V

INCHES

MIN

MAX

0.175

0.205

0.170

0.210

0.125

0.165

0.016

0.022

0.016

0.019

0.050 BSC

0.100 BSC

0.014

0.016

0.500

–––

0.250

–––

0.080

0.105

–––

0.050

0.115

–––

0.135

–––

MILLIMETERS

MIN

MAX

4.45

5.21

4.32

5.33

3.18

4.49

0.41

0.56

0.407

0.482

1.27 BSC

3.54 BSC

0.36

0.41

12.70

–––

6.35

–––

2.03

2.66

–––

1.27

2.93

–––

3.43

–––

STYLE 1:

PIN 1. ANODE

2. CATHODE

CASE 182–02

(T0–226AC) TO–92

PLASTIC

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Package Outline Dimensions

8–3

�PACKAGE OUTLINE DIMENSIONS (continued)

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. MAXIUMUM LEAD THICKNESS INCLUDES

LEAD FINISH THICKNESS. MINIMUM LEAD

THICKNESS IS THE MINIMUM THICKNESS OF

BASE MATERIAL.

A

L

3

B S

1

DIM

A

B

C

D

G

H

J

K

L

S

V

2

V

G

C

H

D

STYLE 6:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

STYLE 8:

PIN 1. ANODE

2. NO CONNECTION

3. CATHODE

STYLE 12:

PIN 1. CATHODE

2. CATHODE

3. ANODE

J

K

STYLE 10:

PIN 1. DRAIN

2. SOURCE

3. GATE

STYLE 9:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 18:

PIN 1. NO CONNECTION

2. CATHODE

3. ANODE

INCHES

MIN

MAX

0.1102 0.1197

0.0472 0.0551

0.0350 0.0440

0.0150 0.0200

0.0701 0.0807

0.0005 0.0040

0.0034 0.0070

0.0140 0.0285

0.0350 0.0401

0.0830 0.1039

0.0177 0.0236

STYLE 19:

PIN 1. CATHODE

2. ANODE

3. CATHODE–ANODE

MILLIMETERS

MIN

MAX

2.80

3.04

1.20

1.40

0.89

1.11

0.37

0.50

1.78

2.04

0.013

0.100

0.085

0.177

0.35

0.69

0.89

1.02

2.10

2.64

0.45

0.60

STYLE 11:

PIN 1. ANODE

2. CATHODE

3. CATHODE–ANODE

STYLE 21:

PIN 1. GATE

2. SOURCE

3. DRAIN

CASE 318–08

(TO–236AB) SOT–23

PLASTIC

A

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

L

3

S

2

DIM

A

B

C

D

G

H

J

K

L

S

B

1

D

G

J

C

H

STYLE 1:

PIN 1. EMITTER

2. BASE

3. COLLECTOR

MILLIMETERS

MIN

MAX

2.70

3.10

1.30

1.70

1.00

1.30

0.35

0.50

1.70

2.10

0.013

0.100

0.09

0.18

0.20

0.60

1.25

1.65

2.50

3.00

INCHES

MIN

MAX

0.1063 0.1220

0.0512 0.0669

0.0394 0.0511

0.0138 0.0196

0.0670 0.0826

0.0005 0.0040

0.0034 0.0070

0.0079 0.0236

0.0493 0.0649

0.0985 0.1181

K

STYLE 2:

PIN 1. N.C.

2. ANODE

3. CATHODE

STYLE 3:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 4:

PIN 1. N.C.

2. CATHODE

3. ANODE

STYLE 5:

PIN 1. CATHODE

2. CATHODE

3. ANODE

CASE 318D–04

SC–59

Package Outline Dimensions

8–4

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�PACKAGE OUTLINE DIMENSIONS (continued)

A

F

NOTES:

3. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

4. CONTROLLING DIMENSION: INCH.

4

S

INCHES

DIM MIN

MAX

A

0.249

0.263

B

0.130

0.145

C

0.060

0.068

D

0.024

0.035

F

0.115

0.126

G

0.087

0.094

H 0.0008 0.0040

J

0.009

0.014

K

0.060

0.078

L

0.033

0.041

M

0_

10 _

S

0.264

0.287

B

1

2

3

D

L

G

J

C

0.08 (0003)

M

H

MILLIMETERS

MIN

MAX

6.30

6.70

3.30

3.70

1.50

1.75

0.60

0.89

2.90

3.20

2.20

2.40

0.020

0.100

0.24

0.35

1.50

2.00

0.85

1.05

0_

10 _

6.70

7.30

K

STYLE 1:

PIN 1.

2.

3.

4.

BASE

COLLECTOR

EMITTER

COLLECTOR

STYLE 2:

PIN 1.

2.

3.

4.

ANODE

CATHODE

NC

CATHODE

STYLE 3:

PIN 1.

2.

3.

4.

GATE

DRAIN

SOURCE

DRAIN

CASE 318E–04

SOT–223

A

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD

FINISH THICKNESS. MINIMUM LEAD THICKNESS

IS THE MINIMUM THICKNESS OF BASE

MATERIAL.

L

6

5

4

2

3

B

S

1

D

G

M

J

C

0.05 (0.002)

H

K

DIM

A

B

C

D

G

H

J

K

L

M

S

MILLIMETERS

MIN

MAX

2.90

3.10

1.30

1.70

0.90

1.10

0.25

0.50

0.85

1.05

0.013

0.100

0.10

0.26

0.20

0.60

1.25

1.55

0_

10 _

2.50

3.00

STYLE 1:

PIN 1.

2.

3.

4.

5.

6.

INCHES

MIN

MAX

0.1142 0.1220

0.0512 0.0669

0.0354 0.0433

0.0098 0.0197

0.0335 0.0413

0.0005 0.0040

0.0040 0.0102

0.0079 0.0236

0.0493 0.0610

0_

10 _

0.0985 0.1181

DRAIN

DRAIN

GATE

SOURCE

DRAIN

DRAIN

CASE 318G–02

TSOP–6

PLASTIC

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Package Outline Dimensions

8–5

�PACKAGE OUTLINE DIMENSIONS (continued)

A

L

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3

B

S

1

2

DIM

A

B

C

D

G

H

J

K

L

N

R

S

V

D

V

G

R N

C

0.05 (0.002)

J

K

H

STYLE 2:

PIN 1. ANODE

2. N.C.

3. CATHODE

STYLE 3:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

STYLE 7:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

STYLE 4:

PIN 1. CATHODE

2. CATHODE

3. ANODE

STYLE 9:

PIN 1. ANODE

2. CATHODE

3. CATHODE–ANODE

INCHES

MIN

MAX

0.071

0.087

0.045

0.053

0.035

0.049

0.012

0.016

0.047

0.055

0.000

0.004

0.004

0.010

0.017 REF

0.026 BSC

0.028 REF

0.031

0.039

0.079

0.087

0.012

0.016

MILLIMETERS

MIN

MAX

1.80

2.20

1.15

1.35

0.90

1.25

0.30

0.40

1.20

1.40

0.00

0.10

0.10

0.25

0.425 REF

0.650 BSC

0.700 REF

0.80

1.00

2.00

2.20

0.30

0.40

STYLE 5:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 10:

PIN 1. CATHODE

2. ANODE

3. ANODE–CATHODE

CASE 419–02

SC–70/SOT–323

A

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

G

V

6

5

4

1

2

3

DIM

A

B

C

D

G

H

J

K

N

S

V

–B–

S

D 6 PL

0.2 (0.008)

M

B

M

N

J

C

H

K

INCHES

MIN

MAX

0.071

0.087

0.045

0.053

0.031

0.043

0.004

0.012

0.026 BSC

–––

0.004

0.004

0.010

0.004

0.012

0.008 REF

0.079

0.087

0.012

0.016

STYLE 1:

PIN 1.

2.

3.

4.

5.

6.

EMITTER 2

BASE 2

COLLECTOR 1

EMITTER 1

BASE 1

COLLECTOR 2

STYLE 6:

PIN 1.

2.

3.

4.

5.

6.

ANODE 2

N/C

CATHODE 1

ANODE 1

N/C

CATHODE 2

MILLIMETERS

MIN

MAX

1.80

2.20

1.15

1.35

0.80

1.10

0.10

0.30

0.65 BSC

–––

0.10

0.10

0.25

0.10

0.30

0.20 REF

2.00

2.20

0.30

0.40

CASE 419B-01

SOT–363

Package Outline Dimensions

8–6

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�PACKAGE OUTLINE DIMENSIONS (continued)

A

C

ÂÂÂ

ÂÂÂ

ÂÂÂ

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

H

1

K

DIM

A

B

C

D

E

H

J

K

B

INCHES

MIN

MAX

0.055

0.071

0.100

0.112

0.037

0.053

0.020

0.028

0.004

–––

0.000

0.004

–––

0.006

0.140

0.152

MILLIMETERS

MIN

MAX

1.40

1.80

2.55

2.85

0.95

1.35

0.50

0.70

0.25

–––

0.00

0.10

–––

0.15

3.55

3.85

E

2

STYLE 1:

PIN 1. CATHODE

2. ANODE

J

D

CASE 425–04

SOD–123

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

–A–

S

2

3

D 3 PL

0.20 (0.008)

G –B–

1

M

B

K

J

0.20 (0.008) A

MILLIMETERS

MIN

MAX

0.70

0.80

1.40

1.80

0.60

0.90

0.15

0.30

1.00 BSC

–––

0.10

0.10

0.25

1.45

1.75

0.10

0.20

0.50 BSC

INCHES

MIN

MAX

0.028

0.031

0.055

0.071

0.024

0.035

0.006

0.012

0.039 BSC

–––

0.004

0.004

0.010

0.057

0.069

0.004

0.008

0.020 BSC

STYLE 1:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

C

L

DIM

A

B

C

D

G

H

J

K

L

S

STYLE 4:

PIN 1. CATHODE

2. CATHODE

3. ANODE

H

CASE 463–01

SOT–416/SC–90

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Package Outline Dimensions

8–7

�PACKAGE OUTLINE DIMENSIONS (continued)

14

NOTES:

1. LEADS WITHIN 0.13 (0.005) RADIUS OF TRUE

POSITION AT SEATING PLANE AT MAXIMUM

MATERIAL CONDITION.

2. DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

3. DIMENSION B DOES NOT INCLUDE MOLD

FLASH.

4. ROUNDED CORNERS OPTIONAL.

8

B

1

7

A

F

DIM

A

B

C

D

F

G

H

J

K

L

M

N

L

C

J

N

H

G

D

SEATING

PLANE

K

M

INCHES

MIN

MAX

0.715

0.770

0.240

0.260

0.145

0.185

0.015

0.021

0.040

0.070

0.100 BSC

0.052

0.095

0.008

0.015

0.115

0.135

0.300 BSC

0_

10_

0.015

0.039

MILLIMETERS

MIN

MAX

18.16

19.56

6.10

6.60

3.69

4.69

0.38

0.53

1.02

1.78

2.54 BSC

1.32

2.41

0.20

0.38

2.92

3.43

7.62 BSC

0_

10_

0.39

1.01

CASE 646–06

14–PIN DIP

PLASTIC

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN

FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

–A–

16

9

1

8

B

F

C

L

S

–T–

SEATING

PLANE

K

H

G

D

M

J

16 PL

0.25 (0.010)

M

T A

M

DIM

A

B

C

D

F

G

H

J

K

L

M

S

INCHES

MIN

MAX

0.740

0.770

0.250

0.270

0.145

0.175

0.015

0.021

0.040

0.70

0.100 BSC

0.050 BSC

0.008

0.015

0.110

0.130

0.295

0.305

0_

10 _

0.020

0.040

MILLIMETERS

MIN

MAX

18.80

19.55

6.35

6.85

3.69

4.44

0.39

0.53

1.02

1.77

2.54 BSC

1.27 BSC

0.21

0.38

2.80

3.30

7.50

7.74

0_

10 _

0.51

1.01

CASE 648–08

16–PIN DIP

PLASTIC

Package Outline Dimensions

8–8

Motorola Small–Signal Transistors, FETs and Diodes Device Data

�PACKAGE OUTLINE DIMENSIONS (continued)

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

–A–

14

8

–B–

1

P 7 PL

0.25 (0.010)

7

G

M

B

M

R X 45 _

C

F

–T–

0.25 (0.010)

M

J

M

K

D 14 PL

SEATING

PLANE

T B

A

S

S

DIM

A

B

C

D

F

G

J

K

M

P

R

MILLIMETERS

MIN

MAX

8.55

8.75

3.80

4.00

1.35

1.75

0.35

0.49

0.40

1.25

1.27 BSC

0.19

0.25

0.10

0.25

0_

7_

5.80

6.20

0.25

0.50

INCHES

MIN

MAX

0.337

0.344

0.150

0.157

0.054

0.068

0.014

0.019

0.016

0.049

0.050 BSC

0.008

0.009

0.004

0.009

0_

7_

0.228

0.244

0.010

0.019

CASE 751A–03

SO–14

PLASTIC

–A–

16

9

1

8

–B–

P

NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI

Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE

MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR

PROTRUSION SHALL BE 0.127 (0.005) TOTAL

IN EXCESS OF THE D DIMENSION AT

MAXIMUM MATERIAL CONDITION.

8 PL

0.25 (0.010)

B

M

S

G

R

K

F

X 45 _

C

–T–

SEATING

PLANE

M

D

16 PL

0.25 (0.010)

M

T B

S

A

S

J

DIM

A

B

C

D

F

G

J

K

M

P

R

MILLIMETERS

MIN

MAX

9.80

10.00

3.80

4.00

1.35

1.75

0.35

0.49

0.40

1.25

1.27 BSC

0.19

0.25

0.10

0.25

0_

7_

5.80

6.20

0.25

0.50

INCHES

MIN

MAX

0.386

0.393

0.150

0.157

0.054

0.068

0.014

0.019

0.016

0.049

0.050 BSC

0.008

0.009

0.004

0.009

0_

7_

0.229

0.244

0.010

0.019

CASE 751B–05

SO–16

PLASTIC

Motorola Small–Signal Transistors, FETs and Diodes Device Data

Package Outline Dimensions

8–9

�