HEF4541B-Q100

Programmable timer

Rev. 2 — 31 December 2013

Product data sheet

1. General description

The HEF4541B-Q100 is a programmable timer. It consists of a 16-stage binary counter,

an integrated oscillator to be used with external timing components, an automatic

power-on reset and output control logic. The external components RTC and CTC

determines the frequency of the oscillator within the frequency range 1 Hz to 100 kHz. An

external clock signal at input RS can replace the oscillator. The timer advances on the

positive-going transition of RS. A LOW on the auto reset input (AR) and a LOW on the

master reset input (MR) enables the internal power-on reset. A HIGH level at input MR

resets the counter independent on all other inputs. Resetting, disables the oscillator to

provide no active power dissipation.

A HIGH at input AR turns off the power-on reset to provide a low quiescent power

dissipation of the timer. The 16-stage counter divides the oscillator frequency by 28, 210,

213 or 216 depending on the state of the address inputs (A0, A1). The divided oscillator

frequency is available at output O. The phase input (PH) features a complementary output

signal. When the mode select input (MODE) is LOW the timer is a single transition timer

and when HIGH the timer is a 2n frequency divider.

It operates over a recommended VDD power supply range of 3 V to 15 V referenced to VSS

(usually ground). Unused inputs must be connected to VDD, VSS, or another input.

This product has been qualified to the Automotive Electronics Council (AEC) standard

Q100 (Grade 1) and is suitable for use in automotive applications.

2. Features and benefits

Automotive product qualification in accordance with AEC-Q100 (Grade 1)

Specified from 40 C to +85 C and from 40 C to +125 C

Fully static operation

5 V, 10 V, and 15 V parametric ratings

Standardized symmetrical output characteristics

ESD protection:

MIL-STD-883, method 3015 exceeds 2000 V

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V (C = 200 pF, R = 0 )

Complies with JEDEC standard JESD 13-B

�HEF4541B-Q100

Nexperia

Programmable timer

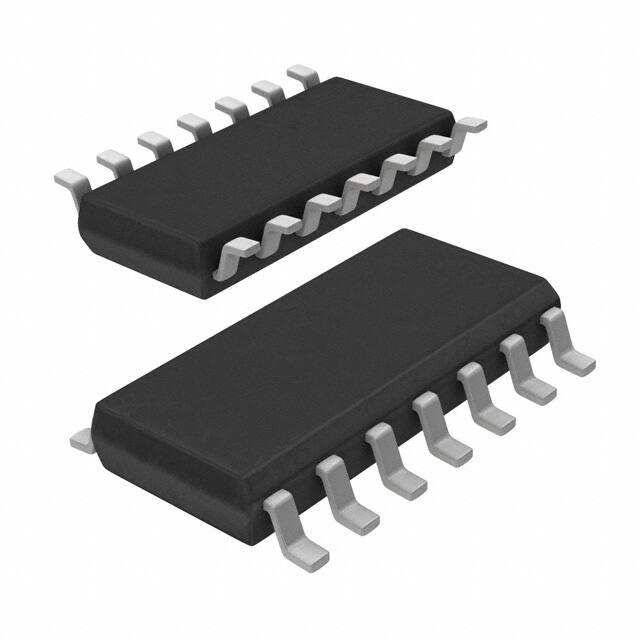

3. Ordering information

Table 1.

Ordering information

All types operate from 40 C to +125 C.

Type number

Package

Name

HEF4541BT-Q100 SO14

Description

Version

plastic small outline package; 14 leads; body width 3.9 mm

SOT108-1

4. Functional diagram

RS

CTC

RTC

3

2

1

A0

12

A1

MODE

13

10

CONTROL INPUTS

AR

MR

PH

CP

5

6

POWER-ON

RESET

CD

BINARY

COUNTER

OUTPUT

STAGE

8

O

9

001aai581

Fig 1.

Functional diagram

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

2 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

CTC

RTC

28 COUNTER

CP

RESET

RS

28

28 COUNTER

CP

RESET 22 25 28

A0

MUX

A1

AR

POWER-ON

RESET

LATCH

MR

MODE

PH

O

001aai583

Fig 2.

Logic diagram

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

3 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

5. Pinning information

5.1 Pinning

+()����%�4���

57&

�

�� 9''

&7&

�

�� $�

56

�

�� $�

Q�F�

�

�� Q�F�

$5

�

�� 02'(

05

�

�

3+

966

�

�

2

DDD�������

Fig 3.

Pin configuration

5.2 Pin description

Table 2.

Pin description

Symbol

Pin

Description

RTC

1

external resistor connection

CTC

2

external capacitor connection

RS

3

external resistor connection (RS) or external clock input

nc

4, 11

not connected

AR

5

auto reset input (active low)

MR

6

master reset input

VSS

7

ground (0 V)

O

8

timer output

PH

9

phase input

MODE

10

mode select input

A0, A1

12, 13

address inputs

VDD

14

supply voltage

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

4 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

6. Functional description

Table 3.

Function table[1]

Input

MODE

AR

MR

PH

MODE

H

L

X

X

auto reset disabled

L

L

X

X

auto reset enabled[2]

X

H

X

X

master reset active

X

L

X

H

normal operation selected division to output

X

L

X

L

single-cycle mode[3]

X

L

L

X

output initially LOW after reset

X

L

H

X

output initially HIGH, after reset

[1]

H = HIGH voltage level; L = LOW voltage level; X = don’t care.

[2]

For correct power-on reset, the supply voltage should be above 8.5 V. For VDD < 8.5 V, disable the auto reset and connect AR to VDD.

[3]

The timer is initialized on a reset pulse and the output changes state after 2n-1 counts and remains in that state (latched). A master reset

or a LOW to HIGH transition on the MODE input, resets this latch.

Table 4.

Frequency selection table

A0

A1

Number of counter stages n

f OSC

---------- = 2

n

fO

L

L

13

8192

L

H

10

1024

H

L

8

256

H

H

16

65536

7. Limiting values

Table 5.

Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol

Parameter

VDD

supply voltage

Conditions

Min

0.5

VI < 0.5 V or VI > VDD + 0.5 V

+18

10

Unit

V

IIK

input clamping current

VI

input voltage

IOK

output clamping current

VO < 0.5 V or VO > VDD + 0.5 V

-

10

mA

II/O

input/output current

O output

-

10

mA

Tstg

storage temperature

65

+150

C

Tamb

ambient temperature

40

+125

C

-

500

mW

-

100

mW

Ptot

total power dissipation

P

power dissipation

[1]

-

Max

0.5

Tamb = 40 C to +125 C

[1]

VDD + 0.5

mA

V

For SO14 package: Ptot derates linearly with 8 mW/K above 70 C.

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

5 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

8. Recommended operating conditions

Table 6.

Recommended operating conditions

Symbol

Parameter

VDD

VI

Conditions

Min

Max

Unit

supply voltage

3

15

V

input voltage

0

VDD

V

Tamb

ambient temperature

in free air

40

+125

C

t/V

input transition rise and fall rate

VDD = 5 V

-

3.75

s/V

VDD = 10 V

-

0.5

s/V

VDD = 15 V

-

0.08

s/V

9. Static characteristics

Table 7.

Static characteristics

VSS = 0 V; VI = VSS or VDD; unless otherwise specified.

Symbol Parameter

VIH

VIL

VOH

VOL

IOH

Conditions

HIGH-level

input voltage

IO < 1 A

LOW-level

input voltage

IO < 1 A

HIGH-level

IO < 1 A

output voltage

Tamb = 40 C

Tamb = 25 C

Tamb = 85 C Tamb = 125 C Unit

Min

Max

Min

Max

Min

Max

Min

Max

5V

3.5

-

3.5

-

3.5

-

3.5

-

V

10 V

7.0

-

7.0

-

7.0

-

7.0

-

V

15 V

11.0

-

11.0

-

11.0

-

11.0

-

V

5V

-

1.5

-

1.5

-

1.5

-

1.5

V

10 V

-

3.0

-

3.0

-

3.0

-

3.0

V

15 V

-

4.0

-

4.0

-

4.0

-

4.0

V

5V

4.95

-

4.95

-

4.95

-

4.95

-

V

10 V

9.95

-

9.95

-

9.95

-

9.95

-

V

15 V

14.95

-

14.95

-

14.95

-

14.95

-

V

5V

-

0.05

-

0.05

-

0.05

-

0.05

V

10 V

-

0.05

-

0.05

-

0.05

-

0.05

V

15 V

-

0.05

-

0.05

-

0.05

-

0.05

V

5V

-

1.4

-

1.2

-

0.95

-

0.95 mA

VO = 4.6 V

5V

-

0.5

-

0.4

-

0.3

-

0.3

VO = 9.5 V

10 V

-

1.4

-

1.2

-

0.95

-

0.95 mA

VO = 13.5 V 15 V

-

4.8

-

4.0

-

3.2

-

3.2

mA

mA

LOW-level

IO < 1 A

output voltage

HIGH-level

output current

VDD

CTC, RTC;

VO = 2.5 V

mA

O;

HEF4541B_Q100

Product data sheet

VO = 2.5 V

5V

-

1.7

-

1.4

-

1.1

-

1.1

VO = 4.6 V

5V

-

0.64

-

0.5

-

0.36

-

0.36 mA

VO = 9.5 V

10 V

-

1.6

-

1.3

-

0.9

-

0.9

mA

VO = 13.5 V 15 V

-

4.2

-

3.4

-

2.4

-

2.4

mA

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

6 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

Table 7.

Static characteristics …continued

VSS = 0 V; VI = VSS or VDD; unless otherwise specified.

Symbol Parameter

IOL

LOW-level

output current

Conditions

VDD

Tamb = 40 C

Tamb = 25 C

Tamb = 85 C Tamb = 125 C Unit

Min

Max

Min

Max

Min

Max

Min

Max

CTC, RTC;

VO = 0.4 V

5V

0.33

-

0.27

-

0.20

-

0.20

-

mA

VO = 0.5 V

10 V

1.0

-

0.85

-

0.68

-

0.68

-

mA

VO = 1.5 V

15 V

3.2

-

2.7

-

2.3

-

2.3

-

mA

VO = 0.4 V

5V

0.64

-

0.5

-

0.36

-

0.36

-

mA

VO = 0.5 V

10 V

1.6

-

1.3

-

0.9

-

0.9

-

mA

VO = 1.5 V

15 V

4.2

-

3.2

-

2.4

-

2.4

-

mA

15 V

-

0.1

-

0.1

-

1.0

-

1.0

A

5V

-

5

-

5

-

150

-

150

A

10 V

-

10

-

10

-

300

-

300

A

15 V

-

20

-

20

-

600

-

600

A

-

-

-

-

7.5

-

-

-

-

pF

O;

II

input leakage

current

IDD

supply current IO = 0 A

CI

input

capacitance

Table 8.

Reset characteristics

VSS = 0 V; VI = VSS or VDD; see Table 12 for test conditions; unless otherwise specified.

Symbol Parameter

IDD

VDD

Conditions

VDD

supply current supply current

5V

for power-on

10 V

reset enable;

AR = MR = 0 V; 15 V

Other inputs at

0 V or VDD

supply voltage supply voltage

for automatic

reset

initialization;

AR = MR = 0 V;

Other inputs at

0 V or VDD

HEF4541B_Q100

Product data sheet

-

Tamb = 40 C Tamb = +25 C Tamb = +85 C Tamb = +125 C Unit

Min

Max

Min Typ Max

Min

Max

Min

Max

-

80

-

20

80

-

230

-

230

A

-

750

-

250 600

-

700

-

700

A

-

1.6

-

0.5

1.3

-

1.5

-

1.5

mA

-

-

8.5

5

-

-

-

-

-

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

V

Nexperia B.V. 2017. All rights reserved

7 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

10. Dynamic characteristics

Table 9.

Dynamic characteristics

VSS = 0 V; Tamb = 25 C unless otherwise specified. For test circuit, see Figure 5.

Symbol

Parameter

propagation delay

tpd

Conditions

RS to O;

28 selected;

see Figure 4

pulse width

fclk(max)

fosc

Min

Typ[1]

348 ns + (0.55 ns/pF)CL

-

375

750

ns

10 V

139 ns + (0.23 ns/pF)CL

-

150

300

ns

15 V

102 ns + (0.16 ns/pF)CL

-

110

220

ns

5V

398 ns + (0.55 ns/pF)CL

-

425

850

ns

10 V

154 ns + (0.23 ns/pF)CL

-

165

330

ns

15 V

5V

RS to O;

210 selected;

see Figure 4

tW

Extrapolation formula

VDD

[2]

Max

Unit

112 ns + (0.16 ns/pF)CL

-

120

240

ns

RS to O;

213 selected;

see Figure 4

5V

483 ns + (0.55 ns/pF)CL

-

510

1020

ns

10 V

179 ns + (0.23 ns/pF)CL

-

190

380

ns

15 V

127 ns + (0.16 ns/pF)CL

-

135

270

ns

RS to O;

216 selected;

see Figure 4

5V

548 ns + (0.55 ns/pF)CL

-

575

1150

ns

10 V

199 ns + (0.23 ns/pF)CL

-

210

420

ns

142 ns + (0.16 ns/pF)CL

-

150

300

ns

15 V

RS LOW;

MR HIGH;

see Figure 4

5V

maximum clock

frequency

RS; see Figure 4

oscillator frequency

Rt = 5 k;

Ct = 1 nF;

RS = 10 k;

see Figure 6

Rt = 56 k;

Ct = 1 nF;

RS = 120 k;

see Figure 6

[3]

60

30

-

ns

10 V

30

15

-

ns

15 V

24

12

-

ns

5V

8

16

-

MHz

10 V

15

30

-

MHz

15 V

18

36

-

MHz

5V

-

90

-

kHz

10 V

-

90

-

kHz

15 V

-

90

-

kHz

5V

-

8

-

kHz

10 V

-

8

-

kHz

15 V

-

8

-

kHz

[1]

The typical values of the propagation delay and transition times are calculated from the extrapolation formulas shown (CL in pF).

[2]

tpd is the same as tPHL and tPLH.

[3]

tW is the same as tWL(min) and tWH(min).

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

8 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

Table 10. Dynamic power dissipation

PD can be calculated from the formulas shown. VSS = 0 V; tr = tf 20 ns; Tamb = 25 C.

Symbol

Parameter

VDD

Typical formula

PD

dynamic power dissipation

Per package

5V

PD = 1300 fi + (fo CL VDD2) W

10 V

PD = 5300 fi + (fo CL VDD2) W

15 V

PD = 12000 fi + (fo CL VDD2) W

Total, using the on-chip oscillator

[1]

5V

PD = 1300 fosc + foCLVDD2 + 2CTCVDD2 fosc + 10VDD W

10 V

PD = 5300 fosc + foCLVDD2 + 2CTCVDD2 fosc + 100VDD W

15 V

PD = 12000 fosc + foCLVDD2 + 2CTCVDD2 fosc + 400VDD W

fi = input frequency in MHz; fo = output frequency in MHz; CL = output load capacitance in pF; VDD = supply voltage in V;

fosc = oscillator frequency in MHz; CTC = timing capacitance in pF.

11. Waveforms

(1)

1/fclk(max)

VI

VM

RS input

VSS

VOH

tWH(min)

tWL(min)

tPLH

O output

tPHL

VM

VOL

VI

MR input

VSS

tWH(min)

aaa-003391

VOL and VOH are typical output voltage levels that occur with the output load.

Measurement points are given in Table 11, the test circuit in Figure 5 and the test data in Table 12

(1) 2n pulses as selected by address inputs (A0, A1).

Fig 4.

Propagation delay clock (RS) to output (O), clock pulse width and maximum clock frequency

Table 11.

Measurement points

Supply voltage

Input

Output

VDD

VM

VM

5 V to 15 V

0.5VDD

0.5VDD

HEF4541B_Q100

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

9 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

VDD

VI

VO

G

DUT

CL

RT

001aag182

Test data is given in Table 12.

Definitions for test circuit:

DUT - Device Under Test.

RL = Load resistance.

CL = load capacitance.

RT = Termination resistance should be equal to output impedance of Zo of the pulse generator.

Fig 5.

Test circuit for measuring switching times

Table 12.

Test data

Supply

Input

VDD

VI

tr, tf

CL

5 V to 15 V

VSS or VDD

20 ns

50 pF

HEF4541B_Q100

Product data sheet

Load

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 31 December 2013

©

Nexperia B.V. 2017. All rights reserved

10 of 17

�HEF4541B-Q100

Nexperia

Programmable timer

12. Application information

RC oscillator timing component limitations

RTCCTC determines the oscillator frequency, provided RTC