SLG88103/4

Rail to Rail I/O 375 nA/Amp

Dual/Quad CMOS Op Amps with Power Down

General Description

Pin Configurations

The SLG88103/4 is a wide voltage range, 375 nA Dual/Quad

Channel CMOS Input Operational Amplifier capable of

rail-to-rail input and output operation. Each Amplifier can be

individually powered down.

Features

•

•

•

•

•

•

•

•

•

•

•

•

Low Quiescent Current: 375 nA per Amplifier (typ)

Low Offset Voltage: ±200 µV (typ)

Zero-Crossover

Low Offset Drift: 1 µV/˚C (typ)

DC Precision:

• PSRR: 115 dB

• CMRR: 100 dB

• AOL: 120 dB

Gain-Bandwidth Product: 10 kHz (typ)

Rail to Rail Input/Output

Supply Voltage: 1.71 V to 5.5 V

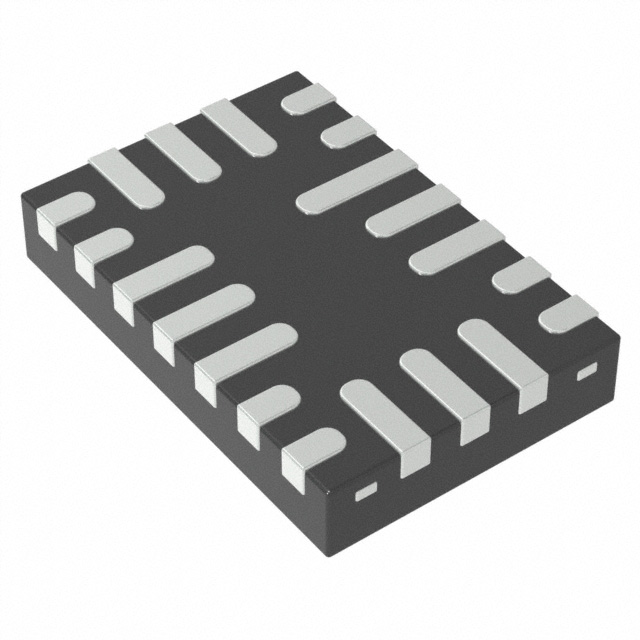

Tiny Package:

10-pin 2 x 2 mm STDFN

20-pin 2 x 3.5 mm STQFN

Industrial Temperature Range: -40 ˚C to 85 ˚C

Typical Applications

•

•

•

•

•

•

•

•

•

Battery-Powered Devices

Portable Devices

Wearable Products

Gas Sensors

Pressure Sensors

Medical Monitors

Smoke Detectors

Active RFID Reader

Energy Harvester

SLG88103

PD1

1

10

OUT1

2

9

OUT2

IN-1

3

8

IN-2

IN+1

4

7

IN+2

VSS

5

6

PD2

VDD

10-pin STDFN

(Top View)

SLG88104

PD1 VDD

OUT1

1

18

OUT4

IN-1

2

17

IN-4

IN+1

3

16

IN+4

20

19

VSS

4

15

PD4

PD2

5

14

VDD

OUT2

IN-2

IN+2

6

7 9

8

OUT3

13

10 12

IN-3

IN+3

11

VSS PD3

20-pin STQFN

(Top View)

Example Application Circuit: Non-Inverting Amplifier + GreenPAK with Wake-Sleep Controller

SLG88103/4

Silego Technology, Inc.

000-0088103/4-101

Rev 1.01

Revised March 13, 2017

�SLG88103/4

Pin Description

Pin #

20L

10L

STQFN STDFN

Pin Name

Type

Pin Description

1

2

OUT1

O

Analog Output (Op Amp 1)

2

3

IN-1

I

Inverting Input (Op Amp 1)

3

4

IN+1

I

Non-inverting Input (Op Amp 1)

4

5

VSS

GND

5

6

PD2

I

Power Down Input (Op Amp 2)

When PD pin is high, the respective amplifier is powered down.

6

9

OUT2

O

Analog Output (Op Amp 2)

7

8

IN-2

I

Inverting Input (Op Amp 2)

8

7

IN+2

I

Non-inverting Input (Op Amp 2)

9

--

VSS

GND

10

--

PD3

I

Power Down Input (Op Amp 3)

When PD pin is high, the respective amplifier is powered down.

Negative Power Supply

Negative Power Supply

11

--

IN+3

I

Non-inverting Input (Op Amp 3)

12

--

IN-3

I

Inverting Input (Op Amp 3)

13

--

OUT3

O

Analog Output (Op Amp 3)

14

10

VDD

PWR

15

--

PD4

I

Power Down Input (Op Amp 4)

When PD pin is high, the respective amplifier is powered down.

16

--

IN+4

I

Non-inverting Input (Op Amp 4)

17

--

IN-4

I

Inverting Input (Op Amp 4)

18

--

OUT4

O

Analog Output (Op Amp 4)

19

--

VDD

PWR

20

1

PD1

I

Power Supply

Power Supply

Power Down Input (Op Amp 1)

When PD pin is high, the respective amplifier is powered down.

Ordering Information

Part Number

Type

Production Flow

SLG88103V

10-pin STDFN

Industrial, -40 °C to 85 °C

SLG88103VTR

10-pin STDFN (Tape and Reel)

Industrial, -40 °C to 85 °C

SLG88104V

20-pin STQFN

Industrial, -40 °C to 85 °C

SLG88104VTR

20-pin STQFN (Tape and Reel)

Industrial, -40 °C to 85 °C

000-0088103/4-101

Page 2 of 22

�SLG88103/4

Absolute Maximum Ratings

Parameter Description

Min.

Typ.

Max.

Unit

Voltage on VDD pin relative to GND

-0.3

--

6.0

V

TA

Operating Range

-40

--

85

˚C

θJA

Thermal Resistance

--

80

--

˚C/W

TS

Storage Temperature

-65

--

150

˚C

TJ

Junction Temperature

--

--

150

˚C

ESD Protection (Human Body Model)

2000

--

--

V

ESD Protection (Charged Device Model)

500

--

--

V

VDD

ESDHBM

ESDCDM

MSL

Moisture Sensitivity Level

1

Note: Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Electrical Characteristics

TA = 25 °C, VDD = 1.71 V to 5.5 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL, unless otherwise stated.

Symbol

Description

Conditions

Min

Typ

Max

Unit

VCM = VDD/2

-1000

±200

1000

μV

Input Offset Voltage

VCM = VDD/2;

TA = -40 ˚C to 85 ˚C

-1100

±250

1100

μV

VCM = VSS;

TA = -40 ˚C to 85 ˚C

-2400

±350

2400

μV

VCM = VDD/2;

TA = -40 ˚C to 85 ˚C

-4

±1

4

μV/˚C

VCM = VSS;

TA = -40 ˚C to 85 ˚C

-10

±2

10

μV/˚C

Input Offset

VOS

dVOS/dT

dVOS/Time

PSRR

CS

Offset Drift with Temperature

10 Year Offset Drift

Power Supply Rejection Ratio

Channel Separation

TA = 85˚C; VDD = 3.3 V

-30

--

+30

μV

TA = 85˚C; VDD = 5.0 V

-40

--

+40

μV

VCM = VDD/2

TA = -40 ˚C to 85 ˚C

95

115

--

dB

VCM = VSS

TA = -40 ˚C to 85 ˚C

85

100

--

dB

VDD = 5 V, f = 10 Hz

--

120

--

dB

VDD = 5 V, f = 1 kHz

--

95

--

dB

Input Voltage Range

VCMR

CMRR

Input Common-Mode Voltage Range TA = -40 ˚C to 85 ˚C

Common-Mode Rejection Ratio

VSS

--

VDD

V

VSS + 0.8 V < VCM < VDD - 0.8 V,

TA = -40 ˚C to 85 ˚C

65

100

--

dB

VSS < VCM < VSS + 0.8 V,

VDD - 0.8 V < VCM < VDD,

TA = -40 ˚C to 85 ˚C

50

75

--

dB

--

2

--

pA

--

320

500

pA

Input Bias Current and Impedance

IB

Input Bias Current1

000-0088103/4-101

TA = 85 ˚C

Page 3 of 22

�SLG88103/4

Electrical Characteristics (continued)

TA = 25 °C, VDD = 1.71 V to 5.5 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL, unless otherwise stated.

Symbol

Description

IOS

Input Offset Current2

RCM

Common Mode Input Resistance

Conditions

Min

Typ

--

±0.3

--

pA

TA = 85 ˚C

--

±20

--

pA

--

1013

--

Ω

--

13

--

Ω

10

Max

Unit

RDIFF

Differential Input Resistance

CCM

Input Capacitance Common-Mode

--

4.3

--

pF

CDIFF

Input Capacitance Differential

--

6

--

pF

RL = 1 MΩ;

VSS + 0.1 V ≤ VOUT ≤ VDD - 0.1 V

100

120

--

dB

RL = 50 kΩ;

VSS + 0.5 V ≤ VOUT ≤ VDD - 0.5 V

100

120

--

dB

RL = 50 kΩ; TA = 85 ˚C;

VSS + 0.1 V ≤ VOUT ≤ VDD - 0.1 V

80

100

--

dB

VSS + 5

--

VDD - 5

mV

VSS + 100

--

VDD - 100

mV

3.8

4.5

--

mA

8.5

10

--

mA

Open-Loop Gain

AOL

DC Open Loop Voltage Gain

Output

VOH, VOL

VOSR

ISC

CLOAD

Maximum Voltage Swing

RL= 50 kΩ

Linear Output Swing Range

VOVR from Rail

Short-circuit Current

VDD = 1.71 V

VDD = 3.0 V to 5.5 V

Capacitive Load Drive

See Typical Performance Charts

Power Supply

VDD

IQ

Supply Voltage

Quiescent Current (Per Amplifier)

Guaranteed by PSRR Test

1.71

--

5.5

V

--

0.38

0.55

μA

TA = -40 ˚C to 85 ˚C

--

0.4

0.8

μA

PDx = VDD

--

1

--

nA

Frequency Response

GBW

Gain Bandwidth Product

G = +1 V/V

--

10

--

kHz

PM

Phase Margin

G = +1 V/V

--

54

--

˚

SR

Slew Rate

RL= 50 kΩ

2.4

5.0

--

V/ms

tOR

Overload Recovery Time

TA = -40 ˚C to 85 ˚C; RL= 50 kΩ

--

350

--

μs

en

Input Voltage Noise

f = 0.1 to 10 Hz

--

6.5

--

μVP-P

Vn

Input Voltage Noise Density

f =1 kHz

--

195

--

nV/√Hz

In

Input Current Noise Density

f =1 kHz

--

< 10

--

fA/√Hz

Noise

Note:

1. Part is measured to be less than 1 μA during production test.

2. Guaranteed by design, not tested in production.

000-0088103/4-101

Page 4 of 22

�SLG88103/4

Typical Performance Charts

TA = 25 °C, VDD = 5.0 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL , CL = 80 pF, unless otherwise stated.

18%

24%

164 Samples

VDD = 1.71 and 5.5V

VCM = VSS

22%

Percentage of Occurrences

Percentage of Occurrences

16%

14%

12%

10%

8%

6%

4%

2%

124 Samples

TA = (-40;+25)°C and (+25;+85)°C

VDD = 3.3V ; VCM = VSS

20%

18%

16%

14%

12%

10%

8%

6%

4%

0%

800

700

600

500

400

300

200

0

100

-100

-200

-300

-400

-500

-600

-800

-700

2%

0%

-3

Input Offset Voltage (�V)

250

250

Input offset voltage (�V)

Input Ofset voltage (�V)

300

TA = -40°C

TA = +25°C

TA = +85°C

100

50

1

2

3

4

5

6

7

TA = -40°C

TA = +25°C

200

TA = +85°C

150

100

50

0

1

2

3

4

Common Mode Input Voltage (V)

5

0.0

6

Fig 2. Input Offset Voltage vs. Common Mode Input Voltage

VDD = 5.5 V.

0.8

130

0.7

120

TA = +85°C

0.6

0.5

TA = +25°C

0.4

0.3

TA = -40°C

0.2

0.1

0.5

1.0

Common mode input voltage (V)

1.5

Fig 5. Input Offset Voltage vs. Common Mode Input Voltage

VDD = 1.71 V.

TA = +25°C

TA = -40°C

110

DC Open Loop Gain (dB)

Quiescent Current (�A/Amplifier)

0

Fig 4. Input Offset Voltage Temperature Drift Distribution

VCM = VSS; VDD = 3.3 V; TA = -40˚C to 85˚C.

300

150

-1

Input Offset Voltage Temperature Drift (�V/°C)

Fig 1. Input Offset Voltage Drift Distribution

VCM = VSS; VDD = 1.71 V and 5.5 V; TA = 25˚C.

200

-2

TA = +85°C

100

90

80

70

60

50

0

0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Power Supply Voltage (V)

Fig 3. Quiescent Current vs. Power Supply Voltage

000-0088103/4-101

-0.5

0.0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

Common mode input voltage (V)

Fig 6. DC Open Loop Gain vs. Common Mode Input Voltage

VDD = 3.3 V.

Page 5 of 22

�SLG88103/4

TA = 25 °C, VDD = 5.0 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL , CL = 80 pF, unless otherwise stated.

50

1200

40

80

Gain (dB)

30

70

20

60

GAIN

10

50

0

40

-10

Phase (°)

PHASE

Input Voltage Noise Density (nV/�Hz)

90

1000

Frequency (Hz)

800

600

400

200

0

30

100

1000

0

10000

Fig 7. Open Loop Gain and Phase vs. Frequency

VDD = 3.3 V.

1

10

Frequency (Hz)

100

1,000

Fig 10. Input Noise Voltage Density vs. Frequency

100

90

PSRR+

70

60

PSRR-

1�V/div

CMRR, PSRR (dB)

80

50

CMRR

40

30

20

10

0

10

100

1,000

Frequency (Hz)

10,000

Time (1s/div)

Fig 8. CMRR, PSRR vs. Frequency

VDD = 3.3 V.

Fig 11. 0.1 Hz to 10 Hz Noise

140

14

Output Short Circuit Current (mA)

Channel Separation (dB)

120

100

80

60

40

20

0

Source

12

10

Sink

8

6

4

2

0

10

100

1000

10000

Frequency (Hz)

100000

Fig 9. Channel Separation vs. Frequency

000-0088103/4-101

1000000

1.0

1.5

2.0

2.5 3.0 3.5 4.0

Power supply voltage (V)

4.5

5.0

5.5

Fig 12. Output Short Circuit Current vs. VDD

Page 6 of 22

�SLG88103/4

TA = 25 °C, VDD = 5.0 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL , CL = 80 pF, unless otherwise stated.

15

14

100

10

Gain Bandwidth Product (kHz)

Input Bias and Offset Currents (pA)

1000

Ib

|Ios|

1

0.1

0.01

-20

0

20

40

60

Ambient Temperature (°C)

80

TA = +25°C

10

9

TA = -40°C

8

7

6

1.5

2.0

2.5

3.0

3.5

4.0

4.5

Power supply voltage (V)

5.0

5.5

Fig 16. Gain Bandwidth Product vs. Power Supply Voltage

15

VDD = 5.5 V

14

100

TA = +85°C

Gain Bandwidth Product (kHz)

Input Bias and Offset Currents (pA)

TA = +85°C

11

100

Fig 13. Input Bias, Offset Currents vs. TA

VDD = 3.3 V.

10

1

TA = +25°C

0.1

Ib

|Ios|

13

Vdd=5.5V

12

11

VDD = 1.71V

10

9

8

7

6

5

0.01

0.0

1.0

2.0

3.0

4.0

Input Common Mode Voltage (V)

-40

5.0

-20

0

20

40

60

80

100

Ambient temperature (°C)

Fig 14. Input Bias, Offset Currents vs. VCM

VDD = 5.5 V.

Fig 17. Gain Bandwidth Product vs. Ambient Temperature

10

700

TA = +55°C

600

9

TA = +85°C

8

TA = +25°C

500

Low-to-High

7

Slew Rate (V/ms)

Input Current (pA)

12

5

-40

1000

13

400

300

200

6

5

High-to-Low

4

3

2

100

1

TA = -40°C

0

0

-0.3

-0.2

-0.2

-0.1

-0.1

Input Common Mode Voltage (V)

Fig 15. Input Current vs. VCM (below VSS)

VDD = 5.5 V.

000-0088103/4-101

0.0

-40

-20

0

20

40

60

80

100

Ambient temperature (°C)

Fig 18. Slew Rate vs. Ambient Temperature

G = 1 V/V; RL = 50 kΩ

Page 7 of 22

�SLG88103/4

10mV/div

10mV/div

TA = 25 °C, VDD = 5.0 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL , CL = 80 pF, unless otherwise stated.

Time (250�s/div)

Time (250�s/div)

Fig 22. Small Signal Non-inverting Step Response

G = 1 V/V; RL = 50 kΩ; CL = 60 pF.

500mV/div

500mV/div

Fig 19. Small Signal Inverting Step Response

G = -1 V/V; RL = 50 kΩ; CL = 60 pF.

Time (1ms/div)

Time (1ms/div)

Fig 23. Large Signal Non-inverting Step Response

G = 1 V/V; RL = 50 kΩ; CL = 60 pF.

1V/div

1V/div

Fig 20. Large Signal Inverting Step Response

G = -1 V/V; RL = 50 kΩ; CL = 80 pF.

Time (1ms/div)

Fig 21. Inverting Overload Recovery

G = -1 V/V; RL = 50 kΩ; CL = 60 pF.

000-0088103/4-101

Time (1ms/div)

Fig 24. Non-Inverting Overload Recovery

G = 1 V/V; RL = 50 kΩ; CL = 60 pF.

Page 8 of 22

�SLG88103/4

TA = 25 °C, VDD = 5.0 V, VSS = GND, VCM = VDD/2, VOUT = VDD/2, VL = VDD/2, RL = 1 MΩ to VL , CL = 80 pF, unless otherwise stated.

150

10mV/div

DC Open Loop Gain (dB)

140

130

TA = +25°C

120

110

100

TA = +85°C

90

80

70

1.0

Time (250�s/div)

Fig 25. Small Signal Non-inverting Step Response

G = 1 V/V; RL = 50 kΩ; CL = 10 nF.

1.5

2.0

2.5 3.0 3.5 4.0

Power supply voltage (V)

4.5

5.0

5.5

Fig 28. DC Open Loop Gain vs. Power Supply Voltage

RL = 50 kΩ

60

1,000

Overshoot

Undershoot

Output Voltage Swing from Rail (mV)

Overshoot (%)

50

40

VIN = 100 mVp-p

30

VIN = 40 mVp-p

20

10

VIN = 100 mVp-p

0

100

1,000

Capacitive load (pF)

VDD = 5.5V

10

— VDD - VOH

- - VOL - VSS

1

10,000

0.1

Fig 26. Small Signal Overshoot vs. Capacitive Load

VDD = 3.3 V; VIN = 40 and 100 mV p-p; G = 1 V/V.

1

Output Load Current (mA)

10

Fig 29. Output Voltage Swing from Rail vs. IOUT

VDD = 1.71 V and 5.5 V.

600

6

500

5

— VPDx

— VOUT

4

400

Voltage(V)

Overload Recovery Time (�s)

VDD = 1.71V

100

High-to-Low

300

Low-to-High

3

200

2

100

1

0

0

1.0

1.5

2.0

2.5 3.0 3.5 4.0 4.5

Power Supply Voltage (V)

5.0

5.5

6.0

Fig 27. Overload Recovery Time vs. Power Supply Voltage

RL= 50 kΩ; G = 1 V/V.

000-0088103/4-101

0

5

10

15

20

25

Time (�s)

30

35

40

Fig 30. Output Response to Power Down Signal

G = 1 V/V; RL = 50 kΩ; CL = 20 pF; VIN = VS/2.

Page 9 of 22

�SLG88103/4

Applications Information

The SLG88103/4 operates on a 1.71 V to 5.5 V power supply over a wide industrial temperature range from -40 °C to 85 °C. This

dual/quad op amp chip has two/four active low enable pins used to individually power-up / power-down each op amp. Its common-mode range extends from 0 to VDD and its output swings from rail-to-rail.

Input Protection

Voltage spikes need to be controlled at the inputs of each operational amplifier in order to avoid damaging the device. Electrical

events like electrostatic discharge can produce large voltages at these nodes. The SLG88103/4 has internal circuitry to protect

the device from these events. If VIN exceeds VDD or drops below VSS, additional currents will flow through the internal ESD

diodes and can damage the device even if the supplies are turned off.

In this case we recommend placing a resistor in series to the input to limit current through the internal ESD diodes to 5 mA (or

preferably less).

Fig 31. ESD Protection .

Driving Capacitive Loads

Capacitive loads degrade circuit stability by decreasing the phase margin and bandwidth of the operational amplifier circuit. The

SLG88103/4 can drive capacitive loads up to 10 nF at low loads. The amplifier’s output impedance and the capacitive load add

phase lag to the system. This phase lag creates gain peaking in the frequency response and peaking/ringing in the output’s

transient response. When large capacitive loads need to be driven, isolation resistors need to be used to increase the phase

margin. This is done by increasing the output load impedance at higher frequencies. After selecting an isolation resistor value,

verify that the frequency peaking and transient overshoot and ringing have been reduced.

Fig 32. Capacitive Load Test Circuit.

000-0088103/4-101

Page 10 of 22

�SLG88103/4

Low Power Considerations

The SLG88103/4 features low quiescent current at 375 nA per amplifier, as well as extremely high-impedance CMOS inputs. To

take most advantage of such low power features, high impedance external components should be used. We recommend using

low-leakage capacitors (such as ceramic). Other types of capacitors (such as aluminum dielectric) can leak at uA levels and

consume more quiescent power than the op-amp itself! High value resistors are needed to keep power consumption low, as well

as to avoid gain loss and non-linearities due to loading effects on the ultra-low power-stage of the op amp. On the other hand,

higher resistances increase thermal noise and sensitivity to external interference. We recommend impedances between 100 kΩ

and 500 kΩ in gain/feedback networks to achieve balanced performance given the ultra-low power characteristics of SLG88103/4.

PCB Layout

For proper PCB layout, place a 100 nF decoupling capacitor close to the VDD pin of the SLG88103/4. To improve sensitive system

performance, keep trace lengths similar on the positive and negative inputs of the op amp. Keep feedback resistors as close to

the op amp and as short as possible. In addition, remove the PCB ground plane from under the inputs and outputs of the op amp.

For low current applications, board leakage currents on sensitive, high impedance inputs can degrade signal integrity. To maximize

system performance, use guard rings / shields around these high impedance op amp inputs. For non-inverting op amps, IN+

should have a guard ring driven to the voltage of IN- by a low impedance source. Similarly, the guard ring around IN- should be

driven to IN+ for an inverting amplifier. The IN- and IN+ nodes for non-inverting and inverting amplifiers respectively can be used

as low impedance voltage sources. This is because these nodes are effectively low impedance nodes due to op amp feedback

properties. For a non-inverting amplifier, leakage current on IN+ will produce a voltage on the input that will be amplified to the

op amp’s output. On the other hand, the op amp will fight changes in voltage on IN- to match the voltage potential at IN+. These

guard rings should be used on both sides of the PCB to help sink stray currents on the PCB before the currents can reach the

input pins of the op amp and to minimize stray capacitance.

Proper Setup for Unused Op Amps

For an unused op amp on the SLG88103/4, connect the op amp as a voltage follower with the input tied to ground and it’s enable

pin tied to VDD. An example circuit using one of the op amps is shown below.

Fig 33. Unused Op Amp Setup.

Application Examples

The SLG88103/4 excels in low-power applications that operate at low frequencies. Please see the “Application Notes” section of

this datasheet for application examples which use the SLG88103/4.

000-0088103/4-101

Page 11 of 22

�SLG88103/4

Design Resources

1.

Spice Macro Model

The most recent SPICE model is available on Silego’s website at www.silego.com. This model is intended for simulation

purposes only and shouldn’t be used in place of hardware testing to verify proper functionality in a full system.

2.

Application Notes

For more information on the topics discussed in this datasheet and applications of this device, please see the following

applications notes available online at our Application Notes Page. New Application Notes are added regularly.

AN-1106 Custom Instrumentation Amplifier Design

3.

Design Support

Please contact a Silego Representative at our Contact Page for more information on the SLG88103/4. They will be happy

to assist you by answering additional questions and by offering design support for projects relating to the SLG88103/4 and

Silego’s GreenPAK devices.

4.

Op Amp + GreenPAK EVB

The OP AMP+GreenPAK EVB provides convenient breakout access for various IC’s in Silego’s Op Amp and GreenPAK

product families. Please see the OP AMP+EVB Layout Guide for more information on which GreenPAK devices and op amps

can be placed on this PCB.

Fig 34. Op Amp + GreenPAK EVB.

000-0088103/4-101

Page 12 of 22

�SLG88103/4

Package Top Marking System Definition - SLG88103

Pin 1 Identifier

PPA

WWN

R

Part Code + Assembly Code

Date Code + S/N Code

Revision Code

PP - Part ID Field

WW - Date Code Field1

N - Lot Traceability Code Field1

A - Assembly Site Code Field 2

R - Part Revision Code Field2

Note 1: Each character in code field can be alphanumeric A-Z and 0-9

Note 2: Character in code field can be alphabetic A-Z

000-0088103/4-101

Page 13 of 22

�SLG88103/4

Package Top Marking System Definition - SLG88104

Pin 1 Identifier

PPPPP

WWNNN

ARR

Part Code

Date Code + LOT Code

Assembly + Rev. Code

PPPPP - Part ID Field

WW - Date Code Field1

NNN - Lot Traceability Code Field1

A - Assembly Site Code Field2

RR - Part Revision Code Field2

Note 1: Each character in code field can be alphanumeric A-Z and 0-9

Note 2: Character in code field can be alphabetic A-Z

000-0088103/4-101

Page 14 of 22

�SLG88103/4

Package Drawing and Dimensions - SLG88103

10 Lead STDFN Package

JEDEC MO-252

000-0088103/4-101

Page 15 of 22

�SLG88103/4

Package Drawing and Dimensions - SLG88104

20 Lead STQFN Package

000-0088103/4-101

Page 16 of 22

�SLG88103/4

Recommended Land Pattern - SLG88103

Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.2 mm3 (nominal). More

information can be found at www.jedec.org.

000-0088103/4-101

Page 17 of 22

�SLG88103/4

Recommended Land Pattern - SLG88104

Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.85 mm3 (nominal). More

information can be found at www.jedec.org.

000-0088103/4-101

Page 18 of 22

�SLG88103/4

Tape and Reel Specifications

Max Units

Leader (min)

Nominal

Reel &

Package # of

Package Size

Hub Size

Length

Type

Pins

per Reel per Box

Pockets

[mm]

[mm]

[mm]

Trailer (min)

Pockets

Length

[mm]

Tape

Width

[mm]

Part

Pitch

[mm]

STDFN

10L

2x2mm

0.4P COL

Green

10

2 x 2 x 0.55

3000

3000

178 / 60

100

400

100

400

8

4

STQFN

20L

2x3.5mm

0.4P

Green

20

2 x 3.5 x 0.55

5000

10000

330 /100

42

336

42

336

12

8

Carrier Tape Drawing and Dimensions - SLG88103

Package

Type

STDFN 10L

2x2mm 0.4P

COL Green

Pocket BTM Pocket BTM

Length

Width

Pocket

Depth

Index Hole

Pitch

Pocket

Pitch

Index Hole

Diameter

Index Hole Index Hole

to Tape

to Pocket Tape Width

Edge

Center

A0

B0

K0

P0

P1

D0

E

F

W

2.2

2.2

0.83

4

4

1.55

1.75

3.5

8

Refer to EIA-481 specification

000-0088103/4-101

Page 19 of 22

�SLG88103/4

Carrier Tape Drawing and Dimensions Dimensions - SLG88104

Pocket BTM Pocket BTM

Package

Length

Width

Type

STQFN 20L

2x3.5mm

0.4P Green

Pocket

Depth

Index Hole

Pitch

Pocket

Pitch

Index Hole

Diameter

Index Hole Index Hole

to Tape

to Pocket Tape Width

Edge

Center

A0

B0

K0

P0

P1

D0

E

F

W

2.2

3.8

0.8

4

8

1.5

1.75

5.5

12

Refer to EIA-481 specification

000-0088103/4-101

Page 20 of 22

�SLG88103/4

Revision History

Date

Version

3/13/2017

1.01

Replaced Slew Rate vs. Ambient Temperature Chart

Fixed Chart formatting for some charts.

Fixed typos

3/1/2017

1.00

Production Release

000-0088103/4-101

Change

Page 21 of 22

�SLG88103/4

Silego Website & Support

Silego Technology Website

Silego Technology provides online support via our website at http://www.silego.com/.This website is used as a means to make

files and information easily available to customers.

For more information regarding Silego Green products, please visit:

GreenPAK

GreenFET

GreenCLK

http://greenpak.silego.com/

http://greenfet.silego.com/

http://greenclk.silego.com/

http://greenpak2.silego.com/

http://greenfet2.silego.com/

http://greenclk2.silego.com/

http://greenpak3.silego.com/

http://greenfet3.silego.com/

http://greenclk3.silego.com/

Products are also available for purchase directly from Silego at the Silego Online Store at http://store.silego.com/.

Silego Technical Support

Datasheets and errata, application notes and example designs, user guides, and hardware support documents and the latest

software releases are available at the Silego website or can be requested directly at info@silego.com.

For specific GreenPAK design or applications questions and support please send e-mail requests to GreenPAK@silego.com

Users of Silego products can receive assistance through several channels:

Online Live Support

Silego Technology has live video technical assistance and sales support available at http://www.silego.com/. Please ask our live

web receptionist to schedule a 1 on 1 training session with one of our application engineers.

Contact Your Local Sales Representative

Customers can contact their local sales representative or field application engineer (FAE) for support. Local sales offices are also

available to help customers. More information regarding your local representative is available at the Silego website or send a

request to info@silego.com

Contact Silego Directly

Silego can be contacted directly via e-mail at info@silego.com or user submission form, located at the following URL:

http://support.silego.com/

Other Information

The latest Silego Technology press releases, listing of seminars and events, listings of world wide Silego Technology offices and

representatives are all available at http://www.silego.com/

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE

SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. SILEGO TECHNOLOGY DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. SILEGO TECHNOLOGY RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY

WITHOUT NOTICE.

000-0088103/4-101

Page 22 of 22

�