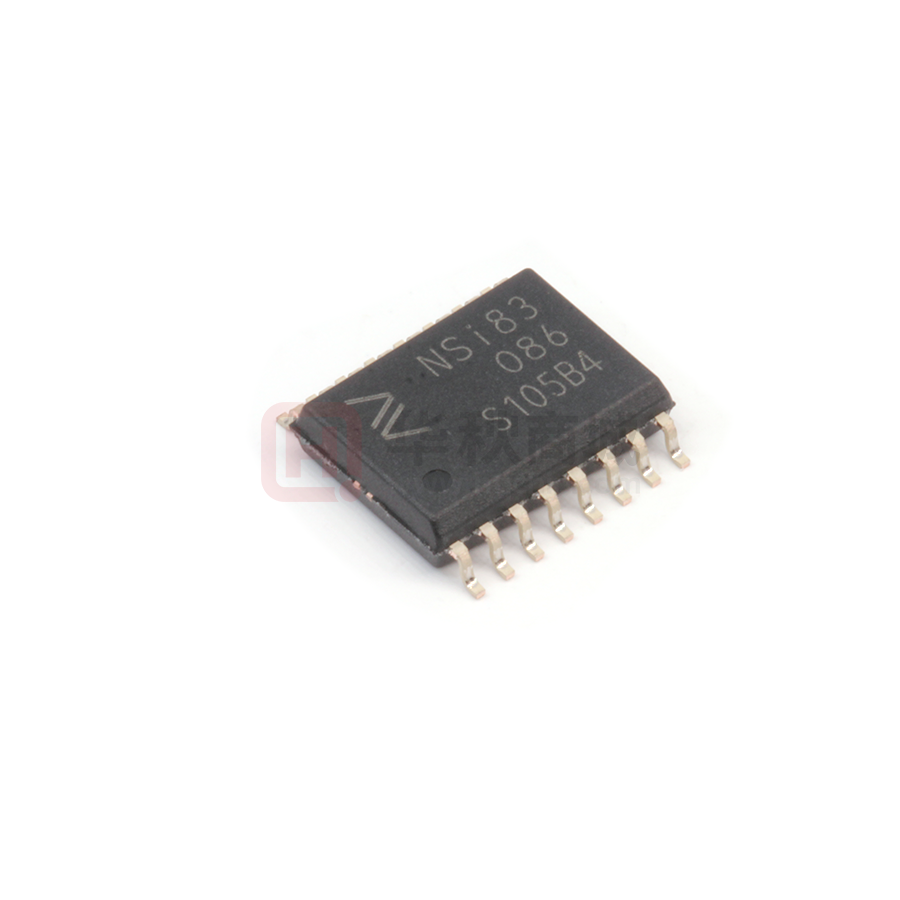

NSi83085/NSi83086: High Reliability Isolated

Half and Full-Duplex RS-485 Transceivers

NOVOSENSE

Datasheet (EN) 1.6

Product Overview

NSi83085 is a high reliability isolated half duplex RS-485

transceiver based on NOVOSENSE digital isolation

technology, while NSi83086 is an isolated full duplex RS485 transceiver. Both devices are safety certified by

UL1577 support 5kVrms insulation withstand voltages,

while providing high electromagnetic immunity and low

emissions at low power consumption.

The Bus pins of NSi83085/NSi83086 are protected from

±16kV system level ESD to GND2 on Bus side. These

devices feature fail-safe circuitry, which guarantees a

logic-high receiver output when the receiver inputs are

open or shorted. The devices have a 1/8-unit-load

receiver input impedance that allows up to 256

transceivers on the bus.

The data rate of NSi83085 is 500kbps. The device is slew

limited to reduce EMI and reflections with improperly

terminated transmission line. The data rate of NSi83086 is

up to 16Mbps.

Key Features

Up to 5000Vrms Insulation voltage

Bus side power supply voltage: 3.0V to 5.5V

VDD1 supply voltage: 2.5V to 5.5V

High CMTI: ±150kV/us

High system level EMC performance:

Safety Regulatory Approvals

UL recognition: up to 5000Vrms for 1 minute per UL1577

CQC certification per GB4943.1-2011

CSA component notice 5A

DIN VDE V 0884-11:2017-01

Applications

Industrial automation system

Isolated RS-485 communication

Smart electric meter and water meter

Security and protection monitoring

Functional Block Diagrams

Bus Pins meet IEC61000-4-2 ±16kV ESD

Other Pins meet ±7kV contact ESD

Fail-safe protection receiver

NSi83085 has slew rate limitation

Up to 256 transceivers on the bus

Isolation Barrier Life: >60 years

Operation temperature: -40℃~105℃

RoHS-compliant packages:

Figure 1. NSi83085 & NSi83086 Block Diagrams

SOIC-16 wide body

Copyright © 2019, NOVOSENSE

Page 1

�NSi83085/NSi83086

Index

1.0 ABSOLUTE MAXIMUM RATINGS................................................................................................................................................ 3

2.0 SPECIFICATIONS.......................................................................................................................................................................... 3

2.1. DC ELECTRICAL CHARACTERISTICS....................................................................................................................................................3

2.2. SWITCHING ELECTRICAL CHARACTERISTICS......................................................................................................................................... 5

2.3. TYPICAL PERFORMANCE CHARACTERISTICS................................................................................................................................. 7

2.4. PARAMETER MEASUREMENT INFORMATION...................................................................................................................................... 9

3.0 HIGH VOLTAGE FEATURE DESCRIPTION................................................................................................................................... 10

3.1. INSULATION AND SAFETY RELATED SPECIFICATIONS............................................................................................................................ 10

3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICS.......................................................................... 11

3.3. REGULATORY INFORMATION......................................................................................................................................................... 12

4.0 FUNCTION DESCRIPTION..........................................................................................................................................................13

4.1. DATA RATE................................................................................................................................................................................13

4.2. TRUE FAIL-SAFE RECEIVER INPUTS.................................................................................................................................................. 13

4.3. TRUTH TABLES........................................................................................................................................................................... 13

4.4. THERMAL SHUTDOWN.................................................................................................................................................................14

5.0 APPLICATION NOTE...................................................................................................................................................................14

5.1. 256 TRANSCEIVERS ON THE BUS................................................................................................................................................... 14

5.2. ESD PROTECTION.......................................................................................................................................................................14

5.3. LAYOUT CONSIDERATIONS............................................................................................................................................................14

5.4. TYPICAL APPLICATION..................................................................................................................................................................14

6.0 PACKAGE INFORMATION..........................................................................................................................................................16

7.0 TAPE AND REEL INFORMATION................................................................................................................................................ 18

8.0 ORDER INFORMATION............................................................................................................................................................. 20

9.0 REVISION HISTORY.................................................................................................................................................................... 20

Copyright © 2019, NOVOSENSE

Page 2

�NSi83085/NSi83086

1.0

ABSOLUTE MAXIMUM RATINGS

Parameters

Symbol

Min

Power Supply Voltage

VDD1, VDD2

-0.5

6

V

Maximum Input Voltage

/RE, DE, TxD

-0.4

VDD+0.4

V

CMTI

-150

150

kV/us

VA, VB, VY, VZ

-7

12

V

Receiver Output Current

Io

-15

15

mA

Maximum Surge Isolation

Voltage

VIOSM

5.3

kV

Operating Temperature

Topr

-40

105

℃

Storage Temperature

Tstg

-40

150

℃

HBM (Bus

pins and GND)

±8000

V

HBM(All pins)

±6000

V

CDM

±2000

V

Common-Mode Transients

Driver Output/Receiver Input

Voltage

Electrostatic discharge

2.0

Typ

Max

Unit

Comments

SPECIFICATIONS

2.1. DC ELECTRICAL CHARACTERISTICS

(VDD1=2.5V~5.5V, VDD2=3.0V~5.5V, Ta=-40℃ to 105℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta =

25℃)

Parameters

Power supply voltage

Symbol

Min

VDD1

VDD 2

Logic-side supply current

IDD1

Bus-side supply current

IDD2

Thermal-Shutdown Threshold

Copyright © 2019, NOVOSENSE

TTS

Typ

Max

Unit

2.5

5.5

V

3.0

5.5

V

Bus Side

3.32

4.98

mA

VDD1=5V, DE=high, /RE=D

=low, no load

3.26

4.89

mA

VDD1=3V, DE=high, /RE=D

=low, no load

3.35

5.02

mA

VDD2=5V, DE=high, /RE=D

=low, no load(NSi83085)

2.15

3.23

mA

VDD2=5V, DE=high, /RE=D

=low, no load(NSi83085)

165

Comments

℃

Page 3

�NSi83085/NSi83086

Thermal-Shutdown Hysteresis

Common Mode Transient

Immunity

TTSH

15

CMTI

±100

Input High Voltage

VIH

2

Input Low Voltage

VIL

℃

±150

kV/us

Logic Side

0.8

V

DE, D, /RE

V

DE, D, /RE

VIT

1.6

V

Input Threshold at rising

edge

VIT_HYS

0.4

V

Input Threshold Hysteresis

uA

DE,/RE

Input Threshold

Input Pull up Current

IPU

20

Input Pull down Current

IPD

-15

uA

DI

Output Voltage High

VOH

VDD10.3

V

IOH = -4mA

Output Voltage Low

VOL

0.3

V

IOL = 4mA

Output Short-Circuit Current

IOSR

150

mA

0 ≤ VR ≤VDD1

Three-State Output Current

IOZ

uA

0 ≤ VR ≤ VDD1 , /RE = high

Input Capacitance

CIN

pF

DE, D, /RE

VDD2

V

No Load

2.7

VDD2

V

See Figure 2.4.1, RL=100Ω

(RS-422),VDD2=5V

1.5

VDD2

V

See Figure 2.4.1, RL=100Ω

(RS-422),VDD2=3.3V

2.1

VDD2

V

See Figure 2.4.1, RL=54Ω (RS485),VDD2=5V

1.3

VDD2

V

See Figure 2.4.1, RL=54Ω (RS485),VDD2=3.3V

0.2

V

See Figure 2.4.1, RL=100Ω or

RL=54Ω

3

V

See Figure 2.4.1, RL=100Ω or

RL=54Ω

0.2

V

See Figure 2.4.1, RL=100Ω or

RL=54Ω

250

mA

0 ≤ VOUT ≤ +12 V

mA

−7V ≤ VOUT ≤ VDD2

uA

DE=GND, VIN=12V

-15

2

Driver

Differential Output Voltage

Change in magnitude of the

| VOD |

Δ|VOD |

differential output voltage

Common-Mode Output

Voltage

| VOC |

Change in Magnitude of

Δ|VOC |

VDD2/2

Common-Mode Voltage

Driver Short-Circuit Output

Current

Output Leakage Current (Y and

Copyright © 2019, NOVOSENSE

IOSD

IO

-250

125

Page 4

�NSi83085/NSi83086

Z) Full-Duplex

-75

uA

DE=GND, VIN=-7V

uA

DE=GND, VDD2=GND,

VIN=12V

uA

DE=GND, VDD2=GND, VIN=7V

mV

−7V ≤ VCM ≤ 12V

mV

VA+VB=0

kΩ

−7V ≤ VCM ≤ 12V, DE=low

Receiver

IA , IB

125

Input Current (A and B)

-200

Receiver Differential Threshold

Voltage

VTH

-200

Receiver Input Hysteresis

ΔVTH

Receiver Input Resistance

RIN

-125

-50

15

96

2.2. SWITCHING ELECTRICAL CHARACTERISTICS

(VDD1=2.5V~5.5V, VDD2=3.0V~5.5V, Ta=-40℃ to 105℃. Unless otherwise noted, Typical values are at VDD1 = 5V, VDD2 = 5V, Ta =

25℃)

Parameters

Symbol

Min

Typ

Max

Unit

Comments

Maximum Data Rate

fMAX

0.5

Driver Propagation Delay

t PLH

450

675

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

t PHL

430

645

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

PWD

20

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

tF

590

885

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

tR

590

885

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

Driver Enable to Output High

tZH

310

465

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Enable to Output Low

tZL

310

465

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Output High to Disable

tHZ

30

45

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Output Low to Disable

tLZ

30

45

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver (NSi83085)

Driver Pulse Width Distortion,|t PHL

– t PLH |

Driver Output Falling Time or

Rising time

Mbps

Receiver (NSi83085)

Copyright © 2019, NOVOSENSE

Page 5

�NSi83085/NSi83086

Maximum Data Rate

fMAX

0.5

Mbps

Receiver Propagation Delay

t PLH

102

153

ns

See Figure 2.4.4, CL=15pF

t PHL

92

138

ns

See Figure 2.4.4, CL=15pF

Receiver Pulse Width Distortion

PWD

10

ns

|t PHL – t PLH |,See Figure

2.4.4, CL=15pF

Receiver Output Falling Time or

Rising time

tF

2.5

3.75

ns

See Figure 2.4.4, CL=15pF

tR

2.5

3.75

ns

See Figure 2.4.4, CL=15pF

Receiver Enable to Output High

tZH

18.5

27.75

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Enable to Output Low

tZL

18.5

27.75

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Disable to Output High

tHZ

23

34.5

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Disable to Output Low

tLZ

23

34.5

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Driver (NSi83086)

Maximum Data Rate

fMAX

Driver Propagation Delay

t PLH

12

18

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

t PHL

13.5

20.25

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

PWD

1.5

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

tF

2.95

4.425

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

tR

2.6

3.9

ns

See Figure 2.4.2,

RL=54Ω,CL=50pF

Driver Enable to Output High

tZH

18.5

27.75

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Enable to Output Low

tZL

19.1

28.65

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Disable to Output High

tHZ

20.8

31.2

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Disable to Output Low

tLZ

20.1

30.15

ns

See Figure 2.4.3,

RL=110Ω,CL=50pF

Driver Pulse Width Distortion,|t PHL

– t PLH |

Driver Output Falling Time or

Rising time

16

Mbps

Receiver (NSi83086)

Maximum Data Rate

Copyright © 2019, NOVOSENSE

fMAX

16

Mbps

Page 6

�NSi83085/NSi83086

Receiver Propagation Delay

t PLH

16.2

24.3

ns

See Figure 2.4.4, CL=15pF

t PHL

22.2

33.3

ns

See Figure 2.4.4, CL=15pF

PWD

6.0

ns

See Figure 2.4.4, CL=15pF

tF

2.3

3.45

ns

See Figure 2.4.4, CL=15pF

tR

2.1

3.15

ns

See Figure 2.4.4, CL=15pF

Receiver Enable to Output High

tZH

13.8

20.7

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Enable to Output Low

tZL

12.6

18.9

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Disable to Output High

tHZ

14

21

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Disable to Output Low

tLZ

13.4

20.1

ns

See Figure 2.4.5,

RL=1kΩ,CL=15pF

Receiver Pulse Width Distortion, |t

PHL – t PLH |

Receiver Output Falling Time or

Rising time

2.3. TYPICAL PERFORMANCE CHARACTERISTICS

Figure 2.1 NSi83085 VDD1 supply current vs Temperature

Copyright © 2019, NOVOSENSE

Figure 2.2 NSi83085 VDD2 supply current vs Temperature

Page 7

�NSi83085/NSi83086

Figure 2.3 NSi83086 VDD1 supply current vs Temperature

Figure 2.5 Receiver output current vs Output low voltage

Figure 2.9 NSi83085 Transmitter Propagation Delay vs Temperature

Figure 2.11 NSi83086 Transmitter Propagation Delay vs Temperature

Copyright © 2019, NOVOSENSE

Figure 2.4 NSi83086 VDD2 supply current vs Temperature

Figure 2.6 Receiver output current vs Output High voltage

Figure 2.10 NSi83085 Receiver Propagation Delay vs Temperature

Figure 2.12 NSi83086 Receiver Propagation Delay vs Temperature

Page 8

�NSi83085/NSi83086

2.4. PARAMETER MEASUREMENT INFORMATION

Figure 2.4.1 Driver DC Test Load

Figure 2.4.2 Driver Timing Test Circuit and waveform

Figure 2.4.3 Driver Enable Disable Timing Test Circuit and waveform

Figure 2.4.4 Receiver Propagation Delay Test Circuit and waveform

Copyright © 2019, NOVOSENSE

Page 9

�NSi83085/NSi83086

Figure 2.4.5 Receiver Enable Disable Timing Test Circuit and waveform

Figure 2.4.6 Common-Mode Transient Immunity Test Circuit

3.0

HIGH VOLTAGE FEATURE DESCRIPTION

3.1. INSULATION AND SAFETY RELATED SPECIFICATIONS

Parameters

Symbol

Value

Unit

Comments

Minimum External Air Gap

(Clearance)

L(I01)

8.0

mm

Shortest terminal-to-terminal

distance through air

Minimum External Tracking

(Creepage)

L(I02)

8.0

mm

Shortest terminal-to-terminal

distance across the package

surface

Minimum internal gap

DTI

20

um

Distance through insulation

Tracking Resistance(Comparative

Tracking Index)

CTI

>400

V

DIN EN 60112 (VDE 0303-11);

IEC 60112

Material Group

Copyright © 2019, NOVOSENSE

Ⅱ

Page 10

�NSi83085/NSi83086

3.2. DIN VDE V 0884-11(VDE V 0884-11):2017-01 INSULATION CHARATERISTICS

Description

Test Condition

Symbol

Value

Unit

Installation Classification per DIN VDE 0110

For Rated Mains Voltage ≤ 150Vrms

Ⅰto Ⅳ

For Rated Mains Voltage ≤ 400Vrms

Ⅰto Ⅳ

For Rated Mains Voltage ≤ 300Vrms

Ⅰto Ⅳ

Climatic Classification

10/105/21

Pollution Degree per DIN VDE 0110, Table 1

2

Maximum repetitive isolation voltage

AC Voltage(Bipolar)

VIORM

1131

Vpeak

AC Voltage(TDDB)

VIORM

800

Vrms

DC Voltage

VIORM

1131

Vdc

V IORM × 1.5 = V pd (m) , 100%

production test,

V pd (m)

1273

Vpeak

V pd (m)

1019

Vpeak

V pd (m)

1019

Vpeak

t = 60 sec

VIOTM

7000

Vpeak

Test method per

IEC60065,1.2/50us waveform,

VTEST=1.3×VIOSM

VIOSM

5384

Vpeak

Isolation resistance

VIO =500V

RIO

>109

Ω

Isolation capacitance

f = 1MHz

CIO

0.6

pF

Input capacitance

CI

2

pF

Total Power Dissipation at 25℃

Ps

1499

mW

Input to Output Test Voltage, Method B1

t ini = t m = 1 sec, partial

discharge < 5 pC

Input to Output Test Voltage, Method A

After Environmental Tests Subgroup 1

After Input and /or Safety Test Subgroup 2 and

Subgroup 3

Maximum transient isolation voltage

Maximum Surge Isolation Voltage

Safety input, output, or supply current

Case Temperature

Copyright © 2019, NOVOSENSE

V IORM × 1.2 = V pd (m) , t ini = 60

sec, t m = 10 sec, partial

discharge < 5 pC

V IORM × 1.2= V pd (m) , t ini = 60

sec, t m = 10 sec, partial

discharge < 5 pC

θJA = 140 °C/W, V I = 5.5 V,

T J = 150 °C, T A = 25 °C

θJA = 84 °C/W, V I = 5.5 V, T J =

150 °C, T A = 25 °C

mA

Is

Ts

237

mA

150

℃

Page 11

�NSi83085/NSi83086

Figure 3.1 NSi83085/NSi83086 Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN VDE V 0884-11

Figure 3.2 NSi83085/NSi83086 Thermal Derating Curve, Dependence of Safety Limiting Values with Case Temperature per DIN VDE V 0884-11

3.3. REGULATORY INFORMATION

The NSi83085/NSi83086 are approved or pending approval by the organizations listed in table.

CUL

UL 1577 Component

Recognition Program1

Single Protection, 5000Vrms

Isolation voltage

VDE

Approved under CSA

Component Acceptance

Notice 5A

DIN VDE V 0884-11(VDE V

0884-11):2017-012

Single Protection, 5000Vrms

Isolation voltage

Basic Insulation 1131Vpeak,

VIOSM=5384Vpeak

CQC

Certified by CQC11471543-2012

GB4943.1-2011

Basic insulation at 800VRMS

(1131Vpeak)

Reinforced insulation at

400VRMS (565Vpeak)

File (E500602)

1

File (E500602)

File (5024579-4880-0001)

File (pending)

In accordance with UL 1577, each NSi83085/NSi83086 is proof tested by applying an insulation test voltage ≥ 6000 V rms for 1 sec.

2

In accordance with DIN VDE V 0884-11, each NSi8100W/NSi8101W is proof tested by applying an insulation test voltage ≥ 1273 V peak for 1 sec (partial

discharge detection limit = 5 pC). The * marking branded on the component designates DIN VDE V 0884-11 approval.

Copyright © 2019, NOVOSENSE

Page 12

�NSi83085/NSi83086

4.0

FUNCTION DESCRIPTION

NSi83085 is a high reliability isolated half duplex RS-485 transceiver , while NSi83086 is an isolated full duplex RS-485 transceiver. Data

isolation is achieved using Novosense integrated capacitive isolation that allows data transmission between the logic side and the Bus

side. Both devices are safety certified by UL1577 support 5kVRMS insulation withstand voltages.

4.1. DATA RATE

The data rate of NSi83085 is 500kbps. The device is slew limited to reduce EMI and reflections with improperly terminated

transmission line. The data rate of NSi83086 is up to 16Mbps.

4.2. TRUE FAIL-SAFE RECEIVER INPUTS

The devices feature fail-safe circuitry, which guarantees a logic-high receiver output when the receiver inputs are open or shorted. The

receiver threshold is fixed between -50mV and -200mV, which meets EIA/TIA-485 standard. If the differential input voltage (VA-VB) is

greater than or equal to -50mV, receiver output R is logic high. In the case of a terminated bus with all transmitters disabled, the

differential input voltage is pulled to zero by the termination resistors. Due to the receiver threshold, the receiver output R is logic high.

4.3. TRUTH TABLES

Table 4.1 Driver Function Table

VDD1 status

VDD2 status

Input

Enable Input

(D)

(DE)

Outputs1

A/Y

B/Z

PU

PU

H

H

H

L

PU

PU

L

H

L

H

PU

PU

X

L

Z

Z

PU

PU

X

OPEN

Z

Z

PU

PU

OPEN

H

H

L

PD

PU

X

X

Z

Z

PU

PD

X

X

Z

Z

PD

PD

X

X

Z

Z

PD= Powered down; PU= Powered up; H= Logic High; L= Logic Low; X= Irrelevant; Z= High Impedance; Driver output pins are Y and Z for NSi83086, A and

B for NSi83085;

1

Table 4.2 Reciever Function Table1

VDD1 status

VDD2 status

Differential Input

Enable Input

Output

(VA-VB)

(/RE)

(R)

L/Open

H

PU

≥-50mV

L/Open

L

PU

PU

≤-200mV

Open/Short

L/Open

H

PU

PU

X

H

Z

PU

PU

Idle

L

H

PD

PU

X

X

Z

PU

PU

PU

Copyright © 2019, NOVOSENSE

Page 13

�NSi83085/NSi83086

1

PU

PD

X

X

H

PD

PD

X

X

Z

PD= Powered down; PU= Powered up; H= Logic High; L= Logic Low; X= Irrelevant; Z= High Impedance.

4.4. THERMAL SHUTDOWN

The device is protected from over temperature damage by integrated thermal shutdown circuitry. When the junction temperature (TJ)

exceeds +165°C (typ), the driver outputs go high-impedance. The device resumes normal operation when TJ falls below +145°C (typ).

5.0

APPLICATION NOTE

5.1. 256 TRANSCEIVERS ON THE BUS

The devices have a 1/8-unit-load receiver input impedance (96kΩ) that allows up to 256 transceivers on the bus. Connect any

combination of these devices, and/or other RS-485 devices, for a maximum of 32 unit-loads to the line.

5.2. ESD PROTECTION

ESD protection structures are enhanced on all pins to protect against electrostatic discharge encountered during handing and assembly.

The Bus pins have extra protection against static electricity to both the logic side (VDD1 side) and bus side (VDD2 side).

ESD protection can be tested in various ways. Below is the ESD spec of the devices.

Bus pins:

± 8kV HBM.

±16kV using the Contact Discharge method specified in IEC 61000-4-2

Other pins except bus pins:

±6kV HBM.

±7kV using the Contact Discharge method specified in IEC 61000-4-2

5.3. LAYOUT CONSIDERATIONS

The NSi83085/NSi83086 requires a 0.1 µF bypass capacitor between VDD1 and GND1, 10uF bypass capacitor between VDD2 and

GND2. The capacitor should be placed as close as possible to the package. To eliminate line reflections, each cable end is terminated

with a resistor, whose value matches the characteristic impedance of the cable. It’s good practice to have the bus connectors and

termination resistor as close as possible to the A and B, Y and Z pins.

5.4. TYPICAL APPLICATION

Figure 5.1 NSi83085 typical application circuit

Copyright © 2019, NOVOSENSE

Page 14

�NSi83085/NSi83086

Figure 5.2 Typical isolated Half-Duplex RS-485 application

Figure 5.3 NSi83086 typical application circuit

Figure 5.4 Typical isolated Full-Duplex RS-485 application

Copyright © 2019, NOVOSENSE

Page 15

�NSi83085/NSi83086

6.0

PACKAGE INFORMATION

Figure 6.1 NSi83085 Package

Figure 6.2 NSi83086 Package

Figure 6.3 SOIC16 Package Shape and Dimension

Copyright © 2019, NOVOSENSE

Page 16

�NSi83085/NSi83086

Dimensions shown in millimeters and (inches)

Table6.1 NSi83085 Pin Configuration and Description

NSi83085

PIN NO.

SYMBOL

FUNCTION

1

VDD1

Power Supply for Isolator Side 1

2

GND1

Ground 1, the ground reference for Isolator Side 1

3

R

Receive output

4

/RE

Receive enable input. This is an active low input.

5

DE

Driver enable input. This is an active high input

6

D

Driver transmit data input.

7

GND1

Ground 1, the ground reference for Isolator Side 1

8

GND1

Ground 1, the ground reference for Isolator Side 1

9

GND2

Ground 2, the ground reference for Isolator Side 2

10

GND2

Ground 2, the ground reference for Isolator Side 2

11

NC

No Connection.

12

A

Noninverting Driver Output/Receiver Input. When the driver is disabled, or when VDD1

or VDD2 is powered down, Pin A is put into a high impedance state to avoid overloading

the bus.

13

B

Inverting Driver Output/Receiver Input. When the driver is disabled, or when VDD1 or

VDD2 is powered down, Pin B is put into a high impedance state to avoid overloading

the bus.

14

NC

No Connection.

15

GND2

Ground 2, the ground reference for Isolator Side 2

16

VDD2

Power Supply for Isolator Side 2

Table6.2 NSi83086 Pin Configuration and Description

NSi83086

PIN NO.

SYMBOL

FUNCTION

1

VDD1

Power Supply for Isolator Side 1

2

GND1

Ground 1, the ground reference for Isolator Side 1

3

R

Receive output

4

/RE

Receive enable input. This is an active low input.

5

DE

Driver enable input. This is an active high input

6

D

Driver transmit data input.

Copyright © 2019, NOVOSENSE

Page 17

�NSi83085/NSi83086

7.0

7

GND1

Ground 1, the ground reference for Isolator Side 1

8

GND1

Ground 1, the ground reference for Isolator Side 1

9

GND2

Ground 2, the ground reference for Isolator Side 2

10

GND2

Ground 2, the ground reference for Isolator Side 2

11

Y

Noninverting Driver Output. When the driver is disabled, or when VDD1 or VDD2 is

powered down, Pin Y is put into a high impedance state to avoid overloading the bus.

12

Z

Inverting Driver Output. When the driver is disabled, or when VDD1 or VDD2 is powered

down, Pin Z is put into a high impedance state to avoid overloading the bus.

13

B

Inverting Receiver Input.

14

A

Noninverting Receiver Input.

15

GND2

Ground 2, the ground reference for Isolator Side 2

16

VDD2

Power Supply for Isolator Side 2

TAPE AND REEL INFORMATION

Copyright © 2019, NOVOSENSE

Page 18

�NSi83085/NSi83086

Figure 7.1 Tape and Reel Information of WB SOIC16

Copyright © 2019, NOVOSENSE

Page 19

�NSi83085/NSi83086

8.0

ORDER INFORMATION

Part No.

Duplex

NSi83085

Isolation

Rating(kVRMS)

5

Temperature

No. of Nodes

Package

Half

Max Data Rate

(MHz)

0.5

-40 to 105℃

256

WB SOIC16

NSi83086

5

Full

16

-40 to 105℃

256

WB SOIC16

NSi83086H

5

Full

16

WB SOIC16

-40 to 105℃ 256

NOTE: All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard

classifications and peak solder temperatures.

9.0

REVISION HISTORY

Revision

1.0

1.2

1.3

1.4

1.5

Description

Added NSi83086 spec

Changed table 3.1 VDE insulation Characteristics

Changed Certification Information

Changed operation temperature range, changed supply voltage

range,Updated VIORM Spec according to VDE Certification.

Copyright © 2019, NOVOSENSE

Date

2018/7/15

2018/10/15

2018/12/20

2019/06/17

2020/8/7

Page 20

�