ES7243E

High Performance Stereo Audio ADC

FEATURES

•

•

•

•

•

•

•

•

•

•

•

APPLICATIONS

High performance multi-bit delta-sigma

audio ADC

101 dB signal to noise ratio

-90 dB THD+N

Low noise PGA

24-bit, 8 to 48 kHz sampling frequency

I2S/PCM master or slave serial data port

Support TDM up to 16 channels

256/384Fs, USB 12/24 MHz and other

non standard audio system clocks

Auto level control (ALC) and noise gate

Support digital mic

Low power

•

•

•

•

•

•

•

Mic Array

Soundbar

Audio Interface

Digital TV

A/V Receiver

DVR

NVR

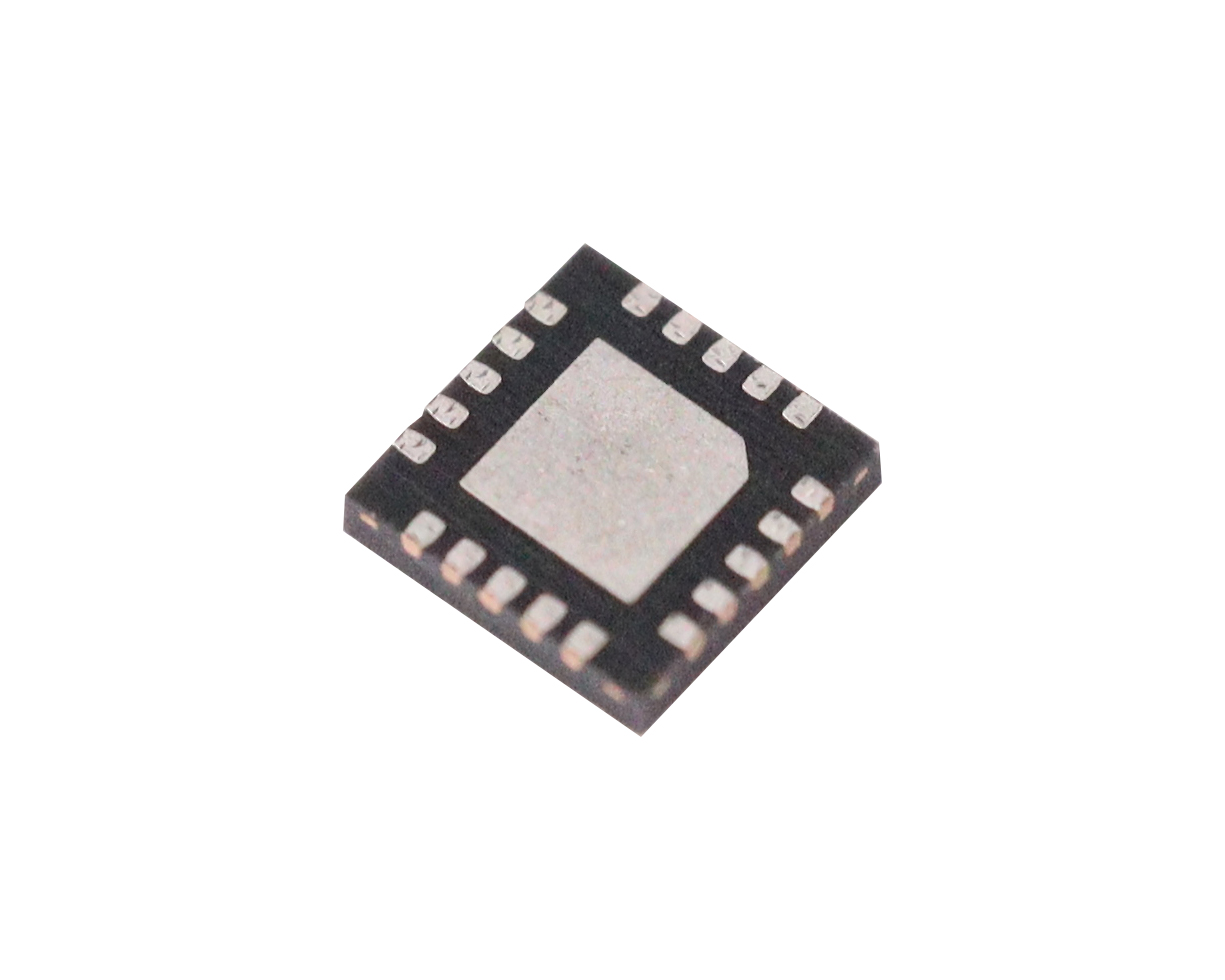

ORDERING INFORMATION

ES7243E -40°C ~ +85°C

QFN-20

BLOCK DIAGRAM

TDMIN

AINLP/AINLN

AINRP/AINRN

Multi-bit

Delta-sigma

Modulator

DSP

Audio

Data

Interface

2

Clock Manager

Sample Rate Detector

IC

Interface

MCLK

CCLK CDATA AD0 AD1

1

SDOUT/AD2

SCLK

LRCK

�Everest Semiconductor

1.

2.

3.

4.

5.

6.

Confidential

ES7243E

PIN OUT AND DESCRIPTION ................................................................................................ 4

TYPICAL APPLICATION CIRCUIT.......................................................................................... 5

CLOCK MODES AND SAMPLING FREQUENCIES ............................................................... 6

MICRO-CONTROLLER CONFIGURATION INTERFACE ...................................................... 6

DIGITAL AUDIO INTERFACE.................................................................................................. 8

ELECTRICAL CHARACTERISTICS ..................................................................................... 10

ABSOLUTE MAXIMUM RATINGS................................................................................................ 10

RECOMMENDED OPERATING CONDITIONS .............................................................................. 10

Note: for VDDD=1.8V, sampling frequency must be less than 24 kHz. ..................................... 10

ADC ANALOG AND FILTER CHARACTERISTICS AND SPECIFICATIONS ........................................ 10

DC CHARACTERISTICS ................................................................................................................ 11

I2C SWITCHING SPECIFICATIONS (SLOW SPEED MODE/HIGH SPEED MODE) ........................... 11

SERIAL AUDIO PORT SWITCHING SPECIFICATIONS ................................................................... 12

7.

CONFIGURATION REGISTER DEFINITION ........................................................................ 13

REGISTER 0X00 –RESET, DEFAULT 0001 1110 ........................................................................... 13

REGISTER 0X01 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 13

REGISTER 0X02 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 13

REGISTER 0X03 – CLOCK MANAGER, DEFAULT 0010 0000 ....................................................... 14

REGISTER 0X04 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 14

REGISTER 0X05 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 14

REGISTER 0X06 – CLOCK MANAGER, DEFAULT 0000 0011 ....................................................... 14

REGISTER 0X07 – CLOCK MANAGER, DEFAULT 0000 0001 ....................................................... 15

REGISTER 0X08 – CLOCK MANAGER, DEFAULT 1111 1111 ....................................................... 15

REGISTER 0X09 – CLOCK MANAGER, DEFAULT 1100 0001 ....................................................... 15

REGISTER 0X0A – SDP, DEFAULT 1000 0001 ............................................................................. 15

REGISTER 0X0B – SDP, DEFAULT 1100 0000.............................................................................. 16

REGISTER 0X0C – SDP, DEFAULT 0000 0000.............................................................................. 16

REGISTER 0X0D – ADC CONTROL, DEFAULT 0000 0000 ............................................................ 17

REGISTER 0X0E – ADC CONTROL, DEFAULT 0000 0000............................................................. 17

REGISTER 0X0F – ADC CONTROL, DEFAULT 0000 0000 ............................................................. 17

REGISTER 0X10 – ADC CONTROL, DEFAULT 0000 0000............................................................. 18

REGISTER 0X11 – ADC CONTROL, DEFAULT 0000 0000............................................................. 18

REGISTER 0X12 – ADC CONTROL, DEFAULT 0000 0000............................................................. 19

REGISTER 0X13 – ADC CONTROL, DEFAULT 0000 0000............................................................. 19

REGISTER 0X14 – ADC CONTROL, DEFAULT 0000 1100............................................................. 20

Revision 2.0

2

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

REGISTER 0X15 – ADC CONTROL, DEFAULT 0000 1100............................................................. 20

REGISTER 0X16 – ANALOG, DEFAULT 1111 1111 ...................................................................... 20

REGISTER 0X17 – ANALOG, DEFAULT 0000 0000 ...................................................................... 20

REGISTER 0X18 – ANALOG, DEFAULT 0010 0100 ...................................................................... 20

REGISTER 0X19 – ANALOG, DEFAULT 1000 1000 ...................................................................... 21

REGISTER 0X1A – ANALOG, DEFAULT 0100 0100 ...................................................................... 21

REGISTER 0X1B – ANALOG, DEFAULT 0100 0100 ...................................................................... 22

REGISTER 0X1C – ANALOG, DEFAULT 0100 0100 ...................................................................... 23

REGISTER 0X1D – ANALOG, DEFAULT 0000 0000...................................................................... 23

REGISTER 0X1E – ANALOG, DEFAULT 0000 0101 ...................................................................... 24

REGISTER 0X1F – ANALOG, DEFAULT 0000 1100 ...................................................................... 24

REGISTER 0X20 – ANALOG, DEFAULT 0000 0000 ...................................................................... 24

REGISTER 0X21 – ANALOG, DEFAULT 0000 0000 ...................................................................... 25

REGISTER 0XF7 – TEST MODE, DEFAULT 1111 0000 ................................................................. 25

REGISTER 0XF8 – TEST MODE, DEFAULT 0000 0000 ................................................................. 26

REGISTER 0XF9 – TEST MODE, DEFAULT 0000 0000 ................................................................. 26

REGISTER 0XFA – I2C CONFIGURE, DEFAULT 0000 0000........................................................... 26

REGISTER 0XFC – FLAG, DEFAULT 0000 0000 ............................................................................ 26

REGISTER 0XFD – CHIP ID1, DEFAULT 0111 1010 ...................................................................... 26

REGISTER 0XFE – CHIP ID2, DEFAULT 0100 0011 ...................................................................... 26

REGISTER 0XFF – CHIP VERSION, DEFAULT 0000 0000 ............................................................. 27

8.

9.

PACKAGE .............................................................................................................................. 28

CORPORATE INFORMATION .............................................................................................. 29

Revision 2.0

3

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

1. PIN OUT AND DESCRIPTION

AINRP

AD0

CDATA

CCLK

MCLK

16

17

18

19

20

VDDP

TDMIN

SDOUT/AD2

GNDD

VDDD

1

2

3

4

5

15

14

13

12

11

ES7243E

AINRN

REFP

GNDA

VDDA

REFQ

10

9

8

7

6

AINLN

AINLP

AD1

LRCK

SCLK

Pin Name

CCLK, CDATA

AD0, AD1

MCLK

SCLK

LRCK

TDMIN

SDOUT/AD2

AINLP, AINLN

AINRP, AINRN

VDDP

VDDD/GNDD

VDDA/GNDA

REFP

REFQ

Revision 2.0

Pin number

19, 18

17,8

20

6

7

2

3

9, 10

16, 15

1

5, 4

12, 13

14

11

Input or Output

Pin Description

I/O

I

I

I/O

I/O

I

O

I2C clock and data

I2C addresses

Master clock

Serial data bit clock

Serial data left and right channel frame clock

TDM data in

Serial data output/ I2C address AD2

I

Analog left and right inputs

I

I

I

O

O

Power supply for the digital input and output

Digital power supply

Analog power supply

Filtering capacitor connection

Filtering capacitor connection

4

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

2. TYPICAL APPLICATION CIRCUIT

0R

AGND

AGND AGND

1uF

IIC

CPU/DSP

TDMIN

VA

14

12

*

16

AINRP

15

13

GNDA

AINRN

1uF

AGND

9

AINLP

TDMIN

PGND

AINRP

1uF

AINRN

ES7243E

MCLK

SCLK

LRCK

SDOUT

2

21

VDDA

AD0

AD1

CCLK

CDATA

20

6

7

3

IIS

**

REFQ

AGND17

8

19

18

1uF

AGND

GNDD

VDDP

4

1uF

11

5

* *100nF

100nF

VDDD

VDDD

1

VDDP

REFP

GND(SYS)

In the layout, chip is treated as a analog device

AINLP

1uF

10

AINLN

AINLN

1uF

100K

AGND

AGND

For the best performance,decoupling and filtering capacitors should be located as close to the device package as possible

Additional paralle capacitors(typically 0.1 μF) can be used, larger value capacitors(typically 10 μF) would also help

*

AGND

AGND AGND

1uF

IIC

CPU/DSP

20

6

7

3

IIS

2

21

TDMIN

100K

AGND

VA

*

12

**

14

11

1

1uF

AGND

GNDD

AD0

AD1

CCLK

CDATA

VDDA

AGND17

8

19

18

1uF

REFQ

4

VDDP

* *100nF

100nF

VDDD

VDDD

5

VDDP

REFP

0R

GND(SYS)

In the layout, chip is treated as a analog device

AINRP

AINRN

16

ES7243E

MCLK

SCLK

LRCK

SDOUT

TDMIN

PGND

AINR

1uF

15

AGND

1uF

GNDA

13

AINLP

9

AINLN

10

AGND

1uF

AINL

AGND

1uF

AGND

For the best performance,decoupling and filtering capacitors should be located as close to the device package as possible

Additional paralle capacitors(typically 0.1 μF) can be used, larger value capacitors(typically 10 μF) would also help

*

Revision 2.0

5

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

3. CLOCK MODES AND SAMPLING FREQUENCIES

The device supports standard audio clocks (64Fs, 128Fs, 256Fs, 384Fs, 512Fs, etc), USB clocks

(12/24 MHz), and some common non standard audio clocks (25 MHz, 26 MHz, etc).

The device can work either in master clock mode or slave clock mode. In slave mode, LRCK and

SCLK are supplied externally, and LRCK and SCLK must be synchronously derived from the

system clock with specific rates. In master mode, LRCK and SCLK are derived internally from

device master clock.

4. MICRO-CONTROLLER CONFIGURATION INTERFACE

The device supports standard I2C micro-controller configuration interface. External microcontroller can completely configure the device through writing to internal configuration

registers.

I2C interface is a bi-directional serial bus that uses a serial data line (CDATA) and a serial clock

line (CCLK) for data transfer. The timing diagram for data transfer of this interface is given in

Figure 1a and Figure 1b. Data are transmitted synchronously to CCLK clock on the CDATA line on

a byte-by-byte basis. Each bit in a byte is sampled during CCLK high with MSB bit being

transmitted firstly. Each transferred byte is followed by an acknowledge bit from receiver to pull

the CDATA low. The transfer rate of this interface can be up to 400 kbps.

A master controller initiates the transmission by sending a “start” signal, which is defined as a

high-to-low transition at CDATA while CCLK is high. The first byte transferred is the slave address.

It is a seven-bit chip address followed by a RW bit. The chip address must be 0010 x, where x

equals AD2 AD1 AD0. The RW bit indicates the slave data transfer direction. Once an

acknowledge bit is received, the data transfer starts to proceed on a byte-by-byte basis in the

direction specified by the RW bit. The master can terminate the communication by generating a

“stop” signal, which is defined as a low-to-high transition at CDATA while CCLK is high.

In I2C interface mode, the registers can be written and read. The formats of “write” and “read”

instructions are shown in Table 1 and Table 2. Please note that, to read data from a register, you

must set R/W bit to 0 to access the register address and then set R/W to 1 to read data from the

register.

Table 1 Write Data to Register in I2C Interface Mode

start

Chip Address

0010 AD2 AD1 AD0

Revision 2.0

R/W

0

ACK

Register Address

RAM

ACK

Data to be written

DATA

6

Latest datasheet: www.everest-semi.com or info@everest-semi.com

ACK

June 2019

Stop

�Everest Semiconductor

Confidential

Chip Addr

CDATA

Write ACK

bit 1 to 7

Reg Addr

ES7243E

ACK

bit 1 to 8

Write Data

ACK

bit 1 to 8

CCLK

START

STOP

Figure 1a I2C Write Timing

Table 2 Read Data from Register in I2C Interface Mode

Chip Address

0010 AD2 AD1 AD0

Chip Address

0010 AD2 AD1 AD0

Start

Start

Chip Addr

CDATA

bit 1 to 7

Write ACK

R/W

0

R/W

1

Reg Addr

ACK

ACK

ACK

bit 1 to 8

Register Address

RAM

Data to be read

Data

Chip Addr

bit 1 to 7

Read ACK

ACK

NACK

Stop

Read Data NO ACK

bit 1 to 8

CCLK

START

START

STOP

Figure 1b I2C Read Timing

Revision 2.0

7

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

5. DIGITAL AUDIO INTERFACE

The device provides many formats of serial audio data interface to the output from the ADC

through LRCK, SCLK and SDOUT pins. These formats are I2S, left justified, DSP/PCM mode and

TDM. ADC data is out at SDOUT on the falling edge of SCLK. The relationships of SDOUT, SCLK

and LRCK with these formats are shown through Figure 2a to Figure 2h. ES7243E can be

cascaded up to 8-ch through single I2S or TDM, please refer to the user guide for detail

description.

1 SCLK

L Channel

LRCK

R Channel

SCLK

MSB

LSB

LSB

MSB

Figure 2a I2S Serial Audio Data Format

LRCK

L Channel

R Channel

SCLK

SDOUT

LSB

MSB

MSB

LSB

Figure 2b Left Justified Serial Audio Data Format

1 SCLK

LRCK

R Channel

L Channel

SCLK

SDOUT

MSB

LSB MSB

LSB

Figure 2c DSP/PCM Mode A Serial Audio Data Format

LRCK

R Channel

L Channel

SCLK

SDOUT

MSB

LSB MSB

LSB

Figure 2d DSP/PCM Mode B Serial Audio Data Format

Revision 2.0

8

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

1 SCLK

ES7243E

1 SCLK

Channel 3

Channel 1

LRCK

Channel 4

Channel 2

SCLK

SDOUT

MSB

LSB

LSB MSB

MSB

LSB

LSB MSB

Figure 2e TDM I2S Serial Audio Data Format

LRCK

Channel 3

Channel 1

Channel 4

Channel 2

SCLK

SDOUT

MSB

LSB

LSB MSB

MSB

LSB

LSB MSB

Figure 2f TDM Left Justified Serial Audio Data Format

1 SCLK

LRCK

Channel 4

Channel 3

Channel 2

Channel 1

SCLK

SDOUT

MSB

LSB MSB

LSB MSB

LSB

LSB MSB

Figure 2g TDM DSP/PCM Mode A Serial Audio Data Format

LRCK

Channel 4

Channel 3

Channel 2

Channel 1

SCLK

SDOUT

MSB

LSB MSB

LSB MSB

LSB MSB

LSB

Figure 2h TDM DSP/PCM Mode B Serial Audio Data Format

Revision 2.0

9

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

6. ELECTRICAL CHARACTERISTICS

ABSOLUTE MAXIMUM RATINGS

Continuous operation at or beyond these conditions may permanently damage the device.

PARAMETER

Analog Supply Voltage Level

Digital Supply Voltage Level

Analog Input Voltage Range

Digital Input Voltage Range

Operating Temperature Range

Storage Temperature

MIN

-0.3V

-0.3V

GNDA-0.3V

GNDD-0.3V

-40°C

-65°C

MAX

+3.6V

+3.6V

VDDA+0.3V

VDDP+0.3V

+85°C

+150°C

RECOMMENDED OPERATING CONDITIONS

PARAMETER

VDDA

VDDD

VDDP

MIN

1.7

1.7

1.7

TYP

3.3

3.3

3.3

MAX

3.6

3.6

3.6

UNIT

V

V

V

Note: for VDDD=1.8V, sampling frequency must be less than 24 kHz.

ADC ANALOG AND FILTER CHARACTERISTICS AND SPECIFICATIONS

Test conditions are as the following unless otherwise specify: VDDA=3.3V, VDDD=3.3V,

GNDA=0V, GNDD=0V, ambient temperature=25°C, Fs=48 KHz, MCLK/LRCK=256.

PARAMETER

ADC Performance

Signal to Noise ratio (A-weigh)

THD+N

Channel Separation (1KHz)

Interchannel Gain Mismatch

Gain Error

Filter Frequency Response

Passband

Stopband

Passband Ripple

Stopband Attenuation

Analog Input

Full Scale Input Level

Input Impedance

Revision 2.0

MIN

TYP

MAX

UNIT

96

-95

95

101

-90

100

0.1

104

-85

105

dB

dB

dB

dB

%

0

0.5465

±5

0.4535

±0.05

70

VDDA/3.3

8 (0 dB PGA)

6 (33 dB PGA)

10

Latest datasheet: www.everest-semi.com or info@everest-semi.com

Fs

Fs

dB

dB

Vrms

KΩ

June 2019

�Everest Semiconductor

Confidential

ES7243E

DC CHARACTERISTICS

PARAMETER

Normal Operation Mode

VDDD=3.3V, VDDP=3.3V, VDDA=3.3V (16 kHz)

VDDD=1.8V, VDDP=1.8V, VDDA=1.8V (16 kHz)

Power Down Mode

Digital Voltage Level

Input High-level Voltage

Input Low-level Voltage

Output High-level Voltage

Output Low-level Voltage

MIN

TYP

MAX

UNIT

26

7.5

0

0.7*VDDP

VDDP

0

mW

uA

V

V

V

V

0.5

I2C SWITCHING SPECIFICATIONS (SLOW SPEED MODE/HIGH SPEED MODE)

PARAMETER

CCLK Clock Frequency

Bus Free Time Between Transmissions

Start Condition Hold Time

Clock Low time

Clock High Time

Setup Time for Repeated Start Condition

CDATA Hold Time from CCLK Falling

CDATA Setup time to CCLK Rising

Rise Time of CCLK

Fall Time CCLK

Symbol

FCCLK

TTWID

TTWSTH

TTWCL

TTWCH

TTWSTS

TTWDH

TTWDS

TTWR

TTWF

MIN

4.7/1.3

4.0/0.6

4.7/1.3

4.0/0.6

4.7/0.6

0.25/0.1

MAX

100/400

UNIT

KHz

us

us

us

us

us

us

us

us

us

3.45/0.9

1.0/0.3

1.0/0.3

SDA

TTWSTS

TTWSTH

TTWCL

SCL

TTWDH

TTWID

TTWDS

TTWCH

S

TTWF TTWR

P

S

Figure 3 I2C Timing

Revision 2.0

11

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

SERIAL AUDIO PORT SWITCHING SPECIFICATIONS

PARAMETER

Symbol

MCLK frequency

MCLK duty cycle

LRCK frequency

LRCK duty cycle (Note 2)

SCLK frequency

SCLK pulse width low

TSLKL

SCLK Pulse width high

TSCLKH

SCLK falling to LRCK edge (master mode only)

TSLR

LRCK edge to SCLK rising (slave mode only)

TLSR

SCLK falling to SDOUT valid

VDDD=3.3V

T

VDDD=1.8V SDO

LRCK edge to SDOUT valid (Note 3)

VDDD=3.3V

T

VDDD=1.8V LDO

Note 2: one SCLK period of high time in DSP/PCM modes.

MIN

40

40

16

16

10

MAX

49.2

60

200

60

26

10

16

39

11

25

UNIT

MHz

%

KHz

%

MHz

ns

ns

ns

ns

ns

ns

Note 3: only apply to MSB of Left Justified or DSP/PCM mode B.

LRCK

TSLR

TLSR

TSCLKH

TSCLKL

SCLK

TSDO

TLDO

SDOUT

Figure 4 Serial Audio Port Timing

Revision 2.0

12

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

7. CONFIGURATION REGISTER DEFINITION

REGISTER 0X00 –RESET, DEFAULT 0001 1110

Bit Name

CSM_ON

Bit

7

MSC

6

SEQ_DIS

5

RST_DIG

4

RST_CMG

3

RST_MST

2

RST_ADC_DIG

1

Description

Chip FSM ON/OFF control

0 - csm power down(default)

1 - csm power up

Master/Slave select for SDP

0 - slave mode(default)

1 - master mode

Power up sequence enable control

0 - power up sequence enable(default)

1 - power up sequence disable

Digital circuits reset

0 - Not reset(default)

1 - Reset

Clock manager circuit reset

0 - Not reset (default)

1 - Reset

Master circuit reset

0 - Not reset (default)

1 - Reset

Adc digital circuit reset

0 - Not reset (default)

1 - Reset

REGISTER 0X01 – CLOCK MANAGER, DEFAULT 0000 0000

Bit Name

MCLK_ON

Bit

5

BCLK_ON

4

CLKADC_ON

3

ANACLKADC_ON

1

Description

MCLK ON/OFF control

0 - MCLK off (default)

1 - MCLK on

BCLK ON/OFF control

0 - BCLK off (default)

1 - BCLK on

Clock clk_adc ON/OFF control

0: clk_adc off(default)

1: clk_adc on

Clock anaclk_adc ON/OFF control

0 - anaclk_adc off(default)

1 - anaclk_adc on

REGISTER 0X02 – CLOCK MANAGER, DEFAULT 0000 0000

Bit Name

MCLK_SEL

Bit

7

MSTBCLK_SEL

6

MSTCLK_SEL

5:4

Revision 2.0

Description

Internal mclk select

0 - from MCLK PAD(default)

1 - from BCLK PAD

Master BCLK derive clocks

0 - from bclk_out[divided by DIV_BCLK](default)

1 - from anaclk_adc

At master mode, source clock select

13

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

BCLK_FITBIT

2

MCLK_INV

1

BCLK_INV

0

Confidential

ES7243E

0 - internal mclk(default)

1 - dig_mclk

2 - DSP_clk

3 - CF_clk

BCLK out control when master mode

0 - continual bclk(default)

1 - master bclk stop after data transfer out

Internal mclk invert

0 - normal(default)

1 - invert

BCLK invert

0 - normal(default)

1 - BCLK invert

REGISTER 0X03 – CLOCK MANAGER, DEFAULT 0010 0000

Bit Name

ADC_OSR

Bit

5:0

Description

ADC Over Sample Rate control

0~14 - not used

15 - 60*fs

16 - 64*fs(default)

...

31 - 124*fs

32 - 128*fs

...

63 - 252*fs

REGISTER 0X04 – CLOCK MANAGER, DEFAULT 0000 0000

Bit Name

DIV_PRE

Bit

7:4

MULT_PRE

1:0

Description

Pre-divided mclk

1~15 - divide by 2~16

0 - divide by 1(default)

Pre-multiplication

0 - 1x(default)

1 - 2x

2 - 4x

3 - 8x

REGISTER 0X05 – CLOCK MANAGER, DEFAULT 0000 0000

Bit Name

DIV_CLKCF

Bit

7:4

DIV_CLKDSP

3:0

Description

CF clock divider

1~15 - divide by 2~16

0 - divide by 1(default)

DSP clock divider

1~15 - divide by 2~16

0 - divide by 1(default)

REGISTER 0X06 – CLOCK MANAGER, DEFAULT 0000 0011

Bit Name

DIV_BCLK

Bit

6:0

Revision 2.0

Description

BCLK divider at master mode

0~2 - divide by 1~3

14

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

3 - divide by 4(default)

4~127 - divide by 5~128

REGISTER 0X07 – CLOCK MANAGER, DEFAULT 0000 0001

Bit Name

TRI_BCLK

Bit

6

TRI_LRCK

5

TRI_SDOUT

4

DIV_LRCK[11:8]

3:0

Description

BCLK Tri-state control

0 - normal(default)

1 - Tri-state

LRCK Tri-state

0 - normal(default)

1 - Tri-state

SDOUT Tri-state

0 - normal(default)

1 - Tri-state

Master LRCK divider bit 11 to bit 8

0~4095 - divide by 1~4096

512 - divide by 512(default)

REGISTER 0X08 – CLOCK MANAGER, DEFAULT 1111 1111

Bit Name

DIV_LRCK[7:0]

Bit

7:0

Description

Master LRCK divider bit 7 to bit 0

0~4095 - divide by 1~4096

512 - divide by 512(default)

REGISTER 0X09 – CLOCK MANAGER, DEFAULT 1100 0001

Bit Name

S1_SEL

Bit

7:6

S1_TIME

5:0

Description

SEL S1

00 – NA

01 – default

10 – state2

11 – state3

Timer for S1

For LRCK=48KHz:

0 - 21us

1 - 104us(default)

2 - 5ms

…

63 - 167ms(max)

REGISTER 0X0A – SDP, DEFAULT 1000 0001

Bit Name

S3_SEL

Bit

7:6

S3_TIME

5:0

Revision 2.0

Description

SEL S3

00 – NA

01 – default

10 – state2

11 – state3

Timer for S3

For LRCK=48KHz:

0 - 21us

1 - 104us(default)

15

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

2 - 5ms

…

63 - 167ms(max)

REGISTER 0X0B – SDP, DEFAULT 1100 0000

Bit Name

SDP_OUT_MUTE

Bit

7:6

SDP_LRP

5

SDP_WL

4:2

SDP_FMT

1:0

Description

SDP out mute control

0 - unmute

1 - mute R channel

2 - mute L channel

3 - mute L/R channels(default)

I2S/Left Justify case:

0 - L/R normal polarity(default)

Left/Right=High/Low (LJ)

Left/Right=Low/High (I2S)

1 - L/R invert polarity

Left/Right=Low/High (LJ)

Left/Right=High/Low (I2S)

DSP mode case:

0 - Mode A, MSB is available on 2nd SCLK rising edge after LRCK rising edge(default)

1 - Mode B, MSB is available on 1st SCLK rising edge after LRCK rising edge

SDP word length

0 – 24-bit(default)

1 – 20-bit

2 – 18-bit

3 – 16-bit

4 – 32-bit

others - 24-bit

SDP format

0 - I2S(default)

1 - LJ

2 - reserved

3 - DSP

REGISTER 0X0C – SDP, DEFAULT 0000 0000

Bit Name

TDM_FLAG

Bit

5:4

TDM_MODE

3:0

Revision 2.0

Description

NFS flag at slot0/LSB

0 - no flag(default)

1 - first chip, generate flag '1' at slot0/LSB

2 - sync chip, get tdm flag '1' and sync, and send flag '1' at current slot

3 - all LSB is flag '0'

TDM mode selection

0 - ADC no TDM(default)

1 - 2FS

2 - 3FS

3 - 4FS

4 - 5FS

5 - 6FS

6 - 7Fs

7 - 8FS

8 - ADC + TDM shift (1FS)

16

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

9 - TDM loop

other - not used

REGISTER 0X0D – ADC CONTROL, DEFAULT 0000 0000

Bit Name

ADC_DATASEL

Bit

7:6

ADC_INV

5:4

ADC_RAMCLR

ADC_SCALE

3

2:0

Description

ADC data mux

0 - output L - R (default)

1 - output L - L

2 - output R - R

3 - output R - L

ADC polarity inverted

0 - normal(default)

1 - ADCR invert

2 - ADCL invert

3 - ADCL/R invert

ADC ram clear when lrck/adc_mclk active

ADC gain scale up

0 - 0dB(default) (recommended when ADC_OSR=0x1C~0x20)

1 - 6dB (recommended when ADC_OSR=0x18~0x1B)

2 - 12dB (recommended when ADC_OSR=0x14~0x17)

3 - 18dB (recommended when ADC_OSR=0x11~0x13)

4 - 24dB (recommended when ADC_OSR=0x10)

5 - 30dB

6 - 36dB

7 - 42dB

REGISTER 0X0E – ADC CONTROL, DEFAULT 0000 0000

Bit Name

ADC_VOLUME

Bit

7:0

Description

ADC volume control

0x00 - '-95.5dB' (default)

0x01 - '-90.5dB'

… 0.5dB/step

0xBE - '-0.5dB'

0xBF - '0dB'

0xC0 - '+0.5dB'

…

0xFF - '+32dB'

ADC_VOLUME is the maxgain when ALC on

REGISTER 0X0F – ADC CONTROL, DEFAULT 0000 0000

Bit Name

ADC_HPF

Bit

7

ALC_EN

6

ADC_AUTOMUTE_EN

5:4

Revision 2.0

Description

ADC offset freeze

0 - freeze offset(default)

1 - dynamic HPF

ADC auto level control

0 - ALC disable(default)

1 - ALC enable

ADC auto mute control

0/1 - ADC automute dis (default)

2 - ADC automute enable

17

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

ADC_RAMPRATE

3:0

Confidential

ES7243E

3 – internal use

ADC VC ramp rate

0 - disable (default)

For LRCK=48KHz:

1 - 0.25dB/80us

2 - 0.25dB /160us

3 - 0.25dB /320us

4 - 0.25dB /640us

5 - 0.25dB /1.28ms

6 - 0.25dB /2.56ms

7 - 0.25dB /5.12ms

8 - 0.25dB /10.24ms

9 - 0.25dB /20.48ms

10 - 0.25dB /40.96ms

11 - 0.25dB /81.92ms

12 - 0.25dB /163.84ms

13 - 0.25dB /327.68ms

14 - 0.25dB /655.36ms

15 - 0.25dB /1.3s

REGISTER 0X10 – ADC CONTROL, DEFAULT 0000 0000

Bit Name

ADC_AUTOMUTE_NG

Bit

6:4

ADC_AUTOMUTE_WS

3:0

Description

ADC automute noise gate

0 - '-96dB'(default)

1 - '-90dB'

2 - '-84dB'

3 - '-78dB'

4 - '-72dB'

5 - '-66dB'

6 - '-60dB'

7 - '-54dB'

ADC automute detection

For LRCK=48KHz:

0 - 40us(default)

1 – 60us

2 – 120us

...

10 – 30ms

11 – 60ms

others: not used

REGISTER 0X11 – ADC CONTROL, DEFAULT 0000 0000

Bit Name

AUTOMUTE_SDP

Bit

5

ADC_AUTOMUTE_VOL

4:0

Revision 2.0

Description

ADC automute SDP control

0 - not mute(default)

1 - mute sdp, SDP_OUT_MUTE=3

ADC auto mute out gain select

0 - mute to -95.5dB(default)

… -4dB/step

23 - mute to 0dB

31 - mute to +32dB

18

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

REGISTER 0X12 – ADC CONTROL, DEFAULT 0000 0000

Bit Name

AUTOMUTE_PGA

Bit

3

AUTOMUTE_MOD

2

AUTOMUTE_MRST

1

AUTOMUTE_DIG

0

Description

ADC automute PDN_PGA control

0 - not mute(default)

1 - mute pga

ADC automute MOD control

0 - not mute(default)

1 - mute mod

ADC automute MOD reset control

0 - not mute(default)

1 - mute mod reset

ADC automute digital circuit control

0 - not mute(default)

1 - mute ADC digital

REGISTER 0X13 – ADC CONTROL, DEFAULT 0000 0000

Bit Name

ALC_WINSIZE

Bit

7:4

ALC_LEVEL

3:0

Revision 2.0

Description

ALC rate selection

For LRCK=48KHz:

1 - 0.25dB/40us

2 - 0.25dB /80us

3 - 0.25dB /160us

4 - 0.25dB /320us

5 - 0.25dB /640us

6 - 0.25dB / 1.28ms

7 - 0.25dB / 2.56ms

8 - 0.25dB /5.12ms

9 - 0.25dB /10.24ms

10 - 0.25dB /20.48ms

11 - 0.25dB /40.96ms

12 - 0.25dB /81.92ms

13 - 0.25dB /163.84ms

14 - 0.25dB /327.68ms

15 - 0.25dB /655.36ms

ALC target level

0 - '-30.0dB' (default)

1 - '-27.0dB'

2 - '-24.0dB'

3 - '-22.0dB'

4 - '-19.0dB'

5 - '-17.0dB'

6 - '-15.0dB'

7 - '-13.5dB'

8 - '-12.0dB'

9 - '-10.5dB'

10 - '-9.0 dB'

11 - '-7.5 dB'

12 - '-6.0 dB'

13 - '-4.5 dB'

14 - '-3.0 dB'

15 - '-1.5 dB'

19

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

REGISTER 0X14 – ADC CONTROL, DEFAULT 0000 1100

Bit Name

ADC_HPFS1

Bit

4:0

Description

ADCHPF stage1 coeff

0x0C (default)

REGISTER 0X15 – ADC CONTROL, DEFAULT 0000 1100

Bit Name

ADC_HPFS2

Bit

4:0

Description

ADCHPF stage2 coeff

0x0C (default)

REGISTER 0X16 – ANALOG, DEFAULT 1111 1111

Bit Name

PDN_ANA

Bit

7

PDN_ADCVREFGEN

6

MODTOP1_RST

5

MODTOP2_RST

4

PDN_MOD1

3

PDN_MOD2

2

PDN_PGA1

1

PDN_PGA2

0

Description

0 – enable analog circuits

1 – power down analog circuits(default)

0 – enable analog ADC bias circuits

1 – power down analog ADC bias circuits(default)

0 – disable(default)

1 – reset modulator1

0 – disable(default)

1 – reset modulator2

0 – enable analog ADC modulator1

1 – power down analog ADC modulator1(default)

0 – enable analog ADC modulator2

1 – power down analog ADC modulator2(default)

0 – enable analog PGA1

1 – power down analog PGA 1(default)

0 – enable analog PGA2

1 – power down analog PGA2(default)

REGISTER 0X17 – ANALOG, DEFAULT 0000 0000

Bit Name

VMIDSEL

Bit

1:0

Description

0 – power down(default)

1 – speed charge1

2 – normal vmid operation

3 – speed charge3

REGISTER 0X18 – ANALOG, DEFAULT 0010 0100

Bit Name

ADCBIAS_SW

Bit

5:4

ADCFL_SW

3:0

Revision 2.0

Description

0 –bias setting level0, (default)

1 –bias setting level1

2 –bias setting level2

3 –bias setting level3(highest bias)

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

20

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

REGISTER 0X19 – ANALOG, DEFAULT 1000 1000

Bit Name

PGA1BIAS_SW

Bit

7:4

PGA2BIAS_SW

3:0

Description

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

REGISTER 0X1A – ANALOG, DEFAULT 0100 0100

Bit Name

ADCI1BIAS_SW

Bit

7:4

Revision 2.0

Description

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

21

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

ADCI23BIAS_SW

3:0

Confidential

ES7243E

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

REGISTER 0X1B – ANALOG, DEFAULT 0100 0100

Bit Name

ADCSMBIAS_SW

Bit

7:4

ADCCMBIAS_SW

3:0

Revision 2.0

Description

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

22

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

REGISTER 0X1C – ANALOG, DEFAULT 0100 0100

Bit Name

ADCVRPBIAS_SW

Bit

7:4

ADCCPPBIAS_SW

3:0

Description

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

0000 – not allowed

0001 - bias setting level1(lowest)

0010 - bias setting level2

0011 - bias setting level3

0100 - bias setting level4

0101 - bias setting level5

0110 - bias setting level6

0111 - bias setting level7

1000 - bias setting level8

1001 - bias setting level9

1010 - bias setting level10

1011 - bias setting level11

1100 - bias setting level12

1101 - bias setting level13

1110 - bias setting level14

1111 - bias setting level15(highest)

REGISTER 0X1D – ANALOG, DEFAULT 0000 0000

Bit Name

LP_VRP

Bit

7

LP_VRPOUT

6

Revision 2.0

Description

0 – default

1 – low power

0 – default

23

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

LP_ADCMOD1

5

LP_ADCMOD2

4

LP_ADCMODF1

3

LP_ADCMODF2

2

LP_ADCMODI1

1

LP_ADCMODI2

0

Confidential

ES7243E

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

REGISTER 0X1E – ANALOG, DEFAULT 0000 0101

Bit Name

LP_PGA1

Bit

5

LP_PGA2

4

LP_PGA11

3

LP_PGA12

2

LP_PGA21

1

LP_PGA22

0

Description

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

0 – default

1 – low power

REGISTER 0X1F – ANALOG, DEFAULT 0000 1100

Bit Name

ADC_DMIC_ON

Bit

5

REFSEL

4

VX2OFF

3

VX1SEL

2

VMIDLVL

1:0

Description

0 – default

1 – enable Dmic

0 – default

1 – internal use

0 – enable internal reference voltage

1 – off(default)

0 – level1

1 – level2(default)

0 –’vdda/2’ (default)

1 – vmid level1

2 – vmid level2

3 – vmid level3

REGISTER 0X20 – ANALOG, DEFAULT 0000 0000

Bit Name

SELMIC1

Bit

4

PGA1GAIN_SETTING

3:0

Revision 2.0

Description

0 – default

1 – select MIC1 as PGA1 input

PGA1 gain

0 – 0dB(default)

24

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

1 – 3dB

2 – 6dB

3 – 9dB

4 – 12dB

5 – 15dB

6 – 18dB

7 – 21dB

8 – 24dB

9 – 27dB

10 – 30dB

11 – 33dB

12 – 34.5dB

13 – 36dB

14 – 37.5dB

REGISTER 0X21 – ANALOG, DEFAULT 0000 0000

Bit Name

SELMIC2

Bit

4

PGA2GAIN_SETTING

3:0

Description

0 – default

1 – select MIC2 as PGA2 input

PGA2 gain

0 – 0dB(default)

1 – 3dB

2 – 6dB

3 – 9dB

4 – 12dB

5 – 15dB

6 – 18dB

7 – 21dB

8 – 24dB

9 – 27dB

10 – 30dB

11 – 33dB

12 – 34.5dB

13 – 36dB

14 – 37.5dB

REGISTER 0XF7 – TEST MODE, DEFAULT 1111 0000

Bit Name

PULLUPSE_BCLK

Bit

7

PULLUPSE_LRCK

6

PULLDNSE_TDMIN

5

PULLDNSE_SDOUT

4

SDOUT_DRIVE

2

Revision 2.0

Description

BCLK pullup control

0 - BCLK no pullup

1 - BCLK pullup(default)

LRCK pullup control

0 - LRCK no pullup

1 - LRCK pullup(default)

TDMIN pulldown control

0 - TDMIN no pulldown

1 - TDMIN pulldown(default)

SDOUT pulldown control

0 - SDOUT no pulldown

1 - SDOUT pulldown(default)

SDOUT driver select

25

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

BCLK_DRIVE

1

LRCK_DRIVE

0

Confidential

ES7243E

0 - SDOUT normal driver(default)

1 - SDOUT weak driver

BCLK driver select

0 - BCLK normal driver(default)

1 - BCLK weak driver

LRCK driver select

0 - LRCK nromal driver(default)

1 - LRCK weak driver

REGISTER 0XF8 – TEST MODE, DEFAULT 0000 0000

Bit Name

SDOUT_FAST

PATHSEL

DELYSEL

ADC_DLY_SEL

Bit

7

6

5:4

3

Description

Internal use

Internal use

Internal use

Internal use

REGISTER 0XF9 – TEST MODE, DEFAULT 0000 0000

Bit Name

DLL_PWD

Bit

0

Description

Internal use

REGISTER 0XFA – I2C CONFIGURE, DEFAULT 0000 0000

Bit Name

I2C_RETIME

Bit

1

INI_REG

0

Description

I2C signals retime

0 - normal(default)

1 - retime mode

Initial registers

0 - normal(default)

1 - reset registers to default

REGISTER 0XFC – FLAG, DEFAULT 0000 0000

Bit Name

FLAG_CSM_CHIP

Bit

5:4

FLAG_ADCAM

0

Description

CSM flag, read only

0 - S0

1 - S1

2 - S2

3 - S3

ADC automute flag, read only

0 - no mute

1 - mute flag

REGISTER 0XFD – CHIP ID1, DEFAULT 0111 1010

Bit Name

CHIP_ID1

Bit

7:0

Description

0X7A, read only

REGISTER 0XFE – CHIP ID2, DEFAULT 0100 0011

Bit Name

CHIP_ID2

Bit

7:0

Revision 2.0

Description

0X43, read only

26

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Everest Semiconductor

Confidential

ES7243E

REGISTER 0XFF – CHIP VERSION, DEFAULT 0000 0000

Bit Name

CHIP_VER

Bit

7:0

Revision 2.0

Description

0X00, read only

27

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�Revision 2.0

Confidential

28

Latest datasheet: www.everest-semi.com or info@everest-semi.com

8. PACKAGE

Everest Semiconductor

June 2019

ES7243E

�Everest Semiconductor

Confidential

ES7243E

9. CORPORATE INFORMATION

Everest Semiconductor Co., Ltd.

No. 1355 Jinjihu Drive, Suzhou Industrial Park, Jiangsu, P.R. China, Zip Code 215021

苏州工业园区金鸡湖大道 1355 号国际科技园, 邮编 215021

Email: info@everest-semi.com

Revision 2.0

29

Latest datasheet: www.everest-semi.com or info@everest-semi.com

June 2019

�