SLG59M1649V

An Ultra-small, Low-power 23 mΩ/4 A P-Channel

Integrated Power Switch with Reverse-Current Blocking

General Description

Pin Configuration

VIN

1

ON

2

ON

3

VIN

4

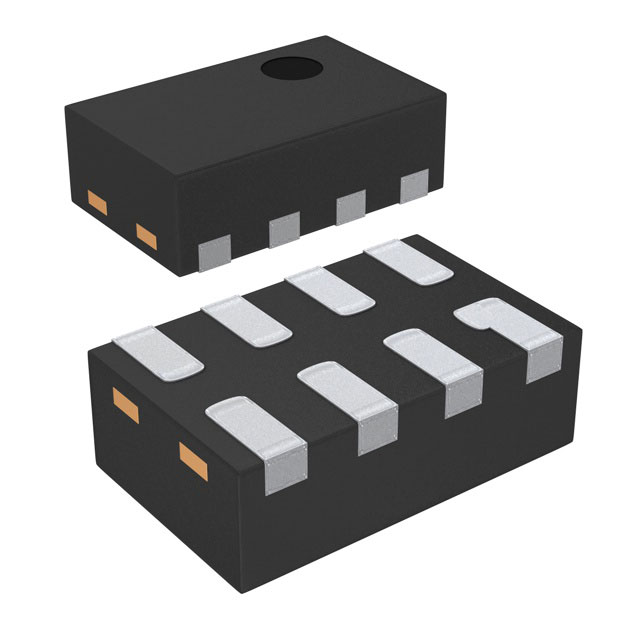

Designed to operate over a -40°C to 85°C range, the

SLG59M1649V is available in a RoHS-compliant, ultra-small

1.0 x 1.6 mm STDFN package.

Features

SLG59M1649V

The SLG59M1649V is a self-powered, high-performance,

23 mΩ pFET integrated power switch designed for 1.5 to 5 V

power rail applications up to 4 A. When enabled, internal

reverse-current protection will quickly open the switch in the

event of a reverse-voltage condition is detected

(a VOUT+50mV > VIN condition opens the switch). Upon the

detection of a reverse condition, an open-drain FAULT output

is asserted. In the event the VIN voltage is too low, the power

switch also contains an internal UVLO threshold monitor to

keep or to turn the switch OFF.

8

VOUT

7

GND

6

FAULT

5

VOUT

8-pin STDFN

(Top View)

Applications

• Steady-state Operating Current: Up to 4 A

• Low Typical RDSON:

• 23 mΩ at VIN = 5 V

• 31 mΩ at VIN = 2.5 V

• 42 mΩ at VIN = 1.5 V

• Operating Voltage: 1.5 V to 5.5 V

• Reverse-voltage Detection ON or OFF

• Internal Gate Drive and VOUT Discharge

• Open-drain FAULT Signaling

• Operating temperature range: -40°C to 85°C

• Low θJA, 8-pin 1.0 mm x 1.6 mm STDFN Packaging

• Pb-Free / Halogen-Free / RoHS compliant packaging

• Power-Rail Switching:

• Notebook/Laptop/Tablet PCs

• Smartphones/Wireless Handsets

• High-definition Digital Cameras

• Set-top Boxes

• Point of Sales Pins

• GPS Navigation Devices

Block Diagram

ILOAD

Reverse

Voltage

Detection

VIN

VOUT

FAULT

Logic

Control

SW Closed

ON

Discharge

CMOS

Input

SW Open

GND

Silego Technology, Inc.

000-0059M1649-100

Rev 1.00

Revised February 23, 2017

�SLG59M1649V

Pin Description

Pin #

Pin Name

1, 4

VIN

Type

Pin Description

Power/Input

With an internal 1.2V UVLO threshold, VIN supplies the power for the

operation of the power switch, the internal control circuitry, and the source

terminal of pFET. Bypass the VIN pin to GND with a 2.2 μF (or larger),

low-ESR capacitor.

A low-to-high transition on this pin initiates the operation of the power

switch. ON is an asserted-HIGH, level-sensitive CMOS input with

VIL < 0.3 V and VIH > 1 V. As the ON input circuitry does not have an internal

pull-down resistor, connect the ON pin directly to a GPIO controller – do

not allow this pin to be open circuited.

2, 3

ON

Input

5, 8

VOUT

Output

Output and drain terminal of MOSFET.

An open drain output, FAULT is asserted within TFAULTLOW when a

(VOUT+VREVERSE > VIN) condition is detected. The FAULT output is deasserted within TFAULTHIGH when the fault condition is removed. Connect

an external 10-kΩ resistor from the FAULT pin to the system’s local logic

supply.

6

FAULT

Output

7

GND

GND

Ground connection. Connect this pin to system analog or power ground

plane.

Ordering Information

Part Number

Type

Production Flow

SLG59M1649V

STDFN

Industrial, -40 °C to 85 °C

SLG59M1649VTR

STDFN (Tape and Reel)

Industrial, -40 °C to 85 °C

000-0059M1649-100

Page 2 of 13

�SLG59M1649V

Absolute Maximum Ratings

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

VIN

Power Switch Input Voltage

-0.3

--

6

V

TS

Storage Temperature

-65

--

150

°C

ESDHBM

ESD Protection

Human Body Model

2000

--

--

V

ESDCDM

ESD Protection

Charged Device Model

1000

--

--

V

MSL

Moisture Sensitivity Level

ΘJA

Thermal Resistance

TJ,MAX

Maximum Junction Temperature

MOSFET

IDSCONT

Continuous Current from VIN to

VOUT

MOSFET IDSPK Peak Current from Drain to Source

1

1.0 x 1.6 mm 8L STDFN

--

82

--

°C/W

--

150

--

°C

Each channel, TJ< 150°C

--

--

2

A

Maximum pulsed switch current, pulse

width < 1 ms, 1% duty cycle

--

--

2.5

A

Note: Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Electrical Characteristics

1.5 V ≤ VIN ≤ 5.5 V; CIN = 2.2 µF, TA =-40 °C to 85 °C, unless otherwise noted.

Typical values are at TA = 25°C (unless otherwise stated)

Parameter

VIN

VIN(UVLO)

IIN

IIN(OFF)

RDSON

Description

Power Switch Input Voltage

VIN Undervoltage Lockout

Threshold

Quiescent Power Switch Current

OFF Mode Power Switch Current

Static Drain to Source ON

Resistance

VREVERSE

Reverse-current Voltage Threshold

IREVERSE

Reverse-current Leakage Current

after Reverse Current Event

VON

Conditions

VIN ↑, VON = 0V, IOUT = -100 mA

Typ.

Max.

Unit

1.5

--

5.5

V

--

--

1.2

V

0.5

--

--

V

VIN = 5.25V, VON = HIGH,

IOUT = 0 mA

--

6.6

11

µA

VIN = 1.5 V, VON = HIGH,

IOUT = 0 mA

--

5

8

µA

VIN = 5.25 V, VON = LOW,

RLOAD = 1 MΩ

--

2

3

µA

VIN = 1.5 V, VON = LOW,

RLOAD = 1 MΩ

--

0.8

2

µA

TA = 25°C, VIN = 5.0 V,

ILOAD = -200 mA

--

23

28

mΩ

TA = 25°C, VIN = 2.5 V,

ILOAD = -200 mA

--

31

38

mΩ

TA = 25°C, VIN = 1.5 V,

ILOAD = -200 mA

--

42

50

mΩ

--

50

--

mV

--

1

--

µA

VIN

V

VIN ↓, VON = 0V, RLOAD = 10Ω

VOUT – VIN > VREVERSE; TA = 25°C;

ON = GND

ON Pin Voltage Range

ION(Leakage) ON Pin Leakage Current

Min.

0

--

--

1

µA

ON_VIH

ON Pin Input High Voltage

1

--

VDD

V

ON_VIL

ON Pin Input Low Voltage

-0.3

0

0.3

V

ONHYS

ON Hysteresis

--

60

--

mV

000-0059M1649-100

1.4 V ≤ VON ≤ VINor VON = GND

Page 3 of 13

�SLG59M1649V

Electrical Characteristics (continued)

1.5 V ≤ VIN ≤ 5.5 V; CIN = 2.2 µF, TA =-40 °C to 85 °C, unless otherwise noted.

Typical values are at TA = 25°C (unless otherwise stated)

Parameter

Min.

Typ.

Max.

Unit

VIN = 5 V; VOUT < 0.4 V

50

80

120

Ω

VIN = 5 V

--

10

--

µs

--

1.5

--

ms

50% ON to 50% VOUT ↑;

TA = 25°C, VIN = 5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

180

235

μs

50% ON to 50% VOUT ↑;

TA = 25°C, VIN = 1.5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

110

145

μs

10% to 90% VOUT ↑;

TA = 25°C, VIN = 5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

130

170

μs

10% to 90% VOUT ↑;

TA = 25°C, VIN = 1.5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

66

86

μs

90% to 10% VOUT ↓;

TA = 25°C, VIN = 5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

2.2

3.6

μs

90% to 10% VOUT ↓;

TA = 25°C, VIN = 1.5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

2.2

3.6

μs

50% ON to 50% VOUT ↓;

TA = 25°C, VIN = 5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

3.5

5

μs

50% ON to 50% VOUT ↓;

TA = 25°C, VIN = 1.5 V;

RLOAD = 10 Ω, CLOAD = 0.1 µF

--

5

7

μs

TFAULTLOW FAULT Assertion Time

Reverse-voltage Detection to

FAULT↓; 1.5 V ≤ IN ≤ 5 V; ON = Low

--

2

--

μs

1.5 V ≤ VIN ≤ 5 V; ON = High

--

0.5

--

μs

TFAULTHIGH FAULT De-assertion Time

Delay to FAULT↑ after fault

condition is removed;

1.5 V ≤ VIN ≤ 5 V; ON = Low

--

7

--

ms

RDSCHRG

TREV

TREARM

TON_Delay

TVOUT(R)

TVOUT(F)

TOFF_Delay

FAULTVOL

Description

Conditions

Output Discharge Resistance

Reverse-current Detect Response

Delay

Reverse Detect Rearm Time

ON Delay Time

VOUT Rise Time

VOUT Fall Time

OFF Delay Time

FAULT Output Low Voltage

000-0059M1649-100

1.5 V ≤ VIN ≤ 5 V; ON = High

--

2

--

ms

IFAULT = 1 mA

--

--

0.2

V

Page 4 of 13

�SLG59M1649V

TTotal_ON, TON_Delay and Slew Rate Measurement

ON

50% ON

50% ON

TVOUT(R)

90% VOUT

VOUT

50% VOUT(R)

TON_Delay

10% VOUT

90% VOUT

TOFF_Delay

50% VOUT(F)

10% VOUT

TVOUT(F)

000-0059M1649-100

Page 5 of 13

�SLG59M1649V

RDSON vs. VIN and Temperature

RDSON vs.Temperature and VIN

000-0059M1649-100

Page 6 of 13

�SLG59M1649V

VIN Inrush Current Details

When the SLG59M1649V is enabled with ON ↑, the power switch closes to charge the VOUT output capacitor to VIN. The charging

current drawn from VIN is commonly referred to as “VIN inrush current” and can cause the input power source to collapse if the

VIN inrush current is too high.

Since the VOUT rise time of the SLG59M1649V is fixed, VIN inrush current is then a function of the output capacitance at VOUT.

The expression relating VIN inrush current, the SLG59M1649V VOUT rise time, and CLOAD is:

VIN Inrush Current = CLOAD x

∆VOUT

VOUT Rise Time

where in this expression ∆VOUT is equivalent to VIN if the initial SLG59M1649V’s output voltages are zero.

In the table below are examples of VIN inrush currents assuming zero initial charge on CLOAD as a function of VIN.

VIN

VOUT Rise Time

CLOAD

Inrush Current

1.5 V

66 μs

0.1 μF

2.3 mA

5V

130 μs

0.1 μF

3.8 mA

Since the relationship is linear and if CLOAD were increased to 1 µF, then the VIN inrush currents would be 10x higher in either

example. If a large CLOAD capacitor is required in the application and depending upon the strength of the input power source, it

may very well be necessary to increase the CIN-to-CLOAD ratio to minimize VIN droop during turn-on.

For other VOUT rise time options, please contact Silego for additional information.

Power Dissipation

The junction temperature of the SLG59M1649V depends on factors such as board layout, ambient temperature, external air flow

over the package, load current, and the RDSON-generated voltage drop across each power MOSFET. While the primary contributor to the increase in the junction temperature of the SLG59M1649V is the power dissipation of its power MOSFETs, its power

dissipation and the junction temperature in nominal operating mode can be calculated using the following equations:

PDTOTAL = RDSON x IDS2

where:

PDTOTAL = Total package power dissipation, in Watts (W)

RDSON = Power MOSFET ON resistance, in Ohms (Ω)

IDS = Output current, in Amps (A)

and

TJ= PDTOTAL x θJA + TA

where:

TJ = Die junction temperature, in Celsius degrees (°C)

θJA = Package thermal resistance, in Celsius degrees per Watt (°C/W) – highly dependent on pcb layout

TA = Ambient temperature, in Celsius degrees (°C)

000-0059M1649-100

Page 7 of 13

�SLG59M1649V

Power Dissipation (continued)

In nominal operating mode, the SLG59M1649V’s power dissipation can also be calculated by taking into account the voltage drop

across each switch (VIN-VOUT) and the magnitude of that channel’s output current (IOUT):

PDTOTAL = (VIN-VOUT) x IDS or

PDTOTAL = (VIN – (RLOAD x IDS)) x IDS

where:

PDTOTAL = Total package power dissipation, in Watts (W)

VIN = Input Voltage, in Volts (V)

RLOAD] = Output Load Resistance, in Ohms (Ω)

IDS = Output current, in Amps (A)

VOUT= Output voltage, or RLOAD x IDS

Power Dissipation Derating Curve

Maximum Power Dissipation (W)

1.0

0.9

0.8

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

Ambient Temperature °(C)

Note: Each VIN, VOUT = 1 in2 1.2 oz. copper on FR4

000-0059M1649-100

Page 8 of 13

�SLG59M1649V

SLG59M1649V Layout Suggestion

Note: All dimensions shown in micrometers (μm)

Recommended PCB Layout for external power traces

SLG59M1649V

VIN

VOUT

Note: All dimensions shown in μm (micrometers)

000-0059M1649-100

Page 9 of 13

�SLG59M1649V

Package Top Marking System Definition

ABC

Serial Number

Pin 1 Identifier

ABC - 3 alphanumeric Part Serial Number

where A, B, or C can be A-Z and 0-9

000-0059M1649-100

Page 10 of 13

�SLG59M1649V

Package Drawing and Dimensions

8 Lead STDFN Package 1.0 x 1.6 mm

000-0059M1649-100

Page 11 of 13

�SLG59M1649V

Tape and Reel Specifications

Max Units

Leader (min)

Nominal

Reel &

Package # of

Package Size

Hub Size

Length

Type

Pins

per Reel per Box

Pockets

[mm]

[mm]

[mm]

STDFN 8L

1x1.6mm

0.4P FCD

Green

8

1.0 x 1.6 x 0.55

3,000

3,000

178 / 60

100

400

Trailer (min)

Pockets

Length

[mm]

Tape

Width

[mm]

100

400

8

Part

Pitch

[mm]

4

Carrier Tape Drawing and Dimensions

Pocket BTM Pocket BTM

Package

Length

Width

Type

STDFN 8L

1x1.6mm

0.4P FCD

Green

Pocket

Depth

Index Hole

Pitch

Pocket

Pitch

Index Hole

Diameter

Index Hole Index Hole

to Tape

to Pocket Tape Width

Edge

Center

A0

B0

K0

P0

P1

D0

E

F

W

1.12

1.72

0.7

4

4

1.55

1.75

3.5

8

Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 0.88 mm3 (nominal). More

information can be found at www.jedec.org.

000-0059M1649-100

Page 12 of 13

�SLG59M1649V

Revision History

Date

Version

2/23/2017

1.00

000-0059M1649-100

Change

Production Release

Page 13 of 13

�