SLG7NT4129

PCIE RTD3

General Description

Features

• Low Power Consumption

• Dynamic Supply Voltage

• RoHS Compliant / Halogen-Free

• Pb-Free TDFN-12 Package

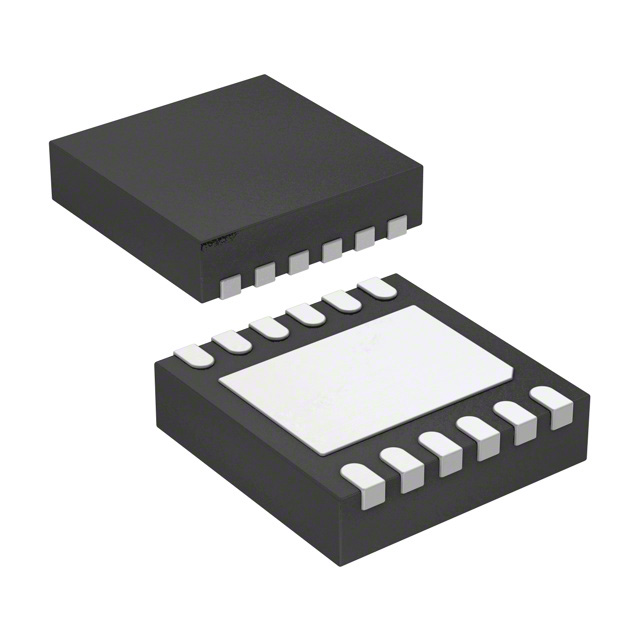

Pin Configuration

VDD

1

12

DEVICE_RESET#

PWR_CNTRL_GPIO#

2

11

PCIE_WAKE#

PLT_RST#

3

10

NC

DEVICE_WAKE#

4

RST_CNTRL_GPIO#

5

NC

6

SLG7NT4129

Renesas SLG7NT4129 is a low power and small

form device. The SoC is housed in a 2.5mm x

2.5mm TDFN package which is optimal for using

with small devices.

TDFN-12

TOP VIEW

9

WAKE_GPIO

8

NC

7

GND

Thermal Pad

connected to GND

Output Summary

• 2 Outputs – Open Drain

• 2 Outputs – 3-State

Block Diagram

Renesas Electronics Corporation.

SLG7NT4129_DS_r102

SLG7NT4129_GP_r004

Rev 1.02

Revised February 25, 2022

�SLG7NT4129

PCIE RTD3

Pin Configuration

Pin #

1

2

3

4

5

6

7

8

9

10

11

12

Exposed

Bottom Pad

Pin Name

VDD

PWR_CNTRL_GPIO#

PLT_RST#

DEVICE_WAKE#

RST_CNTRL_GPIO#

NC

GND

NC

WAKE_GPIO

NC

PCIE_WAKE#

DEVICE_RESET#

Exposed Bottom Pad

Type

PWR

Input

Input

Input/Output

Input

-GND

-Output

-Input/Output

Output

GND

Pin Description

Supply Voltage

Digital Input

Digital Input

3-State

Digital Input

Keep floating or connect to GND

Ground

Keep floating or connect to GND

Open Drain

Keep floating or connect to GND

3-State

Open Drain

Ground

Ordering Information

Part Number

SLG7NT4129V

SLG7NT4129VTR

SLG7NT4129_DS_r102

Package Type

V = TDFN-12

VTR = TDFN-12 - Tape and Reel (3k units)

Page 2

2

�SLG7NT4129

PCIE RTD3

Absolute Maximum Conditions

Parameter

Min.

Max.

Unit

VHIGH to GND

-0.3

7

V

Voltage at input pins

-0.3

7

V

Current at input pin

-1.0

1.0

mA

Storage temperature range

-65

150

°C

Junction temperature

--

150

°C

Electrical Characteristics

(@ 25°C, unless otherwise stated)

Symbol Parameter

VDD

Condition/Note

Min.

Typ.

Max.

Unit

1.71

--

3.6

V

--

1

--

μA

-40

25

85

°C

-100

--

100

nA

Logic Input, at VDD=1.8V

1.1

--

--

Logic Input, at VDD=3.3V

1.8

Logic Input, at VDD=1.8V

--

--

0.65

Supply Voltage

IQ

Quiescent Current

TA

Operating Temperature

IL

Input Leakage Current

Static inputs and outputs

Leakage Current for Digital Inputs or

outputs in High impedance state

VIH

HIGH-Level Input Voltage

VIL

LOW-Level Input Voltage

IIH

HIGH-Level Input Current

Logic Input Pins; VIN=VDD

-1

1

μA

IIL

LOW-Level Input Current

Logic Input Pins; VIN=0V

-1

1

μA

ms

TDLY0

Delay0 Time

VOH

Output Voltage High

VOL

VO

IOL

TSU

Output Voltage Low

Logic Input, at VDD=3.3V

LOW-Level Output Current

Start up Time

3

3.9

3-State, OE=1, IOH = 100µA at VDD=1.8V

1.66

--

--

3-State, OE=1, IOH = 3mA at VDD=3.3V

2.1

--

--

3-State, OE=1, IOL = 100µA at VDD=1.8V

--

--

0.04

3-State, OE=1, IOL = 3mA at VDD=3.3V

--

--

0.81

Open Drain, IOL = 5mA, at VDD=1.8V

--

--

0.340

Open Drain, IOL = 20mA at VDD=3.3V

--

--

0.605

--

--

VDD

3-State, OE=1, VOL =0.15V, at VDD=1.8V

0.34

--

--

3-State, OE=1, VOL = 0.4V, at VDD=3.3V

1.836

--

--

Open Drain, VOL =0.15V, at VDD=1.8V

2.7

--

--

Open Drain, VOL = 0.4V, at VDD=3.3V

14.6

--

--

--

7

--

SLG7NT4129_DS_r102

After VDD reaches 1.6V level

V

1.1

2.1

Maximal Voltage Applied to any

PIN in High-Impedance State

V

V

V

V

mA

ms

Page 3

3

�SLG7NT4129

PCIE RTD3

Timing diagram

SLG7NT4129_DS_r102

Page 4

4

�SLG7NT4129

PCIE RTD3

Package Top Marking

Datasheet

Revision

1.02

SLG7NT4129_DS_r102

Programming

Code Number

04

Part Code

Revision

Date

4129V

AA

02/25/2022

Page 5

5

�SLG7NT4129

PCIE RTD3

Package Drawing and Dimensions

12 Lead TDFN Package

JEDEC MO-252, Variation 2525E

SLG7NT4129_DS_r102

Page 6

6

�SLG7NT4129

PCIE RTD3

Tape and Reel Specification

# of

Package Type

Pins

TDFN 12L

2.5x2.5mm

0.4P Green

12

Max Units

Nominal

Package

Size (mm)

per reel

2.5x2.5x0.75

3000

Trailer A

per box

Reel &

Hub Size

(mm)

Pockets

3000

178/60

42

Leader B

Pocket (mm)

Length

Length

Pockets

(mm)

(mm)

168

42

168

Width

Pitch

8

4

Carrier Tape Drawing and Dimensions

Package

Type

TDFN 12L

2.5x2.5mm

0.4P Green

Pocket

BTM

Length

(mm)

Pocket

BTM Width

(mm)

Pocket

Depth

(mm)

Index Hole

Pitch

(mm)

Pocket

Pitch

(mm)

Index Hole

Diameter

(mm)

Index Hole Index Hole

to Tape

to Pocket Tape Width

Edge

Center

(mm)

(mm)

(mm)

A0

B0

K0

P0

P1

D0

E

F

W

2.75

2.75

1.05

4

4

1.55

1.75

3.5

8

Refer to EIA-481 Specifications

Recommended Reflow Soldering Profile

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 4.6875 mm3 (nominal).

More information can be found at www.jedec.org.

SLG7NT4129_DS_r102

Page 7

7

�SLG7NT4129

PCIE RTD3

Datasheet Revision History

Date

11/08/2012

11/22/2012

11/26/2012

01/18/2013

01/23/2013

06/11/2013

02/25/2022

Version

0.1

0.11

0.20

0.21

1.0

1.01

1.02

SLG7NT4129_DS_r102

Change

New design

Changed PIN12 type to Open Drain

Changed DEVICE_WAKE# and PCIE_WAKE# functionality to bi-directional

Some typos in PIN out table are fixed

Production Release

Housekeeping (fixed block diagram)

Updated Company name and logo

Page 8

8

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2021 Renesas Electronics Corporation. All rights reserved.

�