Vaibhav Kumar

TI Precision Designs: TIPD115 Verified Design

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for

Lowest Distortion and Noise

TI Precision Designs

Circuit Description

TI Precision Designs are analog solutions created by

TI’s analog experts. Verified Designs offer the theory,

component selection, simulation, complete PCB

schematic & layout, bill of materials, and measured

performance of useful circuits. Circuit modifications

that help to meet alternate design goals are also

discussed.

This design is for an 18-bit data acquisition block at

1MSPS throughput optimized for the lowest distortion

and noise performance. The circuit is realized with an

18-bit successive-approximation-resistor (SAR)

analog-to-digital converter (ADC), a fully differential

input driver and a high precision reference and

reference driver. The design details the process for

optimizing the precision front end drive circuit as well

as the reference circuit to achieve excellent dynamic

performance with the ADS8881 while consuming low

power.

Design Resources

Design Archive

TINA-TI™

OPA333

THS4521

THS4281

ADS8881

ADS9110

OPA2625

OPA378

All Design files

SPICE Simulator

Product Folder

Product Folder

Product Folder

Product Folder

Product Folder

Product Folder

Product Folder

Ask The Analog Experts

WEBENCH® Design Center

TI Precision Designs Library

REFERENCE DRIVE CIRCUIT

20kΩ

1µF

THS4281

+

-

1kΩ

AVDD

+

0.2Ω

1µF

AVDD

+

OPA333

1kΩ

+

Vout

AVDD

10µF

REF5045

Vin

Temp

1µF

Trim Gnd

1µF

1KΩ

1KΩ

AVDD

AVDD

VIN+

THS4521

+ + -

VCM

-

+

10Ω

10nF

CONVST

ADS8881

AINM

10Ω

GND

CONVST

+

VIN-

REFP AVDD

AINP

V+

1KΩ

1KΩ

18-Bit 1MSPS

SAR ADC

INPUT DRIVER

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and

other important disclaimers and information.

TINA-TI is a trademark of Texas Instruments

WEBENCH is a registered trademark of Texas Instruments

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise 1

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

1

Design Summary

The primary objective is to design a lowest distortion and noise data acquisition block with low power

consumption using the 18-bit ADS8881 at a throughput of 1MSPS for a 10 kHz full-scale pure sine wave

input. The design requirements for this block design are:

•

System Supply Voltage: 5 V dc

•

ADC Supply Voltage: 3.3 V dc

•

ADC Sampling Rate: 1MSPS

•

ADC Reference Voltage (VREF): 4.5 V dc

•

ADC Input Signal: A differential input signal with amplitude of V pk = 4.315 V (-0.4 dBFS to avoid

clipping) and frequency, f IN = 10 kHz are applied to each differential input of the ADC

The design goals and performance are summarized in Table 1.

Table 1: Comparison of design goals, simulation and measured performance

Goal

Simulated

Total Power

Parameter

< 40 mW

NA

39.4 mW

Signal to Noise Ratio (SNR)

> 98 dB

NA

98.74 dB

Total Harmonic Distortion (THD)

< -110 dB

NA

-110.04 dB

Effective Number of Bits (ENOB)

16

NA

16.05

< ±1.5 LSB

NA

< ±1.5 LSB

Integral Non-Linearity (INL)

Measured

Data Acquisition Block: FFT Spectrum

0

-20

-40

dBc

-60

-80

HD2 HD3

-100

-115.0 -112.4

-120

-123.1

-140

-144.6

-125.1

-130.1

-129.6

-142.2

-137.2

-160

0

20

40

60

80

100

120

Frequency (kHz)

Figure 1: Measurement Result for FFT of the Data Acquisition Block

2 18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

2

Theory of Operation

The two primary design considerations to maximize the performance of a high-resolution SAR ADC are the

input driver and the reference driver design. The overall system block diagram is shown in Figure 2. The

block-diagram comprises of the critical analog circuit blocks, the input driver, anti-aliasing filter and the

reference driver. Each analog circuit block should be carefully designed based on the ADC performance

specifications in order to maximize the distortion and noise performance of the data acquisition system

while consuming low power. The diagram includes the most important specifications for each individual

analog block.

This design systematically approaches the design of each analog circuit block to achieve a 16-bit low

noise and distortion data acquisition system for a 10 kHz sinusoidal input signal. The first step in the

design requires an understanding of the requirement of extremely low distortion input driver amplifier. This

will help in the decision of an appropriate input driver configuration and selection of an input amplifier to

meet the system requirements. The next important step is the design of the anti-aliasing RC-filer to

attenuate ADC kick-back noise while maintaining the amplifier stability. The final design challenge is to

design a high precision reference driver circuit, which would provide the required value V REF with low

offset, drift and noise contributions.

VREF Output: Value & Accuracy

Low Temp & Long-Term Drift

Low Noise

Band-limiting

Reference Noise

Low Output Impedance

Low Offset Error

Low Temp & Long-Term Drift

VREF Load

Regulation

Voltage

Reference

RC Filter

3

Buffer

RC Filter

Reference Driver

10kHz Sine

Wave

18-bit

1MSPS

Input Driver

Gain Network

REFP

Gain Network

Differential

Voltage

Source

Gain Network

+

VINP

Anti-Aliasing

Filter

+

VINM

SAR

ADC

Gain Network

2

1

Attenuate ADC kick-back noise

Stability of the input driver

Ultra Low THD

Low Output Imp

High BW and SR

Figure 2: Block Diagram Highlighting Primary Design Criteria for this DAQ Block

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise 3

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

2.1

Understanding ADC Dynamic Performance

The input driver circuit for an ADC consists of two parts: driving amplifier and a fly wheel RC filter. The

amplifier can be used for signal conditioning of the input voltage and its high input impedance and low

output impedance provides a buffer between the signal source and the ADC input. The RC filter helps to

attenuate the kick-back noise from the switched-capacitor input stage of the ADC as well as acts as an

anti-aliasing filter to band-limit the wideband noise contributed by the front-end circuit.

The main ac specifications under consideration for this design are SNR, THD, SINAD and ENOB.

Essentially, all these parameters are different ways of quantifying the noise and distortion performance of

an ADC based on a Fast-Fourier Transform (FFT) analysis. A typical FFT plot for an ADC is shown in

Figure 3.

Amplitude (dB)

Signal Being Digitized

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

SNR =

Signal Being Digitized

Noise

SINAD =

THD =

Signal Being Digitized

Noise + Harmonic Power

Signal Being Digitized

Harmonic Power

Harmonics

Noise

0

1k

2k

3k

4k

5k

6k

7k

8k

9k

10k

Frequency (Hz)

Figure 3: AC Specifications of an ADC

2.1.1

Signal-to-Noise Ratio (SNR)

SNR provides insight into the total noise of the system. The total noise of the data acquisition system is the

root-sum-square (rss) of the front-end amplifier noise (V n_AMP_RMS ) and the ADC noise (V n_ADC_RMS ). The

ADC noise includes the quantization noise as well as the noise contributed by ADC internal circuitry. The

total noise contributions from all these sources, denoted as V n_TOT_RMS are referred to the input of the ADC

for calculating total SNR of the system (SNR SYS ).

Vn _ TOT _ RMS = Vn2_ AMP _ RMS + Vn2_ ADC _ RMS

SNR SYS =

(1)

VSIG _ RMS

Vn _ TOT _ RMS

4 18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

(2)

SLAU515A-June 2013-Revised October 2015

�www.ti.com

2.1.2

Total Harmonic Distortion (THD)

THD is defined as the ratio of the rss of all harmonic components (generally 9 harmonics are used) to the

power of the fundamental signal frequency. It is generally specified with an input signal near full-scale

(FS), but in this design the input is kept 0.4dB below FS to prevent clipping. If the root-mean-square (rms)

th

value of input signal is denoted as V SIG_RMS and the power in n harmonic is denoted by V HAR_n_RMS , then

the total harmonic distortion (V HAR_TOT_RMS ) and THD can be calculated as:

2

2

2

VHAR _ TOT _ RMS = VHAR

_ 1 _ RMS + VHAR _ 2 _ RMS + 22 + VHAR _ 9 _ RMS

THD =

2.1.3

(3)

VSIG _ RMS

VHAR _ TOT _ RMS

(4)

Signal-to-Noise-and-Distortion Ratio (SINAD)

SINAD combines the effect of distortion and noise to provide a cumulative measure of the overall dynamic

performance of the system.

SINAD SYS =

2.1.4

VSIG _ RMS

2

n _ TOT _ RMS

V

2

+ VHAR

_ TOT _ RMS

(5)

Effective Number of Bits (ENOB)

ENOB is an effective measurement of the quality of a digitized signal from an ADC by specifying the

number of bits above the noise floor. For an ideal N-bit ADC with only quantization noise, the SNR (in dB)

can be calculated as:

SNR = 6.02 × N + 1.76

N=

SNR − 1.76

6.02

(6)

(7)

This definition for ENOB can be extrapolated to indicate the overall dynamic performance of a data

acquisition system by substituting SNR with SINAD SYS from equation

ENOB =

SLAU515A-June 2013-Revised October 2015

SINAD SYS − 1.76

6.02

(8)

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise 5

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

Therefore, in order to maximize the performance of a high precision ADC, it is important to keep both the

distortion and noise contribution from the front-end circuit at an extremely low-level. Based on equation 8,

the minimum THD and SNR requirements to achieve an ENOB 16-bit data acquisition system are

calculated in Figure 4.

16.5

ENOB (bits)

16

15.5

15

14.5

100dB SNR

14

95dB SNR

13.5

90dB SNR

13

80

85

90

95

|THD | (dB)

100

105

110

Figure 4: ENOB versus THD and SNR

2.2

Low Distortion Input Driver Design

In designing a very low distortion data acquisition block it is important to understand the sources of nonlinearity. Both the ADC and the input driver introduce non-linearity in a data acquisition block. To achieve

the lowest distortion, the input driver for a high performance SAR ADC needs to have a distortion that is

negligible against the ADC distortion. This requires the input driver distortion to be 10dB lower than the

ADC THD. This stringent requirement ensures that overall THD of the system is not degraded by more

than -0.5 dB.

THD AMP < THD ADC − 10 dB

(9)

It is therefore important to choose an amplifier that meets the above criteria to avoid the system THD from

being limited by the input driver. The amplifier non-linearity in a feedback system is dependent on the

available loop gain. The block diagram modeling the non-linearity is shown in Figure 5 below.

NL

VIN

+

+

A

∑

-

∑

VOUT

β

Figure 5: Non Linearity in a Feedback System

Vout =

Vin × A

NL

+

1 + Aβ 1 + Aβ

6 18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

(10)

SLAU515A-June 2013-Revised October 2015

�www.ti.com

The non-linearity (NL) in the above feedback system is divided by the loop gain (Aβ). The open loop gain

(A) of the amplifier is a function of frequency and typically degrades at -20dB/decade. This reduction of

open loop gain at higher frequencies causes the THD to degrade at high frequencies. To maintain a low

THD at higher frequencies it is therefore important to choose an amplifier with high gain bandwidth product

(GBW). This will ensure that there is sufficient loop gain available at higher input frequencies to maintain

the minimum required THD specification.

Most amplifier datasheet specify THD+N as a measured specification. It is important to understand that in

some amplifiers the noise dominates the THD+N specification. However, you can calculate just the THD

nd

rd

specification of the amplifier based on the 2 and 3 harmonic distortion (HD 2 and HD 3 respectively)

using Equation 11.

2

HD 3

HD

10

THD(dB) = 10 log10

+ 10 10

(11)

The distortion from the input driver however is not limited to the amplifier distortion specification but also

the amplifier configuration. The input driver can be configured either in an inverting or a non-inverting

configuration as shown in the Figure 6.

Gain Network

Gain Network

Vin

Vout

Vin

Gain Network

Vout

Vcm

+

Non Inverting Amplifier

+

Inverting Amplifier

Figure 6: Non-Inverting and Inverting Amplifier Configurations

The common mode of the input driver in a non-inverting configuration follows the input signal. This adds a

constraint on the input amplifier to have rail-to-rail inputs to allow full scale input signals. Furthermore, the

movement of the common mode of the input amplifier introduces additional common mode dependent

distortion at the output of the amplifier. In comparison, in the inverting configuration the common mode is

fixed and thus does not require rail-to-rail inputs and also does not introduce any additional common mode

dependent distortion. Therefore, in this design the input driver amplifier is configured in an inverting

amplifier configuration. This architectural choice helps improve the THD performance of the system

significantly. However, it does bring other trade-offs which will be explained later.

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise 7

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

2.3

Low Distortion Anti-Aliasing Filter Design

The conversion of analog to digital signals requires sampling an input at a constant rate. If the input

contains high frequency content higher than half the sampling rate, the high frequency content would be

folded back into the low frequency spectrum and digitized. This is called aliasing. Therefore an antialiasing filter is required to remove this harmonic content. An anti-alias filter is designed as a low pass filter

with its corner frequency being equal to the sampling rate. Designing the anti-aliasing filter corner

frequency at the sampling rate ensures that the input signal attenuation is kept to a maximum of 1dB while

filtering high frequency content from folding back. The anti-alias filter also helps limit the bandwidth and

noise at the output of the input driver amplifier.

The inputs of the SAR ADC are shown in Figure 7 introduce transient distortion during the acquisition

period. The input driver is not an ideal source with zero ohms of output impedance and infinite current

drive and thus the anti-alias filter helps with a few important design requirements. The capacitor C FLT helps

to reduce the kick-back noise at the ADC input and provides a charge bucket to quickly charge the input

capacitor C SH during the sampling process. The value of the capacitor C FLT should be chosen such that

when switch SW SAMP closes, the voltage droop (∆V FLT ) on C FLT is less than 5% of the input voltage.

R

R

Vin

Vout

Vcm

SWSAMP

RFLT

+

CFLT

CSH

Inverting Amplifier

Figure 7: Simplified Schematic of Single Ended Input Sampling Stage

Charge required for ADC sampling capacitor,

Charge supplied by filter cap,

Q IN = C SH × VREF

Q FLT = C FLT × ∆VFLT

≤

C FLT × (0.05 × VREF )

By the principle of charge conservation:

QIN = QFLT

CFLT × (0.05 × VREF ) ≥

C SH × VREF

CFLT ≥ 20 × C SH

8 18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

(12)

(13)

SLAU515A-June 2013-Revised October 2015

�www.ti.com

At this point, it is important to understand the trade-offs involved in selecting the values of C FLT and R FLT . If

the value of C FLT is high, it provides better attenuation against the kick-back noise when the sampling

switch closes. However, C FLT cannot be made arbitrarily high because it degrades the phase margin of the

driving amplifier, thus making it unstable. The series resistor R FLT acts as an isolation resistor, which helps

to stabilize the driving amplifier. A higher value of R FLT is helpful from the amplifier stability perspective, but

degrades ac performance and should be balanced with the amplifier stability to ensure that the distortion

does not exceed the required specifications. The distortion happens due to the non-linear input impedance

of the ADC and it increases with source impedance, input signal frequency and amplitude. It is important to

keep the anti-aliasing resistor (R FLT ) much lower than the switch resistance. A resistance of 20 times lower

than the switching resistor is preferred.

RFLT <

R SWITCH

20

(14)

The minimum value for R FLT is dependent on the output impedance of the amplifier based on stability

considerations. If the output impedance of the driving amplifier is equal to R O , its stability can be analyzed

by evaluating the effect of R FLT and C FLT on the amplifier’s open-loop response. The combination of R O ,

R FLT and C FLT introduces one pole, f P (equation 15) and one zero, f Z (equation 16) in the amplifier’s openloop response, for which the corner frequencies are given below:

fP =

1

2π(R O + R FLT )C FLT

fZ =

(15)

1

2πR FLT C FLT

(16)

In order to ensure that the phase change from the zero negates the phase change that the pole initiates, it

is important that the frequency distance between the pole and zero must be less than or equal to one

decade.

f

log Z

fP

≤ 1

(17)

Using equations (15) and (16), the minimum value for RFLT can be derived as:

R FLT ≥

R0

9

(18)

In the interest of stability, the effects of f Z must occur at a frequency lower than the closed-loop gain

bandwidth of the amplifier (f CL ). This is because for stability of the amplifier circuit, the closure rate

between the open and closed loop gain curves should not be greater than 20db/decade. In order to

account for the fabrication process variations associated with the amplifier’s performance, a good practice

is to choose f Z such that closed-loop gain bandwidth of the amplifier, f CL is at least twice the frequency of

the zero.

fCL

≥ 2

fZ

SLAU515A-June 2013-Revised October 2015

(19)

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise 9

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

For a fully differential amplifier combined with a fully differential SAR ADC the anti-aliasing filter is typically

designed as a differential filter as shown in Figure 8.

R

R

+

Vin

-

RFLT

+

R

+

REFP

VINP

+

Vout

-

CFLT

VINM

RFLT

SAR

ADF

R

Figure 8: Fully Differential Anti-Aliasing Filter

The anti-aliasing filter bandwidth for a fully differential system can then be calculated using equation 20. It

is important to note that for a fully differential filter the effective capacitance is twice for the RC Filter.

BWFLT =

2.4

1

2π × RFLT × (2 × CFLT )

(20)

System Noise Analysis

A high-performance 18-bit, 1MSPS SAR ADC has a typical SNR specification of 99dB for a 10 kHz input

signal and V REF = 5V. In order to maintain the superior dynamic performance of this ADC, the effect of

noise from the front-end circuit has been analyzed in this section. This analysis will provide a bound for the

maximum noise which the input driver circuit can have without degrading the system SNR. Based on the

maximum noise and appropriate input amplifier and feedback resistors can be chosen for the design.

The input driver in an inverting configuration requires input and feedback resistors compared to the noninverting configuration. This architectural choice has significant impact on the noise analysis. If we

consider the circuit in Figure 9, which is an amplifier in an inverting configuration with two resistors, we can

calculate the noise separately from each of the resistors and the op amp voltage noise. Each source has

its own contribution to the noise at the amplifier output. Noise referred to the input (RTI) is simply the noise

referred to the output (RTO) divided by the noise gain of the amplifier. Only considering the voltage noise

and not current noise the RTI Noise can be calculated as:

Vn_R2

*

Vn_R1

*

4kTR1

R1

R2

4kTR2

*

Vn_AMP

-

Vout

+

Figure 9: Noise Contribution in an Inverting Amplifier

1018-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

NG = 1 +

R2

R1

(21)

2

Vn_AMP_RTI_RMS = 1.57 × BWFLT × Vn _ AMP

2

R2

R1

+ 4kTR 1

+ 4kTR 2

R1 + R 2

R1 + R 2

2

(22)

Vn_AMP_RTO_RMS = NG × Vn_AMP_RTI_RMS

To calculate the RMS noise, the voltage noise density needs to be integrated over the anti-aliasing filter

𝜋

bandwidth. For an RC-filter, effective bandwidth is equal to (1.57) times the 3-dB cut-off frequency. It can

2

be observed that the thermal noise of the resistor contributes significantly to RTO noise. In an inverting

configuration the input amplifier is in a noise gain (NG) of 2. In this scenario the noise expressions in an

inverting gain of -1 can be simplified as:

Vn_AMP_RTI_RMS =

1.57 × BWFLT × Vn _ AMP + 4kT

2

Vn_AMP_RTO_RMS = 2 × 1.57 × BWFLT × Vn _ AMP

2

R

2

(23)

R

+ 4kT

2

In comparison to the single ended amplifier the fully differential amplifiers have feedback resistors on each

input as shown in Figure 10. The noise in a fully differential amplifier can be calculated as considering two

single ended amplifiers configured in an inverting configuration as shown in Figure 10. Both the single

ended amplifiers are identical and thus using law of superposition the noise of the fully differential amplifier

is calculated in expression 24.

R

R

R

R

+

Vin

-

+

R

+

+

Vout

-

Equivalent

+

Vin

-

Vcm

+

Vout

-

+

+

R

R

R

Figure 10: Fully Differential Amplifier Configuration

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise11

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

Vn_DIFF _ AMP_RTO _ RMS =

Vn_DIFF _ AMP_RTO_RMS =

(V

) + (V

)

2

n_AMP_RTO _ RMS

)

2

n_AMP_RTO_RMS

2 × (Vn_AMP_RTO_RMS

(24)

Vn_DIFF _ AMP_RTO_RMS = 2 × 1.57 × BWFLT × 2 * Vn _ AMP + 4kTR

2

According to the expression in equation 24 above, it is important to choose low resistor values for the

feedback of the amplifier for achieving low noise and high SNR from the amplifier. However, choosing a

low resistor values will increase the system power and also require amplifiers with high output current

drive. Thus it is important to make the appropriate choice to trade-off between system noise and power.

Now considering an ADC with an input dynamic range of V FSR , the input referred noise can be calculated

from the specified value of SNR in the datasheet by using equation below:

Vn _ ADC _ RMS =

VFSR

2 2

× 10

−

SNR (dB )

20

(25)

Hence, the total noise contribution from the total data acquisition system can be calculated as:

Vn _ TOT _ RMS = Vn2_ DIFF _ AMP _ RTO _ RMS + Vn2_ ADC _ RMS

(26)

To achieve a minimum SNR from the complete DAQ block (SNR SYS ), the maximum total rms noise from

the DAQ block needs to meet the requirement in equation 27 (combining equation 2 and 26).

VFSR

Vn2_ DIFF _ AMP _ RTO _ RMS + Vn2_ ADC _ RMS <

2 2 × 10

1218-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SNRSYS

20

(27)

SLAU515A-June 2013-Revised October 2015

�www.ti.com

2.5

Reference Driver Design

External voltage reference circuits are used with ADCs without internal references. They provide low drift

and very accurate voltages for ADC reference input. However, the output broadband noise of the

references is of the order of few 100µVRMS, which degrades the noise and linearity performance of

precision ADCs for which the typical noise is of the order of tens of µVRMS. Hence, in order to optimize

the ADC performance, it is critical to appropriately filter and buffer the output of the voltage reference.

The basic circuit diagram for the reference driver circuit for precision ADCs is shown in Figure 11.

RREF_FLT

Buffer

RBUF_FLT

Voltage

Reference

CREF_FLT

REFP

CBUF_FLT

ADC

Figure 11: Simplified Schematic of Reference Driver Circuit

The reference noise can be categorized into peak-to-peak low frequency flicker or 1/f noise (V 1/f_REF_pp )

from 0.1Hz to 10Hz and higher frequency broadband noise, generally specified as a noise spectral density

(e n_REF_RMS ) over a wide frequency range. The broadband output noise from the reference circuit can be

band-limited by the 3-dB cut-off frequency (f REF_3dB ) of an RC-filter at its output. So, the primary objective

for the filter design is to keep the bandwidth low enough such that the integrated noise from the reference

does not degrade the performance of the ADC. Hence, the total integrated noise from the reference

(V n_REF_RMS ) should be kept at least 3 times less than the ADC noise to prevent any noise degradation in

the system performance:

Vn _ ADC _ RMS

Vn _ REF _ RMS ≤

3

(28)

The value of V n_REF_RMS can be calculated by the root sum square (rss) of the flicker noise and broadband

noise density as shown below:

Vn _ REF _ RMS

V 1 _ REF _ pp

= f

6.6

2

p

+ e2

× fREF _ 3 dB

n _ REF _ RMS ×

2

(29)

Combining 28 and 29, we get:

V 1 _ REF _ pp

f

6.6

SLAU515A-June 2013-Revised October 2015

2

SNR (dB )

−

1 VFSR

p

+ e2

× fREF _ 3 dB ≤ ×

× 10 20

n _ REF _ RMS ×

2

3 2 2

(30)

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise13

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

The variation in the broadband noise density of the voltage reference ranges from 100 nV/√Hz to

1000 nV/√Hz depending on the reference type and power consumption. In general, the reference noise is

inversely proportional to its quiescent current (I Q_REF ). Since broadband noise density is not always

included in voltage reference datasheets, an approximation of the noise density for band-gap reference

circuits is provided in equation 31:

10000nV

e n _ REF _ RMS ≈

Hz

×

1

2 × IQ _ REF (in µA )

(31)

The above formula has been derived on the basis of the measured characteristic between the output noise

density and quiescent current of several TI reference circuits, as shown in Figure 12.

Figure 12: Characteristic Curve of Reference Noise vs. Current

On combining equations 29, 30, 31, the value of f REF_3dB can be derived as:

fREF _ 3 dB ≤

2 × IQ _ REF (µA )

(10000 nV /

Hz

)

2

SNR (dB )

2

V 1 _ REF _ ππ

−

2 1 VFSR

× × ×

× 10 10 − f

π 9

8

6 .6

2

(32)

The value of the capacitor for the RC-filter should be kept higher than 100nF to keep its thermal noise

lower than 0.2 µV RMS . Using the selected value for C REF_FLT and f REF_3dB , the value of R REF_FLT can be

calculated using equation

R REF _ FLT =

1

2πfREF _ 3 dB × C REF _ FLT

(33)

Once the noise of the reference block has been band-limited, the next important step is to ensure the

reference can drive the dynamic load posed by the ADC reference input. The reference buffer must

regulate the voltage such that ∆VREF stays within 1LSB error at the start of each conversion. This

necessitates the use of a capacitor (C BUF_FLT ) along with a buffer to drive the ADC reference pin. The

calculations to determine the size of C BUF_FLT are given below

1418-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

Difference in V REF between conversions:

∆VREF ≤

VREF

2N

If charge consumed during each conversion is QREF, then:

C BUF _ FLT =

Q REF

Q

× 2N

≥ REF

∆VREF

VREF

(34)

The average value of Q REF can be calculated from the maximum ADC conversion time (T CONV_MAX ) and the

average value of reference input current (I REF ) specified in ADC datasheets as below:

QREF = IREF × TCONV _ MAX

(35)

On combining equations 34 and 35, the minimum value of C BUF_FLT can be obtained:

C BUF _ FLT ≥

IREF × TCONV _ MAX × 2 N

VREF

(36)

The capacitor values derived from this equation are high enough to make the driving amplifier unstable, so

it is recommended to use a series resistor, R BUF_FLT to isolate the amplifier output and make it stable. The

value of R BUF_FLT is dependent on the output impedance of the driving amplifier as well as on the signal

frequency. Typical values of R BUF_FLT range between 0.1Ω to 2Ω and the exact value can be found by

using SPICE simulations. It should be noted that higher values of R BUF_FLT cause high voltage spikes at the

reference pin which affects the conversion accuracy.

After designing the appropriate passive filter for band-limiting the noise of the reference circuit, it is

important to select an appropriate amplifier for using as a reference buffer. The key specifications to be

considered when selecting an appropriate amplifier for reference buffer are:

Output Impedance: The output impedance for a reference buffer should be kept as low as possible. This

is because the ADC draws current from the reference pin during conversion and the resultant drop in

reference voltage is directly proportional to the output impedance of the driving buffer. It also helps to keep

the amplifier stable while driving a large capacitive load (C BUF_FLT ).

Input Offset: The input offset error of the buffer amplifier should be as low as possible to ensure that the

reference voltage driving the ADC is very accurate.

Offset Drift: The offset temperature drift of the reference buffer should be extremely low to make sure that

the reference voltage for the ADC does not change significantly over the operating temperature range. For

similar reasons, it is also important to keep a low long-term time drift for the buffer amplifier.

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise15

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

3

Component Selection

3.1

ADC Selection

This TI design has been optimized for low distortion and noise using TI’s high resolution, 18-bit 1MSPS

SAR ADC, ADS8881 at its maximum sampling rate for a full-scale differential sine wave input at 10 kHz.

The ADS8881 is a true differential SAR ADC designed for low voltage operation from 2.7 V–3.6 V AVDD

and 1.65 V–3.6 V DVDD. The ADS8881 has excellent dynamic performance while consuming very low

power. The power dissipation is 5.5mW (typical) at 1MSPS and can be further scaled down linearly for

applications requiring low throughput.

3.2

Input Driver: Amplifier Selection

The primary goal for this design is to achieve a DAQ block with the lowest distortion and noise. The most

important consideration for achieving this system specification is to select a full differential amplifier with

low distortion (THD) for driving the inputs of the SAR ADC. This design is specified for a full scale

sinusoidal signal, the op amp should support rail-to-rail output (RRO) swing. The other key specifications

in order to meet the performance goals for this application are slew rate, output current drive, and low

power.

The THS4521 is a very low power, fully differential op amp with rail-to-rail output and an input common

mode range that includes the negative rail. The amplifier is designed for low-power data acquisition

systems where power dissipation is a critical parameter. The amplifier provides exceptional ac

performance that meets the very low distortion and high slew rate required from the input driver.

3.3

Input Driver: RC Filter Passive Component Selection

The critical passive components for this design are the resistors (R FLT ) and capacitor (C FLT ) for the RCfilter at the input of the ADC. The tolerance of the resistor was chosen to be 0.1%, but when this was not

possible due to reasonable cost or availability, the tolerance was chosen to be 1%.

The design of the low distortion anti-aliasing filter is important to maintain the very low THD and noise

requirement from the analog front end. The distortion due to the non-linear input impedance of the ADC

increases with source impedance. It is therefore important to keep the anti-aliasing resistor (R FL T ) much

lower than the switch resistance as explained in section 2.3. The switch resistance of the ADS8881 is

220Ω therefore the maximum R FL T can be calculated below as

R SΩITCH

20

< 11Ω

RFLT <

RFLT

(37)

The value for the resistor RFLT needs also to maintain the stability of the driving amplifier and is

dependent on the output impedance of the driving amplifier, as explained in equation. The output

impedance of THS4521 is dependent on the frequency of operation.

Using equation, the minimum value for resistance R FLT can be calculated as:

R FLT ≥

80

≈ 9Ω

9

(38)

Therefore in this design the R FLT is chosen to be 10Ω to meet both the minimum and maximum

requirements described above. Higher anti-aliasing resistor value can be chosen however this will results

in additional distortion.

1618-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

The input capacitance of ADS8881 is 59pF, therefore according to equation:

CFLT ≥ 20 × C SH

(39)

CFLT ≥ 1.18nF

In general it is beneficial to design a RC filter with bandwidth as low as possible to filter out amplifier noise.

However, the practical limitation on the choosing large ceramic C0G capacitor due to cost imposes a

maximum value on the capacitor value selection. In this design the selected value of capacitance for the

differential input of the ADC is 10nF. Based on the RC values, the bandwidth of the anti-aliasing filter can

be calculated using equation 20 as:

Table 2: Bandwidth Calculation of the Anti-Aliasing Filter

10 Ω

R FLT

10 nF

C FLT

800 kHz

BW FLT

This solution is designed to achieve the lowest distortion and noise while conserving power. Therefore the

feedback resistors in the inverting gain of -1 configuration are chosen to be 1 kΩ. The choice of 1 kΩ

resistor and the anti-alias filter bandwidth imposes a maximum amplifier noise requirement to meet the

minimum system SNR (SNR SYS ) specification. The calculations on maximum amplifier noise based on

theory described in Section 2.4 are highlighted using parameters defined in Table 3.

Table 3: Parameter for Amplifier Noise Calculation

Required SNR SYSTEM

98 dB

V FSR

4.315 V

ADC SNR

99 dB

BW FLT

800 kHz

R

1000 Ω

Vn _ TOT _ RMS =

VFSR

2 2 × 10

Vn _ ADC _ RMS =

SNRSYSTEM

20

VFSR

2 2

× 10

=

4.315

2 2 × 10

−

SNR (dB )

20

98

20

= 38µV

= 34µV

(40)

(41)

Therefore to meet the required SNR for the system the maximum rms noise from the amplifier can be

calculated using equation 26. The maximum voltage noise density of the amplifier can be calculated using

equation 27.

Vn _ DIFF _ AMP _ RTO _ RMS < V 2 n _ TOT _ RMS − Vn2_ ADC _ RMS < 17µV

SLAU515A-June 2013-Revised October 2015

(42)

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise17

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

Vn_DIFF _ AMP_RTO_RMS = 2 × 1.57 × BWFLT × 2 * Vn _ AMP + 4kTR < 17µV

2

Vn_DIFF _ AMP_RTO_RMS < 4.52

(43)

nV

Hz

Based on the above calculation the amplifier voltage noise needs to have less than the 4.52 nV/√Hz. For a

fully differential amplifier this requirement translates to a maximum voltage noise density of 6.4 nV/√Hz.

This is because fully differential amplifier datasheets specify noise for a fully differential signal path. It is

important to understand that to achieve ENOB of 16-bit the input driver needs to meet the minimum THD

and noise specification. Thus the selected amplifier, THS4521 meets these minimum requirements based

on the calculation above. Summary of key specification of the THS4521 are shown in Table 4.

Table 4: Key Parameters for the THS4521

Parameter

THD @ 10kHz

Fully Differential

Voltage Noise Density

Iout

Bandwidth

Iq

3.4

Datasheet Specification

-132 dBc

4.6 nV/√Hz

55 mA

145 MHz

1.14 mA/ch

Reference Driver: Passive Components Selection

The external reference used to drive the ADS8881 in this design is the REF5045 from TI. This reference

has been selected because it provides the highest possible reference voltage of 4.5V in a system with only

a 5V supply. As mentioned in the datasheet of REF5045, it requires a capacitance of 10µF at the V OUT pin

for stability purposes. A series resistor of 0.2Ω is used with the 10µF capacitor for proper power-up of the

reference.

As explained in Sec. 2.5, the noise from the reference should be bandwidth limited by designing a lowpass RC filter at the reference output. According to equation 31, the 3-dB bandwidth of this filter should be

such that:

(V )2 IQ _ REF (in µA ) (4.5 )2

1000

fREF _ 3 dB ≤ REF2N+2 ×

× −10

=

2

2×18 + 2

−10

10 V

10

π × 2

π × 2

fREF _ 3 dB ≤ 234.5 KHz

(44)

The value of capacitor C REF_FLT has been selected as 1 µF to keep the thermal noise of the capacitor at a

low value. Hence, the value of R REF_FLT can be calculated using equation 15 as:

R REF _ FLT ≥

1

= 678.7Ω

2π × 234.5 × 10 3 × 10 −9

(45)

The value of R REF_FLT has been selected as 1 kΩ for this design.

1818-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

The next important passive element in reference design is the capacitor C BUF_FLT , which helps to regulate

the voltage at the ADC reference pin under load conditions. According to ADS8881 datasheet, the average

current drawn into the reference pin (I REF ) is equal to 200 µA and for a maximum throughput of 1MSPS,

T CONV_MAX is equal to 710ns. Hence, according to equation 35, the value of C BUF_FLT can be calculated as:

C BUF _ FLT

200 × 10 −6 × 710 × 10 −9 × 218

≥

= 8.27µF

4 .5

(46)

The value of C BUF_FLT has been selected as 10 µF for this design.

3.5

Reference Driver: Amplifier Selection

As explained in Sec. 2.3, the key amplifier specifications to be considered to design a reference buffer for

a high-precision ADC are low offset, low drift, wide bandwidth and low output impedance. While it is

possible to pick an amplifier, which sufficiently meets all these requirements, it comes at a cost of

excessive power consumption. For example, the OPA350 is a 38MHz bandwidth amplifier with a maximum

offset of 0.5mV and low offset drift of 4µV/ºC, but it consumes a quiescent current of 5.2mA, which is

extremely high for this design. This is due to the fact that from an amplifier design perspective, offset and

drift are dc specifications while bandwidth, low output impedance and high capacitive drive capability are

high frequency specifications. Thus, achieving all the performance in one amplifier requires power.

However, a more efficient design to meet the low power budget is to use a composite reference buffer,

which utilizes an amplifier with superior high frequency specifications in the feedback loop of a dc precision

amplifier to get the overall performance at much lower power consumption.

In this design, the reference buffer is designed using two amplifiers – THS4281 and OPA333 in composite

double feedback architecture as shown in Figure 13.

RF ≥ 20*R

CF ≥ C

-

R ≥ 1KΩ

-

RREF_FLT

OPA333

+

CREF_FLT

THS4281

+

+

RBUF_FLT

+

C≥100nF

AVDD

AVDD

CBUF_FLT

Figure 13: Schematic of Reference Buffer Circuit

The THS4281 has a wide 3-dB bandwidth of 90MHz at a gain of 1 and output impedance of 1Ω for 1MHz

operation, with a maximum quiescent current of only 1mA. This makes it ideal for driving the high capacitor

C BUF_FLT and regulating the voltage at the ADC reference input. However, the THS4281 suffers from poor

offset (2.5mV max.) and drift (7µV/ºC max.) specifications. In order to improve the DC specifications of the

reference buffer, the OPA333 is used as a dc correcting amplifier. The OPA333 is a zero-drift (0.05µV/ºC

max.) and low offset (10µV max.) amplifier with a maximum quiescent current of only 25µA. Thus, for

similar performance related to reference accuracy and load-regulation, this two amplifier approach

provides almost 5X power savings compared to a single amplifier buffer.

In this reference buffer design, the noise specifications of the dc amplifier (OPA333) are not very important

because it gets heavily filtered by the low frequency RC-filter at its output. The value of C is chosen to be

greater than 100nF to keep the capacitor thermal noise to be less than 0.2µV RMS and the value of R is

selected greater than 1 kΩ to avoid any stability issues due to high capacitive loading.

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise19

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

This amplifier uses a dual feedback in this design, out of which one feedback is active during dc operation

and the other feedback is active during higher frequency ac operations. Figure 14 displays the dc model of

the circuit where RF appears as a short and CF appears as an open. This feedback connects the output of

THS4281 directly to the inputs of OPA333, which then corrects for its offset and drift. The value of RF

should be at least 20 times greater than R to avoid any stability issues.

-

R ≥ 1KΩ

-

RREF_FLT

OPA333

THS4281

+

+

RBUF_FLT

+

+

C≥100nF

AVDD

AVDD

CREF_FLT

CBUF_FLT

Figure 14: DC Equivalent Schematic of Reference Buffer

The active feedback connection during higher frequency operation is shown in Figure 15. At such

frequencies of operation, RF acts as open connection; CF acts as a short and the two amplifiers are

connected as isolated unity-gain buffers. The value of CF should be equal to or greater than C to avoid

any stability issues.

-

R ≥ 1KΩ

-

RREF_FLT

OPA333

+

CREF_FLT

THS4281

+

+

RBUF_FLT

+

C≥100nF

AVDD

AVDD

CBUF_FLT

Figure 15: High Frequency Equivalent Schematic of Reference Buffer

2018-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

4

Simulation

The TINA-TI™ schematic shown in Figure 16 shows the final design and selected components as

explained in the previous sections.

AVDD

3

7

R14 1k

+

+

-

C7 1u

2

U6 THS4281

6

-

AVDD

C3 1u

Vcm

VREF

R10 200m

C11 10u

C5 1u

1

C8 1u

GND Trim

4

U5 OPA333

+

2

Tem p

tower Supplies

AVDD

+

4

Vout

3

R11 200m

Vin

Temp

R12 1k

5

AVDD U1 REF5045

V3 2.35

V2 5

C4 10u

R13 20k

V1 3.3

Reference 5river /ircuit

R5 1k

Vadc+

R16 1k

R9 10

1

-

-

Vref/2

2

-

+

R17 1k

+ +

+5V

-

5

U4 THS4521

C2 10n

ACQ

R8 10

ADS8881

AINM

AINPsmpl

AINMsmpl

+

CNV

ACQ

4

R15 10

1MSPS

CONV

+

V

Vin_sh

GND

R6 1k

VG1

-

AVDD

AINP

PD

FDA+

3

8

VCVS4 500m

+

+

REFP

U7 ads8881

R7 10

6

7

VCVS3 -500m

+

+

Vadc-

-

Input 5river /ircuit

Figure 16: TINA-TI

TM

– Schematic Showing Complete Data Acquisition Block

The circuit in Figure 16 was simulated to perform a transient simulation using a 10 kHz sine wave signal to

check that the ADC inputs are settling to sufficient accuracy before the start of every conversion. The

same circuit is also used to simulate accurate settling of reference input voltage at the beginning of each

conversion. The simulation details and results are provided in the subsequent sections.

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise21

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

4.1

Stability of Input Driver Amplifier

The TINA-TI™ schematic used to check the stability of the input drivers is shown in Figure 17.

+5V

Vo+

Vref/2

Vref

+3.3V

+

V

V1 5

Vout

V2 4.5

V3 2.25

V4 3.3

Vo-

Vref

+3.3V

REFP

AVDD

R1 1k

C2 1T

Vin+

-

1

+

Vfb

Vin

V

Vref/2

2

-

+

VCVS2 -500m

+

+

C3 1T

Vin-

R8 1k

CNV

AINP

ACQ

ACQ

4

FDA+

-

8

+ +

Vin- +5V

5

U1 THS4521

C1 10n

R4 10

Vo-

ADS8881

AINM

R6 10

AINPsmpl

INP

AINMsmpl

INN

GND

R2 1k

VG1

-

L2 1T

U3 ads8881

PD

3

V

R5 10

Vo+ R3 10

L1 1T

+

-

Vin+

R7 1k

6

7

VCVS1 500m

+

+

-

Figure 17: TINA-TI

TM

– Schematic for Checking Input Driver Stability

A large inductor of value 1 TH is connected in the feedback loop of the amplifier, so it behaves like an

open-loop configuration at frequencies higher than dc. The circuit has been simplified by considering only

(2)

half-circuit of the differential input structure . In order to load the amplifier output appropriately, the ADC

is connected with “CNV” pin tie to GND so that it is always sampling the input signal. The ac magnitude &

phase response for this circuit is shown in Figure 18.

T

140.00

Gain (dB)

AOL=Beta_inv @ 39.6MHz

Gain :

aol

betainv

70.00

Phase :

aolbeta

Phase (Deg)

0.00

180.00

Phase Margin: 69.4Deg

90.00

0.00

10.00

100.00k

1.00G

Frequency (Hz)

Figure 18: TINA-TI

TM

Schematic Result - AC Magnitude & Phase Plot for Input Drivers

The resulting phase margin of 69.4º at the 0-dB cross-over frequency of 39.6MHz validates the stability of

the input drivers for this design.

2218-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

4.2

Noise of Input Driver Amplifier

The TINA-TI™ schematic used to simulate the integrated rms noise of the input driver is shown in Figure

19. Ideally to calculate the RTO noise from the input driver, the voltage noise density curve needs to be

integrated to infinity. For a realistic approximation of the referred to the output rms noise; integration to a

decade beyond the bandwidth of the system is sufficient. Figure 20 shows the simulated integrated noise

from the fully differential amplifier input driver referred to output is 13.45 µVRMS which meets the design

requirements.

+5V

Vadc+

Vref

Vref/2

+3.3V

+

V

Vout

V1 5

V2 4.5

V3 2.25

V4 3.3

VadcVref

+3.3V

REFP

AVDD

R1 1k

Vadc+

R7 1k

-

Vref/2

2

+ +

+5V

R8 1k

+

-

5

U1 THS4521

ACQ

ADS8881

AINM

R6 10

AINPsmpl

INP

AINMsmpl

INN

GND

Vadc-

TM

TM

C1 10n

R4 10

-

Figure 19: TINA-TI

Figure 20: TINA-TI

ACQ

4

R2 1k

VG1

-

AINP

PD

FDA+

3

8

VCVS2 500m

+

+

CNV

R3 10

1

-

U3 ads8881

R5 10

6

7

VCVS1 -500m

+

+

– Schematic for Checking Input Driver Noise

Schematic Result – Integrated Fully Differential Amplifier RMS Noise

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise23

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

4.3

Transient Simulation of ADC Input Circuit

The TINA-TI™ schematic shown in Figure 16 is used to check the accurate settling of the sine-wave signal

at the inputs of the ADC during sampling phase. The simulated time-domain response for the circuit is

shown in Figure 21. The transient plot on the top shows one cycle of a 10 kHz sine-wave with an

amplitude of ±4.63V applied at the differential inputs of the ADS8881. The signal "Vin" represents the

actual input signal at the differential inputs of the ADC and the signal "Vin_sh" shows the output of the

ADC's input sample-and-hold circuit, as explained in Section 4. The lower plot shows the same waveform

zoomed in on time scale for more details. The curves are collated together to show that the sampled signal

accurately tracks the input signals during sampling and stays on hold when the ADC is converting.

Figure 21: TINA-TI

TM

Schematic Result – Digitization of Input Sine-Wave Showing ADC Sample & Hold

2418-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

4.4

Settling Response of ADC Reference Input

The TINA-TI™ schematic shown in Figure 16 is used to check the settling of the reference buffer output,

driving the REFP pin of the ADS8881. As explained in Section 2.3, the voltage at the reference pin should

settle to less than the LSB of the ADC for maintaining the overall system performance. The size of the LSB

for the ADS8881 using VREF = 4.5V is equal to 34.3µV. According to the transient simulation plot shown

in Figure 22, the error in the voltage at the REFP pin between two successive conversions is

∆VREF = 0.3µV, which is significantly less than the size of LSB. This validates that the reference voltage

has settled to sufficient accuracy to maintain the performance of this design.

a

4.00

a

bb

CONV

0.00

4.50231125

VREF

∆ Vref

0.3uV

∆Vref

==

0.3µV

4.50230915

36.00u

35.00u

Figure 22: TINA-TI

SLAU515A-June 2013-Revised October 2015

TM

37.00u

Time (s)

38.00u

39.00u

Schematic Result – ADC Reference Settling

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise25

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

5

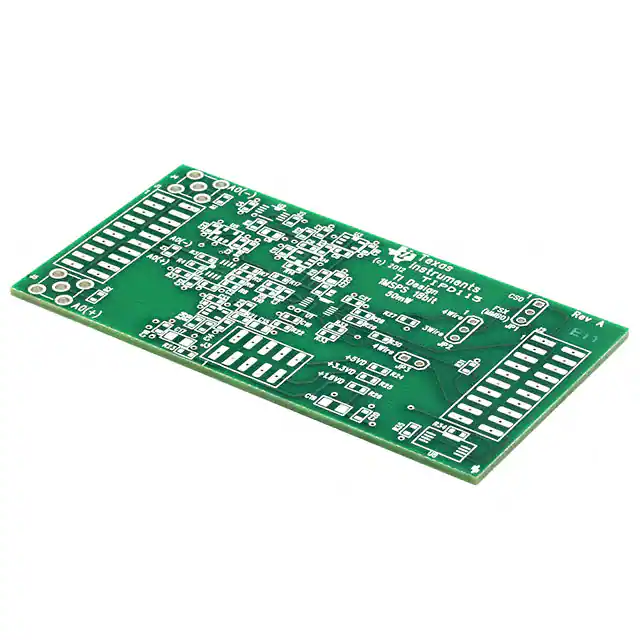

PCB Design

The PCB schematic and bill of materials can be found in Appendix A.

5.1

PCB Layout

The most important considerations in designing the PCB layout for this DAQ block are discussed below:

•

The length of traces from the reference buffer circuit (REF5045, THS4281 and OPA333) to the

REFP input pin of the ADC should be kept as small as possible to minimize the trace inductance

that can lead to instability and potential issues with the accurate settling of the reference voltage

•

The input driver circuit, comprised of THS4521 should be located as close as possible to the

inputs of the ADC to minimize loop area, thus making the layout more robust against EMI/RFI

rejection. Similarly, the resistors and capacitor of the anti-aliasing filter at the inputs of the ADC

should be kept close together and close to the inputs of the ADC to minimize the loop area.

•

The traces feeding the differential input voltage from the source up to the differential inputs of the

ADC should be kept symmetrical without any sharp turns.

The complete PCB layout for this design is shown in Figure 23.

Figure 23: TI Design – 16-bit 50mW DAQ Block PCB Layout

2618-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

6

Verification & Measured Performance

The measurement results for the verification of this design are listed in this section.

6.1

DC Noise Measurement

All ADC circuits suffer from some amount of inherent broadband noise contributed by the internal resistors,

capacitors and other circuitry, which is referred to the inputs of the ADC. The front end driver circuit also

contributes some noise to the system, which can also be referred to the ADC inputs. The cumulative noise,

often called as the input-referred noise of the ADC has significant impact on the overall system

performance. The most common way to characterize this noise is by using a constant dc voltage as the

input signal and collecting a large number of ADC output codes. A histogram can then be plotted to show

the distribution of output codes, which can be used to illustrate the impact of noise on the overall system

performance. In this design, the dc noise for the system is measured by shorting the inputs of both input

driving amplifiers to a common mode voltage, V cm = ½ x V REF = 2.25V, such that the differential voltage at

the inputs of the ADC is equal to V DIFF = 0V. The resulting histogram of output codes is shown in Figure

24.

Figure 24: Measurement Data – Histogram Showing DC Noise (Mid-Scale)

The distribution of output codes looks like a Gaussian distribution which indicates a properly designed

system. However, if the output code distribution has large peaks and valleys which make it distinctly nonGaussian, then it indicates significant DNL errors in the ADC or issues with the system design like

insufficient power supply decoupling, improper ground connections and/or other poor PCB layout effects.

For a theoretically perfect ADC system, the histogram of output codes will be a single vertical bar since the

ADC output will always be the same for a dc input voltage. However, the noise contributions from the ADC

and the front-end circuit lead to a distribution of output codes, which provides a measure of the overall

system's dc noise. The measured values of peak-to-peak difference between the codes (N PP ) and the

standard deviation of codes (N σ ) are listed in Table 5.

The Noise-Free Resolution of an ADC is defined as the number of steady output bits from the converter

beyond which the system performance is dominated by noise and it is not possible to differentiate between

individual code transitions. This is an extremely conservative measurement of the ADC's performance

because the formula for noise-free resolution is derived from the peak-to-peak code noise, which is

extremely dependent on the total number of samples.

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise27

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

A more reliable approach is to use the standard deviation of output codes (N σ ) in calculating the Effective

Resolution of the ADC. Please note that the results shown in Table 5 do not assume a Gaussian based

formula in calculating the standard deviation from the peak-to-peak value because the overall dc noise is

comparable to the size of the LSB. For an 18-bit ADC used in this design, the measured value of Effective

Resolution is also equal to 18 bits which indicates that there is no degradation in the converter's

performance due to the effects of dc noise.

Please note that the Effective Resolution and Effective Number of Bits (ENOB) shown in Section 6.2

should not be confused with each other as they are two completely different entities. The ENOB for an

ADC is measured with an ac sinusoidal input signal and includes the effects due to quantization noise and

distortion terms, which have no impact on a dc measurement.

Table 5: Measurement Results for DC Noise

Parameter

Formula

Measured Value

Mean Output Code

NA

9.17

NA

7

Peak-to-Peak Code

Noise (N PP )

Standard Deviation (N σ )

NA

0.752

2

log 2

N

PP

2 18

log 2

Nσ

18

Noise-Free Resolution

Effective Resolution

15.19

18

2818-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

6.2

ADC Dynamic Performance Measurement

The design explained in this document has been optimized to achieve maximum performance out of

ADS8881 at 1MSPS throughput for a full-scale transient input signal. Table 6 displays the ac performance

of the data acquisition block. The measurements have been performed using a 10 kHz sinusoidal input

signal. Figure 25 shows the FFT of the data acquisition block. The datasheet specifications are done for

V REF = 5V, but these measurements results indicate the ADC performance for V REF = 4.5V, which implies

that the measured values are approximately 0.9dB less than the actual ADC performance for SNR, THD

and SINAD. Despite this adjustment, the measured THD of -110.04 from the system is at par with the

specified THD of ADS8881. The data acquisition system is therefore able to achieve an ENOB of 16-bit

as calculated in Table 6.

Data Acquisition Block: FFT Spectrum

0

-20

-40

dBc

-60

-80

HD2

-100

HD3

-115.0 -112.4

-120

-123.1

-140

-125.1

-130.1

-129.6

-144.6

-142.2

-137.2

-160

0

20

40

60

80

100

120

Frequency (kHz)

Figure 25: Measurement Result for FFT of the Data Acquisition Block

Table 6: Measurement Results for ADC AC Performance

Parameter

Signal-to-Noise Ratio - SNR (dB)

Total Harmonic Distortion – THD (dB)

Signal-to-Noise & Distortion – SINAD (dB)

Effective Number of Bits – ENOB

SLAU515A-June 2013-Revised October 2015

Specification

(V REF = 5V)

Measurement

(V REF = 4.5V)

99 dB

98.73 dB

-110 dB

-110.04 dB

98 dB

98.4 dB

16

16.05

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise29

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

6.3

ADC Linearity Measurement

The linearity of the system was measured by sweeping the differential input voltage from -4.45V to 4.45V

in 26 voltage steps and the integral non-linearity (INL) error is plotted after cancelling the offset and gain

errors from the response. The 26-point INL plot is shown in Figure 26 . The DAQ block provides the best

linearity performance of ±1.5 LSB as seen in the figure below. The amplifier used in the front end driver

(THS4521) has low output impedance which results in extremely low distortion.

ADC 18-bit Linearity Error

Integral Non-Linearity Error (LSB)

1.50

1.00

0.50

0.00

-0.50

-1.00

-1.50

-4.5

-3.5

-2.5

-1.5

-0.5

0.5

1.5

2.5

3.5

4.5

ADC Differential Input

Figure 26: Measurement Data – ADC INL Plot (26 Points)

3018-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

7

Modifications

The comparison in Table 7 shows some other low distortion and low noise RRO fully differential amplifiers

from TI’s portfolio which were considered for this design.

Table 7: Several alternative amplifiers compared with the THS4521

Op Amp

Quiescent

Current (mA)

Noise Density

@ 10kHz

(nV/√Hz)

Total Harmonic

Distortion (dB)

Bandwidth

(MHz)

THS4521

1.14

4.6

-132

145

THS4531

0.25

10

-121

36

THS4031

7.9

1.6

100

The design principles described in this TI Precision Design can also be applied for applications that require

higher throughput than 1 MSPS. An example application circuit using the ADS9110 is shown in Figure 27.

The ADS9110 is an 18-bit, 2 MSPS SAR ADC with best-in-class ±0.5 LSB INL and 100dB SNR

specifications under typical operating conditions. The input signal is processed through the OPA2625, a

high-bandwidth, low-distortion, high-precision dual amplifier in an inverting gain configuration, and a lowpass RC filter before being fed into the ADC. Generally, the distortion from the input driver must be at least

10 dB less than the ADC distortion. The distortion resulting from variation in the common-mode signal is

eliminated by using the OPA2625 in an inverting gain configuration. The low-power OPA625 as an input

driver provides exceptional ac performance because of its extremely low-distortion and high bandwidth

specifications. In addition, the components of the antialiasing filter are such that the noise from the frontend circuit is kept low without adding distortion to the input signal. The reference buffer is designed with

the OPA625 and OPA378 in a composite architecture to achieve superior dc and ac performance at

reduced power consumption, compared to using a single high-performance amplifier.

30 kΩ

Reference Drive Circuit

10 pF

499 Ω

-

4.7 Ω

OPA625

+

+

220 nF

0.1 µF

1 kΩ

OPA+

-

2.49 kΩ

OPA378

+

+

1 kΩ

REF5045

(See Reference Datasheet

for Detailed Pin Configuration)

OPA+

0.1 µF

4.99 kΩ

OPA+

1 µF

1 nF

10 µF

1 kΩ

10 µF

1 kΩ

-

-VDIFF/2

OPA625

1.18 VDC

10 µF

10 nF

REFM REFP REFP REFM

2.2 Ω

+

AINP

V+

VINCM = 0 V

CONVST

ADS9110

1 µF

+

AINM

OPA625

+VDIFF/2

CONVST

2.2 Ω

GND

AVDD

DVDD

10 nF

1 kΩ

GND

AVDD DVDD

1 kΩ

Input Driver

SAR ADC

1 nF

Figure 27: Differential Input DAQ Circuit for Lowest Distortion and Noise at 2 MSPS

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise31

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

The performance of this circuit is measured using a 2 kHz sinusoidal input signal. Figure 28 shows the

FFT plot of the data acquisition block and the various performance specifications are mentioned in Table

8. The datasheet specifications are done for VREF = 5V, but these measurements results indicate the

ADC performance for VREF = 4.5V, which implies that the measured values are approximately 0.9dB less

than the actual ADC performance for SNR, THD and SINAD. Despite this adjustment, the measured THD

of -120.2 from the system is better than the specified THD of ADS9110.

Figure 28: Measurement Result for FFT of the Data Acquisition Block

Table 8: Measurement Results for ADS9110 at 2 MSPS

Specification

(V REF = 5V)

Measurement

(V REF = 4.5V)

Signal-to-Noise Ratio - SNR (dB)

100 dB

99.3 dB

Total Harmonic Distortion – THD (dB)

-118 dB

-120.2 dB

Signal-to-Noise & Distortion – SINAD (dB)

99.9 dB

99.3 dB

Parameter

3218-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

Appendix A. Appendix

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise33

Copyright © 2013, Texas Instruments Incorporated

�www.ti.com

A.1 Electrical Schematic

Figure A-1: Electrical Schematic

3418-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise

Copyright © 2013, Texas Instruments Incorporated

SLAU515A-June 2013-Revised October 2015

�www.ti.com

A.2 Bill of Materials

Item

QTY

1

1

2

5

0.1u

3

1

10000p

C3

4

9

1u

C4, C5, C7, C8, C9,

C12, C13, C21, C24

5

3

10u

C6, C15, C22

6

3

1000p

C16, C18, C20

7

2

10u

C17, C19

8

2

J1, J2 (Top)

9

2

J1, J2 (Bottom)

10

1

J3 (Top)

11

1

J3 (Bottom)

12

2

J4, J5

CONN SMA JACK STRAIGHT PCB

13

2

JP1, JP2

Header Strip, 3 pin .100" Gold (1x3)

14

1

JP3

Header Strip, 2 pin .100" Gold (1x2)

7

R1, R2, R20, R24,

R26, R34, R36

Not Installed

15

16

Value

Ref Des

Description

C1

C2, C10, C11, C14,

C23

Not Installed

Capacitor, X7R Ceramic +/-10%, 25WV,

0603

Capacitor, NP0 Ceramic +/-5%, 50WV,

0603

Capacitor, X7R Ceramic +/-10%, 25WV,

0603

Capacitor, X7R Ceramic +/-10%, 10WV,

0805

Capacitor, C0G Ceramic +/-5%, 50WV,

0603

Capacitor, X7R Ceramic +/-10%, 16WV,

1206

Header 20 Pin SMT Plug, .100" Gold

(2x10)

Header 20 Pin SMT Socket, .100" Gold

(2x10)

Header 10 Pin SMT Plug, .100" Gold

(2x5)

Header 10 Pin SMT Socket, .100" Gold

(2x5)

Resistor, Thin Film Chip, 0.1%, 1/10W,

0603

Resistor, Thick Film Chip, 1%, 1/10W,

0603

Manufacturer

Part Number

Murata

GRM188R71E104KA01D

TDK

C1608C0G1H103J

Murata

GRM188R71E105KA12D

Murata

GRM21BR71A106KE51L

Murata

GRM1885C1H102JA01D

TDK

C3216X7R1C106K

Samtec

TSM-110-01-L-DV-P

Samtec

SSW-110-22-F-D-VS-K

Samtec

TSM-105-01-L-DV-P

Samtec

SSW-105-22-F-D-VS-K

Amphenol

132134

Emerson

Samtec

142-0701-201

TSW-103-07-L-S

Samtec

TSW-102-07-L-S

Panasonic

ERA-3AEB102V

Vishay/Dale

CRCW060310R0FKEA

Susumu

RL0816S-R22-F

Panasonic

ERJ-3EKF1001V

Panasonic

ERJ-3GEY0R00V

Panasonic

ERJ-3EKF2002V

Panasonic

TI

ERJ-3EKF47R0V

ADS8881IDGS

4

1k

5

10

R3, R4, R5, R6

R7, R8, R9, R10,

R22

3

0.22

R11, R16, R21

3

1k

5

0

5

20k

5

1

47

23

R12, R13, R37

R14, R19, R23, R25,

R30

R15, R17, R18, R27,

R31

R28, R29, R32, R33,

R35

U1

24

1

U2

IC VREF SERIES PREC 4.5V 8-MSOP

TI

REF5045IDGK

25

1

U3

IC OPAMP CHOP R-R 350KHZ SOT23-5

TI

OPA333AIDBV

26

1

U4

IC OPAMP VFB R-R 95MHZ SOT23-5

TI

THS4281DBV

27

1

U5

IC OPAMP GP R-R CMOS SOT23-5

TI

OPA330AIDBV

28

1

U6

IC REG LDO 3.3V .15A SOT-23-5

TI

TPS78833DBV

29

1

U7

IC OPAMP DIFF R-R 145MHZ 8MSOP

TI

THS4521IDGK

30

1

U8

IC EEPROM 256KBIT 400KHZ 8TSSOP

Microchip

24LC256-I/ST

17

18

19

20

21

22

Resistor, Thin Film Chip, 1%, 1/5W, 0603

Resistor, Thick Film Chip, 1%, 1/10W,

0603

Resistor, Thick Film Chip, 1/10W, 0603

Resistor, Thick Film Chip, 1%, 1/10W,

0603

Resistor, Thick Film Chip, 1%, 1/10W,

0603

IC ADC 16-bit 1MSPS Fully Diff 10-MSOP

Figure A-2: Bill of Materials

SLAU515A-June 2013-Revised October 2015

18-Bit, 1MSPS Data Acquisition Block (DAQ) Optimized for Lowest Distortion and Noise35

Copyright © 2013, Texas Instruments Incorporated

�IMPORTANT NOTICE FOR TI REFERENCE DESIGNS

Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers (“Buyers”) who are developing systems that

incorporate TI semiconductor products (also referred to herein as “components”). Buyer understands and agrees that Buyer remains

responsible for using its independent analysis, evaluation and judgment in designing Buyer’s systems and products.

TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any

testing other than that specifically described in the published documentation for a particular reference design. TI may make

corrections, enhancements, improvements and other changes to its reference designs.

Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the

reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL

OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY

OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right,

or other intellectual property right relating to any combination, machine, or process in which TI components or services are used.

Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE

REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR

COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY

INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE

FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO

OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE

LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY

THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN

ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER’S USE OF TI REFERENCE DESIGNS.

TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per