XS1-G04B-FB144 Datasheet

2012/10/15

XMOS © 2012, All Rights Reserved

Document Number: X1087,

�XS1-G04B-FB144 Datasheet

1

Table of Contents

1

2

3

4

5

6

7

8

9

10

11

12

13

Features . . . . . . . . . . . . . . .

Pin Configuration . . . . . . . . . .

Signal Description . . . . . . . . . .

Block Diagram . . . . . . . . . . . .

Product Overview . . . . . . . . . .

DC and Switching Characteristics .

Package Information . . . . . . . .

Ordering Information . . . . . . . .

Development Tools . . . . . . . . .

Addendum: XMOS USB Interface . .

Associated Design Documentation

Related Documentation . . . . . . .

Revision History . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

2

3

4

7

8

15

18

19

19

19

20

21

22

TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and

software components used in this product. To subscribe to receive updates, visit http://www.xmos.com/.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you “AS IS” with

no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes

no representation that the information, or any particular implementation thereof, is or will be free from any

claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries,

and may not be used without written permission. Company and product names mentioned in this document

are the trademarks or registered trademarks of their respective owners.

X1087,

�XS1-G04B-FB144 Datasheet

1

2

Features

· Quad-Tile Multicore Microcontroller with Advanced Multi-Core RISC Architecture

• Up to 1600 MIPS shared between up to 32 real-time logical cores

• Each logical core has:

— Guaranteed throughput of between 1/4 and 1/8 of tile MIPS

— 16x32bit dedicated registers

• 159 high-density 16/32-bit instructions

— All have single clock-cycle execution (except for divide)

— 32x32→64-bit MAC instructions for DSP, arithmetic and user-definable cryptographic

functions

· Programmable I/O

• 88 general-purpose I/O pins, configurable as input or output

• Port sampling rates of up to 60 MHz with respect to an external clock

• 128 channel ends for communication with other cores, on or off-chip

· Memory

• 256KB internal single-cycle SRAM (max 64KB per tile) for code and data storage

• 32KB internal OTP (max 8KB per tile) for application boot code

· JTAG Module for On-Chip Debug

· Security Features

• Programming lock disables debug and prevents read-back of memory contents

• AES bootloader ensures secrecy of IP held on external flash memory

· Ambient Temperature Range

• Commercial qualification: 0 °C to 70 °C

• Industrial qualification: -40 °C to 85 °C

· Speed Grade

• 400 MHz part: 400 MIPS

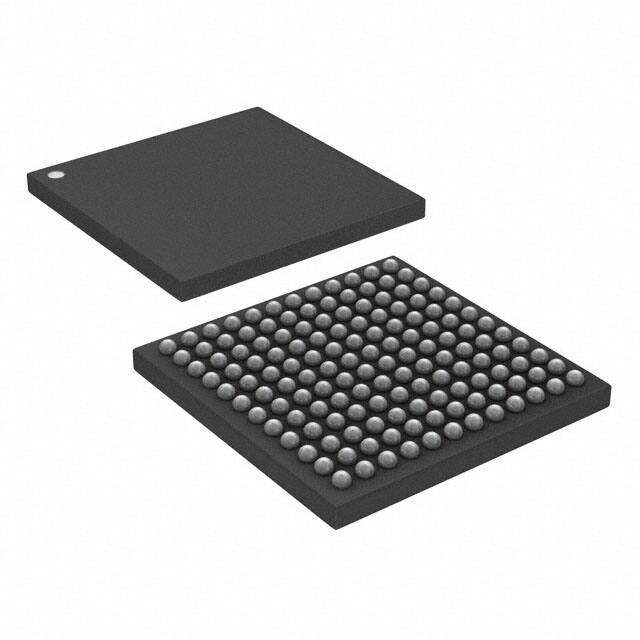

· 144-pin FBGA package 0.8 mm pitch

X1087,

�XS1-G04B-FB144 Datasheet

2

3

Pin Configuration

1

2

3

4

5

6

7

8

9

10

11

12

A

IO VDD

X0D34

X0D35

X0D36

X0D37

X0D38

X0D39

X0D40

X0D41

X0D42

X0D43

VSS

B

X0D33

VSS

X0D18

X0D19

X0D20

IO VDD

VSS

X0D21

X0D22

X0D23

IO VDD

X2D24

C

X0D32

X0D17

VDD

X0D06

X0D07

X0D08

X0D09

X0D10

X0D11

VDD

X2D12

X2D25

D

X0D31

X0D16

X0D05

SS_PLL_

BYPASS

SS_

RESET

VDD

OTP_

VPP

SS_XC0_

BS[0]

SS_XC_

CFG[0]

X2D00

X2D13

X2D26

E

X0D30

X0D15

X0D04

SS_CLK

VSS

VSS

VSS

VSS

SS_

DEBUG

X2D01

X2D14

X2D27

F

X0D29

IO VDD

X0D03

SS_PLL_

AGND

VSS

VSS

VSS

VSS

VDD

X2D02

VSS

X2D28

G

X0D28

VSS

X0D02

VDD

VSS

VSS

VSS

VSS

SS_

TEST_

ENA

X2D03

IO VDD

X2D29

H

X0D27

X0D14

X0D01

SS_PLL_

AVDD

VSS

VSS

VSS

VSS

SS_TCK

X2D04

X2D15

X2D30

J

X0D26

X0D13

X0D00

SS_PLL_

LOCK

SS_TMS

SS_TDO

VDD

SS_TDI

SS_TRST

X2D05

X2D16

X2D31

K

X0D25

X0D12

VDD

X2D11

X2D10

X2D09

X2D08

X2D07

X2D06

VDD

X2D17

X2D32

L

X0D24

IO VDD

X2D23

X2D22

X2D21

VSS

IO VDD

X2D20

X2D19

X2D18

VSS

X2D33

M

VSS

X2D43

X2D42

X2D41

X2D40

X2D39

X2D38

X2D37

X2D36

X2D35

X2D34

IO VDD

X1087,

�XS1-G04B-FB144 Datasheet

3

4

Signal Description

Module

Signal

Function

Type

Active

Properties

PU=Pull Up, PD=Pull Down, ST=Schmitt Trigger Input, OT=Output Tristate, S=Switchable

RS =Required for SPI boot (§5.6), RU =Required for USB-enabled devices (§10)

Power

PLL

JTAG

VDD

Digital tile power

PWR

—

VSS

Digital ground

GND

—

IO VDD

Digital I/O power

PWR

—

SS_PLL_AGND

Analog ground for PLL

GND

—

SS_PLL_AVDD

Analog PLL power

PWR

—

OTP_VPP

OTP programming voltage

PWR

—

SS_RESET

Global reset input

Input

—

PU, ST

SS_CLK

PLL reference clock

Input

—

PD, ST

SS_PLL_BYPASS

PLL bypass

Input

—

PD

SS_XC0_BS[0:0]

Boot status (tile 0)

I/O

—

PU

SS_TDI

Test data input

Input

—

PU, ST

SS_TDO

Test data output

Output

—

PD

SS_TMS

Test mode select

Input

—

PU, ST

SS_TRST

Test reset input

Input

—

PU, ST

SS_TCK

Test clock

Input

—

PU, ST

SS_DEBUG

Multi-chip debug

I/O

—

PU

P1A0

I/O

—

RS

P1B0

I/O

—

RS

X0D00

Tile 0 I/O

X0D01

X0LA4i

5b

X0D02

X0LA3i

5b

P4A0 P8A0 P16A0 P32A20

I/O

—

RU

X0D03

X0LA2i

5b

P4A1 P8A1 P16A1 P32A21

I/O

—

RU

X0D04

X0LA1i

2b/5b

P4B0 P8A2 P16A2 P32A22

I/O

—

RU

X0D05

X0LA0i

2b/5b

P4B1 P8A3 P16A3 P32A23

I/O

—

RU

X0D06

X0LA0o

2b/5b

P4B2 P8A4 P16A4 P32A24

I/O

—

RU

X0D07

X0LA1o

2b/5b

P4B3 P8A5 P16A5 P32A25

I/O

—

RU

X0D08

X0LA2o

5b

P4A2 P8A6 P16A6 P32A26

I/O

—

RU

X0D09

X0LA3o

5b

P4A3 P8A7 P16A7 P32A27

I/O

—

RU

X0D10

X0LA4o

5b

P1C0

I/O

—

RS

X0D11

P1D0

I/O

—

RS

X0D12

P1E0

I/O

—

RU

P1F0

I/O

—

RU

X0D13

X0LB4i

5b

X0D14

X0LB3i

5b

P4C0 P8B0 P16A8 P32A28

I/O

—

RU

X0D15

X0LB2i

5b

P4C1 P8B1 P16A9 P32A29

I/O

—

RU

X0D16

X0LB1i

2b/5b

P4D0 P8B2 P16A10

I/O

—

RU

X0D17

X0LB0i

2b/5b

P4D1 P8B3 P16A11

I/O

—

RU

X0D18

X0LB0o

2b/5b

P4D2 P8B4 P16A12

I/O

—

RU

X0D19

X0LB1o

2b/5b

P4D3 P8B5 P16A13

I/O

—

RU

X0D20

X0LB2o

5b

P4C2 P8B6 P16A14 P32A30

I/O

—

RU

X0D21

X0LB3o

5b

P4C3 P8B7 P16A15 P32A31

I/O

—

RU

(continued)

X1087,

�XS1-G04B-FB144 Datasheet

Module

Tile 0 I/O

5

Name

Function

X0D22

X0LB4o

5b

Type

Active

Properties

P1G0

I/O

—

RU

X0D23

P1H0

I/O

—

RU

X0D24

P1I0

I/O

—

X0D25

P1J0

I/O

—

X0D26

P4E0 P8C0 P16B0

I/O

—

RU

X0D27

P4E1 P8C1 P16B1

I/O

—

RU

X0D28

P4F0 P8C2 P16B2

I/O

—

RU

X0D29

P4F1 P8C3 P16B3

I/O

—

RU

X0D30

P4F2 P8C4 P16B4

I/O

—

RU

X0D31

P4F3 P8C5 P16B5

I/O

—

RU

X0D32

P4E2 P8C6 P16B6

I/O

—

RU

X0D33

P4E3 P8C7 P16B7

I/O

—

RU

I/O

—

X0D34

P1K0

X0D35

P1L0

I/O

—

X0D36

P1M0

P8D0 P16B8

I/O

—

X0D37

P1N0

P8D1 P16B9

I/O

—

RU

X0D38

P1O0

P8D2 P16B10

I/O

—

RU

X0D39

P1P0

P8D3 P16B11

I/O

—

RU

X0D40

P8D4 P16B12

I/O

—

RU

X0D41

P8D5 P16B13

I/O

—

RU

X0D42

P8D6 P16B14

I/O

—

RU

X0D43

P8D7 P16B15

I/O

—

RU

I/O

—

P1A0

X2D00

X2D01

X2LA4i

5b

X2D02

X2D11

X2LA3i

5b

X2LA2i

5b

X2LA1i

2b/5b

X2LA0i

2b/5b

X2LA0o

2b/5b

X2LA1o

2b/5b

X2LA2o

5b

X2LA3o

5b

X2LA4o

P1C0

5b

P1D0

X2D12

P1E0

P1F0

X2D03

X2D04

X2D05

X2D06

X2D07

X2D08

X2D09

Tile 2 I/O

X2D10

P1B0

I/O

—

P4A0 P8A0 P16A0 P32A20

I/O

—

RU

P4A1 P8A1 P16A1 P32A21

I/O

—

RU

P4B0 P8A2 P16A2 P32A22

I/O

—

RU

P4B1 P8A3 P16A3 P32A23

I/O

—

RU

P4B2 P8A4 P16A4 P32A24

I/O

—

RU

P4B3 P8A5 P16A5 P32A25

I/O

—

RU

P4A2 P8A6 P16A6 P32A26

I/O

—

RU

P4A3 P8A7 P16A7 P32A27

I/O

—

RU

I/O

—

I/O

—

I/O

—

RU

I/O

—

RU

X2D13

X2LB4i

5b

X2D14

X2LB3i

5b

P4C0 P8B0 P16A8 P32A28

I/O

—

RU

X2D15

X2LB2i

5b

P4C1 P8B1 P16A9 P32A29

I/O

—

RU

X2D16

X2LB1i

2b/5b

P4D0 P8B2 P16A10

I/O

—

RU

X2D17

X2LB0i

2b/5b

P4D1 P8B3 P16A11

I/O

—

RU

X2D18

X2LB0o

2b/5b

P4D2 P8B4 P16A12

I/O

—

RU

X2D19

X2LB1o

2b/5b

P4D3 P8B5 P16A13

I/O

—

RU

X2D20

X2LB2o

5b

P4C2 P8B6 P16A14 P32A30

I/O

—

RU

(continued)

X1087,

�XS1-G04B-FB144 Datasheet

Module

Tile 2 I/O

Reserved

X1087,

6

Name

Function

X2D21

X2LB3o

5b

Type

Active

Properties

I/O

—

X2D22

X2LB4o

5b

RU

P1G0

I/O

—

RU

X2D23

P1H0

I/O

—

RU

X2D24

P1I0

I/O

—

X2D25

P1J0

P4C3 P8B7 P16A15 P32A31

I/O

—

X2D26

P4E0 P8C0 P16B0

I/O

—

RU

X2D27

P4E1 P8C1 P16B1

I/O

—

RU

X2D28

P4F0 P8C2 P16B2

I/O

—

RU

X2D29

P4F1 P8C3 P16B3

I/O

—

RU

X2D30

P4F2 P8C4 P16B4

I/O

—

RU

X2D31

P4F3 P8C5 P16B5

I/O

—

RU

X2D32

P4E2 P8C6 P16B6

I/O

—

RU

X2D33

P4E3 P8C7 P16B7

I/O

—

RU

I/O

—

X2D34

P1K0

X2D35

P1L0

I/O

—

X2D36

P1M0

P8D0 P16B8

I/O

—

X2D37

P1N0

P8D1 P16B9

I/O

—

RU

X2D38

P1O0

P8D2 P16B10

I/O

—

RU

X2D39

P1P0

P8D3 P16B11

I/O

—

RU

X2D40

P8D4 P16B12

I/O

—

RU

X2D41

P8D5 P16B13

I/O

—

RU

X2D42

P8D6 P16B14

I/O

—

RU

X2D43

P8D7 P16B15

I/O

—

RU

SS_PLL_LOCK

Reserved (do not connect)

Output

—

PD

SS_TEST_ENA

Reserved (tie to VSS)

Input

—

PD

SS_XC_CFG[0:0]

Reserved (tie to VSS)

Input

—

PD

�XS1-G04B-FB144 Datasheet

Block Diagram

Port 8A

Port 4B

4A

64KB SRAM

Core 0

Boot ROM

Port 16A

1C

· 1D

· 1E

Core 2

8KB OTP

4C

Core 3

1G

6 Clock

Blocks

Core 4

10 Timers

Core 5

4 Locks

Core 6

Core 0

64KB SRAM

Core 1

Boot ROM

Core 2

8KB OTP

Core 3

Security Register

Core 4

6 Clock Blocks

Core 5

10 Timers

Core 6

4 Locks

Core 7

7 Synchronizers

X3

4E

1A ¶

1B

64KB SRAM

Core 1

Boot ROM

4 Locks

Core 6

7 Synchronizers

Core 7

Core 5

10 Timers

Core 6

4 Locks

Core 7

7

Synchronizers

X0LB

Port 4D

4C

Core 5

6 Clock

Blocks

4E

Core 4

10 Timers

Core 4

Port 4F

Core 3

6 Clock Blocks

Security

Register

4E

Security Register

Core 3

Port 8C

Core 2

8KB OTP

Port 16B

8KB OTP

32 Channel Ends

Core 1

Switch

Boot ROM

32 Channel Ends

Core 0

Switch

X1

64KB SRAM

Core 2

4C

Port 16A

1C

1D¶

1E ¶

1F

Port 8B

PLL

OTP_VPP

VDD

VDDIO

GND

X1087,

4A

X0

PLL_BYPASS

PLL_LOCK

PLL_AVDD

PLL_AGND

CLK

XC0_BS0

RST_N

X0LA

Core 0

Port 8A

Core 7

Port 4B

4A

X2

7

Synchronizers

Port 8D

·

·

·

·

TDI

TDO

TCK

TMS

TRST_N

DEBUG_N

JTAG

Switch

Port 4F

Port 16B

· 1K

· 1L

· 1M

· 1N

· 1O

· 1P

·

·

·

·

·

·

·

·

Port 8C

· 1H

· 1I

· 1J

Switch

Security

Register

32 Channel Ends

Port 8B

Port 4D

4C

1F

Switch

4A

Core 1

32 Channel Ends

1B

4E

·

·

·

·

·

·

·

·

·

·

· 1A

Port 8D

·

·

·

·

·

·

·

·

·

·

X0LA

X0D00 ¶

X0D01 ¶

X0D02 ¶

X0D03 ¶

X0D04 ¶

X0D05 ¶

X0D06 ¶

X0D07 ¶

X0D08 ¶

X0D09 ¶

X0D10 ¶

X0D11 ¶

X0D12 ¶

X0D13 ¶

X0D14 ¶

X0D15 ¶

X0D16 ¶

X0D17 ¶

X0D18 ¶

X0D19 ¶

X0D20 ¶

X0D21 ¶

X0D22 ¶

X0D23 ¶

X0D24 ¶

X0D25 ¶

X0D26 ¶

X0D27 ¶

X0D28 ¶

X0D29 ¶

X0D30 ¶

X0D31 ¶

X0D32 ¶

X0D33 ¶

X0D34 ¶

X0D35 ¶

X0D36 ¶

X0D37 ¶

X0D38 ¶

X0D39 ¶

X0D40 ¶

X0D41 ¶

X0D42 ¶

X0D43 ¶

X0LB

4

7

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

1G

1H¶

1I ¶

1J ¶

1K ¶

1L ¶

1M¶

1N ¶

1O¶

1P ¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

¶

· X2D00

· X2D01

· X2D02

· X2D03

· X2D04

· X2D05

· X2D06

· X2D07

· X2D08

· X2D09

· X2D10

· X2D11

· X2D12

· X2D13

· X2D14

· X2D15

· X2D16

· X2D17

· X2D18

· X2D19

· X2D20

· X2D21

· X2D22

· X2D23

· X2D24

· X2D25

· X2D26

· X2D27

· X2D28

· X2D29

· X2D30

· X2D31

· X2D32

· X2D33

· X2D34

· X2D35

· X2D36

· X2D37

· X2D38

· X2D39

·X2D40

·X2D41

·X2D42

·X2D43

�XS1-G04B-FB144 Datasheet

5

8

Product Overview

The XMOS XS1-G04B-FB144 is a powerful device that provides a simple design

process and highly-flexible solution to many applications. The device consists of

four xCORE Tiles, each comprising a flexible multicore microcontroller with tightly

integrated I/O and on-chip memory. The processors run mutiple tasks simultaneously using logical cores, each of which is guaranteed a slice of processing power

and can execute computational code, control software and I/O interfaces. Logical

cores use channels to exchange data within a tile or across tiles. The tiles are

connected via an integrated switch network, which uses a proprietary physical

layer protocol, and which can also be used to add additional resources to a design.

The I/O pins are driven using intelligent ports that can serialize data, interpret

strobe signals and wait for scheduled times or events, making the device ideal for

real-time control applications.

The device can be configured using a set of software components that are rapidly

customized and composed. XMOS provides source code libraries for many standard

components. The device can be programmed using high-level languages such as

C/C++ and XMOS-originated extensions to C, called XC, that simplify the control

over concurrency, I/O and time.

The XMOS toolchain includes compilers, a simulator, debugger and static timing

analyzer. The combination of real-time software, a compiler and timing analyzer

enables the programmer to close timings on components of the design without a

detailed understanding of the hardware characteristics.

5.1

Logical cores, Synchronizers and Locks

Each xCORE Tile has up to eight active logical cores, which issue instructions

down a shared four-stage pipeline. Instructions from the active cores are issued

round-robin. If up to four logical cores are active, each core is allocated a quarter

of the processing cycles. If more than four logical cores are active, each core

is allocated at least 1/n cycles (for n cores). Figure 1 shows the guaranteed core

performance depending on the number of cores used.

Figure 1:

Core

performance

Speed Grade

400 MHz

Minimum MIPS per core (for n cores)

1

2

3

4

5

6

7

8

100

100

100

100

80

67

57

50

There is no way that the performance of a logical core can be reduced below these

predicted levels. Because cores may be delayed on I/O, however, their unused

processing cycles can be taken by other cores. This means that for more than

four logical cores, the performance of each core is often higher than the predicted

minimum.

5.2

Channel Ends, Links and Switch

Logical cores communicate using point-to-point connections formed between two

channel ends. Between tiles, channel communications are implemented over

X1087,

�XS1-G04B-FB144 Datasheet

9

xConnect Links and routed through switches. The links operate in either 2bit/direction or 5bit/direction mode, depending on the amount of bandwidth required.

Circuit switched, streaming and packet switched data can both be supported efficiently. Streams provide the fastest possible data rates between xCORE Tiles (up to

250 MBit/s), but each stream requires a single link to be reserved between switches

on two tiles. All packet communications can be multiplexed onto a single link. A

total of eight 5bit links are available between every pair of cores.

Information on the supported routing topologies that can be used to connect

multiple devices together can be found in the XS1-G Link Performance and Design

Guide, X7561.

5.3

Ports and Clock Blocks

Ports provide an interface between the logical cores and I/O pins. All pins of a port

provide either output or input. Signals in different directions cannot be mapped

onto the same port.

The operation of each port is synchronized to a clock block. A clock block can be

connected to an external clock input, or it can be run from the divided reference

clock. A clock block can also output its signal to a pin. On reset, each port is

connected to clock block 0, which runs from the xCORE Tile reference clock.

The ports and links are multiplexed, allowing the pins to be configured for use by

ports of different widths or links. If an xConnect Link is enabled, the pins of the

underlying ports are disabled. If a port is enabled, it overrules ports with higher

widths that share the same pins. The pins on the wider port that are not shared

remain available for use when the narrower port is enabled. Ports always operate

at their specified width, even if they share pins with another port.

5.4

Timers

Timers are 32-bit counters that are relative to the xCORE Tile reference clock. A

timer is defined to tick every 10 ns. This value is derived from the reference clock,

which is configured to tick at 100 MHz by default.

5.5

PLL

The PLL is used to generate all on-chip clocks. SS_CLK is the reference clock input.

It should be supplied with a clock with monotonic rising edges and should be

stable before SS_RESET is taken high.

Many standard clock frequencies can be used with appropriate settings configured

into the PLL. At boot time, before the PLL can be reconfigured, the PLL multiplier is

set using the pins specified in the table in Figure 2. The PLL increases the clock

frequency to the tile frequency used to run the processor data path and the switch.

Further details on configuring the clock can be found in the XS1-G Clock Frequency

Control document, X3221.

X1087,

�XS1-G04B-FB144 Datasheet

Figure 2:

PLL boot

modes

10

SS_PLL_BYPASS

PLL Multiplier

SS_CLK Input (MHz)

Boot Frequency (MHz)

0

20

12.5–20

250–400

1

0.5