SQ29020

High Efficiency, 16V/20A Synchronous Step-down Regulator

Advanced Design Specification

General Description

Features

Wide Input Voltage Range: 2.9V/3.6V to 16V

Internal 7.5mΩ Power Switch and 2.4mΩ Synchronous

Rectifier

Accurate Feedback Set Point: 0.6V ±1%

Differential Remote Sense

Fast Transient Response

600kHz, 800kHz and 1000kHz Operating Frequency

Selectable Automatic High-efficiency Discontinuous

Operating Mode at Light Loads

Programmable Valley Current Limit

Reliable Built-in Protections:

Automatic Recovery for Input Under-voltage

(UVLO), Output Under-voltage (UVP) and Overtemperature (OTP) Conditions

Cycle-by-cycle Valley and Peak Current Limit (OCP)

Cycle-by-cycle Reverse Current Limit

Internal and Adjustable Soft-start to Limits Inrush Current

Smooth Pre-biased Startup

Power Good Output Monitor for Under-voltage and Overvoltage

导

小

芯

The SQ29020 is a high-efficiency synchronous step-down

DC-DC regulator featuring internal power and synchronous

rectifier switches capable of delivering 20A of continuous

output current over a wide input voltage range, from as low as

2.9V up to 16V. The output voltage is adjustable from 0.6V to

5.5V.

dF

or

半

Silergy’s proprietary Instant-PWM™ fast-response, constanton-time (COT) PWM control method supports high

input/output voltage ratios (low duty cycles) and responds to

load transients within ~100ns while maintaining a near

constant operating frequency over line, load and output

voltage ranges. This control method provides stable operation

without complex compensation, even with low ESR ceramic

output capacitors.

lP

Applications

de

nti

a

Internal 7.5mΩ power and 2.4mΩ synchronous rectifier

switches provide excellent efficiency for a wide range of

applications, especially for low output voltages and low duty

cycles. Cycle-by-cycle current limit, input under-voltage lockout, internal soft-start, output under- and over-voltage

protection, and thermal shutdown provide safe operation in all

operating conditions.

rep

are

The stable internal reference (VREF) provides ±1% accuracy

over TJ= -40°C to 125°C, and the differential input sense

configuration allows the feedback sensing at the most relevant

load point.

VIN=2.9V~16V

erg

+

90

L=0.22μH

BS

IN

CIN=100μF

Efficiency vs. Load Current

(fSW=600kHz, FCCM, L=0.22μH/VLBU1007090T-R22L)

100

CBS=0.1μF

LX

CIN=22μF×2 CIN=0.1μF×2

RPG=10kΩ

External VCC

Supply(opt.)

Sil

PG

CVCC=1μF

ON/

OFF

RILMT=5.6kΩ

GNDS

EN

MODE

SS

AGND

VSENSE+

COUT=47μF×5

R1=100kΩ

R2=100kΩ

VCC

ILMT

GND

VOUT=1.2V

RFF=1kΩ CFF=220pF

FBS

80

VSENSE-

Load

Efficiency (%)

yC

orp

.C

on

fi

The SQ29020 is available in a compact QFN3x4 package.

Telecom and Networking Systems

Servers

High Power Access Points

Storage Systems

Cellular Base Stations

70

VIN=3.6V, VOUT=1.2V

VIN=7.4V, VOUT=1.2V

VIN=12V, VOUT=1.2V

VIN=16V, VOUT=1.2V

60

50

40

30

20

10

RMODE=0Ω

0

0.001

CSS=0.22µF

Figure 1. Typical Application Circuit

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

0.01

0.1

1

10 20

Load Current (A)

Figure 2. Efficiency vs. Load Current

Silergy Corp. Confidential- Prepared for Customer Use Only

1

All Rights Reserved.

�SQ29020

Ordering Information

Ordering

Part Number

SQ29020VDC

Pinout (top view)

Package type

Top mark

QFN3×4-19

DDExyz

RoHS Compliant and Halogen Free

3

MODE

4

SS

5

GNDS

6

FBS

7

EN

8

PG

9, 18

10, 11, 12, 13, 14, 15

IN

GND

16

VCC

17

LX

19

BS

or

半

ILMT

dF

2

Pin Description

Analog ground

Synchronous rectifier current limit setting. Connect a resistor to AGND to set the inductor valley current

limit

Operation mode selection. Program MODE to select FCCM/PFM, and the operating switching frequency.

See table 1

External soft-start setting. Optionally adjust the soft-start time by adding an appropriate external capacitor

between this pin and AGND pin. See Detailed Description

Remote ground sense. Connect this pin directly to the negative side of the preferred voltage sense point.

Short to GND if remote sense is not used

Remote feedback sense. Connect this pin to the center point of the output resistor divider to program the

output voltage. See Design Procedure

Enable input. Pull low to disable the device, high to enable. Do not leave this pin floating. May be used

for increasing startup voltage or sequencing. See Detailed Description

Power good indicator. Open drain output when the output voltage is within 92.5% to 120% of the

regulation set point

Power input. Decouple this pin to GND pin with at least a 30μF ceramic capacitor

Power ground

Internal 3.3V LDO output. Power supply for internal analog circuits and driving circuits. Decouple this

pin to GND with at least a 1μF ceramic capacitor. Make one good Kelvin connection from AGND to VCC

capacitor GND connection. Use short, direct connections and avoid the use of vias. May be driven by an

external bias supply. See Detailed Description.

Inductor pin. Connect this pin to the switching node of the inductor

Boot-strap supply for the high side gate driver. Connect a 0.1µF ceramic capacitor between the BS and the

LX pin

rep

are

Pin Name

AGND

Sil

erg

yC

orp

.C

on

fi

de

nti

a

lP

Pin No

1

导

小

芯

x=year code, y=week code, z= lot number code

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

2

All Rights Reserved.

�lP

rep

are

dF

or

半

导

小

芯

SQ29020

de

nti

a

Figure 3. Block Diagram

Absolute Maximum Ratings (1)

IN

.C

orp

LX, 10ns duration

BS

FBS, GNDS, AGND, VCC, PG

Junction Temperature, Operating

Lead Temperature (Soldering, 10 sec.)

Storage Temperature

on

fi

ILMT, SS

EN, MODE, LX

Min

Max

-0.3

18

-0.3

4

-0.3

IN + 0.3

-5

IN + 5

LX - 0.3 LX + 4

-0.3

4

-40

150

260

-65

150

Min

Recommended Operating Conditions (3)

IN

Output Voltage

GNDS

VCC external bias

Output current

Output current limit setting

Peak inductor current

Junction Temperature

Min

2.9

0.6

-0.2

3.12

Sil

erg

yC

Thermal Information (2)

θ JA Junction-to-ambient thermal resistance

θ JC Junction-to-case (bottom) thermal resistance

PD Power dissipation TA = 25°C

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

-40

Max

24

4.5

4.2

Max

16

5.5

0.2

3.6

20

24

28

125

Unit

V

°C

Unit

°C/W

W

Unit

V

A

°C

3

All Rights Reserved.

�SQ29020

Electrical Characteristics VIN = 12V, TJ = -40°C to +125°C, typical values are at TJ = 25°C, unless otherwise specified (4)

Power Switch

Synchronous Rectifier

Quiescent Current

IQ

UVLO, Rising

UVLO, Hysteresis

Output

Load regulation

External Bias input

Reference Voltage

Error Amp Offset

Input Current

On resistance

Leakage

Current Limit

On resistance

Leakage

VVCC,UVLO

VVCC,HYS

VCC

VCC,REG

VCC,EXT

VREF

VOS

IFBS

RDS(ON)HS

IHS, LKG

ILMT,HS

RDS(ON)LS

ILS, LKG

ILMT,RVS

tRCL,BLK

ILMT,BOT

VILMT

IILMT/ILMT,BOT

RDIS

VEN,R

VEN,HYS

IEN

ISS1

ISS2

tSS,MIN

VOVP

VUVP

tUVP,DLY

tHICCUP,ON

tHICCUP,OFF

Reverse current

Forward current

ILMT Pin Output Voltage

ILMT Ratio

Discharge FET Resistance

erg

yC

orp

.C

on

fi

Rising Threshold

Enable (EN)

Threshold Hysteresis

Input Current

Charging current

Soft Start (SS)

Discharge current

Min soft-start time

Overvoltage protection threshold

threshold

Undervoltage protection

Delay

UVP/OCP Hiccup ON Time

UVP/OCP Hiccup OFF Time

Sil

Thresholds

Power Good

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Delay

VPG

tPG,R

tPG,F

Output low

voltage

VPG,LOW

Output low leakage

IPG,LKG

Min

2.9

2.6

VEN=0V, TJ=25°C

VEN=2V, VFBS = 0.65V, PFM mode,

No Switching

导

小

芯

VEN=2V, VFBS = 1V

VBS-LX = 3.3V, TJ=25°C

VEN=0V, VLX=0V

3.15

0.594

-3

-50

25.5

VCC = 3.3V, TJ=25°C

VEN=0V, VLX=12V

9

40

RILMT = 5.6kΩ

ILMT,BOT >5A

1.15

9

1.18

VEN=2V

VSS=0V

VSS=1V

110

45

CSS open

VFBS falling, fault

VFBS rising, good

VFBS rising, fault

VFBS falling, good

VFBS falling, good

VFBS rising, fault

VIN=0V, 100kΩ from PG to 3.3V

VIN=0V, 10kΩ from PG to 3.3V

VEN = 2V, VFBS = 0V, IPG=10mA

VPG = 3.3V

Silergy Corp. Confidential- Prepared for Customer Use Only

Typ

2.75

200

2

550

3.15

or

半

IVCC=0mA

IVCC=25mA

optional

GNDS = 0V

dF

FBS

Test Conditions

lP

VCC

Symbol

VIN

VIN,UVLO

VIN,HYS

ISHDN

de

nti

a

Input

Voltage

UVLO, rising

UVLO, Hysteresis

Shutdown Current

rep

are

Parameter

77

89.5

110

102

100

3.3

1.4

0.600

0

7.5

0.01

28

2.4

0.04

13

60

21.4

1.2

10

120

1.23

0.2

0

46

38

1

120

50

20

3

12

80

92.5

120

105

0.8

20

550

660

3

Max

16

2.9

5

Unit

V

V

mV

µA

850

µA

2.5

V

mV

V

%

V

V

mV

nA

mΩ

µA

A

mΩ

µA

A

ns

A

V

µA/A

Ω

V

V

µA

µA

mA

ms

3.45

3.6

0.606

3

50

11.3

8

33

3.6

32

16

1.25

11

1.28

130

55

%VFBS

µs

ms

84

96.5

130

108

%VFBS

ms

750

850

0.4

5

V

µA

4

All Rights Reserved.

�SQ29020

Electrical Characteristics (cont.) VIN = 12V, TJ = -40°C to +125°C, typical values are at TJ = 25°C, unless otherwise specified (4)

Parameter

Symbol

Switching Frequency

fSW

Test Conditions

RMODE=0Ω, IOUT=0A, FCCM,

VOUT=1V, TJ=25°C

RMODE=30.1kΩ, IOUT=0A, FCCM,

VOUT=1V, TJ=25°C

RMODE=60.4kΩ, IOUT=0A, FCCM,

VOUT=1V, TJ=25°C

IOUT=3A (Note 4)

IOUT=3A (Note 4)

Min

Typ

Max

510

600

690

690

800

910

900

1000

1100

Unit

kHz

dF

or

半

导

小

芯

Min ON Time

tON,MIN

60

ns

Min OFF Time

tOFF,MIN

180

Thermal Shutdown Temperature

TSD

160

˚C

Thermal Shutdown Hysteresis

THYS

(Note 4)

30

Note 1: Stresses beyond the “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only. Functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note2: Package thermal resistance is measured in the natural convection at TA=25˚C on a 8.5cm×8.5cm size four-layer Silergy Evaluation Board.

Note 3: The device is not guaranteed to function outside its operating conditions.

Note 4: Production testing is performed at 25˚C; limits at -40°C to +125°C are guaranteed by design, test or statistical correlation.

Typical Performance Characteristics

rep

are

(TA=25℃, VIN=12V, VOUT=1.2V, L=0.22μH, COUT=235μF, fSW=600kHz, RILMT=5.6kΩ, CSS=0.22μF, unless otherwise noted)

Efficiency vs. Load Current

(fSW=600kHz, PFM, L=0.22μH/VLBU1007090T-R22L)

100

100

60

50

40

VIN=3.6V, VOUT=1.2V

VIN=7.4V, VOUT=1.2V

VIN=12V, VOUT=1.2V

VIN=16V, VOUT=1.2V

20

0

0.001

0.01

0.1

1

50

40

10

0

0.001

10 20

0.01

0.1

1

10 20

Load Current (A)

orp

Load Current (A)

60

20

.C

10

70

30

on

fi

30

de

nti

a

70

80

Efficiency (%)

80

Efficiency vs. Load Current

Efficiency vs. Load Current

(fSW=600kHz, PFM, L=0.22μH/VLBU1007090T-R22L)

(fSW=600kHz, FCCM, L=0.22μH/VLBU1007090T-R22L)

100

yC

100

90

90

80

erg

80

70

Sil

60

50

40

VIN=5V, VOUT=1.8V

VIN=12V, VOUT=1.8V

VIN=16V, VOUT=1.8V

30

20

10

0

0.001

Efficiency (%)

Efficiency (%)

VIN=3.6V, VOUT=1.2V

VIN=7.4V, VOUT=1.2V

VIN=12V, VOUT=1.2V

VIN=16V, VOUT=1.2V

90

lP

90

Efficiency (%)

Efficiency vs. Load Current

(fSW=600kHz, FCCM, L=0.22μH/VLBU1007090T-R22L)

VIN=5V, VOUT=1.8V

VIN=12V, VOUT=1.8V

VIN=16V, VOUT=1.8V

70

60

50

40

30

20

10

0.01

0.1

1

10 20

0

0.001

0.01

Load Current (A)

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

0.1

1

10 20

Load Current (A)

5

All Rights Reserved.

�SQ29020

Typical Performance Characteristics (cont.)

Efficiency vs. Load Current

Efficiency vs. Load Current

(fSW=600kHz, PFM, L=0.56μH/FCUL1060-H-R56M=P3)

(fSW=600kHz, FCCM, L=0.56μH/FCUL1060-H-R56M=P3)

100

100

90

90

80

80

70

70

60

50

40

30

0

0.001

0.01

0.1

20

10

0

0.001

10 20

1

40

or

半

10

50

30

VIN=6V, VOUT=3.3V

VIN=12V, VOUT=3.3V

VIN=16V, VOUT=3.3V

20

60

dF

Load Current (A)

Efficiency vs. Load Current

0.1

10 20

1

Load Current (A)

Efficiency vs. Load Current

(fSW=600kHz, FCCM, L=0.56μH/FCUL1060-H-R56M=P3)

100

100

90

90

80

70

lP

60

40

30

0.01

0.1

1

Load Current (A)

orp

Load Transient

10 20

70

60

50

40

30

VIN=7.4V, VOUT=5V

VIN=12V, VOUT=5V

VIN=16V, VOUT=5V

20

10

0

0.001

Sil

erg

yC

100mV/div

IL

20A/div

10 20

1

Output Ripple

(VIN=12V, VOUT=1.2V, IOUT=20A)

∆VOUT

50mV/div

VLX

10V/div

IL

20A/div

Time (200µs/div)

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

0.1

Load Current (A)

(VIN=12V, VOUT=1.2V, IOUT=2~20A, FCCM)

∆VOUT

0.01

.C

10

on

fi

VIN=7.4V, VOUT=5V

VIN=12V, VOUT=5V

VIN=16V, VOUT=5V

20

de

nti

a

50

Efficiency (%)

80

Efficiency (%)

0.01

VIN=6V, VOUT=3.3V

VIN=12V, VOUT=3.3V

VIN=16V, VOUT=3.3V

rep

are

(fSW=600kHz, PFM, L=0.56μH/FCUL1060-H-R56M=P3)

0

0.001

导

小

芯

Efficiency (%)

Efficiency (%)

(TA=25℃, VIN=12V, VOUT=1.2V, L=0.22μH, COUT=235μF, fSW=600kHz, RILMT=5.6kΩ, CSS=0.22μF, unless otherwise noted)

Silergy Corp. Confidential- Prepared for Customer Use Only

Time (2μs/div)

6

All Rights Reserved.

�SQ29020

Typical Performance Characteristics (cont.)

(TA=25℃, VIN=12V, VOUT=1.2V, L=0.22μH, COUT=235μF, fSW=600kHz, RILMT=5.6kΩ, CSS=0.22μF, unless otherwise noted)

Shutdown from VIN

(VIN=12V, VOUT=1.2V, IOUT=20A)

VIN

VOUT

1V/div

VLX

10V/div

IL

20A/div

dF

Time (4ms/div)

Startup from EN

1V/div

VLX

10V/div

IL

20A/div

10V/div

IL

20A/div

Shutdown from EN

lP

VOUT

VLX

Time (4ms/div)

de

nti

a

5V/div

1V/div

(VIN=12V, VOUT=1.2V, IOUT=20A)

EN

5V/div

VOUT

1V/div

VLX

10V/div

IL

20A/div

Time (4ms/div)

orp

.C

Time (4ms/div)

on

fi

EN

rep

are

(VIN=12V, VOUT=1.2V, IOUT=20A)

10V/div

VOUT

导

小

芯

10V/div

or

半

VIN

Startup from VIN

(VIN=12V, VOUT=1.2V, IOUT=20A)

Short Circuit Protection

(VIN=12V, VOUT=1.2V, IOUT=20A~short, RILMT=5.6kΩ)

1V/div

VOUT

1V/div

IL

20A/div

Sil

erg

VOUT

yC

Short Circuit Protection

(VIN=12V, VOUT=1.2V, IOUT=0A~short, RILMT=5.6kΩ, FCCM)

IL

20A/div

Time (20ms/div)

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

Time (20ms/div)

7

All Rights Reserved.

�SQ29020

Typical Performance Characteristics (cont.)

(TA=25℃, VIN=12V, VOUT=1.2V, L=0.22μH, COUT=235μF, fSW=600kHz, RILMT=5.6kΩ, CSS=0.22μF, unless otherwise noted)

Short Circuit Protection

Short Circuit Protection

(VIN=12V, VOUT=1.2V, IOUT=0A~short, RILMT=10kΩ, FCCM)

(VIN=12V, VOUT=1.2V, IOUT=10A~short, RILMT=10kΩ)

IL

20A/div

VOUT

IL

dF

Time (20ms/div)

Output Ripple

rep

are

(VIN=12V, VOUT=1.2V, IOUT=0A, PFM)

10V/div

IL

10A/div

de

nti

a

VLX

lP

50mV/div

Time (20ms/div)

Output Ripple

∆VOUT

50mV/div

VLX

10V/div

IL

10A/div

Time (2μs/div)

Sil

erg

yC

orp

.C

Time (2μs/div)

20A/div

(VIN=12V, VOUT=1.2V, IOUT=0A, FCCM)

on

fi

∆VOUT

1V/div

导

小

芯

1V/div

or

半

VOUT

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

8

All Rights Reserved.

�SQ29020

Detailed Description

be reduced as needed to always ensure a proper operation.

Constant-on-time Architecture

Under TJ=-40℃ ~125℃ condition, the device can support up

to 5.5V output even the input voltage is as low as 8V.

L1

VOUT

R1

Power switch

COUT

R2

Synchronous

rectifier

Ramp

Generator

DIFF

VRAMP

S

R

VREF

orp

On-time

Generator

.C

VFB

Q

on

fi

CIN

PWM

signal

Sil

erg

yC

Silergy’s Instant-PWM control method adds several

proprietary improvements to traditional COT architecture.

Whereas most legacy COT implementations require a

dedicated connection to the output voltage terminal to

calculate the tON duration, Instant-PWM derives this signal

internally. Another improvement optimizes operation when

used with low ESR ceramic output capacitors. In many

applications it is desirable to utilize very low ESR ceramic

output capacitors, but legacy COT regulators may become

unstable when used with these output capacitors.

Minimum Duty Cycle and Maximum Duty Cycle

In the COT architecture, there is no limitation for small duty

cycle, since at very low duty cycle operation, once the on-time

is close to the minimum on time, the switching frequency can

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

or

半

导

小

芯

When operating conditions include changes in input voltage

and/or output loads, the COT operating frequency will

naturally vary from the ideal. Silergy’s FLL technology

minimizes this variation by comparing the actual operating

frequency with the desired frequency. The FLL block adjusts

the calculated tON period to lock the operating frequency to the

onboard reference oscillator. The FLL function is disabled

during soft-start and discontinuous current mode (DCM)

operating condition. Note that FLL does not impede the high

frequency retriggering of the power switch during load

transients.

dF

Operating Frequency/Light Load Settings

rep

are

The MODE pin sets both the operating frequency and the light

load behavior of the device. This pin is sampled when the

device is enabled and the operating modes are set when the

internal regulator (Vcc) rises above VVCC,UVLO. The mode is

locked until the device is restarted.

de

nti

a

Instant-PWM Operation

VIN

Frequency Locked Loop (FLL)

lP

Fundamental to any constant-on-time (COT) architecture is

the one-shot circuit or on-time generator, which determines

how long to turn on the high-side power switch. Each on-time

(tON) is a “fixed” period internally calculated to operate the

regulator at the desired switching frequency over the input and

output voltage range, where tON=(VOUT/VIN)×(1/fSW). For

example, consider a hypothetical converter configured for

1.2V output from a 12V input operating at 600kHz. The target

on-time is (1.2V/12V)×(1/600kHz)=167ns. Each tON pulse is

triggered by the feedback comparator when the output voltage

as measured at FB drops below the target value. As the input

or output voltages change, an appropriate tON pulse is

calculated, maintaining a fairly constant operating frequency

while regulating the output voltage. In a COT architecture,

there is no fixed clock, so the power switch can turn on almost

immediately after a load transient and subsequent switching

pulses can be quickly initiated, ramping the inductor current

up to meet load requirements with minimal delays. COT has

significant benefits over traditional current mode or voltage

mode control methods that must simultaneously monitor the

feedback voltage, inductor current and compensation signals

to determine when to turn off the power switch and turn on the

synchronous rectifier.

MODE

Pin connection

VCC

240kΩ* to GND

120kΩ* to GND

GND

30kΩ* to GND

60kΩ* to GND *±20%

LightLoad

operation

PFM

PFM

PFM

FCCM

FCCM

FCCM

Operating

Frequency

600kHz

800kHz

1000kHz

600kHz

800kHz

1000kHz

Table 1

Under medium to heavy loads, the inductor current, even at

the lowest point just before each tON pulse, is always positive.

This is known as continuous conduction mode (CCM). At

lower load currents, when IOUT ~ < 1/2×ΔIL, the current

through the inductor will ramp to near zero before the next tON

pulse. The behavior of the device in this condition may be set

to pulse frequency modulation (PFM) to optimize efficiency,

or to forced continuous conduction mode (FCCM) which

maintains a fixed operating frequency.

When operating in PFM under light load conditions, the

synchronous rectifier will turn off, preventing recirculation

current that can seriously reduce efficiency under these light

load conditions. As load current is further reduced, and while

the feedback is greater than the reference voltage, the control

loop will not trigger another tON until needed, lowering the

operating frequency, further enhancing efficiency. Fixed

frequency CCM resumes smoothly as soon as the load current

increases sufficiently for the inductor current to remain

positive throughout the cycle. PFM operation should not be

Silergy Corp. Confidential- Prepared for Customer Use Only

9

All Rights Reserved.

�SQ29020

selected if the application is sensitive to frequencies lower

than the selected operating frequency, including audible

frequencies.

controlled starts. The accurate threshold is useful to inhibit

operation until a specific IN voltage is reached.

When EN is < 0.4V the internal linear regulator that drives

VCC and most internal circuitry is turned off, disabling the

device. Driving EN above VEN,R initiates a startup sequence as

the device is enabled.

In FCCM operation under light loads, the synchronous

rectifier remains on even when the inductor current crosses

zero. Current flow will continue until the next tON cycle. In

this way, the device always operates in CCM and keeps a

relatively constant switching frequency over the entire output

current range.

VIN

IN

导

小

芯

RH

EN

RL

AGND GND

Linear Regulator (VCC)

An internal linear regulator produces a 3.3V supply at VCC

from IN. VCC powers the internal gate drivers, PWM logic,

analog circuitry, and other blocks. Connect a 1µF (minimum)

low ESR ceramic capacitor from VCC to GND. Note that an

external bias supply may be used to drive VCC in the range

specified by VCC,EXT. Care should be taken to ensure that the

bias supply draws no current from the VCC linear regulator.

dF

or

半

For automatic start-up, connect EN to IN through resistor RH.

If power supply sequencing is required, similarly connect EN

to the output of the power rail that should start first. RH should

be 1kΩ to 1MΩ.

Note that when enabling the device via EN, two thresholds

will be observed. First, at ~0.8V, the internal linear regulator

that drives VCC will be enabled and, assuming sufficient

voltage at IN, VCC will rise. Second, as EN is driven above

VEN,R (1.23V nom) a startup sequence will be enabled. If EN

falls VEN,HYS below VEN,R (1.03V nom) switching regulation

will be disabled.

CVCC

1µF

GND

Under Voltage Lock-out

.C

on

fi

de

nti

a

To prevent operation before all internal circuitry is ready and

to ensure that the power and synchronous rectifier switches

can be sufficiently enhanced, this device includes undervoltage lockout protection at IN and VCC. The device remains

in a low current state and all switching actions are inhibited

until IN exceeds VIN,UVLO and VCC exceeds VIN,UVLO. At that

time, if EN is enabled, the device will start-up by initiating a

soft-start ramp. If IN or VCC fall below their respective

UVLO falling thresholds, the device will be disabled.

lP

AGND

rep

are

VCC

Differential Remote Sense (FBS, GNDS)

FBS and GNDS may be used as a differential feedback

connection directly to the output capacitor or main load

connection. This helps to compensate for DC losses in the

PCB at high output currents. Keep these connections short

and direct. If remote sense is not required, connect GNDS

directly to AGND. GNDS must be within +/-0.2V of GND

and AGND.

Power Good (PG)

This device integrates a floating power supply for the gate

driver that operates the power switch. Proper operation

requires a 0.1µF low ESR ceramic capacitor to be connected

between BS and LX. This bootstrap capacitor provides the

gate driver supply voltage for the high-side N-channel power

MOSFET switch.

The power good indicator is an open drain output controlled

by a window comparator connected to the internal feedback

signal VFB. PG will be high impedance during normal device

operation when VFBS is within a range of VREF x 0.925 to VREF

x 1.05 (nom) for at least tPG,R . Once within this range and to

prevent a false fault indication, PG will remain high

impedance unless VFB falls below VREF*0.80 or exceeds VREF

x 1.20 (nom) for tPG,F.

erg

yC

orp

External Bootstrap Capacitor (BS)

CBS

0.1µF

Sil

BS

LX

Enable Control (EN)

PG is held low during start up, when the device is disabled and

during an over-temperature protection (OTP) fault condition

(see OTP). PG should be pulled up to a 3.3V (nom) or lower

logic supply through a resistor in the range 10kΩ~100kΩ. PG

will remain low even if VCC is 0V.

EN is a high-voltage capable input with a stable, logiccompatible threshold that provides convenient control of

device start-up behavior such as automatic, delayed or logicDS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

10

All Rights Reserved.

�SQ29020

Programmable Soft-start Time (SS)

Pre-biased operation

A soft-start circuit is incorporated to smoothly ramp the output

to the desired voltage whenever the device is enabled. At

startup, soft-start clamps the output at a low voltage and then

ramps the output to the desired voltage over the soft-start time

tSS, which avoids high current flow and transients during

startup. The default tSS is ~1mS. Longer tSS may be achieved

by connecting a capacitor CSS from SS to AGND.

If the output is not at 0V at startup, it is considered pre-biased.

In this case, the power switch and synchronous rectifiers will

not begin switching until the soft-start ramp VSS,ACT exceeds

the sensed output voltage VFBS.

The output is actively discharged when the converter is shut

down by EN, UVLO or OTP. Typically 120Ω, the discharge

FET parallels the synchronous rectifier and pulls LX low to

discharges the output through the inductor.

CSS (nF) VREF

ISS (μA)

导

小

芯

t SS (ms)=

Output Discharge

(where ISS is ~46μA, VREF is 0.6V)

Fault Protections

Selecting CSS = 150nF would set tSS ~ 2ms. CSS is not required

if the default tSS of ~ 1ms is adequate for the application.

or

半

Output Under Voltage Protection (UVP)

If a fault condition, such as a short circuit at the output, brings

VFBS < ~50% of the set point for tUVP,DLY, UVP will be

triggered and switching will be disabled for tHICCUP,OFF.

Switching will resume for tHICCUP,ON and this cycle will repeat.

If the output fault conditions are removed, the device will

return to normal operation.

VFB

VCC

Min{VSS,INT,VSS,VREF}

ISS,INT

dF

VSS,ACT

VCC

ISS

Output Short Circuit

SS

VREF

VSS,INT

VSS

CSS

GND

de

nti

a

Startup and Shutdown sequence

.C

orp

VUVLO

yC

EN

tDLY2

470µs

erg

tDLY1

80µs

VCC

VREF

Sil

VSS,ACT(internal signal)

VPG

VFB

Bottom FET

current limit

IL

VSS,ACT(internal signal)

on

fi

If IN exceeds VIN,UVLO, normal startup can be initiated by

bringing EN high, or by pulling EN high from V IN. After a

short delay, tDLY1, the internal VCC LDO is turned on to

power the internal control circuits. Once VCC is up and after

another short delay, tDLY2, the soft-start signal Vss ramps and

normal switching action begins. The output voltage VOUT

ramps up and once the output voltage is 92.5% of the

regulation point, PG becomes high-impedance after a delay

time tPG,R.

VIN

~50%VSET

VOUT

lP

AGND

rep

are

Set

UVP delay

time

0.6VREF

Hic-up off Hic-up on

time

time

Hic-up off

time

Soft start

time

Over Temperature Protection (OTP)

OTP includes circuitry to prevent overheating due to

excessive power dissipation. This will shut down the device

when the junction temperature exceeds 160°C. Once the

junction temperature cools down by approximately 30°C, the

device will resume normal operation with a complete soft-start

cycle. For continuous operation, provide adequate cooling so

that the junction temperature does not exceed the OTP

threshold.

TSD

TSD-THYS

VPG-VPG,HYS

VUVP

tSS

TJ

VOUT

tPG,R

tPG,F

VSS,ACT

(internal signal)

VREF

PG

VOUT

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

11

All Rights Reserved.

�SQ29020

PFM / FCCM settings determine the behavior. In FCCM, the

synchronous rectifier will be turned on and will remain on for

most of the cycle, except for tON minimum pulses of tON,MIN. In

PFM, the synchronous rectifier will remain on only until the

inductor current reaches zero. Further switching is inhibited. If

VFBS exceeds VOVP, OQDM is activated.

Valley Current Limit Protection (OCP)

Inductor current is measured in the synchronous rectifier on

every cycle when it turns on and as the inductor current

ramps down. If the current exceeds ILMT,BOT, the next tON is

inhibited until the current returns back to safe levels.

Bottom FET current limit

See Inductor Design regarding proper inductor value selection.

Under light loads false OVP triggering is possible if the

inductor is too small. This may also cause the reverse current

limiting.

IL

导

小

芯

VFB

VREF

Output Quick Discharging Mode (OQDM)

When operating in PFM under light load conditions, if FBS is

driven above VOVP for more than ~20μs, OQDM will be

activated. This changes the operating mode to FCCM. The

synchronous rectifier is turned on at a very high duty factor to

discharge the output as quickly as possible. This will continue

until the inductor current becomes positive and VFBS is below

VOVP. Note that OQDM may not prevent UVP or OTP from

triggering a latch off protection of the device.

VLX

VFB 500µF and minimum load current is

low, set feed-forward values as RFF = 1kΩ and CFF > 2.2nF to

provide for sufficient ripple signal to VFBS for small output

ripple and good transient behavior.

Silergy Corp. Confidential- Prepared for Customer Use Only

14

All Rights Reserved.

�SQ29020

the input capacitor should be connected to the IN and GND by

wide copper plane. Place one smaller package input MLCC

capacitor at the reach out port of pin18. This capacitor can be

connected with GND by vias.

Thermal Design Considerations

Maximum power dissipation depends on the thermal

resistance of the IC package, the PCB layout, the surrounding

airflow, and the difference between the junction and ambient

temperatures. The maximum power dissipation may be

calculated by:

PD,MAX = (TJ,MAX− TA) / θJA

where, TJ,MAX is the maximum junction temperature, T A is the

ambient temperature, and θJA is the junction to ambient

thermal resistance.

导

小

芯

or

半

AGND Layout: Make one Kelvin connection between AGND

and GND at the CVCC negative sides. CSS, RMODE, RILMT should

connect to AGND using short, direct copper trace.

rep

are

dF

Feedback Network: Place the feedback components (R1, R2,

RFF and CFF) as close to FBS pin as possible. Avoid routing

the remote output sense line and remote GND sense (GNDS)

line near LX, BS or other high frequency signal as they are

noise sensitive. Make the feedback sampling point Kelvin

connect with COUT rather than the inductor output terminal.

.C

5

4.2

orp

4

3

1

0

0

25

50

75

Layout Design

Sil

Ambient Temperature (

100

LX Connection: The LX connection has large voltage swings

and fast edges and can easily radiate noise to adjacent

components. Keep its area small to prevent excessive EMI,

while providing wide copper traces to minimize parasitic

resistance and inductance. Keep sensitive components away

from the switching node or provide ground traces between for

shielding, to prevent stray capacitive noise pickup.

BS Capacitor: Place the BS capacitor on the same layer as the

device, keep the BS voltage path (BS, LX and CBS) as short as

possible.

Control Signals: It is not recommended to connect control

signals and IN directly. A resistor in a range of 1kΩ to 1MΩ

should be used if they are pulled high by IN.

GND Vias: Place adequate number of vias on the GND layer

around the device for better thermal performance.

yC

2

erg

Maximum Power Dissipation (W)

Maximum Power Derating Curve

on

fi

de

nti

a

The maximum power dissipation at T A=25℃ may be

calculated by the following formula:

PD,MAX = (125℃ − 25℃) / (24℃/W) = 4.2W

The maximum power dissipation depends on operating

ambient temperature for fixed T J,MAX and thermal resistance

θJA. Use the derating curve in figure below to calculate the

effect of rising ambient temperature on the maximum power

dissipation.

VCC Capacitor: Place the VCC capacitor close to VCC using

short, direct copper trace to one nearest device GND pin.

lP

The recommended operating conditions include a maximum

junction temperature of 125℃. The junction to ambient

thermal resistance θJA is layout dependent. For the QFN3×419 package the thermal resistance θJA is 24℃/W when

measured on a standard Silergy four-layer thermal test board.

These standard thermal test layouts have a very large area with

long 2-oz. copper traces connected to each IC pin and very

large, unbroken 1-oz. internal power and ground planes. Good

thermal performance requires wide copper traces at all the

pads leading to exposed copper areas on the component side

of the board as well as good thermal via from the exposed pad

connecting to a wide middle-layer ground plane and, perhaps,

to an exposed copper area on the board's solder side.

Output Capacitors: Guarantee the COUT negative sides are

connected with GND pin by wide copper traces instead of

vias, in order to achieve better accuracy and stability of output

voltage.

125

)

Follow these PCB layout guidelines for optimal performance

and good thermal dissipation.

PCB Board: A four-layer layout with 2-oz copper is strongly

recommended to achieve better thermal performance. The top

layer and bottom layer should place power IN and GND

copper plane as wide as possible. Middle1 layer should place

all GND layer for conducting heat and shielding middle2 layer

signal line from top layer crosstalk. Place signal lines on

middle2 layer instead of the other layers, so that the other

layers’ GND plane not be cut apart by these signal lines.

Input Capacitors: Place the input capacitor very near IN and

GND, minimizing the loop formed by these connections. And

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

15

All Rights Reserved.

�SQ29020

CFF

RILMT

RFF

R2

VIN

RMODE

IN Vias

to EN

R1

MODE

5

4

3

ILMT

FBS

6

AGND

EN

7

2

IN

GND Vias

1

8

PG

19

18

9

BS

CIN

IN

17

LX

11

12

13

14

15

GND

GND

GND

GND

GND

GND

16

10

VCC

AGND Kelvin connection

CVCC

GND

L

or

半

COUT

GND Vias

导

小

芯

CIN

SS

CBS

GNDS

CIN

GND Vias

CSS

open drain

CIN

COUT

remote GND sense

COUT

dF

COUT

remote output sense

Top Layer

Middle2 Layer

VOUT

Middle1 Layer

(GND Layer, not shown)

lP

GND

rep

are

COUT

Bottom Layer

Sil

erg

yC

orp

.C

on

fi

de

nti

a

Figure 4. PCB Layout Suggestion

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

16

All Rights Reserved.

�SQ29020

rep

are

dF

or

半

导

小

芯

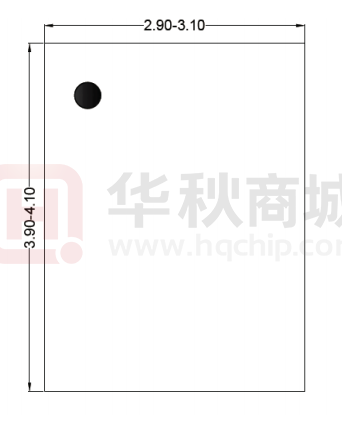

QFN3×4-19 Package Outline Drawing

Bottom view

Sil

erg

yC

orp

.C

on

fi

de

nti

a

lP

Top view

Front view

Recommended PCB layout (Reference only)

Notes: All dimension in millimeter and exclude mold flash & metal burr. Center line refers chip body center.

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

17

All Rights Reserved.

�SQ29020

Taping & Reel Specification

Package orientation

or

半

导

小

芯

1.

Carrier Tape & Reel specification for packages

QFN3×4

12

Pocket pitch(mm)

yC

Tape width

(mm)

8

Reel size (Inch)

Trailer length (mm)

Leader length

(mm)

Qty per reel

13"

400

400

5000

Sil

erg

Package type

orp

.C

on

fi

Reel

Size

de

nti

a

lP

rep

are

2.

dF

Feeding direction

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Silergy Corp. Confidential- Prepared for Customer Use Only

18

All Rights Reserved.

�SQ29020

Revision History

Revision Number

Description

Pages changed

Initial draft

1.

The max. input voltage changes from 18V to 16V;

2.

Update the Absolute Maximum Ratings

3. Add efficiency curves for PFM Mode;

4. Update the Detailed Description.

a) Add Minimum Duty Cycle and Maximum Duty Cycle (page9);

b) Update the diagrammatic drawing in UVP description (page11);

c) Update the Layout Design (page15)

Revision history is for reference only and may not be comprehensive or complete.

Page3

Page 5~6

Page9~15

Sil

erg

yC

orp

.C

on

fi

de

nti

a

lP

rep

are

dF

or

半

导

小

芯

0.0

0.0A

Revision

Date

04/17/2020

07/28/2020

DS_SQ29020 Rev.0.0A

©2020 Silergy Corp.

Powered by TCPDF (www.tcpdf.org)

Silergy Corp. Confidential- Prepared for Customer Use Only

19

All Rights Reserved.

�