COS1042

High-Speed CAN Transceiver

Features

General Description

■

Very Low Standby Current (5 μA,typical)

The COS1042 is a high-speed CAN, fault

■

Suitable for 12 V and 24 V systems

tolerant

■

VIO Supply Pin to interface Directly to CAN

between a Controller Area Network (CAN)

Controllers and MCU with 1.8V to 5.5V I/O

protocol controller and the physical two-wire

SPLIT Output Pin to Stabilize Common Mode

CAN bus. The COS1042 provides differential

in Biased Split Termination Schemes

transmit and receive capability for the CAN

CAN Bus Pins are Disconnected when

protocol controller, and is fully compatible with

Device is Unpowered

the ISO-11898-2 and ISO-11898-5 standards.

■

■

■

Bus Glitch-Free Power-Up and Power-Down

■

Over Temperature Protection

■

Allow Up to 128 Transceivers on the bus

■

Data Rate Up to 5Mbps

■

Half-duplex Transceiver

■

Available Packaging: SOP8/DFN8/DIP8

transceiver. It serves the interface

The COS1042 can be interfaced directly to

micro-controllers with supply voltages from

1.8V to 5.5V. It has a passive behavior to the

CAN bus when the supply voltage is off.

Applications

The COS1042 has a very low-current standby

■

Industrial Automation, Control

reliable communication in the CAN FD fast

■

CAN Networks

phase at data rates up to 5 Mbit/s.

Rev1.0

Copyright@2018 Cosine Nanoelectronics Inc. All rights reserved

The information provided here is believed to be accurate and reliable. Cosine Nanoelectronics assumes

no reliability for inaccuracies and omissions. Specifications described and contained here are subjected

to change without notice on the purpose of improving the design and performance. All of this information

described herein should not be implied or granted for any third party.

www.cosine-ic.com

mode with bus wake-up capability. It enables

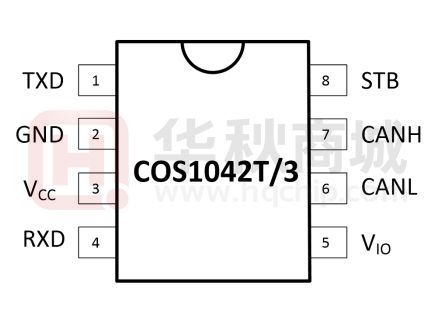

Pin Diagram

1

�COS1042

1. Pin Configuration and Block Diagram

Figure 1 Pin Diagram

Pin Description

Pin

Name

1

TXD

2

3

4

5

5

6

7

8

Description

Transmit digital data input. LOW for dominant and HIGH for

recessive bus states.

GND

VCC

RXD

Ground

Supply voltage

Receive digital data output; reads out data from the bus lines,

LOW for dominant and HIGH for recessive bus states.

SPLIT

Common-mode stabilization output; in COS1042T version only

CANL

LOW-level CAN bus I/O line

VIO

CANH

STB

Supply voltage for I/O level adapter; in COS1042T/3 version only

HIGH-level CAN bus I/O line

Standby mode control input ( Active high)

2. Ordering Information

Model

COS1042

www.cosine-ic.com

Order Number

Package

Package Option

Marking

Information

COS1042T

SOP-8

Tape and Reel, 4000

COS1042T

COS1042T/3

SOP-8

Tape and Reel, 4000

COS1042T/3

2

�COS1042

Note

1: COS1042T has the SPLIT pin.

2: COS1042T/3 has the VIO pin.

Figure 2. Block Diagram

www.cosine-ic.com

3

�COS1042

3. Product Specification

3.1 Absolute Maximum Ratings (1)

Min

Max

Unit

DC supply voltage VCC

-0.3

7

V

DC supply voltage VIO

-0.3

7

V

DC voltage at TXD, RXD, STB

-0.3

VIO + 0.3

V

DC voltage at CANH, CANL and SPLIT

-44

+44

V

RXD output current

-8

+8

mA

Operating junction temperature

-40

+125

°C

Storage temperature

-55

+150

°C

Parameter

(1) Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable

above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition,

extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute

maximum ratings are stress ratings only.

3.2 Thermal Data

Parameter

Package Thermal Resistance

Rating

Unit

150 (SOP8)

90 (DIP8)

57 (DFN8,3x3)

°C/W

3.3 Recommended Operating Conditions

Parameter

Min.

Typ.

Max.

Unit

VCC Supply voltage

4.5

5.0

5.5

V

VIO Supply voltage on Pin VIO

2.8

3.3

5.5

V

Operating ambient temperature

-40

+85

°C

Operating junction temperature

-40

+125

°C

www.cosine-ic.com

4

�COS1042

3.4 DC Characteristics

(Typical values are tested at TA=25 oC, VCC=4.5V to 5.5V, VIO=2.8V to 5.5V, RL=60Ω, unless otherwise

specified.)

Parameter

Sym.

Conditions

Min.

Typ.

Max.

Unit

VCC

4.5

5.0

5.5

V

Undervoltage detection voltage VUVD

3.5

4.0

4.5

V

Hysteresis of UVD comparator VUVDH

0.3

0.5

0.8

V

Recessive; VTXD=VIO

-

4

10

mA

Dominant; VTXD=0V

-

22

40

mA

COS1042T

-

12

17

μA

COS1042T/3

-

-

1

μA

2.8

-

5.5

V

1.3

2.0

2.7

V

Normal mode; VTXD=0 or VIO

-

20

200

μA

Standby mode;

-

12

17

μA

-0.1

0

+0.1

V

0.5VCC

3

mV

Vcc Supply

Voltage range

Supply current

ICC

Standby current

ICCS

VIO Supply

Digital Supply voltage range

VIO

Undervoltage detection voltage VUVIO

Supply current

IVIO

BUS Line (CANH; CANL) Transmitter

Standby mode

output voltage

Recessive

output voltage

VO(S)

VO(R)

Recessive

Differential output voltage

VO(DIFF)

Recessive

Short circuit output current

IO(SC)

Dominant

output voltage

VO(D)

Dominant

Differential output voltage

www.cosine-ic.com

VO(DIFF)

Standby mode,

no load

Normal mode, VTXD=VIO,

no load

2

VTXD=VIO

-50

0

50

mV

VTXD=VIO, no load

-500

0

50

mV

Normal mode,

VCANH=VCANH=-27V to +32V

-5

+5

mA

Pin CANH, VTXD=0V

2.75

3.5

4.5

V

Pin CANL, VTXD=0V

0.5

1.5

2.25

V

Dominant, Normal mode,

VTXD=0V

1.5

2.0

3.0

V

5

�COS1042

Dominant

Output voltage symmetry

-400

0

400

mV

CANH; VTXD=0, VCANH=0V

-120

-70

-40

mA

CANL; VTXD=0, VCANL=18V

40

85

120

mA

-1.0

-

+0.5

V

-1.0

-

+0.4

V

0.9

-

VDD

V

1.0

-

VDD

V

0.5

0.7

0.9

V

0.4

-

1.15

V

50

-

200

mV

RIN

10

15

25

kΩ

Common mode resistance

matching

RIN(M)

-1

-

+1

%

Differential input resistance

RIN(DIFF)

20

30

50

kΩ

Common mode input

capacitance

CIN(CM)

-

-

20

pF

Differential input capacitance

CIN(DIFF)

-

-

10

pF

+5

μA

0.7VCC

V

0.45VCC 0.5VCC 0.55VCC

V

Dominant

Short circuit output current

VO(D)(M) VDD-VCANH-VCANL

IO(SC)

BUS Line (CANH; CANL) Receiver

Normal mode;

Recessive Differential input

voltage

VDIFF(RI)

12V VCANH,CANL +12V;

Standby mode;

12V VCANH,CANL +12V;

Normal mode;

Dominant Differential input

voltage

VDIFF(DI)

12V VCANH,CANL +12V;

Standby mode;

12V VCANH,CANL +12V;

Normal mode;

Differential Receiver Threshold VTH(DIFF)

12V VCANH,CANL +12V;

Standby mode;

12V VCANH,CANL +12V;

Differential Input Hysteresis

Common mode input

resistance

Input leakage current

VHYS(DIFF)

ILI

Normal mode

VCC = VTXD = VSTB = 0V;

VCANH = VCANL = 5V

-5

SPLIT; Common Mode Stabilization Output Pin (only for COS1042T)

Output voltage

VO

Leakage current

IL

Normal mode;

ISPLIT = -500μA to +500μA

Normal mode;

RL = 1MΩ

Standby mode;

VSPLIT = -24V to +24V

0.3VCC

0.5VCC

-5

+5

μA

TXD, STB Digital Input Pin

HIGH-level input voltage

VIH

0.7VIO

-

VIO+0.3

V

LOW-level input voltage

VIL

-0.3

-

0.3VIO

V

HIGH-level input current

IIH

-1

+1

μA

www.cosine-ic.com

6

�COS1042

TXD:LOW-level input current IIL(TXD)

STB:LOW-level input current

IIL(STB)

-270

-150

-30

μA

-20

-

-1

μA

RXD Receive Data Output Pin

HIGH-level output voltage

VOH

IOH=-4mA

VIO-0.4

-

-

V

LOW-level output voltage

VOL

IOL=4mA

-

-

0.4

V

TJ(SD)

160

170

180

°C

TJ(HYST)

20

30

40

°C

Thermal Shutdown

Shutdown

junction temperature

Shutdown

temperature Hysteresis

3.5 Dynamic Characteristics

(Typical values are tested at TA=25 oC, VCC=4.5V to 5.5V, VIO=1.8V to 5.5V, RL=60Ω, unless otherwise

specified. See Figure 6,7,8)

Parameter

Sym.

Delay TXD Low to bus dominant

tTXD-BUSON

Min.

Typ.

Max.

Unit

Normal mode

-

65

-

ns

Delay TXD High to bus recessive tTXD-BUSOFF Normal mode

-

60

-

ns

Delay bus dominant to RXD

tBUSON-RXD Normal mode

-

65

-

ns

Delay bus recessive to RXD

tBUSOFF-RXD Normal mode

-

65

-

ns

Propagation delay TXD Low

to RXD Low

Propagation delay TXD High

to RXD High

Bus wake-up filter time

Delay standby to normal mode

Conditions

tTXDL-RXDL

Normal mode

-

-

220

ns

tTXDH-RXDH

Normal mode

-

-

220

ns

tFLTR(WAKE)

Standby mode

0.5

1

4

μs

2

3

10

μs

tWAKE

Negative edge on STB

TXD dominant time-out time

Tto(dom)TXD VTXD=0V, Normal mode

0.3

2

5

ms

Bus dominant time-out time

Tto(dom)BUS Standby mode

0.3

2

5

ms

4. Functional Description

4.1 Operating Mode

The COS1042 supports two operating modes, Normal and Standby, which are selected via pin STB.

See Table 1 for a description of the operating modes under normal supply conditions.

www.cosine-ic.com

7

�COS1042

Table 1. Operating Modes

Mode

STB

DRIVER

RECEIVER

Normal

LOW

Enable

(ON)

Standby

HIGH

Disable

(OFF)

Enable

(ON)

Only low power

Bus monitor is

active

RXD

LOW

HIGH

Bus dominant

Bus recessive

Wake-up request

detected

No wake-up request

detected

4.1.1 Normal Mode

A LOW level on pin STB selects Normal mode. In this mode, the transceiver can transmit and

receive data via the bus lines CANH and CANL (see Figure 2 for the block diagram). The differential

receiver converts the analog data on the bus lines into digital data which is output to pin RXD. The

slopes of the output signals on the bus lines are controlled internally and are optimized in a way that

guarantees the lowest possible EME.

4.1.2 Standby Mode

A HIGH level on pin STB selects Standby mode. In Standby mode, the transceiver is not able to

transmit or correctly receive data via the bus lines. The transmitter and Normal-mode receiver blocks

are switched off to reduce supply current, and only a low-power differential receiver monitors the bus

lines for activity. The wake-up filter on the output of the low-power receiver does not latch bus

dominant states, but ensures that only bus dominant and bus recessive states that persist longer

than tfltr(wake)bus are reflected on pin RXD. In Standby mode, the bus lines are biased to ground to

minimize the system supply current. The low-power receiver is supplied by VIO, and is capable of

detecting CAN bus activity even if VIO is the only supply voltage available. When pin RXD goes LOW

to signal a wake-up request, a transition to Normal mode will not be triggered until STB is forced

LOW.

4.2 Fail-Safe Features

4.2.1 TXD Dominant Time-out Function

A ‘TXD dominant time-out’ timer is started when pin TXD is set LOW. If the LOW state on pin TXD

persists for longer than tto(dom)TXD, the transmitter is disabled, releasing the bus lines to recessive

state. This function prevents a hardware and/or software application failure from driving the bus lines

to a permanent dominant state (blocking all network communications). The TXD dominant time-out

timer is reset when pin TXD is set to HIGH. The TXD dominant time-out time also defines the

minimum possible bit rate of 40 kbit/s.

www.cosine-ic.com

8

�COS1042

4.2.2 Bus Dominant Time-out Function

In Standby mode a 'bus dominant time-out' timer is started when the CAN bus changes from

recessive to dominant state. If the dominant state on the bus persists for longer than tto(dom)bus, the

RXD pin is reset to HIGH. This function prevents a clamped dominant bus (due to a bus short-circuit

or a failure in one of the other nodes on the network) from generating a permanent wake-up request.

The bus dominant time-out timer is reset when the CAN bus changes from dominant to recessive

state.

4.2.3 Internal Biasing of TXD and STB Input Pins

Pins TXD and STB have internal pull-ups to VIO to ensure a safe, defined state in case one or both of

these pins are left floating. Pull-up currents flow in these pins in all states; both pins should be held

HIGH in Standby mode to minimize standby current.

4.2.4 Undervoltage Detection on Pins Vcc and VIO

Should VCC drop below the VCC undervoltage detection level, VUVD(VCC), the transceiver will switch to

Standby mode. The logic state of pin STB will be ignored until VCC has recovered. Should VIO drop

below the VIO undervoltage detection level, VUVD(VIO), the transceiver will switch off and disengage

from the bus (zero load) until VIO has recovered.

4.2.5 Over-temperature Protection

The output drivers are protected against over-temperature conditions. If the virtual junction

temperature exceeds the shutdown junction temperature, Tj(sd), the output drivers will be disabled

until the virtual junction temperature falls below Tj(sd) and TXD becomes recessive again. Including

the TXD condition ensures that output driver oscillation due to temperature drift is avoided.

4.2.6 Unpowered Device

The COS1042 is designed to be “ideal passive” or “no load” to the CAN bus if it is unpowered. The

bus terminals (CANH, CANL) have extremely low leakage currents when the device is unpowered to

avoid loading down the bus. This is critical if some nodes of the network are unpowered while the

rest of the of network remains in operation. The logic terminals also have extremely low leakage

currents when the device is unpowered to avoid loading down other circuits that may remain

powered.

www.cosine-ic.com

9

�COS1042

4.2.7 Floating Terminals

The COS1042 has internal pull ups on critical terminals to place the device into known states if the

terminals float. The TXD terminal is pulled up to VCC or VIO to force a recessive input level if the

terminal floats. The STB terminal is also pulled up to force the device into low power Standby mode if

the terminal floats.

4.2.8 CAN Bus Short Circuit Current Limiting

The COS1042 has The device has two protection features that limit the short circuit current when a

CAN bus line is short-circuit fault condition: driver current limiting (both dominant and recessive

states) and TXD dominant state time out to prevent permanent higher short circuit current of the

dominant state during a system fault.

4.3 SPLIT Output Pin and VIO Supply Pin

Two versions of the COS1042 are available, only differing in the function of a single pin. Pin 5 is

either a SPLIT output pin or a VIO supply pin. Using the SPLIT pin on the COS1042T in conjunction

with a split termination network (see Figure 3 and Figure 4) can help to stabilize the recessive

voltage level on the bus. This will reduce EME in networks with DC leakage to ground (e.g. from

deactivated nodes with poor bus leakage performance). In Normal mode, pin SPLIT delivers a DC

output voltage of 0.5VCC. In Standby mode or when VCC is off, pin SPLIT is floating. When not used,

the SPLIT pin should be left open.

Pin VIO on the COS1042T/3 should be connected to the micro-controller supply voltage (see Figure

5). This will adjust the signal levels of pins TXD, RXD and STB to the I/O levels of the

micro-controller. Pin VIO also provides the internal supply voltage for the low-power differential

receiver of the transceiver. For applications running in low-power mode, this allows the bus lines to

be monitored for activity even if there is no supply voltage on pin VCC. For versions of the COS1042

without a VIO pin, the VIO input is internally connected to VCC. This sets the signal levels of pins TXD,

RXD and STB to levels compatible with 5 V micro-controllers.

www.cosine-ic.com

10

�COS1042

Figure 3. Stabilization Circuitry and Application for Version with SPLIT Pin

5. Typical Application Diagrams

Figure 4. Typical Application with COS1042T and a 5V Micro-controller

www.cosine-ic.com

11

�COS1042

Figure 5. Typical Application with COS1042T/3 and a 3V Micro-controller

Figure 6. Test Circuit for Measuring Transceiver Driver Symmetry

www.cosine-ic.com

12

�COS1042

Figure 7. CAN Transceiver Timing Diagram

Figure 8. CAN FD Timing Definition According to ISO11898-2

www.cosine-ic.com

13

�COS1042

6. Package Information

6.1 SOP8 (Package Outline Dimensions)

6.2 DIP8 (Package Outline Dimensions)

www.cosine-ic.com

14

�