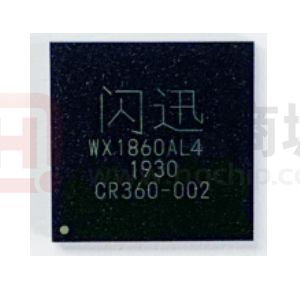

WX1860 Datasheet

2019.12

�WX1860 Datasheet

Revision History

Revision

Data

Comments

0.1

2018.12

Initial revision

0.2

2019.8

Add DC characteristics and footprint

0.3

2019.9

Add ordering information

0.4

2019.10

Change Emerald to WX1860, update section 1.3.4

0.5

2019.11

Update pin description

0.6

2019.11

Add suggested SPI flash and MDI signal description

0.7

2019.12

Add IO DC specification

1

�WX1860 Datasheet

Table of Contents

Revision History .............................................................................................................................. 1

Table of Contents ............................................................................................................................ 2

1 Feature List................................................................................................................................... 4

1.1 Network Feature ............................................................................................................................ 4

1.2 PCIe Feature .................................................................................................................................. 5

1.3 LAN Feature ................................................................................................................................... 6

1.4 Virtualization Features ................................................................................................................... 8

1.5 Management Feature .................................................................................................................... 9

1.6 Algorithm Feature ........................................................................................................................ 10

1.7 Power Management Features ...................................................................................................... 10

2 Pin Interface ............................................................................................................................... 11

2.1 Package Size ................................................................................................................................ 11

2.2 Ball Map ...................................................................................................................................... 13

2.3 Pin Descrption ............................................................................................................................. 13

2.3.1 Misc Interface ....................................................................................................................... 13

2.3.2 Internal PHY #0 ..................................................................................................................... 15

2.3.3 RGMII PHY #0 ........................................................................................................................ 16

2.3.4 Internal PHY #1 ..................................................................................................................... 17

2.3.5 RGMII PHY #1 ........................................................................................................................ 18

2.3.6 Internal PHY #2 (4-Port only) ................................................................................................. 18

2.3.7 RGMII PHY #2 (4-Port only) ................................................................................................... 19

2.3.8 Internal PHY #3 (4-Port only) ................................................................................................. 20

2.3.9 RGMII PHY #3 (4-Port only) ................................................................................................... 21

2.3.10 GPIO ................................................................................................................................... 21

2.3.11 Management Interface........................................................................................................ 22

2.3.12 TS1588 Pins ......................................................................................................................... 23

2.3.13 PCIe Interface...................................................................................................................... 23

2.3.14 SPI flash Interface................................................................................................................ 24

2.3.15 JTAG.................................................................................................................................... 25

2.3.16 Power Supply ...................................................................................................................... 25

2.3.17 Ground................................................................................................................................ 26

2.4 Ball List ordered by Ball location .................................................................................................. 26

3 电气规格.................................................................................................................................... 36

3.1

3.2

3.3

3.4

3.5

3.6

极限工作条件 ........................................................................................................................... 36

建议工作条件 ........................................................................................................................... 36

直流特性 ................................................................................................................................... 36

外部时钟输入 ........................................................................................................................... 37

上电顺序 ................................................................................................................................... 38

工作电流 ................................................................................................................................... 38

2

�WX1860 Datasheet

4 SPI Flash 推荐型号 .................................................................................................................... 39

5 订购信息.................................................................................................................................... 40

3

�WX1860 Datasheet

1 Feature List

1.1 Network Feature

Feature

I350

WX1860

10/100/1000 Copper PHY integrated on-chip

4 ports

2/4 ports

Jumbo frames supported

9.5 KB

9.5 KB

Flow control support: send/receive PAUSE frames and receive

FIFO thresholds

Y

Y

Statistics for management and RMON

Y

Y

802.1q VLAN support

Y

Y

802.3az EEE support

Y

Y

MDI Flip

Y

Y

SerDes interface for external PHY connection or system

interconnect

4 ports

N

1000BASE-KX interface for Blade Server Backplane connections

Y

N

802.3ap Backplane Auto-negotiation

N

N

SGMII interface for external 1000BASE-T PHY connection

4 ports

N

RGMII interface for external PHY

N

2/4 ports

Fiber/copper auto-sense

4 ports

N

SerDes support of non-Auto-Negotiation partner

Y

N

SerDes signal detect

Y

N

External PHY control I/F MDC/MDIO

shared or

perfunction

perfunction

4

�WX1860 Datasheet

Feature

I350

WX1860

External PHY control I/F 2 wire I/F

perfunction

perfunction

IPsec with SM4-GCM algorithm

N

Y

LinkSec with SM4-GCM algorithm

N

Y

1.2 PCIe Feature

Feature

I350

WX1860

Max Link Speed

Gen2x4

Gen2x4

Max Payload Size

512 B

128 B

Max Read Request Size

2 KB

128 B

VPD

Y

Y

ECRC

Y

Y

LTR

Y

N

CSR access via Configuration space

Y

N

ACS

Y

N

AER

Y

Y

Multiple PF

4

4

DCA support

Y

N

TPH support

N

Y

PF FLR

Y

Y

SR-IOV

8VF/PF

8VF/PF

VF AER

Y

Y

5

�WX1860 Datasheet

Feature

I350

WX1860

VF FLR

Y

Y

64-bit BAR

Y

Y

MSI

Y

Y

MSI-X

32/PF

32/PF

VF MSI-X

2/VF

2/VF

1.3 LAN Feature

Feature

I350

WX1860

Programmable host memory receive buffers

Y

Y

Descriptor ring management hardware for transmit and receive

Y

Y

Software controlled global reset bit (resets everything except the

configuration registers)

Y

Y

Software Definable Pins (SDP) - per port

4

4

Four SDP pins can be configured as general purpose interrupts

Y

Y

Wake up

Y

Y

Flexible wake-up filters

8

8

Flexible filters for queue assignment in normal operation

8

N

IPv6 wake-up filters

Y

Y

Default configuration by the EEPROM for all LEDs for pre-driver functionality

4 LED

4 LED

LAN function disable capability

Y

Y

Programmable memory transmit buffers

Y

Y

6

�WX1860 Datasheet

Feature

I350

WX1860

Double VLAN

Y

Y

IEEE 1588

Y

Y

Per-Packet Timestamp

Y

N

TX rate limiting per queue

N

N

TCP segmentation offload Up to 256 KB

Y

Y

iSCSI TCP segmentation offload (CRC)

N

N

IPv6 support for IP/TCP and IP/UDP receive checksum offload

Y

Y

Fragmented UDP checksum offload for packet reassembly

Y

Y

Message Signaled Interrupts (MSI)

Y

Y

Message Signaled Interrupts (MSI-X) number of vectors

25

36

Packet interrupt coalescing timers (packet timers) and absolute delay

interrupt timers for both transmit and receive operation

Y

Y

Interrupt throttling control to limit maximum interrupt rate and improve CPU

utilization

Y

Y

Rx packet split header

Y

Y

Receive Side Scaling (RSS) number of queues per port

up to 8 up to 8

Total number of Rx queues per port

8

8

Total number of TX queues per port

8

8

RX header replication

Y

N

Low latency interrupt

Y

Y

TCP timer interrupts

Y

Y

No snoop

Y

Y

7

�WX1860 Datasheet

Feature

I350

WX1860

Relax ordering

Y

Y

TSO interleaving for reduced latency

Y

Y

1.4 Virtualization Features

Feature

I350

WX1860

Support for Virtual Machines Device queues (VMDq) per

port

8 pools single

queue

8 pools single

queue

L2 MAC address filters (unicast and multicast)

32

32

L2 VLAN filters

per pool

per pool

PCI-SIG SR-IOV

8 VF

8 VF

Multicast/Broadcast Packet replication

Y

Y

VM to VM Packet forwarding (Packet Loopback)

Y

Y

MAC and VLAN anti-spoofing

Y

Y

Per-pool statistics

Y

Y

Per-pool off loads

Y

Y

Per-pool jumbo support

Y

Y

Mirroring rules

4

4

External switch VEPA support

Y

Y

Promiscuous modes

VLAN, unicast,

multicast

VLAN, unicast,

multicast

ETAG

N

Y

8

�WX1860 Datasheet

1.5 Management Feature

Feature

I350

WX1860

Advanced pass-through-compatible management packet

transmit/receive support

Y

Y

Managed ports on SMBus interface to external BMC

4

4

Auto-ARP reply over SMBus

Y

Y

NC-SI Interface to an External BMC

Y

Y

Standard DMTF NC-SI protocol support

Y

Y

DMTF MCTP protocol over SMBus

Y

Y

NC-SI HW arbitration

Y

Y

OS to BMC traffic

Y

Y

L2 address filters

2

4

VLAN L2 filters

8

8

EtherType filters

4

4

Flex L4 port filters

8

16

Flex TCO filters

1

4

L3 address filters (IPv4)

4

4

L3 address filters (IPv6)

4

4

Build-in Temperature sensor

N

Y

9

�WX1860 Datasheet

1.6 Algorithm Feature

Feature

I350

WX1860

Hardware implemented SM2/SM3/SM4 engine

N

Y

True Random number generator

N

Y

1.7 Power Management Features

Feature

I350

WX1860

Magic packet wake-up enable with unique MAC address

Y

Y

ACPI register set and power down functionality supporting D0 and D3 states

Y

Y

Full wake-up support (APM and ACPI 2.0)

Y

Y

Smart power down at S0 no link and Sx no link

Y

Y

LAN disable functionality

Y

Y

EEE

Y

Y

DMA coalescing

Y

N

10

�WX1860 Datasheet

2 Pin Interface

2.1 Package Size

11

�WX1860 Datasheet

Symbol

Min

Nominal

Max

A

1.17

1.24

1.31

A1

0.13

0.18

0.23

A2

1.01

1.06

1.11

c

0.32

0.36

0.40

b

0.20

0.25

0.30

D

12.90

13.00

13.10

E

12.90

13.00

13.10

D1

--

11.70

--

E1

--

11.70

--

e

--

0.65

--

aaa

0.10 BSC

ccc

0.15 BSC

ddd

0.13 BSC

eee

0.15 BSC

fff

0.08 BSC

N

327

Note:

1. Controlling dimension: millimeter

2. Primary datum C and seating plance are defined by the spherical crowns of the solder

balls.

3. Dimension b is measured at the maximum solder ball diameter, parallel to primary

datum c.

4. The pattern of pin 1 fiducial is for reference only.

5. Refernce document: JEDEC publication 95 design guide 4.5

12

�WX1860 Datasheet

2.2 Ball Map

Figure 1 Ball Map

2.3 Pin Descrption

2.3.1 Misc Interface

芯片采用 3.3V LVCMOS IO 电平标准。输出最大驱动电流 16mA。列表中 Pull 状态表示内部

上下拉电阻状态,上下拉电阻值为 75KΩ。Misc 信号有内部上下拉,正常模式下可以悬空。

需保留调试模式时,可以加外部电阻。MDI/RGMII/GPIO 信号,端口不用时都可以悬空。

Name

Location

Direction

Pull

Description

prb_en

D1

IN

Down

用于调试,N/C

prb_hit

C12

OUT

用于调试,N/C

prb_clkout

C13

OUT

用于调试,建议加测试点

pcie_bsy

D2

OUT

高有效信号,用于指示 PCIe 连接上有数据传

输。

13

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

mng_bsy

C1

OUT

scan_enable

G2

IN

Down

用于 DFT 测试。正常模式 N/C。

test_sel

F5

IN

Down

用于调试,N/C

test_mode_0

F1

IN

Down

test_mode_1

F4

IN

Down

test_mode_2

F2

IN

Down

jtag_sel_0

E16

IN

Down

jtag_sel_1

C19

IN

Down

clk_tst_sel_0

E4

IN

Down

clk_tst_sel_1

E1

IN

Down

clk_tst_sel_2

E5

IN

Down

clk_tst_sel_3

E2

IN

Down

flash_sector

G4

IN

Down

选择用于初始化的 flash sector, N/C

0-64KB sector

1-256KB sector

flash_bypass

H1

IN

Down

跳过 flash 初始化,用于调试,N/C

mng_det

F3

IN

Up

用于调试, N/C

sec_disable

G1

IN

Down

用于调试,N/C

use_ext_phy

E3

IN

Down

高有效信号。有效时 4 个网口都选择用外部

RGMII PHY,否则 4 个网口都用内部 PHY。

xtal_in

R2

IN

外部无源晶振的输入,也可以直接输入

25MHz 的有源时钟信号。

xtal_out

P2

OUT

输出信号用于连接外部无源晶振。

sec_mode

H2

IN

Up

用于调试, N/C

pe_rst_seq

B16

IN

Down

用于调试,N/C

pe_aux_pwr_det

D15

IN

Down

使用 WoL 功能时拉高,其他模式为低。

高有效信号用于指示 NCSI 接口上的数据传

输。

选择 JTAG 接口的使用模块,2’b11 把芯片

JTAG 接口连接在内部 CPU,其它值用于调

试。

用于调试,N/C

支持 WoL 时,支持 D0,D3hot,D3cold。D3

状态下,网口不可通信,NC/SI 可用。不支持

WoL 时,支持到 D0,D3hot,D3cold。PCIe

clock 与 WOL 无关,只在 D3cold 时由系统判

断。具体内容参考 PCIe Base spec。

14

�WX1860 Datasheet

2.3.2 Internal PHY #0

Name

Location

Direction

n0_gphy_rset

U6

A

Pull

Description

网口#0 参考电阻接口,通过 2.49KΩ±1%接地

15

�WX1860 Datasheet

n0_led_0

n0_led_1

n0_led_2

K1

H4

J2

OUT

LED_0, Programmable LED which indicates by

default activity, active high. Blink time 20-60ms

adjustable, active high/low adjustable.

OUT

LED_1, Programmable LED which indicates by

default a 100Mbps Link, active high.

OUT

LED_2, Programmable LED which indicates by

default a 1000Mbps Link, active high.

In MDI mode, this is the first pair in 1000Base-T,

i.e., the BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DB+/- pair, and is the receive pair in 10Base-T

and 100Base-TX.

n0_mdi_p_0

V6

A

n0_mdi_n_0

W6

A

n0_mdi_p_1

V5

A

n0_mdi_n_1

W5

A

n0_mdi_p_2

V4

A

n0_mdi_n_2

W4

A

n0_mdi_p_3

V3

A

n0_mdi_n_3

W3

A

In MDI mode, this is the second pair in

1000Base-T, i.e., the BI_DB+/- pair, and is the

receive pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI mode, this is the third pair in 1000Base-T,

i.e.,the BI_DC+/- pair.

In MDI crossover mode, this pair acts as the

BI_DD+/- pair.

In MDI mode, this is the Fourth pair in 1000BaseT, i.e.,the BI_DD+/- pair.

In MDI crossover mode, this pair acts as the

BI_DC+/- pair.

2.3.3 RGMII PHY #0

Name

Location

Direction

n0_rgmii_tx_0

L17

OUT

n0_rgmii_tx_1

L16

OUT

n0_rgmii_tx_2

M17

OUT

n0_rgmii_tx_3

M16

OUT

n0_rgmii_rx_0

N17

IN/OUT

n0_rgmii_rx_1

M15

IN/OUT

n0_rgmii_rx_2

P16

IN/OUT

Pull

Description

网口#0 RGMII 发送数据接口

网口#0 RGMII 接收数据接口

16

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

n0_rgmii_rx_3

P17

IN/OUT

n0_rgmii_txc

N16

OUT

n0_rgmii_tx_ctl

R16

OUT

n0_rgmii_rxc

N15

IN

Down

n0_rgmii_rx_ctl

R17

IN

Down

n0_rgmii_mdc

P15

OUT

n0_rgmii_mdio

T17

IN/OUT

网口#0 RGMII 发送控制接口

网口#0 RGMII 接收控制接口

网口#0 RGMII MDIO 接口,MDIO 信号需外部

上拉 1.5-10Kohm 电阻。

2.3.4 Internal PHY #1

Name

Location

Direction

Pull

Description

n0_dis_n

C17

IN

Up

网口#0 不使能信号,低有效

n1_dis_n

E17

IN

Up

网口#1 不使能信号,低有效

n2_dis_n

C18

IN

Up

网口#2 不使能信号,低有效

n3_dis_n

F16

IN

Up

网口#3 不使能信号,低有效

n1_gphy_rset

U9

A

网口#1 参考电阻接口,通过 2.49KΩ±1%接地

OUT

LED_0, Programmable LED which indicates by

default activity, active high. Blink time 20-60ms

adjustable, active high/low adjustable.

OUT

LED_1, Programmable LED which indicates by

default a 100Mbps Link, active high.

OUT

LED_2, Programmable LED which indicates by

default a 1000Mbps Link, active high.

In MDI mode, this is the first pair in 1000Base-T,

i.e., the BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DB+/- pair, and is the receive pair in 10Base-T

and 100Base-TX.

n1_led_0

n1_led_1

n1_led_2

H3

K2

H5

n1_mdi_p_0

V10

A

n1_mdi_n_0

W10

A

n1_mdi_p_1

V9

A

n1_mdi_n_1

W9

A

In MDI mode, this is the second pair in

1000Base-T, i.e., the BI_DB+/- pair, and is the

receive pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

17

�WX1860 Datasheet

Name

Location

Direction

n1_mdi_p_2

V8

A

n1_mdi_n_2

W8

A

n1_mdi_p_3

V7

A

n1_mdi_n_3

W7

A

Pull

Description

In MDI mode, this is the third pair in 1000Base-T,

i.e.,the BI_DC+/- pair.

In MDI crossover mode, this pair acts as the

BI_DD+/- pair.

In MDI mode, this is the Fourth pair in 1000BaseT, i.e.,the BI_DD+/- pair.

In MDI crossover mode, this pair acts as the

BI_DC+/- pair.

2.3.5 RGMII PHY #1

Name

Location

Direction

Pull

Description

n1_rgmii_tx_0

M19

OUT

n1_rgmii_tx_1

P19

OUT

n1_rgmii_tx_2

N19

OUT

n1_rgmii_tx_3

U19

OUT

n1_rgmii_rx_0

P18

IN/OUT

n1_rgmii_rx_1

V19

IN/OUT

n1_rgmii_rx_2

R18

IN/OUT

n1_rgmii_rx_3

N18

IN/OUT

n1_rgmii_txc

U18

OUT

n1_rgmii_tx_ctl

T18

OUT

n1_rgmii_rxc

L18

IN

Down

n1_rgmii_rx_ctl

T19

IN

Down

n1_rgmii_mdc

R19

OUT

n1_rgmii_mdio

M18

IN/OUT

网口#1 RGMII 发送数据接口

网口#1 RGMII 接收数据接口

网口#1 RGMII 发送控制接口

网口#1 RGMII 接收控制接口

网口#1 RGMII MDIO 接口,MDIO 信号需外部

上拉 1.5-10Kohm 电阻。

2.3.6 Internal PHY #2 (4-Port only)

Name

Location

Direction

n2_gphy_rset

U12

A

Pull

Description

网口#2 参考电阻接口,通过 2.49KΩ±1%接地

18

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

n2_led_0

M1

OUT

LED_0, Programmable LED which indicates by

default activity, active high. Blink time 20-60ms

adjustable, active high/low adjustable.

n2_led_1

J3

OUT

LED_1, Programmable LED which indicates by

default a 100Mbps Link, active high.

n2_led_2

L1

OUT

LED_2, Programmable LED which indicates by

default a 1000Mbps Link, active high.

n2_mdi_p_0

V14

A

n2_mdi_n_0

W14

A

In MDI mode, this is the first pair in 1000Base-T,

i.e., the BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DB+/- pair, and is the receive pair in 10Base-T

and 100Base-TX.

n2_mdi_p_1

V13

A

n2_mdi_n_1

W13

A

n2_mdi_p_2

V12

A

n2_mdi_n_2

W12

A

n2_mdi_p_3

V11

A

n2_mdi_n_3

W11

A

In MDI mode, this is the second pair in

1000Base-T, i.e., the BI_DB+/- pair, and is the

receive pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI mode, this is the third pair in 1000Base-T,

i.e.,the BI_DC+/- pair.

In MDI crossover mode, this pair acts as the

BI_DD+/- pair.

In MDI mode, this is the Fourth pair in 1000BaseT, i.e.,the BI_DD+/- pair.

In MDI crossover mode, this pair acts as the

BI_DC+/- pair.

2.3.7 RGMII PHY #2 (4-Port only)

Name

Location

Direction

n2_rgmii_tx_0

D19

OUT

n2_rgmii_tx_1

E18

OUT

n2_rgmii_tx_2

F18

OUT

n2_rgmii_tx_3

G18

OUT

n2_rgmii_rx_0

H18

IN

n2_rgmii_rx_1

E19

IN

Pull

Description

网口#2 RGMII 发送数据接口

网口#2 RGMII 接收数据接口

19

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

n2_rgmii_rx_2

F19

IN

n2_rgmii_rx_3

G19

IN

n2_rgmii_txc

H19

OUT

n2_rgmii_tx_ctl

J18

OUT

n2_rgmii_rxc

J19

IN

Down

n2_rgmii_rx_ctl

K18

IN

Down

n2_rgmii_mdc

K19

OUT

n2_rgmii_mdio

L19

IN/OUT

网口#2 RGMII 发送控制接口

网口#2 RGMII 接收控制接口

网口#2 RGMII MDIO 接口,MDIO 信号需外部

上拉 1.5-10Kohm 电阻。

2.3.8 Internal PHY #3 (4-Port only)

Name

Location

Direction

Pull

Description

n3_gphy_rset

U15

A

网口#3 参考电阻接口,通过 2.49KΩ±1%接地

n3_led_0

J4

OUT

LED_0, Programmable LED which indicates by

default activity, active high. Blink time 20-60ms

adjustable, active high/low adjustable.

n3_led_1

L2

OUT

LED_1, Programmable LED which indicates by

default a 100Mbps Link, active high.

n3_led_2

J5

OUT

LED_2, Programmable LED which indicates by

default a 1000Mbps Link, active high.

n3_mdi_p_0

V18

A

n3_mdi_n_0

W18

A

In MDI mode, this is the first pair in 1000Base-T,

i.e., the BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DB+/- pair, and is the receive pair in 10Base-T

and 100Base-TX.

n3_mdi_p_1

V17

A

n3_mdi_n_1

W17

A

n3_mdi_p_2

V16

A

n3_mdi_n_2

W16

A

In MDI mode, this is the second pair in

1000Base-T, i.e., the BI_DB+/- pair, and is the

receive pair in 10Base-T and 100Base-TX.

In MDI crossover mode, this pair acts as the

BI_DA+/- pair, and is the transimit pair in

10Base-T and 100Base-TX.

In MDI mode, this is the third pair in 1000Base-T,

i.e.,the BI_DC+/- pair.

20

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

In MDI crossover mode, this pair acts as the

BI_DD+/- pair.

n3_mdi_p_3

V15

A

n3_mdi_n_3

W15

A

In MDI mode, this is the Fourth pair in 1000BaseT, i.e.,the BI_DD+/- pair.

In MDI crossover mode, this pair acts as the

BI_DC+/- pair.

2.3.9 RGMII PHY #3 (4-Port only)

Name

Location

Direction

Pull

Description

n3_rgmii_tx_0

G16

OUT

n3_rgmii_tx_1

F17

OUT

n3_rgmii_tx_2

G15

OUT

n3_rgmii_tx_3

G17

OUT

n3_rgmii_rx_0

H16

IN/OUT

n3_rgmii_rx_1

J15

IN/OUT

n3_rgmii_rx_2

H15

IN/OUT

n3_rgmii_rx_3

K15

IN/OUT

n3_rgmii_txc

J16

OUT

n3_rgmii_tx_ctl

K16

OUT

n3_rgmii_rxc

L15

IN

Down

n3_rgmii_rx_ctl

H17

IN

Down

n3_rgmii_mdc

J17

OUT

n3_rgmii_mdio

K17

IN/OUT

网口#3 RGMII 发送数据接口

网口#3 RGMII 接收数据接口

网口#3 RGMII 发送控制接口

网口#3 RGMII 接收控制接口

网口#3 RGMII MDIO 接口,MDIO 信号需外部

上拉 1.5-10Kohm 电阻。

2.3.10 GPIO

Name

Location

Direction

Pull

Description

n0_gpio_0

D12

IN/OUT

网口#0 GPIO 0,可用于复位输出或中断输入

n0_gpio_1

A16

IN/OUT

网口#0 GPIO 1,可用于复位输出或中断输入

n1_gpio_0

E13

IN/OUT

网口#1 GPIO 0,可用于复位输出或中断输入

n1_gpio_1

B15

IN/OUT

网口#1 GPIO 1,可用于复位输出或中断输入

n2_gpio_0

D13

IN/OUT

网口#2 GPIO 0,可用于复位输出或中断输入

21

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

n2_gpio_1

A17

IN/OUT

网口#2 GPIO 1,可用于复位输出或中断输入

n3_gpio_0

E14

IN/OUT

网口#3 GPIO 0,可用于复位输出或中断输入

n3_gpio_1

A18

IN/OUT

网口#3 GPIO 1,可用于复位输出或中断输入

mng_gpio_0

D14

IN/OUT

CPU GPIO 0,可用于复位输出或中断输入

mng_gpio_1

C14

IN/OUT

片 CPU GPIO 1,可用于复位输出或中断输入

2.3.11 Management Interface

管理 接口可以作为 MII 接口外接 PHY 使用,也可以作为 NCSI 接 BMC 芯片使用。

在连接外部 mac 时,SMBUS mode 和 NC-SI mode 可以同时支持。

Name

Location

Direction

Pull

Description

uart_srx

A14

IN

Down

uart_stx

D11

OUT

片上 CPU UART 接口,用于调试,可访问 CPU

内部寄存器信息。

mng_ic_clk

K4

IN/OD

Up

片上 CPU I2C 接口时钟信号,该信号在任何状

态下都支持,与 pe_aux_pwr_det 无关。

mng_ic_data

P1

IN/OD

Up

片上 CPU I2C 接口数据信号,该信号在任何状

态下都支持,与 pe_aux_pwr_det 无关。

mng_ic_smbsus_n

K3

IN/OUT

Up

片上 CPU I2C 接口挂起信号

mng_ic_smbalt_n

N1

IN/OD

Up

片上 CPU I2C 接口输出中断信号

rmii_ref_clk/

ncsi_ref_clk

R1

IN

Down

NC-SI Reference Clock Input – Synchronous clock

reference for receive, transmit and control

interface. It is a 50MHz clock +/- 100 ppm.

rmii_csr_dv/

ncsi_ tx_en

K5

IN

Down

Transmit Enable

rmii_rxd_0/

ncsi_txd_0

M2

IN

Down

Transmit data signals from BMC to WX1860

rmii_rxd_1/

ncsi_txd_1

U1

IN

Down

rmii_tx_en/

ncsi_csr_dv

L4

OUT

Carrier Sense/Receive Data Valid

OUT

Received data signals from WX1860 to BMC

rmii_txd_0/

ncsi_rxd_0

T1

22

�WX1860 Datasheet

Name

Location

Direction

rmii_txd_1/

ncsi_rxd_0

L3

mii_mdc

D3

OUT

mii_md

C2

IN /OUT

Pull

Description

OUT

MII MDIO 接口。

2.3.12 TS1588 Pins

Name

Location

Direction

n0_ts1588_sdp_0

T2

IN/OUT

n0_ts1588_sdp_1

L5

IN/OUT

n0_ts1588_sdp_2

V1

IN/OUT

n0_ts1588_sdp_3

M3

IN/OUT

n1_ts1588_sdp_0

V2

IN/OUT

n1_ts1588_sdp_1

M4

IN/OUT

n1_ts1588_sdp_2

U2

IN/OUT

n1_ts1588_sdp_3

P3

IN/OUT

n2_ts1588_sdp_0

U3

IN/OUT

n2_ts1588_sdp_1

N4

IN/OUT

n2_ts1588_sdp_2

W2

IN/OUT

n2_ts1588_sdp_3

M5

IN/OUT

n3_ts1588_sdp_0

R3

IN/OUT

n3_ts1588_sdp_1

R4

IN/OUT

n3_ts1588_sdp_2

T3

IN/OUT

n3_ts1588_sdp_3

N5

IN/OUT

Pull

Description

网口#0 TS1588 GPIO,结合芯片定时器,用于

产生可配置时钟、脉冲、电平、集外部事

件、基于外部事件产生中断。不使用可以悬

空。

网口#1 TS1588 GPIO,结合芯片定时器,用于

产生可配置时钟、脉冲、电平、集外部事

件、基于外部事件产生中断。不使用可以悬

空。

网口#2 TS1588 GPIO,结合芯片定时器,用于

产生可配置时钟、脉冲、电平、集外部事

件、基于外部事件产生中断。不使用可以悬

空。

网口#3 TS1588 GPIO,结合芯片定时器,用于

产生可配置时钟、脉冲、电平、集外部事

件、基于外部事件产生中断。不使用可以悬

空。

2.3.13 PCIe Interface

Name

Location

Direction

Pull

Description

pe_wake_n

E15

OD

Up

PCIe WAKE# 信号,低有效,使用 WOL 功能时

需使能此信号。

pxpor_res

J1

IN

Down

高有效信号,用于复位片内上电复位控制电

路。0-使用片内上电复位,1-使用外部复位。

23

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

使用外部复位时,只用到了 perst_n,按照

PCIe Base Spec, perst_n 在电源稳定后,至少保

持有效 100ms。

por_bypass

G5

IN

Down

perst_n

G3

IN

PCIe PERST#信号,低有效。

pe_phy_resref

C10

A

PCIe PHY 参考电阻,200Ω (1% ,±100 ppm/°C)

pe_ref_clk_p

C8

A-in

PCIe 100MHz 参考时钟,来自 PCIe slot。

pe_ref_clk_n

D8

A-in

pe_tx_p_0

B13

A-out

pe_tx_n_0

A13

A-out

pe_tx_p_1

B8

A-out

pe_tx_n_1

A8

A-out

pe_tx_p_2

B7

A-out

pe_tx_n_2

A7

A-out

pe_tx_p_3

B2

A-out

pe_tx_n_3

A2

A-out

pe_rx_p_0

B11

A-in

pe_rx_n_0

A11

A-in

pe_rx_p_1

B10

A-in

pe_rx_n_1

A10

A-in

pe_rx_p_2

B5

A-in

pe_rx_n_2

A5

A-in

pe_rx_p_3

B4

A-in

pe_rx_n_3

A4

A-in

片内上电复位控制电路旁路使能,高有效。

有效时,片内上电复位控制电路被旁路,片

内不再产生上电复位信号,芯片的上电复位

信号来自 pxpor_res,此时 pxpor_res 作为低

有效信号。

PCIe PHY Gen2x4 差分收发信号

2.3.14 SPI flash Interface

Name

Location

Direction

Pull

spi_clk_div_0

A15

IN

Up

Description

24

�WX1860 Datasheet

Name

Location

Direction

Pull

Description

spi_clk_div_1

E12

IN

Up

用于调试,建议客户采用默认配置。

spi_clk_div_2

B14

IN

Down

spi_clk

B17

OUT

spi_cs_n

D16

OUT

spi_si

C15

IN

spi_so

D17

OUT

SPI flash 接口信号

Down

2.3.15 JTAG

Name

Location

Direction

Pull

Description

jrst_n

B18

IN

Down

JTAG 接口信号

jtck

F15

IN

Down

jtdi

B19

IN

Up

jtdo

D18

OUT

jtms

C16

IN/OUT

Up

2.3.16 Power Supply

管脚名称

管脚

描述

VCC33_N0_EFUSE

C5

VCC33_N1_EFUSE

C4

VCC33_N2_EFUSE

D5

VCC33_N3_EFUSE

C3

VCC33_EFUSE

D4

VCC33A_TDC

C7

内部温度传感器模拟 3.3V

VCC33A_PE_VPH

E8

PCIe 模拟 3.3V

VCC3IO

G7 G11 G12 J7 L7

RGMII、Misc 数字 IO 3.3V

VCC33A_GIGA

N8 N10 N12 N13

MDI 网口模拟 3.3V

VCC33A_CEN

T15

MDI 网口模拟 3.3V

VCCK_VMAIN

E11

内核数字电源 1.1V

EFUSE 模拟 3.3V

25

�WX1860 Datasheet

VCCK_AUX

G10 H7 H13 K7 K13 M7 M13 T7 T9

内核数字备用电源 1.1V

T11 T13

VCC11A_PE_VP

D7 D9

VCC11A_PE_VPTX0 E10

VCC11A_PE_VPTX1 E9

PCIe 模拟电源 1.1V

VCC11A_PE_VPTX2 E7

VCC11A_PE_VPTX3 E6

VCC11A_A10

P7 P9 P11 P13

MDI 网口模拟电源 1.1V

VCC11A_PLL

N2

PLL 电源,模拟 1.1V

VCC11A_CEN

T5

MDI 网口模拟 1.1V

VCC18IO_25V

J13

VCC18IO_25V

L13

RGMII 数字 IO ,目前 1.8V/2.5V 模式不

支持,需接到 3.3V。

2.3.17 Ground

管脚名称

管脚

GND

A1 A3 A6 A9 A12 B1 B3 B6 B9 B12

C9 C11 D6 D10 G8 G9 G13 H8 H9

H10 H11 H12 J8 J9 J10 J11 J12 K8

K9 K10 K11 K12 A19 L8 L9 L10

L11 L12 M8 M9 M10 M11 M12

N7 N9 N11 P4 P5 P8 P10 P12 R5

R15 T4 T6 T8 T10 T12 T14 T16 U4

电源地

U17 W1 W19

GND_PLL

N3

PLL 电源,通过磁珠单点接地,目的是

为了隔离电源模拟地和数字地。

C6

内部 Thermal sensor 电源,通过磁珠单

点接地,目的是为了隔离电源模拟地和

数字地。

GND_TS

描述

2.4 Ball List ordered by Ball location

Pin

A1

A2

Netname

GND_PEPHY_GD

PE_TX_N_3

Description

PCIe 5Gbps SerDes

26

�WX1860 Datasheet

Pin

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

C1

C2

Netname

GND_PEPHY_GD

PE_RX_N_3

PE_RX_N_2

GND_PEPHY_GD

PE_TX_N_2

PE_TX_N_1

GND_PEPHY_GD

PE_RX_N_1

PE_RX_N_0

GND_PEPHY_GD

PE_TX_N_0

UART_SRX

SPI_CLK_DIV_0

N0_GPIO_1

N2_GPIO_1

N3_GPIO_1

GND

GND_PEPHY_GD

PE_TX_P_3

GND_PEPHY_GD

PE_RX_P_3

PE_RX_P_2

GND_PEPHY_GD

PE_TX_P_2

PE_TX_P_1

GND_PEPHY_GD

PE_RX_P_1

PE_RX_P_0

GND_PEPHY_GD

PE_TX_P_0

SPI_CLK_DIV_2

N1_GPIO_1

PE_RST_SEQ

SPI_CLK

JRST_N

JTDI

MNG_BSY

MII_MD

Description

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

UART

SPI clock divider bit[0]

Lan0 GPIO bit[1]

Lan2 GPIO bit[1]

Lan3 GPIO bit[1]

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

PCIe 5Gbps SerDes

SPI clock divider bit[2]

Lan1 GPIO bit[1]

PCIe reset sequence control.

SPI flash clock, max clock frequency is 50MHz

JTAG reset

JTAG TDI

Management busy indication

NCSI PHY MDIO

27

�WX1860 Datasheet

Pin

C3

C4

C5

C6

C7

C8

C9

C10

C11

Netname

VCC33_N3_EFUSE

VCC33_N1_EFUSE

VCC33_N0_EFUSE

GND_TS_GND33A

VCC33A_TDC

PE_REF_CLK_P

GND_PEPHY_GD

PE_PHY_RESREF

GND_PEPHY_GD

C12

PRB_HIT

C13

PRB_CLKOUT

C14

C15

C16

C17

C18

C19

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

MNG_GPIO_1

SPI_SI

JTMS

N0_DIS_N

N2_DIS_N

JTAG_SEL_1

PRB_EN

PCIE_BSY

MII_MDC

VCC33_EFUSE

VCC33_N2_EFUSE

GND_PEPHY_GD

VCC11A_PE_VP

PE_REF_CLK_N

VCC11A_PE_VP

GND_PEPHY_GD

UART_STX

N0_GPIO_0

N2_GPIO_0

MNG_GPIO_0

PE_AUX_PWR_DET

SPI_CS_N

SPI_SO

JTDO

N2_RGMII_TX_0

E1

CLK_TST_SEL_1

Description

PCIe 100MHz reference clock

PCIe reference resistor

Probe hit 用于调试

Probe clock out 用于调试

Managment GPIO bit [1]

SPI flash SI

JTAG JMS

Active low Lan0 disable

Active low Lan2 disable

JTAG select bit[1]

Probe enable, 0 for normal function

PCIe link busy indication

NCSI PHY MDIO

PCIe PHY reference clock

UART

PCIe Aux power available

SPI flash CS_N

SPI flash SO

JTAG JTDO

RGMII interface

Test clock selection, 用于调试 only

28

�WX1860 Datasheet

Description

Pin

Netname

E2

CLK_TST_SEL_3

E3

USE_EXT_PHY

E4

CLK_TST_SEL_0

Test clock selection, 用于调试 only

E5

CLK_TST_SEL_2

Test clock selection, 用于调试 only

E6

E7

E8

E9

E10

E11

E12

E13

E14

E15

E16

E17

E18

E19

F1

F2

F3

F4

F5

F15

F16

F17

F18

F19

G1

G2

G3

G4

VCC11A_PE_VPTX3

VCC11A_PE_VPTX2

VCC33A_PE_VPH

VCC11A_PE_VPTX1

VCC11A_PE_VPTX0

VCCK_VMAIN

SPI_CLK_DIV_1

N1_GPIO_0

N3_GPIO_0

PE_WAKE_N

JTAG_SEL_0

N1_DIS_N

N2_RGMII_TX_1

N2_RGMII_RX_1

TEST_MODE_0

TEST_MODE_2

MNG_DET

TEST_MODE_1

TEST_SEL

JTCK

N3_DIS_N

N3_RGMII_TX_1

N2_RGMII_TX_2

N2_RGMII_RX_2

SEC_DISABLE

SCAN_ENABLE

PERST_N

FLASH_SECTOR

G5

POR_BYPASS

G7

G8

VCC3IO

GND

Test clock selection, 用于调试 only

External PHY selection, 1'b0 to use internal 1000Base-T

PHY, 1'b1 to use external RGMII PHY. It controls all 4 ports.

SPI clock divider control bit[1]

Lan1 GPIO bit[0]

Lan3 GPIO bit[0]

Active low WAKE# on PCIe slot.

JTAG selection bit[0]

Active low Lan1 disable

RGMII interface

RGMII interface

Test mode, 0 for normal function

Test mode, 0 for normal function

Management available, 1 for normal function

Test mode, 0 for normal function

Test selection, 0 for normal function

JTAG TCK

Active low Lan3 disable

RGMII interface

RGMII interface

RGMII interface

1'b1 to disable IPsec and LinkSec

For DFT, 0 for normal function

PERST# at PCIe slot

0 for 64KB, 1 for 256KB

1 to by pass chip internal POR module and use PXPOR_RES

as active low power on reset

29

�WX1860 Datasheet

Pin

G9

G10

G11

G12

G13

G15

G16

G17

G18

G19

H1

H2

H3

H4

H5

H7

H8

H9

H10

H11

H12

H13

H15

H16

H17

H18

H19

Netname

GND

VCCK

VCC3IO

VCC3IO

GND

N3_RGMII_TX_2

N3_RGMII_TX_0

N3_RGMII_TX_3

N2_RGMII_TX_3

N2_RGMII_RX_3

FLASH_BYPASS

SEC_MODE

N1_LED_0

N0_LED_1

N1_LED_2

VCCK

GND

GND

GND

GND

GND

VCCK

N3_RGMII_RX_2

N3_RGMII_RX_0

N3_RGMII_RX_CTL

N2_RGMII_RX_0

N2_RGMII_TXC

J1

PXPOR_RES

J2

J3

J4

J5

J7

J8

J9

J10

J11

N0_LED_2

N2_LED_1

N3_LED_0

N3_LED_2

VCC3IO

GND

GND

GND

GND

Description

RGMII interface

RGMII interface

RGMII interface

RGMII interface

RGMII interface

0 for normal function

1 to enable sec mode

Lan LED

Lan LED

Lan LED

RGMII interface

RGMII interface

RGMII interface

RGMII interface

RGMII interface

Active High reset to reset chip intern POR. When

POR_BYPASS=1, it is the active low power on reset.

Lan LED

Lan LED

Lan LED

Lan LED

30

�WX1860 Datasheet

Pin

J12

J13

J15

J16

J17

J18

J19

K1

K2

K3

K4

K5

K7

K8

K9

K10

K11

K12

K13

K15

K16

K17

K18

K19

L1

L2

L3

L4

L5

L7

L8

L9

L10

L11

L12

L13

L15

L16

Netname

GND

VCC18IO_25V

N3_RGMII_RX_1

N3_RGMII_TXC

N3_RGMII_MDC

N2_RGMII_TX_CTL

N2_RGMII_RXC

N0_LED_0

N1_LED_1

MNG_IC_SMBSUS_N

MNG_IC_CLK

RMII_CSR_DV

VCCK

GND

GND

GND

GND

GND

VCCK

N3_RGMII_RX_3

N3_RGMII_TX_CTL

N3_RGMII_MDIO

N2_RGMII_RX_CTL

N2_RGMII_MDC

N2_LED_2

N3_LED_1

RMII_TXD_1

RMII_TX_EN

N0_TS1588_SDP_1

VCC3IO

GND

GND

GND

GND

GND

VCC18IO_25V

N3_RGMII_RXC

N0_RGMII_TX_1

Description

RGMII interface

RGMII interface

RGMII MDIO for extern PHY control

RGMII interface

RGMII interface

Lan LED

Lan LED

SMbus for management

SMbus for management

NCSI interface

RGMII interface

RGMII interface

RGMII MDIO for extern PHY control

RGMII interface

RGMII MDIO for extern PHY control

Lan LED

Lan LED

NCSI interface

NCSI interface

TS1588 GPIO

RGMII interface

RGMII interface

31

�WX1860 Datasheet

Pin

L17

L18

L19

M1

M2

M3

M4

M5

M7

M8

M9

M10

M11

M12

M13

M15

M16

M17

M18

M19

N1

N2

N3

N4

N5

N7

N8

N9

N10

N11

N12

N13

N15

N16

N17

N18

N19

P1

Netname

N0_RGMII_TX_0

N1_RGMII_RXC

N2_RGMII_MDIO

N2_LED_0

RMII_RXD_0

N0_TS1588_SDP_3

N1_TS1588_SDP_1

N2_TS1588_SDP_3

VCCK

GND

GND

GND

GND

GND

VCCK

N0_RGMII_RX_1

N0_RGMII_TX_3

N0_RGMII_TX_2

N1_RGMII_MDIO

N1_RGMII_TX_0

MNG_IC_SMBALT_N

VCC11A_PLL

GND11A_PLL

N2_TS1588_SDP_1

N3_TS1588_SDP_3

GND

VCC33A_GIGA

GND

VCC33A_GIGA

GND

VCC33A_GIGA

VCC33A_GIGA

N0_RGMII_RXC

N0_RGMII_TXC

N0_RGMII_RX_0

N1_RGMII_RX_3

N1_RGMII_TX_2

MNG_IC_DATA

Description

RGMII interface

RGMII interface

RGMII MDIO for extern PHY control

Lan LED

NCSI interface

TS1588 GPIO

TS1588 GPIO

TS1588 GPIO

RGMII interface

RGMII interface

RGMII interface

RGMII MDIO for extern PHY control

RGMII interface

SMbus for management

TS1588 GPIO

TS1588 GPIO

RGMII interface

RGMII interface

RGMII interface

RGMII interface

RGMII interface

SMbus for management

32

�WX1860 Datasheet

Pin

P2

P3

P4

P5

P7

P8

P9

P10

P11

P12

P13

P15

P16

P17

P18

P19

R1

R2

R3

R4

R5

R15

R16

R17

R18

R19

T1

T2

T3

T4

T5

T6

T7

T8

T9

T10

T11

T12

Netname

OSC_IO

N1_TS1588_SDP_3

GND

GND

VCC11A_A10

GND

VCC11A_A10

GND

VCC11A_A10

GND

VCC11A_A10

N0_RGMII_MDC

N0_RGMII_RX_2

N0_RGMII_RX_3

N1_RGMII_RX_0

N1_RGMII_TX_1

RMII_REF_CLK

OSC_I

N3_TS1588_SDP_0

N3_TS1588_SDP_1

GND

GND

N0_RGMII_TX_CTL

N0_RGMII_RX_CTL

N1_RGMII_RX_2

N1_RGMII_MDC

RMII_TXD_0

N0_TS1588_SDP_0

N3_TS1588_SDP_2

GND

VCC11A_CEN

GND

VCCK

GND

VCCK

GND

VCCK

GND

Description

External oscillator

TS1588 GPIO

RGMII MDIO for extern PHY control

RGMII interface

RGMII interface

RGMII interface

RGMII interface

NCSI interface

External oscillator

TS1588 GPIO

TS1588 GPIO

RGMII interface

RGMII interface

RGMII interface

RGMII MDIO for extern PHY control

NCSI interface

TS1588 GPIO

TS1588 GPIO

33

�WX1860 Datasheet

Pin

T13

T14

T15

T16

T17

T18

T19

U1

U2

U3

U4

U5

U6

U7

U8

U9

U10

U11

U12

U13

U14

U15

U16

U17

U18

U19

V1

V2

V3

V4

V5

V6

V7

V8

V9

V10

V11

V12

Netname

VCCK

GND

VCC33A_CEN

GND

N0_RGMII_MDIO

N1_RGMII_TX_CTL

N1_RGMII_RX_CTL

RMII_RXD_1

N1_TS1588_SDP_2

N2_TS1588_SDP_0

GND

G0_RTT

N0_GPHY_RSET

G0_OPIN_PAD

G1_RTT

N1_GPHY_RSET

G1_OPIN_PAD

G2_RTT

N2_GPHY_RSET

G2_OPIN_PAD

G3_RTT

N3_GPHY_RSET

G3_OPIN_PAD

GND

N1_RGMII_TXC

N1_RGMII_TX_3

N0_TS1588_SDP_2

N1_TS1588_SDP_0

N0_MDI_P_3

N0_MDI_P_2

N0_MDI_P_1

N0_MDI_P_0

N1_MDI_P_3

N1_MDI_P_2

N1_MDI_P_1

N1_MDI_P_0

N2_MDI_P_3

N2_MDI_P_2

Description

RGMII MDIO for extern PHY control

RGMII interface

RGMII interface

NCSI interface

TS1588 GPIO

TS1588 GPIO

RGMII interface

RGMII interface

TS1588 GPIO

TS1588 GPIO

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

34

�WX1860 Datasheet

Pin

V13

V14

V15

V16

V17

V18

V19

W1

W2

W3

W4

W5

W6

W7

W8

W9

W1

0

W1

1

W1

2

W1

3

W1

4

W1

5

W1

6

W1

7

W1

8

W1

9

Netname

N2_MDI_P_1

N2_MDI_P_0

N3_MDI_P_3

N3_MDI_P_2

N3_MDI_P_1

N3_MDI_P_0

N1_RGMII_RX_1

GND

N2_TS1588_SDP_2

N0_MDI_N_3

N0_MDI_N_2

N0_MDI_N_1

N0_MDI_N_0

N1_MDI_N_3

N1_MDI_N_2

N1_MDI_N_1

N1_MDI_N_0

N2_MDI_N_3

N2_MDI_N_2

N2_MDI_N_1

N2_MDI_N_0

N3_MDI_N_3

N3_MDI_N_2

N3_MDI_N_1

N3_MDI_N_0

Description

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

RGMII interface

TS1588 GPIO

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

1000Base-T serdes

GND

35

�WX1860 Datasheet

3 电气规格

3.1 极限工作条件

参数

Min

存储温度范围

Typ

Max

Units

-65

140

°C

Tj(PN 结温度)

-55

125

°C

VCCK 和 VCC11A

-0.1

1.1

1.155

V

VCC11A_PE,VCC11A_A10,VCC11A_CEN,VCC11A_PLL

-0.1

1.1

1.155

V

VCC3IO,VCC33A,VCC33

-0.4

3.3

3.7

V

VCC18IO_25V

-0.4

3.3

3.7

V

Table1 WX1860 极限工作条件

3.2 建议工作条件

参数

工作温度范围

Min

-40

Typ

Max

85

Units

°C

VCCK 和 VCC11A

VCC11A_PE,VCC11A_A10,VCC11A_CEN,VCC11A_PLL

1.045

1.045

1.1

1.1

1.155

1.155

V

V

VCC3IO,VCC33A,VCC33

3.135

3.3

3.465

V

VCC18IO_25V

3.135

3.3

3.465

V

Table2 WX1860 建议工作条件

3.3 直流特性

参数

IO reference voltage

Symbol

Vref

Conditions

Input low voltage

Input high voltage

Vil

Vih

Input low current

Iil

Vin=0V

Input high current

Iih

Output low voltage

Vol

Output high voltage

Voh

Vin=VrefVref,max

Iol=4mA,Vref=mi

n

I0h=4mA,Vref=min

Min

3.0

Typ

3.3

Max

3.6

Units

V

0.8

V

V

-20

0

µA

0

200

µA

0

400

mV

2.4

Vref

V

2.0

Table2 WX1860 直流特性

36

�WX1860 Datasheet

3.4 交流特性

3.1.1 NCSI AC Specification

The WX1860 is designed to support the standard DMTF NCSI interface. For NCSI I/F timing

specification see the following table.

Symbol

Tckf

Parameter

NCSI_REF_CLK Frequency

Min

Rdc

Racc

NCSI_REF_CLK duty cycle

NCSI_REF_CLK accuracy

35

Tco

Clock-to-out (10 pF =< cload 2.5