ODKMDLVTNF-200.000000 数据手册

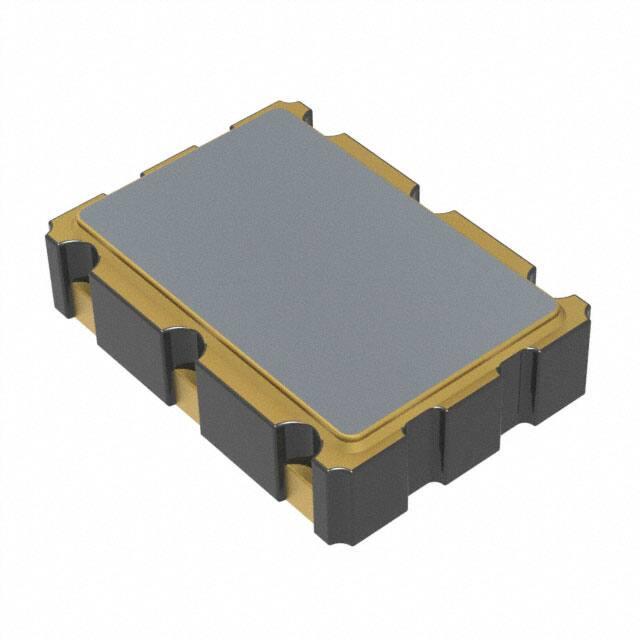

OD-M Type High Frequency and Ultra

Low Noise

7.0 x 5.0mm SMD Crystal Oscillator

Actual Size

FEATURE

- Low Power Supply Voltage: 3.3, 2.5 and 1.8V Supply Options

- Clock Output: LVPECL, LVDS, CML, HCSL and LVCMOS

- Output Frequency Support from 15MHz to 2.1GHz

- Ultra Low Noise, Phase Jitter < 300 fs

(Typical: 150 fs at 12kHz to 20MHz Frequency Offsets)

- Tri-state Enable / Disable Mode.

- Temperature Range: -40 to 85。C

- Pb-free/RoHS Compliant

RoHS Compliant

TYPICAL APPLICATION

- SONET/SDH, Gigabit Ethernet

- SD/HD Video

- Storage Area Networking (SAN)

- FPGA Clock Generation

DIMENSION (mm)

SOLDER PAD L AYOUT (mm)

[ TOP VIEW ]

#1

#2

#7

#8

#3

#3

#2

1.40±0.20

Pin#

0.7

1.70±0.15

[ SIDE VIEW ]

1

2

3

4

5

6

7

8

GND

#1

VDD

0.1µF

6

NC

3.50

#8

5.08

#6

1.3

#7

#5

(LVPECL/LVDS/CML)

1.6

#4

#4

1.00

1.28±0.20

#5

[ TOP VIEW ]

5.7

5.08±0.20

3.46±0.20

5.00±0.20

#6

[ BOTTOM VIEW ]

7.00±0.20

PIN ASSIGNMENTS

CMOS

NC

OE

GND

Output

NC

VDD

NC

NC

5

OUT

4

7

8

1

2

NC

OE

NC

3

GND

(CMOS)

1.18

Functions

LVPECL/LVDS/CML

NC

OE

GND

Output

Comp. Output

VDD

NC

NC

OUT-

1.7

VDD

1.6

To ensure optimal oscillator performance, place

a by-pass capacitor of 0.1μF as close to the part

as possible between Vdd and GND pads.

NC

NC

OUT

6

5

4

1

2

3

NC

OE

7

8

NC

GND

ELECTRICAL SPECIFICATION

Parameter

Supply Voltage Variation (VDD) ±10%

Frequency Range

Standard Frequency

Supply Current

Output Level

Output High

Output Low

Transition Time

(20%-80%)

Rise Time / Fall Time

Duty Cycle

Startup Time

Tri-State Mode (Input to Pin 2)

Standby Current

Phase Noise

Enable

Disable

100kHz offset

1MHz offset

20MHz offset

RMS Phase Jitter (12kHz to 20MHz)

Period Jitter

LVPECL

Max.

Min.

2.5V

unit

Max.

VDD-10%

VDD+10%

VDD-10%

VDD+10%

15

2100

15

2100

100, 106.25, 125, 156.25, 187.5, 200, 212.5, 266, 300, 312.5, 400

_

_

110

95

VDD-1.165

VDD-0.8

VDD-1.165

VDD-0.8

VDD-2.0

VDD-1.55

VDD-2.0

VDD-1.55

V

MHz

mA

V

_

0.35

_

0.35

nSec

45

_

55

8

_

45

_

55

8

_

%

mSec

0.7 x VDD

_

_

Typ.

1kHz offset

10kHz offset

At VDD=3.3V, Fout=873.515MHz

Min.

3.3V

-106

-115

-123

-133

-150

150

_

0.3 x VDD

110

Max.

_

_

_

_

_

300

50

0.7 x VDD

_

_

Typ.

-106

-115

-123

-133

-150

150

_

0.3 x VDD

95

Max.

_

_

_

_

_

300

50

V

mA

dBc/Hz

fs

ps

Note: not all combination of options are available. Other specifications may be available upon request.

66

www.taitien.com

sales@taitien.com.tw

XO-0157

Rev(6) 01/2023

�Parameter

Supply Voltage Variation (VDD) ±5%

Supply Voltage Variation (VDD) ±10%

Frequency Range

Standard Frequency

Supply Current

Output Level

Output High

Output Low

Transition Time

(20%-80%)

Rise Time / Fall Time

Min.

_

Max.

_

3.63

15

2.97

2100

_

0.9

_

0.35

45

_

55

8

_

0.7 x VDD

_

_

Enable

Disable

Standby Current

Phase Noise

0.3 x VDD

90

Max.

_

_

_

_

_

Typ.

-106

-115

-123

-133

-150

1kHz offset

10kHz offset

At VDD=3.3V, Fout=873.515MHz

100kHz offset

1MHz offset

10MHz offset

RMS Phase Jitter (12kHz to 20MHz)

150

_

Period Jitter

_

0.35

45

_

55

8

_

0.7 x VDD

_

_

Output High

Output Low

Transition Time

(20%-80%)

Rise Time / Fall Time

Duty Cycle

Startup Time

Max.

_

3.63

15

2.97

2100

Standby Current

Phase Noise

100kHz offset

1MHz offset

10MHz offset

RMS Phase Jitter (12kHz to 20MHz)

Period Jitter

Parameter

Typ.

150

_

300

50

Supply Voltage Variation (VDD)±10%

Frequency Range

Supply Current

Output High

Output Level

Output Low

Transition Time Rise Time

(20% - 80%)

Fall Time

Duty Cycle

Startup Time

Tri-State mode Enable

(Input to Pin 2) Disable

Stand by Current Disable

Output Load

Phase Noise

1kHz offset

10kHz offset

At VDD=3.3V,

fout=

100kHz offset

873.515MHz

1MHz offset

10MHz offset

RMS Phase Jitter (12KHz to 20MHz)

Period Jitter

Min.

_

45

0.7 x VDD

-

1.89

_

15

2100

2.75

2100

V

MHz

70

1.6

_

mA

_

0.35

nSec

45

_

55

8

_

%

mSec

0.7 x VDD

_

_

0.3 x VDD

70

Max.

_

_

_

_

_

Typ.

-106

-115

-123

-133

-150

150

_

V

V

mA

dBc/Hz

300

fs

50

ps

1.8V

Max.

_

2.25

15

unit

Min.

Max.

1.71

_

1.89

_

15

2100

V

MHz

mA

V

_

0.35

_

0.35

_

0.35

nSec

55

8

_

45

_

55

8

_

45

_

55

8

_

%

mSec

0.3 x VDD

90

Max.

_

_

_

_

_

-107

-117

-125

-135

-150

150

_

0.7 x VDD

_

_

0.3 x VDD

80

Max.

_

_

_

_

_

Typ.

-107

-117

-125

-135

-150

300

150

_

50

300

50

0.7 x VDD

_

_

Typ.

-107

-117

-125

-135

-150

150

_

HCSL

2.5V

3.3V

Min.

3.63

15

15

0.66

0

-

1.71

_

45

_

Typ.

1kHz offset

10kHz offset

Max.

100, 106.25, 125, 156.25, 187.5, 200, 212.5, 266, 300, 312.5, 400

_

_

90

80

70

VDD

VDD-0.085

VDD

VDD-0.085

VDD

VDD-0.32

VDD-0.6

VDD-0.32

VDD-0.6

VDD-0.32

0.7 x VDD

_

_

Enable

Disable

unit

Min.

CML

2.5V

Min.

_

_

0.3 x VDD

80

Max.

_

_

_

_

_

-106

-115

-123

-133

-150

50

VDD-0.085

VDD-0.6

Output Level

At VDD=3.3V, Fout=873.515MHz

2.75

2100

3.3V

Supply Voltage Variation (VDD) ±5%

Supply Voltage Variation (VDD) ±10%

Frequency Range

Standard Frequency

Supply Current

1.8V

Max.

_

2.25

15

300

Parameter

Tri-State Mode (Input to Pin 2)

Min.

_

100, 106.25, 125, 156.25, 187.5, 200, 212.5, 266, 300, 312.5, 400

_

_

90

80

_

_

1.6

1.6

_

_

0.9

0.9

_

Duty Cycle

Startup Time

Tri-State Mode (Input to Pin 2)

LVDS

2.5V

3.3V

Max.

2.97

700

115

700

1.15

0.15

0.4

0.4

55

8

0.3 x VDD

Min

2.25

15

15

0.66

0

-

0.3 x VDD

70

Max.

_

_

_

_

_

fs

50

ps

Unit

Min.

1.71

15

15

0.66

0

45

0.7xVDD

-

Max.

1.89

700

94

2100

1.15

0.15

0.4

0.4

55

8

0.3 x VDD

94

115

0.7x VDD

-

Typ.

Max.

Typ.

Max.

Typ.

Max.

-87

-110

-127

-138

-153

150

-

300

50

-87

-110

-127

-138

-153

150

-

300

50

-87

-110

-127

-138

-153

150

-

300

50

100

50 ohms to GND

dBc/Hz

300

1.8V

Max.

2.75

700

100

2100

1.15

0.15

0.4

0.4

55

8

0.3 x VDD

V

mA

V

MHz

mA

V

V

nSec

nSec

%

mSec

V

V

mA

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

dBc/Hz

fs

ps

Note: not all combination of options are available. Other specifications may be available upon request.

www.taitien.com

sales@taitien.com.tw

XO-0157

Rev(6) 01/2023

67

�Parameter

Supply Voltage Variation (VDD) ±5%

Supply Voltage Variation (VDD) ±10%

Frequency Range

Supply Current

Output Level

Min.

_

Max.

_

3.63

15

_

2.97

250

90

_

0.9 x VDD

_

Output High

Output Low

Transition Time

(20%-80%)

Rise Time / Fall Time

Duty Cycle

Fout 100MHZ

Startup Time

Tri-State Mode (Input to Pin 2)

CMOS

2.5V

3.3V

Enable

Disable

Period Jitter

_

45

40

_

0.7 x VDD

_

_

0.1 x VDD

Min.

_

2.25

15

0.9 x VDD

_

1.2

_

55

60

8

_

45

40

_

0.3 x VDD

100

0.7 x VDD

_

_

1.8V

Max.

_

2.75

250

80

_

0.1 x VDD

unit

Min.

Max.

1.71

_

1.89

_

15

250

70

_

0.9 x VDD

_

0.1 x VDD

1.5

_

2

55

60

8

_

45

40

_

55

60

8

_

0.3 x VDD

100

0.7 x VDD

_

_

V

MHz

mA

V

nSec

%

mSec

0.3 x VDD

100

V

mA

FREQ. STABILITY vs. TEMP. RANGE

Temp. (°C)

ppm

±20

-20~+70

-40~+85

X

±25

±30

±50

*

○: Available △:Conditional X: Not available

* Inclusive of calibration @ 25 °C, operating temperature range, input

voltage variation, load variation, aging (1st year), shock, and vibration

Note: not all combination of options are available. Other specifications may be available upon request.

68

www.taitien.com

sales@taitien.com.tw

XO-0157

Rev(6) 01/2023

�

ODKMDLVTNF-200.000000 价格&库存

很抱歉,暂时无法提供与“ODKMDLVTNF-200.000000”相匹配的价格&库存,您可以联系我们找货

免费人工找货