Product

Folder

Order

Now

Support &

Community

Tools &

Software

Technical

Documents

TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

TPS7A6x-Q1 300-mA, 40-V Low-Dropout Regulator With 25-µA Quiescent Current

1 Features

2 Applications

•

•

•

•

•

Qualified for Automotive Applications

AEC-Q100 Test Guidance With the Following

Results:

– Device Temperature Grade 1: –40°C to 125°C

Ambient Operating Temperature

– Device HBM ESD Classification Level H3A

– Device CDM ESD Classification Level C6

Low Dropout Voltage

– 300 mV at IOUT = 150 mA

11-V to 40-V Wide Input Voltage Range With up

to 45-V Transients

300-mA Maximum Output Current

Ultralow Quiescent Current

– IQUIESCENT = 25 µA (Typical) at Light Loads

– ISLEEP < 2 µA When ENABLE = Low

3.3-V and 5-V Fixed Output Voltage

Low-ESR Ceramic Output Stability Capacitor

Integrated Power-On Reset

– Programmable Delay

– Open-Drain Reset Output

Integrated Fault Protection

– Short-Circuit and Overcurrent Protection

– Thermal Shutdown

Low-Input-Voltage Tracking

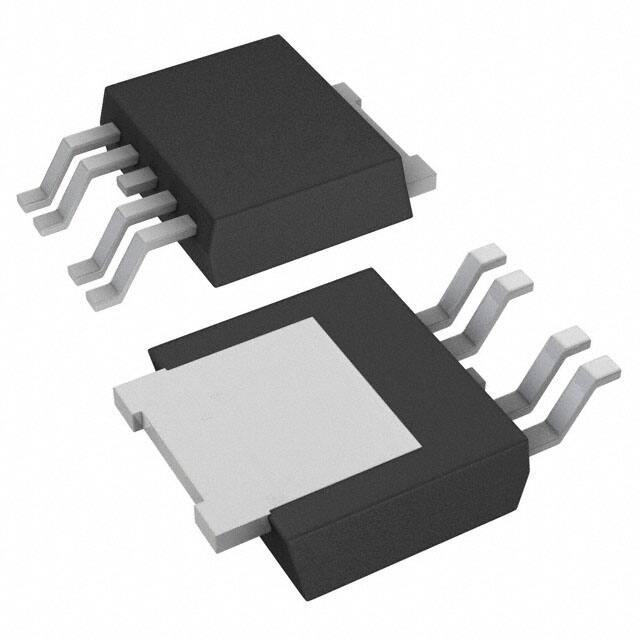

Thermally Enhanced Power Package

– 5-pin TO-263 (KTT, D2PAK)

– 5-pin TO-252 (KVU, DPAK)

1

•

•

•

•

•

•

•

•

•

•

Infotainment Systems With Sleep Mode

Body Control Modules

Always-On Battery Applications

– Gateway Applications

– Remote Keyless Entry Systems

– Immobilizers

3 Description

The TPS7A60-Q1 and TPS7A61-Q1 comprise a

family of low-dropout linear voltage regulators

designed for low power consumption and quiescent

current less than 25 µA in light-load applications.

These devices feature integrated overcurrent

protection and are designed to achieve stable

operation even with low-ESR ceramic capacitors.

Power-on-reset delay is implemented during device

start-up to indicate that the output voltage is stable

and in regulation. The power-on-reset delay is fixed

(250 µs typical), and can also be programmed by an

external capacitor. A low-voltage tracking feature

allows for a smaller input capacitor and can possibly

eliminate the need of using a boost converter during

cold-crank conditions. Because of these features,

these devices are well-suited in power supplies for

various automotive applications.

Device Information(1)

PART NUMBER

PACKAGE

BODY SIZE (NOM)

TO-263 (5)

10.16 mm × 9.15 mm

TO-252 (5)

6.10 mm × 6.60 mm

TO-263 (5)

10.16 mm × 9.15 mm

TO-252 (5)

6.10 mm × 6.60 mm

TPS7A6133-Q1

TO-252 (5)

6.10 mm × 6.60 mm

TPS7A6150-Q1

TO-252 (5)

6.10 mm × 6.60 mm

TPS7A6033-Q1

TPS7A6050-Q1

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Programmable Reset Delay Option

Enable Option

TPS7A61-Q1

TPS7A60-Q1

VIN

VIN

VOUT

COUT

VOUT

VIN

CIN

VIN

VOUT

VOUT

COUT

CIN

VIN

RRST

RDELAY

ENABLE

RRST

CDLY

GND

nRST

RESET

GND

nRST

RESET

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

Table of Contents

1

2

3

4

5

6

7

8

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Device Comparison Table.....................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

5

7.1

7.2

7.3

7.4

7.5

7.6

7.7

5

5

5

5

6

7

8

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Switching Characteristics ..........................................

Typical Characteristics ..............................................

8.3 Feature Description................................................. 12

8.4 Device Functional Modes........................................ 16

9

9.1 Application Information............................................ 17

9.2 Typical Applications ................................................ 17

10 Power Supply Recommendations ..................... 21

11 Layout................................................................... 21

11.1 Layout Guidelines ................................................. 21

11.2 Layout Examples................................................... 24

12 Device and Documentation Support ................. 26

12.1

12.2

12.3

12.4

12.5

12.6

Detailed Description ............................................ 11

8.1 Overview ................................................................. 11

8.2 Functional Block Diagrams ..................................... 11

Application and Implementation ........................ 17

Related Links ........................................................

Receiving Notification of Documentation Updates

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

26

26

26

26

26

26

13 Mechanical, Packaging, and Orderable

Information ........................................................... 26

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision H (March 2016) to Revision I

Page

•

Changed device names from TPS7A6033-Q1, TPS7A6050-Q1, TPS7A6133-Q1, and TPS7A6150-Q1 to TPS7A60Q1 and TPS7A61-Q1 ............................................................................................................................................................. 1

•

Changed 4 V to 11 V in fourth Features bullet ...................................................................................................................... 1

•

Changed VIN minimum specification from 4 V to 11 V in Recommended Operating Conditions table .................................. 5

•

Changed VIN and VENABLE parameters to be separate rows, changed VENABLE description to Enable pin voltage ................ 5

•

Changed VIN parameter: condensed test conditions to one row and changed minimum specification from 5.3 V to 11 V ... 6

•

Changed 4 V (3.3-V version) or 5.3 V (5-V version) to 11 V in Regulation Mode section .................................................. 16

•

Changed Input voltage range parameter example value in TPS7A60-Q1 Design Parameters table .................................. 17

•

Changed Input voltage range parameter example value in TPS7A61-Q1 Design Parameters table ................................. 19

Changes from Revision G (April 2012) to Revision H

Page

•

Added new bullets to top of Features list ............................................................................................................................... 1

•

Appended "-Q1" to the part number in numerous locations throughout the data sheet......................................................... 1

•

Added ESD Rating table, Switching Characteristics tableFeature Description section, Device Functional Modes,

Application and Implementation section, Power Supply Recommendations section, Layoutsection, Device and

Documentation Support section, and Mechanical, Packaging, and Orderable Information section....................................... 1

•

Added MIN values for VIN, RDELAY, and VOUT in Absolute Maximum Ratings table......................................................... 5

•

Deleted two graphs from the Typical Characteristics section................................................................................................. 8

•

Updated Typical Application Schematic for the TPS7A61xx-Q1 Device image. ................................................................. 19

2

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

5 Device Comparison Table

PART NUMBER

OUTPUT VOLTAGE

TPS7A6033-Q1

3.3 V

ENABLE

RESET

PROGRAMMABLE RESET

DELAY

No

Yes

Yes

No

Yes

Yes

No

Yes

Yes

No

Yes

Yes

TPS7A6050-Q1

5V

TPS7A6133-Q1

3.3 V

Yes

Yes

No

TPS7A6150-Q1

5V

Yes

Yes

No

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

3

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

6 Pin Configuration and Functions

2

3

4

5

nRST

GND

ENABLE, RDELAY

VOUT

5

VOUT

1

4

ENABLE, RDELAY

VIN

3

GND

Pad

2

Thermal

Pad

nRST

Thermal

1

KVU Package

5-Pin TO-252 With Exposed Thermal Pad

Top View

VIN

KTT Package

5-Pin TO-263 With Exposed Thermal Pad

Top View

Pin Functions

PIN

NAME

NO.

TYPE

DESCRIPTION

Enable pin (for TPS7A61-Q1 only): This is a high-voltage-tolerant input pin with an internal pulldown. A high

input to this pin activates the device and turns the regulator ON. This input can be connected to the VIN pin

for self-bias applications. If this pin is not connected, the device stays disabled.

ENABLE

4

I

GND

3

I/O

Ground pin: This is the signal-ground pin of the IC.

nRST

2

O

Reset pin: This is an output pin with an external pullup resistor connected to the VOUT pin.

RDELAY

4

O

Reset delay timer pin (for TPS7A60-Q1 only): This pin is used to program the reset delay timer using an

external capacitor (CDLY) to ground.

VIN

1

I

Input voltage pin: The unregulated input voltage is supplied to this pin. A bypass capacitor is connected

between the VIN pin and the GND pin to dampen input line transients.

VOUT

5

O

Regulated output-voltage pin: This is a regulated voltage output (VOUT = 3.3 V or 5 V, as applicable) pin with

a limitation on maximum output current. In order to achieve stable operation and prevent oscillation, an

external output capacitor (COUT) with low ESR is connected between this pin and the GND pin.

4

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

MIN

MAX

UNIT

Unregulated inputs (2)

VIN, ENABLE

–0.3

45

V

Regulated output

VOUT

–0.3

7

V

Open-drain reset output

nRST

–0.3

7

V

Output to charge an external capacitor

RDELAY

–0.3

7

V

Operating ambient temperature, TJ

–40

150

°C

Storage temperature, Tstg

–65

150

°C

(1)

(2)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Absolute maximum voltage for duration less than 480 ms

7.2 ESD Ratings

VALUE

UNIT

TPS7A60-Q1 and TPS7A61-Q1 Devices in KVU Package

V(ESD)

Electrostatic discharge

Human-body model (HBM), per AEC Q100-002 (1)

±4000

Charged-device model (CDM), per AEC Q100-011

±1000

Human-body model (HBM), per AEC Q100-002 (1)

±4000

Charged-device model (CDM), per AEC Q100-011

±1500

V

TPS7A60-Q1 Device in KTT Package

V(ESD)

(1)

Electrostatic discharge

V

AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

MIN

MAX

11

40

V

Enable pin voltage (1)

4

40

V

VnRST, VRDELAY

Low-voltage output range (2)

0

5.25

V

IOUT

Output current

0

300

mA

TA

Operating ambient temperature

–40

150

°C

VIN

Unregulated input voltage

VENABLE

(1)

(2)

UNIT

Applicable for the TPS7A61-Q1 only.

Applicable for the TPS7A60-Q1 only.

7.4 Thermal Information

THERMAL METRIC (1) (2)

TPS7A60-Q1,

TPS7A61-Q1

TPS7A60-Q1

KVU (TO-252)

KTT (TO-263)

5 PINS

5 PINS

UNIT

RθJA

Junction-to-ambient thermal resistance

26.9

24.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

32.2

38.9

°C/W

RθJB

Junction-to-board thermal resistance

6.5

7.4

°C/W

ψJT

Junction-to-top characterization parameter

2.5

3.8

°C/W

ψJB

Junction-to-board characterization parameter

6.5

7.4

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.8

1.5

°C/W

(1)

(2)

The thermal data is based on JEDEC standard high K profile JESD 51-5. The copper pad is soldered to the thermal land pattern. The

correct attachment procedure must be incorporated.

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

5

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

7.5 Electrical Characteristics

VIN = 14 V, TJ = –40°C to 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

INPUT VOLTAGE (VIN PIN)

VIN

Input voltage

Fixed 5-V or 3.3-V output, IOUT = 1 mA

IQUIESCENT

Quiescent current

VIN = 8.2 V to 18 V, VENABLE (1) = 5 V,

IOUT = 0.01 mA to 0.75 mA

11

ISLEEP (1)

Sleep or shutdown current

VIN = 8.2 V to 18 V, VENABLE (1) < 0.8 V,

IOUT = 0 mA (no load), TA = 125°C

VIN-UVLO

Undervoltage lockout voltage

Ramp VINdown until output is turned OFF

3.16

V

VIN(POWERUP)

Power-up voltage

Ramp VINup until output is turned ON

3.45

V

25

40

V

40

µA

3

µA

ENABLE INPUT (ENABLE PIN)

VIL (1)

Logic input low level

VIH (1)

Logic input high level

0

0.8

V

2.5

40

V

–2%

2%

REGULATED OUTPUT VOLTAGE (VOUT PIN)

VOUT

Regulated output voltage

∆VLINE-REG

Line regulation

∆VLOAD-REG

Load regulation

Fixed VOUT value (3.3 V or 5 V as applicable),

IOUT = 10 mA to 300 mA, VIN= VOUT + 1 V to 16 V

VIN = 6 V to 28 V, IOUT = 10 mA, VOUT = 5 V

15

mV

VIN = 6 V to 28 V, IOUT = 10 mA, VOUT = 3.3 V

20

mV

IOUT = 10 mA to 300 mA, VIN= 14 V, VOUT = 5 V

25

mV

IOUT = 10 mA to 300 mA, VIN = 14 V, VOUT = 3.3 V

35

mV

500

mV

IOUT = 150 mA

300

mV

VDROPOUT (2)

Dropout voltage

(VIN – VOUT)

IOUT = 250 mA

RSW

Switch resistance

VIN to VOUT resistance

ICL

Output current limit

VOUT = 0 V (VOUT pin is shorted to ground)

PSRR

Power supply ripple rejection

2

350

1000

VIN-RIPPLE = 0.5 Vpp, IOUT = 300 mA,

frequency = 100 Hz, VOUT = 5 V and VOUT = 3.3 V

60

VIN-RIPPLE = 0.5 Vpp, IOUT = 300 mA,

frequency = 150 kHz, VOUT = 5 V and VOUT = 3.3 V

30

Ω

mA

dB

RESET (nRST PIN)

VOL

Reset pulled low

IOL = 5 mA

IOH

Leakage current

Reset pulled to VOUT through 5-kΩ resistor

VTH(POR)

UVTHRES

(1)

(2)

6

Power-on-reset threshold

Reset threshold

VOUT power up above internally set tolerance,

VOUT = 5 V

4.5

VOUT falling below internally set tolerance,

VOUT = 3.3 V

V

1

µA

4.77

V

VOUT power up above internally set tolerance,

VOUT = 3.3 V

VOUT falling below internally set tolerance,

VOUT = 5 V

4.65

0.4

3.07

4.5

4.65

4.77

V

3.07

Applicable for the TPS7A61-Q1 only.

This test is done with VOUT in regulation and VIN – VOUT parameter is measured when VOUT (3.3 V or 5 V) drops by 100 mV at specified

loads.

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

Electrical Characteristics (continued)

VIN = 14 V, TJ = –40°C to 150°C (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

3

3.3

V

1

1.25

µA

RESET DELAY (RDELAY PIN)

VTH(RDELAY) (3)

Threshold to release nRST

high

IDLY (3)

Delay capacitor charging

current

IOL (3)

Delay capacitor discharging

current

Voltage at RDELAY pin is ramped up.

0.75

Voltage at RDELAY pin = 1 V

5

mA

OPERATING TEMPERATURE RANGE

TJ

Operating junction

temperature

TSHUTDOWN

Thermal shutdown trip point

THYST

Thermal shutdown hysteresis

(3)

–40

150

ºC

165

ºC

10

ºC

Applicable for the TPS7A60-Q1 only.

7.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

RESET (nRST PIN)

tPOR

Power-on-reset delay

tPOR-PRESET

Internally preset power-onreset delay

tDEGLITCH

Reset deglitch time

CDLY = 100 pF

300

µs

CDLY = 100 nF

300

ms

CDLY not connected in TPS7A60xx or not available

in TPS7A61xx, VOUT = 5 V and VOUT = 3.3 V

250

µs

5.5

µs

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

7

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

7.7 Typical Characteristics

80

55

VIN = 14V

TA = 25°C

VOUT = 5V, 3.3V

70

50

40

30

35

30

25

10

20

0.01

0.1

1

IOUT (mA)

10

100

IOUT = 250mA

40

20

0

0.001

15

1000

IOUT = 1mA

-50

50

T A (°C)

100

0.4

700

VOUT = 5V, 3.3V

600

V OUT = 5V

0.3

VDROP OUT (V)

500

400

300

150

0.35

TA= 25°C

IOUT = 100mA

T A = 125°C

0.25

T A = 25°C

0.2

T A = -40°C

0.15

0.1

200

No Load

100

0.05

0

4

14

24

V IN (V)

34

0

40

Figure 3. Quiescent Current vs Input Voltage

5.1

50

100

150

IOUT (mA)

Figure 4. Dropout Voltage

200

(1)

6

VIN = 14V

5.08

IOUT = 1mA

5.04

250

300

vs Load Current

IOUT = 100mA

TA = 25°C

5

5.06

4

5.02

VOUT (V)

VOUT (V)

0

Figure 2. Quiescent Current vs Ambient Air Temperature

Figure 1. Quiescent Current vs Load Current

I QUIESCENT (µA)

VOUT =5V, 3.3V

45

IQUIESCENT (µA)

I QUIESCENT (µA)

60

0

VIN =14V

50

5

4.98

3

2

4.96

4.94

1

4.92

4.9

-50

0

50

TA (°C)

100

150

8

2

3

4

5

6

7

V IN (V)

Figure 5. Output Voltage vs Ambient Air Temperature

(1)

0

Figure 6. Output Voltage vs Input Voltage

Dropout voltage is measured when the output voltage drops by 100 mV from the regulated output voltage level. (For example, dropout

voltage for the TPS7A6050-Q1 is measured when the output voltage drops down to 4.9 V from 5 V.)

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

Typical Characteristics (continued)

0.12

0.1

0.08

650

TA= 125°C

TA = 25°C

0.06

TA = -40°C

0.04

500

450

-50

0

VIN (V)

50

TA (°C)

Figure 7. Output Voltage vs Input Voltage

Figure 8. Output Current Limit vs Ambient Air Temperature

10

20

30

12

40

50

11.5

11

10

9.5

9

100

150

IOUT = 10mA

VOUT = 5V, 3.3V

VIN step from

8V to 28V

2.5

10.5

2

1.5

1

0.5

8.5

8

-50

0

50

T A (°C)

100

0

-50

150

Figure 9. Load Regulation vs Ambient Air Temperature

120

50

T A (°C)

150

VIN = 14V

IOUT = 1mA

TA = 25°C

COUT = 10µF

VOUT = 5V, 3.3V

100

60

100

Figure 10. Line Regulation vs Ambient Air Temperature

PSRR (dB)

80

0

120

VIN = 14V

IOUT = 250mA

TA = 25°C

COUT = 10µF

VOUT = 5V, 3.3V

100

PSRR (dB)

0

3

VIN = 14V

VOUT = 5V, 3.3V

IOUT step from

10mA to 300mA

Line Regulation (mV)

0

Load Regulation (mV)

600

550

0.02

80

60

40

40

20

20

0

VIN = 14V

VOUT = 5V, 3.3V

700

ICL (mA)

IOUT (A)

750

ILOAD = 100mA

VOUT = 5V, 3.3V

0

10

100

10k

1k

Frequency (Hz)

100k

1M

Figure 11. PSRR at Heavy Load Current

10

100

10k

1k

Frequency (Hz)

100k

1M

Figure 12. PSRR at Light Load Current

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

9

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

Typical Characteristics (continued)

10

ESR of COUT (Ω)

VIN = 14V

COUT = 10µF, 47µF

TA = 27°C

VOUT = 5V, 3.3V

1

Stable Operation

Over Entire Region

0.1

0.01

0.01

0.1

1

10

100 300

IOUT (mA)

Figure 13. ESR Stability vs Load Current

for TPS7A60-Q1 and TPS7A61-Q1

10

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

8 Detailed Description

8.1 Overview

The TPS7A60-Q1 and TPS7A61-Q1 devices comprise a family of monolithic low-dropout linear voltage

regulators with integrated reset functionality. These voltage regulators are designed for low power consumption

and quiescent current less than 25 µA in light-load applications. These devices are well-suited in power supplies

for microprocessors and microcontrollers because of an integrated reset delay, also called power-on-reset delay.

These devices are available in two fixed output-voltage (3.3-V and 5-V) versions as follows:

• Programmable reset delay version (TPS7A60-Q1)

• Enable version (TPS7A61-Q1)

8.2 Functional Block Diagrams

VIN

Band Gap

VRef1

VIN

CIN

.

UVLO Comp

With Internal

Reference

Logic

Control

Temperature Sensor

Thermal Shutdown

Q1

VRef1

+

Regulator Error

Amp.

Control

VOUT

VOUT

COUT

Overcurrent

Detection

RDELAY

CDLY

RRST

Voltage

Supervisor With

Reset Delay

Charge

Pump

Oscillator

Q2

RESET

nRST

GND

Figure 14. TPS7A60-Q1 Functional Block Diagram

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

11

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

Functional Block Diagrams (continued)

VIN

Band Gap

VRef1

VIN

CIN

.

UVLO Comp

With Internal

Reference

Logic

Control

VENABLE

Temperature Sensor

Thermal Shutdown

Q1

VRef1

+

Regulator Error

Amp.

Control

VOUT

ENABLE

VOUT

COUT

Overcurrent

Detection

RRST

Voltage

Supervisor With

Reset Delay

Charge

Pump

Oscillator

Q2

RESET

nRST

GND

Figure 15. TPS7A61-Q1 Functional Block Diagram

8.3 Feature Description

The following section describes the features of TPS7A60-Q1 and TPS7A61-Q1 voltage regulators in detail.

8.3.1 Reset Delay and Reset Output

Reset delay is implemented when the device starts up to indicate that output voltage is stable and in regulation,

and also when the output recovers from a negative voltage spike due to a load step or a dip in the input voltage

for a specified duration. The reset-delay timer is initialized when the voltage at the output (VOUT) exceeds 93% of

the regulated output voltage (3.3 V or 5 V, as applicable). The reset output (nRST) is asserted high after the

power-on-reset delay (tPOR) has elapsed. If the regulated output voltage falls below 93% of the set level, nRST is

asserted low after a short de-glitch time of approximately 5.5 µs (typical).

For TPS7A60-Q1 devices, the reset-delay time can be programmed by connecting an external capacitor (CDLY)

to the RDELAY pin. The delay time is given by Equation 1:

´3

C

t POR = DLY -6

1 ´ 10

where

•

•

tPOR = reset delay time in seconds

CDLY = reset delay capacitor value in farads, 100 pF to 100 nF

(1)

In TPS7A61xx devices, there is no RDELAY pin, and the reset-delay time is preset internally (250 µs typical).

12

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

Feature Description (continued)

During power up, the regulator incorporates a protection scheme to limit the current through the pass element

and output capacitor. When the input voltage exceeds a certain threshold (VIN(POWERUP)) level, the output voltage

begins to ramp as shown in Figure 16 and Figure 17. When the output voltage reaches the power-on-reset

threshold (VTH(POR)) level, a constant output current charges an external capacitor (CDLY) to an internal threshold

(VTH(RDELAY)) voltage level. Then, nRST is asserted high and CDLY is discharged through an internal load. This

allows CDLY to charge from approximately 0 V during the next power cycle. If no external capacitor is connected,

the delay time is preset internally. This is shown in Figure 16.

In TPS7A60-Q1 devices, if the CDLY capacitor is not connected to the RDELAY pin, the reset-delay time is set

internally. This is shown in Figure 17.

VIN(POWERUP)

VIN

VTH(POR) = 93% of VOUT

VOUT

VTH(RDELAY)

RDELAY

Programmable

Reset Delay

nRST

Figure 16. Power Up and Reset-Delay Function With the CDLY Capacitor Connected to the RDELAY Pin

for TPS7A60-Q1

VIN(POWERUP)

VIN

VTH(POR) = 93% of VOUT

VOUT

VTH(RDELAY)

Internal

Reset

Delay

250µs

(typ)

nRST

Figure 17. Power Up and Reset Delay Function With the CDLY Capacitor Not Connected or Available in

TPS7A60-Q1 and TPS7A61-Q1, Respectively

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

13

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

Feature Description (continued)

In case of negative transients in the input voltage (VIN), the reset signal is asserted low only if the output (VOUT)

drops and stays below the reset threshold level (VTH(POR)) for more than the de-glitch time (tDEGLITCH). This is

shown in Figure 18.

While nRST is low, if the input voltage returns to the nominal operating voltage, the normal power-up sequence

is followed. nRST is asserted high, only if the output voltage exceeds the reset-threshold voltage (VTH(POR)) and

the reset-delay time (tPOR) has elapsed. This is shown in the shaded region of Figure 18.

VIN

t < tDEGLITCH t > tDEGLITCH

VTH(POR)

UVTHRES

VOUT

VTH(RDELAY)

RDELAY

tPOR

tPOR

tDEGLITCH

tDEGLITCH

nRST

Figure 18. Conditions for Activation of Reset

8.3.2 Charge Pump Operation

Charge Pump State

Charge Pump State

These devices have an internal charge pump which turns on or off depending on the input voltage and the output

current. The charge-pump switching circuitry does not cause conducted emissions to exceed required thresholds

on the input-voltage line. For a given output current, the charge pump stays on at lower input voltages and turns

off at higher input voltages. The charge-pump switching thresholds are hysteretic. Figure 19 and Figure 20 show

typical switching thresholds for the charge pump at light (IOUT < approximately 2 mA) and heavy (IOUT >

approximately 2 mA) loads, respectively.

ON

Hysteresis

OFF

7.8

Hysteresis

OFF

9.2

7.9

9.6

VIN (V)

VIN (V)

Figure 19. Charge Pump Operation at Light Loads

14

ON

Figure 20. Charge Pump Operation at Heavy Loads

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

Feature Description (continued)

8.3.3 Undervoltage Shutdown

These devices have an integrated undervoltage lockout (UVLO) circuit to shut down the output if the input

voltage (VIN) falls below an internally fixed UVLO threshold level (VIN-UVLO). This ensures that the regulator is not

latched into an unknown state during low-input-voltage conditions. The regulator powers up when the input

voltage exceeds the VIN(POWERUP) level.

8.3.4 Low-Voltage Tracking

At low input voltages, the regulator drops out of regulation, and the output voltage tracks the input minus a

voltage based on the load current (IOUT) and switch resistance (RSW). This allows for a smaller input capacitor

and can possibly eliminate the need of using a boost converter during cold-crank conditions.

8.3.5 Integrated Fault Protection

These devices feature integrated fault protection to make them ideal for use in automotive applications. In order

to keep them in a safe area of operation during certain fault conditions, internal current-limit protection and

current-limit foldback are used to limit the maximum output current. This protects them from excessive power

dissipation. For example, during a short-circuit condition on the output, current through the pass element is

limited to ICL to protect the device from excessive power dissipation.

8.3.6 Thermal Shutdown

These devices incorporate a thermal shutdown (TSD) circuit as a protection from overheating. For continuous

normal operation, the junction temperature should not exceed the TSD trip point. If the junction temperature

exceeds the TSD trip point, the output is turned off. When the junction temperature falls below the TSD trip point,

the output is turned on again. This is shown in Figure 21.

VIN = 24 V

IOUT = 300 mA

VOUT = 5 V

Figure 21. Thermal Cycling Waveform for the TPS7A6150-Q1

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

15

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

8.4 Device Functional Modes

8.4.1 Low-Power Mode

At light loads and high input voltages (VIN > approximately 8 V such that charge pump is off), the device operates

in low-power mode and the quiescent current consumption is reduced to 25 µA (typical) as shown in Table 1.

Table 1. Typical Quiescent Current Consumption

IOUT

CHARGE PUMP ON

CHARGE PUMP OFF

IOUT < approximately 2 mA (light load)

250 µA

25 µA (low-power mode)

IOUT > approximately 2 mA (heavy load)

280 µA

70 µA

8.4.2 Sleep Mode (TPS7A61-Q1 Only)

The enable falling edge is 0.8 V (minimum). The device operates in the sleep mode by holding the ENABLE pin

below that voltage, and the quiescent current consumption is reduced to 3 µA (maximum) as shown in Electrical

Characteristics.

8.4.3 Regulation Mode

When the input voltage is above 11 V, with the ENABLE pin pulled higher than 2.5 V, the device operates in

regulation mode and outputs the nominal voltage.

16

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component

specification, and TI does not warrant its accuracy or completeness. TI’s customers are

responsible for determining suitability of components for their purposes. Customers should

validate and test their design implementation to confirm system functionality.

9.1 Application Information

The TPS7A60-Q1 and TPS7A61-Q1 devices are 300-mA low-dropout linear regulators designed for up to 40-V

VIN operation with only 25-µA quiescent current at no load. There are specific EVMs designed for these devices

to enable evaluation of all the functions of the devices. Both the EVM and its user guide are available on the

product folder as well.

9.2 Typical Applications

Figure 22 and Figure 24 show typical application circuits for the TPS7A60-Q1 and TPS7A61-Q1, respectively.

One may use different values of external components, depending on the end application. An application may

require a larger output capacitor during fast load steps in order to prevent reset from occurring. TI recommends a

low-ESR ceramic capacitor with dielectric of type X5R or X7R.

9.2.1 TPS7A60-Q1 Typical Application

TPS7A60-Q1

VIN

VIN

VOUT

VOUT

10 µF

to

22 µF

0.1 µF

0.1 µF

10 µF

1 kΩ

to

5 kΩ

RDELAY

100 pF

to

100 nF

GND

nRST

RESET

Figure 22. Typical Application Schematic for the TPS7A60-Q1 Device

9.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 2.

Table 2. TPS7A60-Q1 Design Parameters

DESIGN PARAMETER

EXAMPLE VALUE

Input voltage range

11 V to 40 V

Output voltage

3.3 V (for TPS7A6033-Q1) or 5 V (for TPS7A6050-Q1)

Output current rating

300 mA

Output capacitor range

10 µF to 47 µF

Output-capacitor ESR range

10 mΩ to 10 Ω

RESET-delay capacitor range

100 pF to 100 nF

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

17

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

9.2.1.2 Detailed Design Procedure

To

•

•

•

•

•

begin the design process, determine the following:

Input voltage range

Output voltage

Output current rating

Input capacitor

Output capacitor

9.2.1.2.1 Input Capacitor

The device requires an input bypass capacitor, the value of which depends on the application. The typical

recommended value for the bypass capacitor is 10 µF. The voltage rating must be greater than the maximum

input voltage.

9.2.1.2.2 Output Capacitor

The device requires an output capacitor to stabilize the output voltage. TI recommends to selecting a capacitor

between 10 µF and 47 µF with ESR range from 10 mΩ to 10 Ω.

9.2.1.3 Application Curve

Figure 23. Power Up (VOUT = 5 V) With 10-ms RESET Delay, 10 ms/div, IL = 20 mA

18

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

9.2.2 TPS7A61-Q1 Typical Application

TPS7A61-Q1

VIN

VIN

VOUT

VOUT

10 µF

to

22 µF

0.1 µF

VENABLE

10 µF

1 kΩ

to

5 kΩ

ENABLE

nRST

GND

0.1 µF

RESET

Figure 24. Typical Application Schematic for the TPS7A61-Q1 Device

9.2.2.1 Design Requirements

For this design example, use the parameters listed in Table 3.

Table 3. TPS7A61-Q1 Design Parameters

DESIGN PARAMETER

EXAMPLE VALUE

Input voltage range

11 V to 40 V

Output voltage

3.3 V (for TPS7A6133-Q1) or 5 V (for TPS7A6150-Q1)

Output current rating

300 mA

Output capacitor range

10 µF to 47 µF

Output-capacitor ESR range

10 mΩ to 10 Ω

9.2.2.2 Detailed Design Procedure

To

•

•

•

•

•

begin the design process, determine the following:

Input voltage range

Output voltage

Output current rating

Input capacitor

Output capacitor

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

19

�TPS7A60-Q1, TPS7A61-Q1

SLVSA62I – MARCH 2010 – REVISED MAY 2018

www.ti.com

9.2.2.3 Application Curve

Figure 25. Power Up (VOUT = 5 V), 10 ms/div, IL = 20 mA

20

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

TPS7A61-Q1

�TPS7A60-Q1, TPS7A61-Q1

www.ti.com

SLVSA62I – MARCH 2010 – REVISED MAY 2018

10 Power Supply Recommendations

Design of the device is for operation from an input voltage supply with a range between 4 V and 40 V. This input

supply must be well regulated. If the input supply is located more than a few inches from the TPS7A60-Q1 or

TPS7A61-Q1 device, TI recommends adding an electrolytic capacitor with a value of 22 µF and a ceramic

bypass capacitor at the input.

11 Layout

11.1 Layout Guidelines

For the LDO power supply, especially these high voltage and large current ones, layout is an important step. If

layout is not carefully designed, the regulator could not deliver enough output current because of the thermal

limitation. To improve the thermal performance of the device, and maximize the current output at high ambient

temperature, it is recommended to spread the thermal pad as large as possible and put enough thermal vias on

the thermal pad. Figure 29 and Figure 30 show an example layout.

11.1.1 Power Dissipation and Thermal Considerations

Power dissipated in the device can be calculated using Equation 2.

PD = I OUT ´ (VIN - VOUT ) + I QUIESCENT ´ VIN

where

•

•

•

•

•

PD = continuous power dissipation

IOUT = output current

VIN = input voltage

VOUT = output voltage

IQUIESCENT = quiescent current

(2)

As IQUIESCENT