DATASHEET

Frequency Timing Generator for Peripherals

9FGP204

VDDRMII

RMII1

RMII0

VDDRGMII

GNDRGMII

RGMII1

RGMII0

SMBCLK

VttPwr_GD/PD#

Output Features:

•

1 - 0.7V current-mode differential CPU pair

•

6 - 50MHz RMII outputs

•

2 - 125MHz RGMII outputs

•

1 - DOT 96MHz output

•

1 - 33.33MHz output

•

1 - 32.768KHz output

•

2 - 25MHz REF outputs

SMBDAT

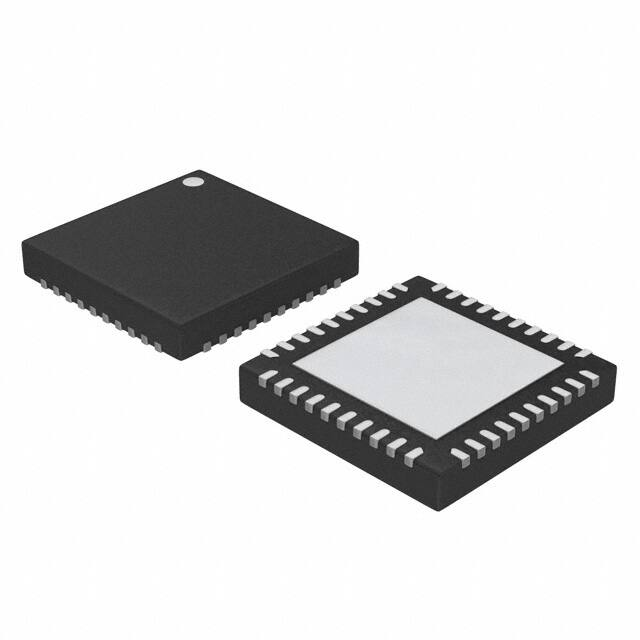

Pin Configuration

Recommended Application:

Peripheral Clock for Intel Server

40 39 38 37 36 35 34 33 32 31

GND

VDD96

DOT96SST

DOT96SSC

OE_96

OE_CPU

CPUCLKT0

CPUCLKC0

VDDCPU

GNDCPU

Key Specifications:

•

Exact synthesis on CPU, RGMII, RMII & 33.33MHz

clocks

•

+/- 100ppm frequency accuracy on other clocks

1

2

3

4

5

6

7

8

9

10

30

29

28

27

26

25

24

23

22

21

9FGP204

GNDRMII

RMII2

RMII3

GNDRMII

VDDRMII

RMII4

RMII5

VDD33

33.33MHZ/**SMBADR

GND33

X2_25

X1_25

GNDREF

25MHZ_1

25MHz_0

VDDREF

GND32K

32.768KHz

IREF

Features/Benefits:

•

Selectable SMBus Address - D0/D1 or C0/C1

•

Spread Spectrum capability on CPU and DOT 96MHz

clocks

•

SMBus Control:

- M/N and spread programming on CPU and DOT

96MHz clocks via SMBus

- Differential outputs can be disabled via pins or SMBus

VDD32K

11 12 13 14 15 16 17 18 19 20

40-VFQFPN

* Internal Pull-Up Resistor

** Internal Pull-Dow n Resistor

Functionality

CPU FS2 CPU FS1 CPU FS0 CPUCLK DOT96SS

MHz

MHz

Byte0 Bit2 Byte0 Bit1 Byte0 Bit0

0

0

0

266.67

96.00

0

0

1

133.33

96.00

0

1

0

200.00

96.00

0

1

1

166.67

96.00

1

0

0

333.33

96.00

1

0

1

100.00

96.00

1

1

0

400.00

96.00

1

1

1

Reserved

96.00

33.33

MHz

33.33

33.33

33.33

33.33

33.33

33.33

33.33

33.33

RMII

MHz

50.00

50.00

50.00

50.00

50.00

50.00

50.00

50.00

RGMII

MHz

125.00

125.00

125.00

125.00

125.00

125.00

125.00

125.00

25

MHz

25.00

25.00

25.00

25.00

25.00

25.00

25.00

25.00

32.768

KHz

32.768

32.768

32.768

32.768

32.768

32.768

32.768

32.768

Power up default is highlighted.

SMBus Address Selection

SMBADR

*SMBADR = 0

D0/D1

SMBADR = 1

C0/C1

* Default value

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

1

�9FGP204

Frequency Timing Generator for Peripherals

Pin Description

1

2

GND

VDD96

PIN

TYPE

PWR

PWR

3

DOT96SST

OUT

4

DOT96SSC

OUT

5

OE_96

IN

6

OE_CPU

IN

7

CPUCLKT0

OUT

8

CPUCLKC0

OUT

9

10

VDDCPU

GNDCPU

PWR

PWR

11

IREF

OUT

12

13

14

15

16

17

18

19

20

21

VDD32K

32.768KHz

GND32K

VDDREF

25MHz_0

25MHZ_1

GNDREF

X1_25

X2_25

GND33

PWR

OUT

PWR

PWR

OUT

OUT

PWR

IN

OUT

PWR

22

33.33MHZ/**SMBADR

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

VDD33

RMII5

RMII4

VDDRMII

GNDRMII

RMII3

RMII2

GNDRMII

VDDRMII

RMII1

RMII0

VDDRGMII

GNDRGMII

RGMII1

RGMII0

SMBCLK

SMBDAT

40

VttPwr_GD/PD#

PIN #

PIN NAME

I/O

PWR

OUT

OUT

PWR

PWR

OUT

OUT

PWR

PWR

OUT

OUT

PWR

PWR

OUT

OUT

IN

I/O

IN

DESCRIPTION

Ground pin.

Power pin for the DOT96 clocks, nominal 3.3V

True clock of differential pair for 96.00MHz spread spectrum capable DOT clock. These are

current mode outputs. External resistors are required for voltage bias.

Complementary clock of differential pair for 96.00MHz spread spectrum capable DOT clock.

These are current mode outputs. External resistors are required for voltage bias.

Active high input for enabling 96Hz outputs.

1 = enable output(s), 0 =disable output(s)

Active high input for enabling CPU DIFF pairs.

1 = enable output(s), 0 =disable output(s)

True clock of differential pair CPU outputs. These are current mode outputs. External resistors

are required for voltage bias.

Complementary clock of differential pair CPU outputs. These are current mode outputs.

External resistors are required for voltage bias.

Supply for CPU clocks, 3.3V nominal

Ground pin for the CPU outputs

This pin establishes the reference for the differential current-mode output pairs. It requires a

fixed precision resistor to ground. 475ohm is the standard value for 100ohm differential

impedance. Other impedances require different values. See data sheet.

Power pin for the 32.768KHz outputs, nominal 3.3V

32.768KHz clock output

Ground pin for the 32.768KHz outputs

Ref, XTAL power supply, nominal 3.3V

25MHz clock output, 3.3V

25MHz clock output, 3.3V

Ground pin for the REF outputs.

Crystal input, Nominally 25.00MHz.

Crystal output.

Ground pin for the 33.33MHz outputs

33.33MHz clock output / SMBus address select bit.

Power pin for the 33.33MHz outputs, nominal 3.3V

3.3V 50MHz RMII clock output

3.3V 50MHz RMII clock output

3.3V power pin for the RMII clocks.

Ground pin for the RMII outputs

3.3V 50MHz RMII clock output

3.3V 50MHz RMII clock output

Ground pin for the RMII outputs

3.3V power pin for the RMII clocks.

3.3V 50MHz RMII clock output

3.3V 50MHz RMII clock output

3.3V power pin for the RGMII clocks and PLL

Ground pin for the RGMII outputs

3.3V 125MHz RGMII clock output

3.3V 125MHz RGMII clock output

Clock pin of SMBUS circuitry, 5V tolerant

Data pin of SMBUS circuitry, 5V tolerant

This 3.3V LVTTL input is a level sensitive strobe used to determine when latch inputs are valid

and are ready to be sampled. This is an active high input. / Asynchronous active low input pin

used to power down the device into a low power state.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

2

�9FGP204

Frequency Timing Generator for Peripherals

General Description

The 9FGP204 is a peripheral clock for Intel Servers. It is driven with a 25MHz crystal and generates a variety of clocks,

including 125MHz RGMII. An SMBus interface allows full control of the device.

Block Diagram

25MHz(1:0)

X1_25

X2_25

XTAL

VttPwr_GD/PD#

CPU PLL

(SPREAD

CAPABLE)

CPUCLK

DOT PLL

(SPREAD

CAPABLE)

DOT96SS

OE_CPU

OE_96

CONTROL

LOGIC

33.33MHz

FIXED

PLL

DIVIDERS

2

RGMII(1:0)

6

RMII(5:0)

SMBADR

SMBDAT

SMBCLK

DIVIDERS

32.768KHz

Power Supply Pins

Pin Number

Description

VDD

GND

9

10

CPUCLK output and PLL

2

1

DOT96SS output and PLL

34

35

125 MHz RGMII outputs and PLL

26,31

27,30

50 MHz RMII outputs

23

21

33.33MHz output

12

14

32.768KHz output

15

18

XTAL, REF outputs

Note: All VDD should be connected to a common power rail with proper

filtering and decoupling. Pins 2, 9 and 34 should be treated as analog pins for

decoupling purposes.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

3

�9FGP204

Frequency Timing Generator for Peripherals

ICS9FGP202A

ICS9FGP204

Zo

Rs

CL=5pF

Test Load

SEPP Output Buffer

(Single Ended

Push Pull)

L1

Zo

Rs

CL=5pF

L2

Zo

Rs

SEPP Output Buffer

(Single Ended

Push Pull)

CL=5pF

NOTE: L1 must equal L2 +/- 25 mils

Drive Strength for all the single-ended outputs can be controlled by the SMBus Bytes 4 and 5 as shown in the Default Drive Strength Table.

Default Drive Strength Table

Default Drive

RGMII

1 Load

RMII

1 Load

33.33MHz

2 Loads

25Mhz

2 Loads

32.768KHz

2 Loads

Series Termination Resistor Values EXCEPT RGMII

Series Resistor Series Resistor

Output Drive (Rs) for driving 1 (Rs) for driving 2

Load

Loads

Strength

1 Load

22 ohms

N/A

2 Loads

33 ohms

8.2 ohms

Note: All values are for Zo = 50Ω

Series Termination Resistor Values - RGMII

Series Resistor Series Resistor

(Rs)

for driving 1 (Rs) for driving 2

Output Drive

Load

Loads

Strength

1 Load

27 ohms

N/A

Note: All values are for Zo = 50Ω

Optional Drive

NA

2 Loads

1 Load

1 Load

1 Load

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

4

�9FGP204

Frequency Timing Generator for Peripherals

Truth Table 1: VttPwr_GD/PD# and OE_96

VttPwr_GD/PD#

OE_96

Clocks

Pin 40

Pin 5

0

0

All clocks are powered down

0

1

All clocks are powered down

1

0

All clocks are enabled except DOT96SS

1

1

*All clocks are enabled including DOT96SS

*Assuming DOT96 Output Enable from SMBus Byte2 Bit0 sets to enable (default)

Truth Table 2: VttPwr_GD/PD# and OE_CPU

VttPwr_GD/PD#

OE_CPU

Clocks

Pin 40

Pin 6

0

0

All clocks are powered down

0

1

All clocks are powered down

1

0

All clocks are enabled except CPUCLK

1

1

*All clocks are enabled including CPUCLK

*Assuming CPUCLK Output Enable from SMBus Byte2 Bit1 sets to enable (default)

Table 1: CPU Spread and Frequency Selection

CPU

SS_EN

Byte 0

Bit 3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

CPU

FS2

Byte 0

Bit 2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

CPU

FS1

Byte 0

Bit 1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

CPU

FS0

Byte 0

Bit 0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

CPU

MHz

Down

Spread %

266.67

133.33

200.00

166.67

333.33

100.00

400.00

200.00

266.67

133.33

200.00

166.67

333.33

100.00

400.00

200.00

0%

0%

0%

0%

0%

0%

0%

0%

0.5%

0.5%

0.5%

0.5%

0.5%

0.5%

0.5%

0.5%

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

5

�9FGP204

Frequency Timing Generator for Peripherals

Table2: DOT96 Spread and Frequency Selection Table

DOT96

SS_EN

Byte 0

bit 4

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

FS3

FS2

FS1

FS0

Byte 3

bit 3

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Byte 3

bit 2

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Byte 3

bit 1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Byte 3

bit 0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

DOT96SS

MHz

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

96.00

IDT® Frequency Timing Generator for Peripherals

Spread %

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

+/-0.25

+/-0.5

+/-0.75

+/-1.0

-0.25

-0.50

-0.75

-1.0

-1.25

-1.50

-1.75

-2.0

-2.25

-2.5

-2.75

-3.00

Center

Center

Center

Center

Down

Down

Down

Down

Down

Down

Down

Down

Down

Down

Down

Down

1604C—04/23/15

6

�9FGP204

Frequency Timing Generator for Peripherals

Absolute Maximum Ratings

PARAMETER

SYMBOL

CONDITIONS

3.3V Supply Voltage

VDDxxx

-

VDDdelta

-

Maximum difference across all

VDD pins

Storage Temperature

TYP

3.3V

MAX

GND +

4.5

UNITS

Notes

V

1

0.5

V

1

Ts

-

-65

150

C

1

Tambient

-

0

70

°C

1

Junction Temperature

Tj

-

125

°C

1

Input ESD protection HBM

ESD prot

-

V

1

Ambient Operating Temp

1

MIN

GND 0.5

2000

°

Guaranteed by design and characterization, not 100% tested in production.

Electrical Characteristics - Input/Supply/Common Output Parameters

PARAMETER

SYMBOL

CONDITIONS*

Input High Voltage

VIH

3.3 V +/-5%

2

VDD + 0.3

V

1

Input Low Voltage

VIL

3.3 V +/-5%

VSS - 0.3

0.8

V

1

Input High Current

IIH

VIN = VDD

-5

5

uA

1

-5

uA

1

-200

uA

1

IIL1

Input Low Current

IIL2

Low Threshold InputHigh Voltage

Low Threshold InputLow Voltage

Operating Current

Powerdown Current

IDD3.3PD

Input Frequency

Fi

MIN

VIN = 0 V; Inputs with no pull-up

resistors

VIN = 0 V; Inputs with pull-up

resistors

TYP

MAX

UNITS

Notes

VIH_FS

3.3 V +/-5%

0.7

VDD + 0.3

V

1

VIL_FS

3.3 V +/-5%

VSS - 0.3

0.35

V

1

IDD3.3OP

all outputs driven, CPU@100M

204

225

mA

1

all diff pairs driven

20

30

mA

1

all differential pairs tri-stated

5

8

mA

1

VDD = 3.3 V

25.00000

MHz

2

7

nH

1

CIN

Logic Inputs

4

pF

1

COUT

Output pin capacitance

5

pF

1

CINX

5

pF

1

2.5

ms

1

33

kHz

1

300

us

1

Tfall_PD

X1 & X2 pins

From VDD Power-Up or deassertion of PD to 1st clock

Triangular Modulation

CPU output enable after

PD de-assertion

PD fall time of

5

ns

1

Trise_PD

PD rise time of

5

ns

1

5.5

V

1

0.4

V

1

mA

1

1000

ns

1

300

ns

1

Pin Inductance

Input Capacitance

Clk Stabilization

Lpin

TSTAB

Modulation Frequency

Tdrive_PD

SMBus Voltage

30

260

2.7

VDD

Low-level Output Voltage

VOL

Current sinking at

IPULLUP

VOL = 0.4 V

SCLK/SDATA

TRI2C

Clock/Data Rise Time

SCLK/SDATA

TFI2C

Clock/Data Fall Time

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%

0.5

@ IPULLUP

4

(Max VIL - 0.15) to

(Min VIH + 0.15)

(Min VIH + 0.15) to

(Max VIL - 0.15)

5

1

Guaranteed by design and characterization, not 100% tested in production.

2

Input frequency should be measured at the REF pin and tuned to ideal 25.00MHz to meet ppm frequency accuracy on PLL outputs.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

7

�9FGP204

Frequency Timing Generator for Peripherals

Electrical Characteristics - CPU 0.7V Current Mode Differential Pair

PARAMETER

Current Source Output

Impedance

Voltage High

SYMBOL

CONDITIONS*

MIN

Zo

VO = Vx

3000

VHigh

731

850

mV

1,3

VLow

Statistical measurement on single

ended signal

660

Voltage Low

-150

70

150

mV

1,3

Measurement on single ended

signal using absolute value.

800

1150

-300

8

250

366

16

Max Voltage

Vovs

Min Voltage

Vuds

Crossing Voltage (abs)

Vx(abs)

Crossing Voltage (var)

d-Vx

Long Accuracy

ppm

MAX

UNITS NOTES

Ω

1

mV

1

mV

1

550

mV

1

140

mV

1

Variation of crossing over all

edges

see Tperiod min-max values

-100

0

100

ppm

1,2

100.00MHz nominal

9.9990

10.0000

10.0001

ns

2

100.00MHz spread

10.0240

10.0250

10.0251

ns

2

1,2

Average period

Tperiod

Absolute min/max period

Tabsmin/max

100.00MHz nominal/spread

9.9490

10.1011

ns

Rise Time

tr

VOL = 0.175V, VOH = 0.525V

175

376

700

ps

1,4

Fall Time

tf

VOH = 0.525V VOL = 0.175V

175

335

700

ps

1,4

Rise Time Variation

d-tr

VOL = 0.175V, VOH = 0.525V

104

125

ps

1

Fall Time Variation

d-tf

92

125

ps

1

12.7

20

%

1

1

2

4

V/ns

1,5

45

49.8

55

%

1

45

50

ps

1

VOH = 0.525V VOL = 0.175V

Single-ended measurement,

Rise/Fall Matching

tRFM

averaging on

Slew Rate

tSLEW

Differential Measurment

Measurement from differential

Duty Cycle

dt3

wavefrom

Measurement from differential

Jitter, Cycle to cycle

tjcyc-cyc

wavefrom, CPUCLK

*TA = 0 - 70°C; VDD = 3.3 V +/-5%; CL =2pF, RS=33.2Ω, RP=49.9Ω, IREF = 475Ω

1

TYP

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz_x is tuned to exactly 25.000MHz

3

IREF = VDD/(3xRR). For RR = 475Ω (1%), IREF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50Ω.

4

Rise/fall time measured on single-ended waveform per CK410 specification.

5

Slew rate measured on differential waveform per CK505 specification.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

8

�9FGP204

Frequency Timing Generator for Peripherals

Electrical Characteristics - DOT96SS 0.7V Current Mode Differential Pair

PARAMETER

Current Source Output

Impedance

Voltage High

SYMBOL

CONDITIONS*

MIN

Zo

VO = Vx

3000

VHigh

660

Voltage Low

VLow

Statistical measurement on single

ended signal

Max Voltage

Vovs

Min Voltage

Vuds

Crossing Voltage (abs)

Vx(abs)

Crossing Voltage (var)

d-Vcross

Long Accuracy

ppm

Measurement on single ended

signal using absolute value.

UNITS

Notes

Ω

1

850

mV

1,3

51

150

mV

1,3

764

1150

mV

1

mV

1

550

mV

1

140

mV

1

1,2

725

-150

-300

5

250

372

MAX

Variation of crossing over all

edges

see Tperiod min-max values

-100

-41

100

ppm

96.00MHz nominal

10.4156

10.4166

10.4176

ns

2

96.00MHz -0.5% spread

10.4417

10.4427

10.4437

ns

2

10.6937

ns

1,2

Average period

Tperiod

Absolute min period

Tabsmin

96.00MHz nominal/-0.5% spread

10.1917

Rise Time

tr

VOL = 0.175V, VOH = 0.525V

175

361

700

ps

1,4

Fall Time

tf

VOH = 0.525V VOL = 0.175V

175

375

700

ps

1,4

Rise Time Variation

d-tr

VOL = 0.175V, VOH = 0.525V

107

125

ps

1

Fall Time Variation

d-tf

107

125

ps

1

15

20

%

1

1

2

4

V/ns

1,5

45

51.3

55

%

1

54

250

ps

1

VOH = 0.525V VOL = 0.175V

Single-ended measurement,

Rise/Fall Matching

tRFM

averaging on

Slew Rate

tSLEW

Differential Measurment

Measurement from differential

Duty Cycle

dt3

wavefrom

Measurement from differential

Jitter, Cycle to cycle

tjcyc-cyc

wavefrom

*TA = 0 - 70°C; VDD = 3.3 V +/-5%; CL =2pF, RS=33.2Ω, RP=49.9Ω, IREF = 475Ω

1

TYP

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz_x is tuned to exactly 25.000MHz

3

IREF = VDD/(3xRR). For RR = 475Ω (1%), IREF = 2.32mA. IOH = 6 x IREF and VOH = 0.7V @ ZO=50Ω.

4

Rise/fall time measured on single-ended waveform per CK410 specification.

5

Slew rate measured on differential waveform per CK505 specification.

Electrical Characteristics - REF - 25MHz

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Notes

Long Accuracy

ppm

see Tperiod min-max values

-50

0

50

ppm

1,2

Clock period

Tperiod

25.00MHz output nominal

39.998

40.000

40.002

ns

2

Output High Voltage

VOH

IOH = -1 mA

2.4

V

1

Output Low Voltage

VOL

IOL = 1 mA

Output High Current

Output Low Current

IOH

IOL

0.4

V OH @MIN = 1.0 V

-29

VOH@MAX = 3.135 V

VOL @ MIN = 1.95 V

-23

1

mA

1

mA

1

mA

1

27

mA

1

29

VOL @ MAX = 0.4 V

V

Rise Time

tr1

VOL = 0.4 V, VOH = 2.4 V

1

1.14

2

ns

1

Fall Time

tf1

VOH = 2.4 V, VOL = 0.4 V

1

1.32

2

ns

1

16

500

ps

1

45

53.2

55

%

1

75

200

ps

1

Skew

tsk1

VT = 1.5 V

Duty Cycle

dt1

VT = 1.5 V

Jitter, Cycle-cycle

tjcyc-cyc

VT = 1.5 V

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs as shown in the termination table (unless otherwise specified)

1

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz_x is tuned to exactly 25.000MHz

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

9

�9FGP204

Frequency Timing Generator for Peripherals

Electrical Characteristics - RGMII - 125MHz

PARAMETER

SYMBOL

CONDITIONS*

MIN

TYP

MAX

Long Accuracy

ppm

see Tperiod min-max values

0

Clock period

Tperiod

125.00MHz output nominal

-50

7.9996

50

8.0004

Output High Voltage

VOH

IOH = -1 mA

2.4

Output Low Voltage

VOL

IOL = 1 mA

Output High Current

IOH

V OH @MIN = 1.0 V

8.000

VOL @ MIN = 1.95 V

ns

1

V

1

0.4

V

1

mA

1

-33

mA

1

mA

1

-33

VOH@MAX = 3.135 V

UNITS NOTES

1,2

ppm

30

Output Low Current

IOL

38

mA

1

Rise Time

tr

VOL=20%xVdd, VOH=80%xVdd

0.66

0.75

ns

1

Fall Time

tf

VOL=20%xVdd, VOH=80%xVdd

0.70

0.75

ns

1

VOL @ MAX = 0.4 V

Duty Cycle

dt1

VT = 1.5 V

52.9

55

%

1

Group Skew

tskew_RGMII

VT = 1.5 V,

45

15

100

ps

1

Jitter, Long Term

tjabs

VT = 1.5 V, 10 sec interval

141

500

ps

1

Jitter, Cycle to cycle

tjcyc-cyc

VT = 1.5 V

75

250

ps

1

Jitter, Peak

tjpeak

VT = 1.5 V

68

100

ps

1,3

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs as shown in the termination table (unless otherwise specified)

1

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz_x is tuned to exactly 25.000MHz

3

1/2 of the peak-to-peak jitter. (Lg+ + |Lg-|)/2

Electrical Characteristics - RMII - 50MHz

PARAMETER

SYMBOL

CONDITIONS*

MIN

TYP

MAX

Long Accuracy

ppm

see Tperiod min-max values

0

Clock period

Tperiod

50.00MHz output nominal

-50

19.9990

50

20.001

Output High Voltage

VOH

IOH = -1 mA

2.4

Output Low Voltage

VOL

IOL = 1 mA

Output High Current

IOH

20.0000

0.4

V OH @MIN = 1.0 V

-33

VOH@MAX = 3.135 V

VOL @ MIN = 1.95 V

-33

30

UNITS NOTES

1,2

ppm

ns

1

V

1

V

1

mA

1

mA

1

mA

1

Output Low Current

IOL

38

mA

1

Rise Time

tr

VOL = 0.4 V, VOH = 2.4 V

1

1.1

3

ns

1

Fall Time

tf

VOH = 2.4 V, VOL = 0.4 V

1

1.1

3

ns

1

Duty Cycle

dt1

VT = 1.5 V

35

51.5

65

%

1

1

VOL @ MAX = 0.4 V

Jitter, Long Term

tjabs

VT = 1.5 V,

across all 6 outputs

VT = 1.5 V, 10 sec interval

Jitter, Peak

tjpeak

VT = 1.5 V

Group Skew

tskew_RMII(5:0)

60

200

ps

127

500

ps

1

88

100

ps

1,3

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs as shown in the termination table (unless otherwise specified)

1

Guaranteed by design and characterization, not 100% tested in production.

2

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that 25MHz_x is tuned to exactly 25.000MHz

3

1/2 of the peak-to-peak jitter. (Lg+ + |Lg-|)/2

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

10

�9FGP204

Frequency Timing Generator for Peripherals

Electrical Characteristics - 33.33MHz

PARAMETER

SYMBOL

CONDITIONS*

MIN

TYP

MAX

Long Accuracy

ppm

see Tperiod min-max values

Clock period

Tperiod

33.33MHz output non-spread

-100

29.9970

0

30.0000

100

30.0030

Output High Voltage

VOH

IOH = -1 mA

2.4

Output Low Voltage

VOL

IOL = 1 mA

Output High Current

IOH

V OH @MIN = 1.0 V

VOL @ MIN = 1.95 V

ns

1

V

1

0.4

V

1

mA

1

-33

mA

1

mA

1

-33

VOH@MAX = 3.135 V

UNITS NOTES

1

ppm

30

Output Low Current

IOL

38

mA

1

Rise Time

tr

VOL = 0.4 V, VOH = 2.4 V

0.5

0.87

2

ns

1

Fall Time

tf

VOH = 2.4 V, VOL = 0.4 V

0.5

1.35

2

ns

1

Duty Cycle

dt1

VT = 1.5 V

45

50.7

55

%

1

Jitter, Cycle to cycle

tjcyc-cyc

VT = 1.5 V

104

350

ps

1

VOL @ MAX = 0.4 V

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs as shown in the termination table (unless otherwise specified)

1

Guaranteed by design and characterization, not 100% tested in production.

Electrical Characteristics - 32.768KHz

UNITS NOTES

1

ppm

PARAMETER

SYMBOL

CONDITIONS*

MIN

TYP

MAX

Long Accuracy

ppm

see Tperiod min-max values

-100

-79

100

Clock period

Tperiod

32.768KHz output nominal

30.5149

30.5180

30.5211

us

Output High Voltage

VOH

IOH = -1 mA

2.4

V

1

Output Low Voltage

VOL

IOL = 1 mA

0.4

V

1

Output High Current

IOH

mA

1

-33

mA

1

mA

1

V OH @MIN = 1.0 V

-33

VOH@MAX = 3.135 V

VOL @ MIN = 1.95 V

30

1

Output Low Current

IOL

38

mA

1

Rise Time

tr

VOL = 0.4 V, VOH = 2.4 V

1

1.39

4

ns

1

Fall Time

tf

VOH = 2.4 V, VOL = 0.4 V

1

1.6

4

ns

1

Duty Cycle

dt1

VT = 1.5 V

45

49.5

55

%

1

Jitter, Cycle to cycle

tjcyc-cyc

VT = 1.5 V

220

500

ps

1

VOL @ MAX = 0.4 V

*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs as shown in the termination table (unless otherwise specified)

1

Guaranteed by design and characterization, not 100% tested in production.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

11

�9FGP204

Frequency Timing Generator for Peripherals

General SMBus serial interface information for the 9FGP204

How to Write:

How to Read:

Controller (host) sends a start bit.

Controller (host) sends the write address D0 (H)

ICS clock will acknowledge

Controller (host) sends the beginning byte location = N

ICS clock will acknowledge

Controller (host) sends the data byte count = X

ICS clock will acknowledge

Controller (host) starts sending Byte N through

Byte N + X -1

• ICS clock will acknowledge each byte one at a time

• Controller (host) sends a Stop bit

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Index Block Write Operation

Controller (Host)

starT bit

T

Slave Address *D0(H)

WR

WRite

Controller (host) will send start bit.

Controller (host) sends the write address D0 (H)

ICS clock will acknowledge

Controller (host) sends the begining byte

location = N

ICS clock will acknowledge

Controller (host) will send a separate start bit.

Controller (host) sends the read address D1 (H)

ICS clock will acknowledge

ICS clock will send the data byte count = X

ICS clock sends Byte N + X -1

ICS clock sends Byte 0 through byte X (if X(H)

was written to byte 8).

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

Index Block Read Operation

Controller (Host)

T

starT bit

Slave Address *D0(H)

WR

WRite

ICS (Slave/Receiver)

ICS (Slave/Receiver)

ACK

ACK

Beginning Byte = N

Beginning Byte = N

ACK

ACK

RT

Repeat starT

Slave Address *D1(H)

RD

ReaD

Data Byte Count = X

ACK

Beginning Byte N

ACK

X Byte

ACK

Data Byte Count = X

ACK

Beginning Byte N

ACK

X Byte

Byte N + X - 1

ACK

P

stoP bit

Byte N + X - 1

N

P

* The SMBus address depends on the latched value of pin 22.

Please see SMBus Address Selection table on page 1.

IDT® Frequency Timing Generator for Peripherals

Not acknowledge

stoP bit

1604C—04/23/15

12

�9FGP204

Frequency Timing Generator for Peripherals

SMBus Table: CPU Frequency Select and Spread Spectrum Control Register

Name

Control Function

Byte 0

Pin #

Reserved

Reserved

Bit 7

Type

RW

0

1

PWD

0

Reserved

Bit 6

-

Reserved

Reserved

Rev 0.20

Reserved

0

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

-

Reserved

DOT96 SS_EN

CPU SS_EN

CPU FS2

CPU FS1

CPU FS0

Reserved

DOT96 Spread Spectrum Enable

CPU Spread Spectrum Enable

CPU Freq Select Bit 2

CPU Freq Select Bit 1

CPU Freq Select Bit 0

RW

RW

RW

RW

RW

RW

Reserved

Disable

Enable

0

0

0

1

0

1

Control Function

RMII_7 Output Control

RMII_6 Output Control

RMII_5 Output Control

RMII_4 Output Control

RMII_3 Output Control

RMII_2 Output Control

RGMII_1 Output Control

RGMII_0 Output Control

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Disable

Disable

Disable

Disable

Disable

Disable

Disable

Disable

1

Enable

Enable

Enable

Enable

Enable

Enable

Enable

Enable

PWD

1

1

1

1

1

1

1

1

Type

RW

0

Driven

1

Hi-Z

PWD

0

RW

Driven

Hi-Z

0

RW

RW

RW

RW

RW

RW

Disable

Disable

Disable

Disable

Disable

Disable

Enable

Enable

Enable

Enable

Enable

Enable

1

1

1

1

1

1

0

1

3

2

1

0

Type

RW

RW

RW

RW

RW

RW

RW

RW

PWD

0

0

0

0

0

0

0

0

Control Function

RMII_7 Strength Control

RMII_6 Strength Control

RMII_5 Strength Control

RMII_4 Strength Control

RMII_3 Strength Control

RMII_2 Strength Control

Reserved

Reserved

Type

RW

RW

RW

RW

RW

RW

RW

RW

SMBus Table: RMII Output Control Register

Byte 1

Name

Pin #

24

RMII_5 Enable

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

25

28

29

32

33

36

37

RMII_4 Enable

RMII_3 Enable

RMII_2 Enable

RMII_1 Enable

RMII_0 Enable

RGMII_1 Enable

RGMII_0 Enable

SMBus Table: DOT, CPU, 32.768KHz, 25MHz and 33.33MHz Outputs Control Register

Byte 2

Name

Control Function

Pin #

CPUCLK PD Drive Mode

Driven in PD

7,8

Bit 7

DOT96SS PD Drive

Driven in PD

3,4

Bit 6

Mode

33.33MHz Enable

33.33MHz Output Control

22

Bit 5

25MHz_1 Enable

25MHz_1 Output Control

17

Bit 4

25MHz_0 Enable

25MHz_0 Output Control

16

Bit 3

32.768kHz Enable

32.768KHz Output Control

13

Bit 2

CPUCLK Enable

CPUCLK Output Control

6

Bit 1

DOT96SS Enable

DOT96SS Output Control

5

Bit 0

SMBus Table: DOT96 Frequency Select and Spread Spectrum Control Register

Name

Control Function

Byte 3

Pin #

Reserved

Reserved

Bit 7

Reserved

Reserved

Bit 6

Reserved

Reserved

Bit 5

Reserved

Reserved

Bit 4

DOT96SS FS3

DOT96 Freq Select Bit

Bit 3

DOT96SS FS2

DOT96 Freq Select Bit

Bit 2

DOT96SS FS1

DOT96 Freq Select Bit

Bit 1

DOT96SS FS0

DOT96 Freq Select Bit

Bit 0

SMBus Table: RMII Strength Control Register

Name

Byte 4

Pin #

RMII_5 Str

24

Bit 7

RMII_4 Str

25

Bit 6

RMII_3 Str

28

Bit 5

RMII_2 Str

29

Bit 4

RMII_1 Str

32

Bit 3

RMII_0 Str

33

Bit 2

Reserved

Bit 1

Reserved

Bit 0

IDT® Frequency Timing Generator for Peripherals

See Table 1:

CPU Frequency Selection

Table

Reserved

Reserved

Reserved

Reserved

See Table 2:

DOT Frequency Selection

Table

0

1

1-Load (1X) 2-Loads

1-Load (1X) 2-Loads

1-Load (1X) 2-Loads

1-Load (1X) 2-Loads

1-Load (1X) 2-Loads

1-Load (1X) 2-Loads

Reserved

Reserved

(2X)

(2X)

(2X)

(2X)

(2X)

(2X)

PWD

0

0

0

0

0

0

0

0

1604C—04/23/15

13

�9FGP204

Frequency Timing Generator for Peripherals

SMBus Table: 32.768KHz, 25Mhz and 33.33MHz Strength Control Register

Pin #

Byte 5

Name

Control Function

Reserved

Reserved

Bit 7

Reserved

Reserved

Bit 6

22

33.33MHz Str

33.33MHz Strength Control

Bit 5

17

25MHz_1 Str

25MHz_1 Strength Control

Bit 4

16

25MHz_0 Str

25MHz_1 Strength Control

Bit 3

13

32.768kHz Str

32.768kHz Strength Control

Bit 2

Reserved

Reserved

Bit 1

Reserved

Reserved

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Reserved

Reserved

1-Load (1X)

1-Load (1X)

1-Load (1X)

1-Load (1X)

Reserved

Reserved

SMBus Table: Vendor & Revision ID Register

Pin #

Name

Byte 6

RID3

Bit 7

RID2

Bit 6

RID1

Bit 5

RID0

Bit 4

VID3

Bit 3

VID2

Bit 2

VID1

Bit 1

VID0

Bit 0

Type

R

R

R

R

R

R

R

R

0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Type

RW

RW

RW

RW

RW

RW

RW

RW

Type

SMBus Table: Device ID

Pin #

Byte 7

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

Device ID 7 (MSB)

Device ID 6

Device ID 5

Device ID 4

Device ID 3

Device ID 2

Device ID 1

Device ID 0 (LSB)

SMBus Table: Byte Count Register

Pin #

Name

Byte 8

BC7

Bit 7

BC6

Bit 6

BC5

Bit 5

BC4

Bit 4

BC3

Bit 3

BC2

Bit 2

BC1

Bit 1

BC0

Bit 0

SMBus Table: Reserved

Pin #

Byte 9

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Name

Control Function

REVISION ID

VENDOR ID

Control Function

Device ID

Control Function

Writing to this register configures

how many bytes will be read back.

Control Function

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

IDT® Frequency Timing Generator for Peripherals

1

2-Loads

2-Loads

2-Loads

2-Loads

1

A rev = 0000

B rev = 0001

ICS/IDT = 0001

(2X)

(2X)

(2X)

(2X)

PWD

0

0

1

1

1

1

0

0

PWD

X

X

X

X

0

0

0

1

1

PWD

0

0

1

0

0

1

0

0

0

-

1

-

PWD

0

0

0

0

1

0

0

1

0

1

PWD

0

0

0

0

0

0

0

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

1604C—04/23/15

14

�9FGP204

Frequency Timing Generator for Peripherals

SMBus Table: PLLs M/N Programming Enable Register

Byte 10

Name

Control Function

Pin #

M/N_EN

PLLs M/N Programming Enable

Bit 7

Reserved

Bit 6

Reserved

Bit 5

Reserved

Bit 4

Reserved

Bit 3

Reserved

Bit 2

Reserved

Bit 1

Reserved

Bit 0

Type

RW

0

Disable

1

Enable

PWD

0

0

0

0

0

0

0

0

SMBus Table: CPU PLL VCO Frequency Control Register

Pin #

Byte 11

Name

Control Function

N Div8

N Divider Prog bit 8

Bit 7

N Div 9

N Divider Prog bit 9

Bit 6

M Div5

Bit 5

M Div4

Bit 4

M Div3

Bit 3

M Divider Programming bits

M Div2

Bit 2

M Div1

Bit 1

M Div0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

The decimal representation

of M and N Divier in Byte 11

and 12 will configure the

VCO frequency. Default at

power up = latch-in or Byte 0

Rom table. VCO Frequency

= 25 x [NDiv(9:0)+8] /

[MDiv(5:0)+2]

PWD

X

X

X

X

X

X

X

X

SMBus Table: CPU PLL VCO Frequency Control Register

Pin #

Byte 12

Name

Control Function

N Div7

Bit 7

N Div6

Bit 6

N Div5

Bit 5

N Div4

Bit 4

N Divider Programming b(7:0)

N Div3

Bit 3

N Div2

Bit 2

N Div1

Bit 1

N Div0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

The decimal representation

of M and N Divier in Byte 11

and 12 will configure the

VCO frequency. Default at

power up = latch-in or Byte 0

Rom table. VCO Frequency

= 25 x [NDiv(9:0)+8] /

[MDiv(5:0)+2]

PWD

X

X

X

X

X

X

X

X

SMBus Table: CPU PLL Spread Spectrum Control Register

Pin #

Byte 13

Name

Control Function

SSP7

Bit 7

SSP6

Bit 6

SSP5

Bit 5

Spread Spectrum Programming

SSP4

Bit 4

b(7:0)

SSP3

Bit 3

SSP2

Bit 2

SSP1

Bit 1

SSP0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

SMBus Table: CPU PLL Spread Spectrum Control Register

Pin #

Byte 14

Name

Control Function

Reserved

Bit 7

SSP14

Bit 6

SSP13

Bit 5

SSP12

Bit 4

Spread Spectrum Programming

SSP11

Bit 3

b(14:8)

SSP10

Bit 2

SSP9

Bit 1

SSP8

Bit 0

IDT® Frequency Timing Generator for Peripherals

Type

RW

RW

RW

RW

RW

RW

RW

0

1

These Spread Spectrum bits

in Byte 13 and 14 will

program the spread

pecentage. It is

recommended to use ICS

Spread % table for spread

programming.

0

1

These Spread Spectrum bits

in Byte 13 and 14 will

program the spread

pecentage. It is

recommended to use ICS

Spread % table for spread

programming.

PWD

X

X

X

X

X

X

X

X

PWD

0

X

X

X

X

X

X

X

1604C—04/23/15

15

�9FGP204

Frequency Timing Generator for Peripherals

SMBus Table: DOT PLL VCO Frequency Control Register

Pin #

Name

Control Function

Byte 15

N Div8

N Divider Prog bit 8

Bit 7

N Div9

N Divider Prog bit 9

Bit 6

M Div5

Bit 5

M Div4

Bit 4

M Div3

Bit 3

M Divider Programming bits

M Div2

Bit 2

M Div1

Bit 1

M Div0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

The decimal representation

of M and N Divier in Byte 17

and 18 will configure the

VCO frequency. Default at

power up = Byte 0 Rom

table. VCO Frequency = 25

x [NDiv(9:0)+8] /

[MDiv(5:0)+2]

PWD

X

X

X

X

X

X

X

X

SMBus Table: DOT PLL VCO Frequency Control Register

Pin #

Byte 16

Name

Control Function

N Div7

Bit 7

N Div6

Bit 6

N Div5

Bit 5

N Div4

Bit 4

N Divider Programming b(7:0)

N Div3

Bit 3

N Div2

Bit 2

N Div1

Bit 1

N Div0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

The decimal representation

of M and N Divier in Byte 17

and 18 will configure the

VCO frequency. Default at

power up = Byte 0 Rom

table. VCO Frequency = 25

x [NDiv(9:0)+8] /

[MDiv(5:0)+2]

PWD

X

X

X

X

X

X

X

X

SMBus Table: DOT PLL Spread Spectrum Control Register

Pin #

Byte 17

Name

Control Function

SSP7

Bit 7

SSP6

Bit 6

SSP5

Bit 5

Spread Spectrum Programming

SSP4

Bit 4

b(7:0)

SSP3

Bit 3

SSP2

Bit 2

SSP1

Bit 1

SSP0

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

SMBus Table: DOT PLL Spread Spectrum Control Register

Pin #

Byte 18

Name

Control Function

Reserved

Bit 7

SSP14

Bit 6

SSP13

Bit 5

SSP12

Bit 4

Spread Spectrum Programming

SSP11

Bit 3

b(14:8)

SSP10

Bit 2

SSP9

Bit 1

SSP8

Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

0

1

These Spread Spectrum bits

in Byte 19 and 20 will

program the spread

pecentage. It is

recommended to use ICS

Spread % table for spread

programming.

0

1

These Spread Spectrum bits

in Byte 19 and 20 will

program the spread

pecentage. It is

recommended to use ICS

Spread % table for spread

programming.

PWD

X

X

X

X

X

X

X

X

PWD

0

X

X

X

X

X

X

X

Bytes 19:21 are reserved.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

16

�9FGP204

Frequency Timing Generator for Peripherals

(Ref.)

Seating Plane

(N D -1)x e

(Ref.)

A1

Index Area

ND & NE

Even

A3

N

L

N

2

2

E2

or

E

(Ref.)

b

(Ref.)

A

D

(NE -1)x e

E2

2

Sawn

Singulation

Top View

are Even

1

Anvil

Singulation

1

(Typ.)

e

2 If N & N

D

E

e

Thermal

Base

D2

2

ND & NE

Odd

D2

0.08

C

C

THERMALLY ENHANCED, VERY THIN, FINE PITCH

QUAD FLAT / NO LEAD PLASTIC PACKAGE

DIMENSIONS

DIMENSIONS

SYMBOL

MIN.

MAX.

A

0.8

1.0

A1

0

0.05

40L

SYMBOL

0.25 Reference

A3

b

0.1 8

0.3

0.50 BASIC

e

Marking Diagram

ICS

9FGP204BL

YYWW

COO

LOT

(JEDEC

reference only) (IDT package)

VJJD-2 / -5

TOLERANCE

N

40

40

ND

10

10

NE

10

10

D x E BASIC

6.00 x 6.00

6.00 x 6.00

D2 MIN. / MAX.

1.75 / 4.80

2.75 / 3.0

E2 MIN. / MAX.

1.75 / 4.80

2.75 / 3.0

L MIN. / MAX.

0.30 / 0.50

0.3 / 0.5

Notes:

1. “LOT” is the lot sequence number.

2. “COO” denotes country of origin.

3. “YYWW” is the last two digits of the year and week that the part was assembled.

4. “L” denotes RoHS compliant package.

Ordering Information

Part / Order Number

9FGP204BKLF

9FGP204BKLFT

Shipping Packaging

Trays

Tape and Reel

Package

40-pin MLF

40-pin MLF

Temperature

0 to +70° C

0 to +70° C

Parts that are ordered with an “LF” to the suffix are the Pb-Free configuration and are RoHS compliant.

IDT® Frequency Timing Generator for Peripherals

1604C—04/23/15

17

�9FGP204

Frequency Timing Generator for Peripherals

Revision History

Rev.

Issue Date

Who

A

4/7/2010

RDW

B

C

8/29/2011

4/23/2015

RDW

RDW

Description

Page #

1. Updated Series Termination values and highlighted values are for Zo

= 50 ohms.

2. Raised Idd MAX to 225mA from 200 mA

3. Adding Rise/Fall Matching spec to CPU and DOT96SS Electrical

4, 7, 8,

Tables.

9, 10, 11

4. Removed All CPU frequencies except 100 from CPU Electrical

Table.

5. Updated Min/Max clock periods to reflect new 50 ps cycle to cycle

jitter limit on CPU output.

4. Updated electrical tables with typical values from char report.

1. Removed OE pins for RMII from the block diagram.

3

Added marking diagram and associated notes

Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

For Tech Support

800-345-7015

408-284-8200

Fax: 408-284-2775

408-284-6578

pcclockhelp@idt.com

Corporate Headquarters

Asia Pacific and Japan

Europe

Integrated Device Technology, Inc.

6024 Silver Creek Valley Road

San Jose, CA 95138

United States

800 345 7015

+408 284 8200 (outside U.S.)

IDT Singapore Pte. Ltd.

1 Kallang Sector #07-01/06

KolamAyer Industrial Park

Singapore 349276

Phone: 65-6-744-3356

Fax: 65-6-744-1764

IDT Europe Limited

321 Kingston Road

Leatherhead, Surrey

KT22 7TU

England

Phone: 44-1372-363339

Fax: 44-1372-378851

© 2010 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT, ICS, and the IDT logo are trademarks

of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks

are or may be trademarks or registered trademarks used to identify products or services of their respective owners.

Printed in USA

18

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

�