PC MAIN CLOCK - CK540

9UMS9001

•

Fully integrated Vreg

•

Integrated series resistors on differential

outputs

•

Supports split rail operation for maximum

power savings

•

Also runs from single 3.3V rail

•

1.05V-3.3V support for differential VDDIO

•

4 - SRC low power differential push-pull pairs

•

1 - LCD100 SSCD low power differential

push-pull pair

•

1 - DOT96 low power differential push-pull

pair

•

3 - PCI, 33MHz

•

1 - USB, 48MHz

•

1 - REF, 14.31818MHz

FSLC

GNDREF

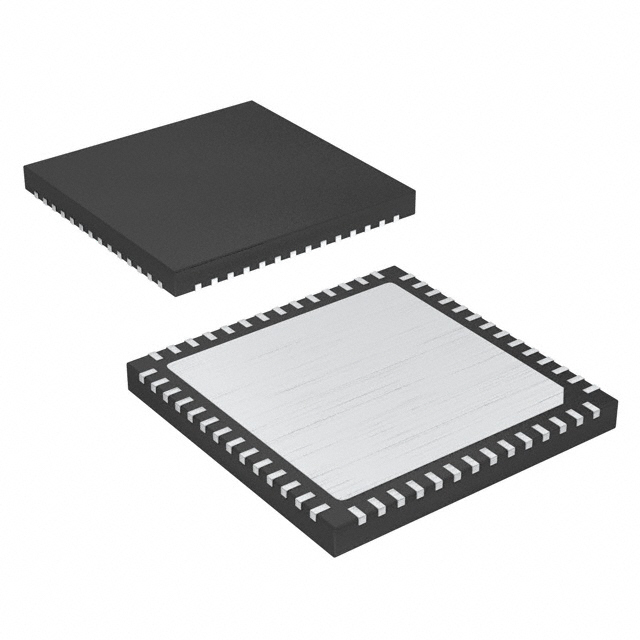

Pin Configuration

VDDCPUPLL_3.3

1 - ITP low power differential push-pull pair

CK_PWRGD#/PD

•

FSLB

PCI_SRC and CPU STOP inputs for power

manangment

2 - CPU Low Power differential push-pull pairs

CPU_STOP#

•

•

CPUITPC_LPRS

Dedicated TEST/SEL and TEST/MODE pins

saves isolation resistors on pins

CPUITPT_LPRS

•

CPU1C_LPRS

Output Features:

CPU1T_LPRS

Supports Dothan ULV CPUs with 100 and

133 MHz CPU outputs

VDDIO_CPU

•

GNDCPU

Calistoga Based Ultra-Mobile PC (UMPC)

CPU0C_LPRS

Features/Benefits:

CPU0T_LPRS

Recommended Application:

56 55 54 53 52 51 50 49 48 47 46 45 44 43

X2

X1

VDDREFIO_3.3

REF0

1

2

3

4

SDATA 5

SCLK 6

TEST_SEL 7

TEST_MODE 8

PCI_STOP# 9

VDDIO_PCI3.3 10

PCI0 11

PCI1 12

PCI_F2 13

GNDPCI 14

ICS9UMS9001

42

41

40

39

38

CLKREQ2#

CLKREQ3#

VDDCORE_3.3

SRC3T_LPRS

37

36

35

34

33

32

31

30

29

SRC2T_LPRS

SRC2C_LPRS

VDDIO_SRC

GNDSRC

SRC1T_LPRS

SRC1C_LPRS

SRC0T_LPRS

SRC0C_LPRS

CLKREQ0#

SRC3C_LPRS

CLKREQ1#

VDDLCDPLL_3.3

VDDIO_LCD

LCD100T_LPRS

LCD100C_LPRS

GND

GND

DOT96T_LPRS

VDDIO_96Mhz

DOT96C_LPRS

VDD48PLL_3.3

USB_48MHz

VDD48IO_3.3

GND48

15 16 17 18 19 20 21 22 23 24 25 26 27 28

56-pin MLF

®

IDT PC MAIN CLOCK - CK540

1247C—06/16/11

1

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Pin Description

PIN #

PIN NAME

TYPE

DESCRIPTION

1

X2

OUT Crystal output, nominally 14.318MHz.

2

X1

3

VDDREFIO_3.3

PWR Power pin for the REF output and crystal oscillator. 3.3V nominal.

4

REF0

OUT 3.3V 14.318MHz reference clock

5

SDATA

I/O

Data pin for SMBus circuitry, 5V tolerant.

6

SCLK

IN

7

TEST_SEL

IN

8

TEST_MODE

IN

Clock pin of SMBus circuitry, 5V tolerant.

3.3V input that puts the part in test mode. This is a realtime input. See the Test Clarification Table for

details.

When Test mode is selected, this chooses either hi-Z or REF/N for the outputs.

9

PCI_STOP#

IN

3.3V tolerant input that stops all PCI and SRC clocks, except those set to be free running.

10

VDDIO_PCI3.3

PWR 3.3V power supply for the PCI outputs

11

PCI0

OUT 3.3V PCI clock output.

12

PCI1

OUT 3.3V PCI clock output.

13

PCI_F2

OUT Free running 3.3V PCI clock output

14

GNDPCI

PWR Ground for PCI output clocks.

15

GND48

PWR Ground for the USB clock.

16

USB_48MHz

OUT

17

VDD48IO_3.3

PWR 3.3V Power supply for the 48MHz output

IN

Crystal input, Nominally 14.318MHz.

Fixed 3.3V 48MHz USB clock output

18

VDD48PLL_3.3

PWR 3.3V Power supply for the 48/96MHz PLL

19

VDDIO_96Mhz

20

DOT96C_LPRS

21

DOT96T_LPRS

22

GND

PWR Power supply for DOT96 output. VDD_IO = 1.05 to 3.3V +/-5%.

Complement side of low-power CK505-type 96MHz differential clock. Rs is integrated (No external

OUT

series resistor required).

True side of low-power CK505-type 96MHz differential clock. Rs is integrated (No external series

OUT

resistor required).

PWR Ground for 96MHz output

23

GND

PWR Ground for LCD 100 MHz output.

24

LCD100C_LPRS

OUT

25

LCD100T_LPRS

Complement side of low-power CK505-type LCD100MHz spreading differential clock. Rs is integrated

(No external series resistor required).

26

VDDIO_LCD

True side of low-power CK505-type LCD100MHz spreading differential clock. Rs is integrated (No

external series resistor required).

PWR Power supply for LCD100 output. VDD_IO = 1.05 to 3.3V +/-5%.

27

VDDLCDPLL_3.3

PWR 3.3V Power supply for the LCD100 Spreading PLL

28

CLKREQ1#

OUT

IN

Clock request input for SRC output pair 1. See the SRC, LCD, DOT Power Management Table for

details

IDT® PC MAIN CLOCK - CK540

1247C—06/16/11

2

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Pin Description (continued)

PIN #

PIN NAME

TYPE

29

CLKREQ0#

30

SRC0C_LPRS

OUT

31

SRC0T_LPRS

OUT

32

SRC1C_LPRS

OUT

33

SRC1T_LPRS

OUT

34

GNDSRC

PWR

35

VDDIO_SRC

36

SRC2C_LPRS

37

SRC2T_LPRS

38

SRC3C_LPRS

39

SRC3T_LPRS

40

VDDCORE_3.3

41

CLKREQ3#

42

CLKREQ2#

43

FSLB

44

CPU_STOP#

45

CPUITPC_LPRS

46

CPUITPT_LPRS

47

CPU1C_LPRS

48

CPU1T_LPRS

PWR Power supply for SRC outputs. VDD_IO = 1.05 to 3.3V +/-5%.

Complement side of low-power CK505-type SRC2 differential clock. Rs is integrated (No external

OUT

series resistor required).

True side of low-power CK505-type SRC2 differential clock. Rs is integrated (No external series

OUT

resistor required).

Complement side of low-power CK505-type SRC3 differential clock. Rs is integrated (No external

OUT

series resistor required).

True side of low-power CK505-type SRC3 differential clock. Rs is integrated (No external series

OUT

resistor required).

PWR 3.3V Power supply for 3.3V core

Clock request input for SRC output pair 3. See the SRC, LCD, DOT Power Management Table for

IN

details

Clock request input for SRC output pair 2. See the SRC, LCD, DOT Power Management Table for

IN

details

Low threshold Frequency Select input. See Table 1: CPU Frequency Select Table and the Vih_fs and

IN

Vil_fs specifications.

IN Stops all CPU clocks except those set to be free running.

Complement side of low-power CK505-type CPUITP differential clock. Rs is integrated (No external

OUT

series resistor required). Note that this pin is NOT muxed with an SRC output.

True side of low-power CK505-type CPUITP differential clock. Rs is integrated (No external series

OUT

resistor required).

Complement side of low-power CK505-type CPU1 differential clock. Rs is integrated (No external

OUT

series resistor required). Note that this pin is NOT muxed with an SRC output.

True side of low-power CK505-type CPU1 differential clock. Rs is integrated (No external series

OUT

resistor required).

PWR Power supply for CPU outputs. VDD_IO = 1.05 to 3.3V +/-5%.

49

VDDIO_CPU

50

GNDCPU

51

CPU0C_LPRS

52

CPU0T_LPRS

53

VDDCPUPLL_3.3

54

CK_PWRGD#/PD

55

FSLC

56

GNDREF

IN

DESCRIPTION

Clock request input for SRC output pair 0. See the SRC, LCD, DOT Power Management Table for

details

Complement side of low-power CK505-type SRC0 differential clock. Rs is integrated (No external

series resistor required).

True side of low-power CK505-type SRC0 differential clock. Rs is integrated (No external series

resistor required).

Complement side of low-power CK505-type SRC1 differential clock. Rs is integrated (No external

series resistor required).

True side of low-power CK505-type SRC1 differential clock. Rs is integrated (No external series

resistor required).

Ground for SRC clocks

PWR Ground Pin for CPU Outputs

Complement side of low-power CK505-type CPU1 differential clock. Rs is integrated (No external

OUT

series resistor required). Note that this pin is NOT muxed with an SRC output.

True side of low-power CK505-type CPU1 differential clock. Rs is integrated (No external series

OUT

resistor required).

PWR 3.3V Power Supply for CPU PLL.

Notifies 9UMS9001 to sample latched inputs or enter power down mode.

1 = Power down mode

IN

Falling Edge = Sample latched inputs

0 = Normal operation

Low threshold Frequency Select input. See Table 1: CPU Frequency Select Table and the Vih_fs and

IN

Vil_fs specifications.

PWR Ground pin for crystal oscillator circuit and REF output

IDT® PC MAIN CLOCK - CK540

1247C—06/16/11

3

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Functional Block Diagram

REF

X1

OSC

X2

PCI

CPU/SRC/

PC

SS-PLL

SRC(3:0)

CPU(2:0)

LCD SS

PLL

LCD

Fixed

EXACT

48MHz

DOT96MHZ

48MHZ

FSLC

FSLB

CKPWRGD#/PD

PCI_STOP#

CPU_STOP#

CLKREQ(3:0)#

Control

Logic

ITP_EN

TESTSEL

TESTMODE

Power Groups

VDD3.3V

Pin Number

VDDIO 1.05~3.3V

49

53

53

35

40

26

27

19

17, 18

3

10

Description

GND

50

34

23

22

15

56

14

Low power outputs

Analog

Master Clock, Analog

Low power outputs

SRCCLK

Analog

Low power outputs

LCDCLK

PLL

DOT 96Mhz

Low power outputs

USB 48

Xtal, REF

PCICLK

CPUCLK

IDT® PC MAIN CLOCK - CK540

1247C—06/16/11

4

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Table 1: CPU Frequency Select Table

1

FSLC

B0b7

0

0

1

1

1

FSLB

B0b6

0

1

0

1

CPU

MHz

SRC

MHz

133.33

100.00

Reserved

100.00

100.00

200.00

PCI

MHz

REF

MHz

USB

MHz

DOT

MHz

33.33

14.318

48.00

96.00

33.33

14.318

48.00

96.00

1. FSLC is a low-threshold input.Please see VIL_FS and VIH_FS specifications in

the Input/Supply/Common Output Parameters Table for correct values.

Also refer to the Test Clarification Table.

Table 2: LCD Quick Configuration

B1b3

B1b2

B1b1

B1b0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Pin 24/25

MHz

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

100.00

Spread

Comment

%

0.25% Down Spread

LCDCLK

0.5% Down Spread

LCDCLK

1% Down Spread

LCDCLK

1.25% Down Spread

LCDCLK

1.5% Down Spread

LCDCLK

2% Down Spread

LCDCLK

2.5% Down Spread

LCDCLK

3.0% Down Spread

LCDCLK

0.25% Center Spread LCDCLK

0.5% Center Spread

LCDCLK

1% Center Spread

LCDCLK

1.25% Center Spread LCDCLK

1.5% Center Spread

LCDCLK

2% Center Spread

LCDCLK

2.5% Center Spread

LCDCLK

3.0% Center Spread

LCDCLK

Table 3: IO_Vout select table

B5b2

B5b1

B5b0 IO_Vout

0.3V

0

0

0

0.4V

0

0

1

0.5V

0

1

0

0.6V

0

1

1

0.7V

1

0

0

0.8V

1

0

1

0.9V

1

1

0

1.0V

1

1

1

IDT® PC MAIN CLOCK - CK540

1247C—06/16/11

5

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Absolute Maximum Ratings

PARAMETER

SYMBOL

CONDITIONS

Maximum Supply Voltage

VDDxxx_3.3

Supply Voltage

MIN

MAX

4.6

V

1,7

Maximum Supply Voltage

VDDxxx_1.8

Supply Voltage

2.3

V

1,7

Maximum Supply Voltage

VDDxxx_IO

Low-Voltage Differential I/O Supply

3.8

V

1,7

Maximum Input Voltage

VIH

3.3V LVCMOS Inputs

4.6

V

1,7,8

Minimum Input Voltage

VIL

Any Input

GND - 0.5

Storage Temperature

Ts

-

-65

Input ESD protection

ESD prot

Human Body Model

2000

150

UNITS Notes

V

1,7

°

C

1,7

V

1,7

Electrical Characteristics - Input/Supply/Common Output Parameters

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

Ambient Operating Temp

Tambient

-

0

70

°C

Supply Voltage

VDDxxx_3.3

Supply Voltage

3.135

3.465

V

1

Supply Voltage

VDDxxx_1.8

Supply Voltage

1.71

1.89

V

1

Supply Voltage

VDDxxx_IO

Low-Voltage Differential I/O Supply

1.05

3.465

V

1

Input High Voltage

VIHSE

Single-ended inputs

2

VDD + 0.3

V

1

Input Low Voltage

VILSE

Single-ended inputs

VSS - 0.3

0.8

V

1

Input Leakage Current

IIN

-5

5

uA

1

Input Leakage Current

IINRES

VIN = VDD , VIN = GND

Inputs with pull or pull down

resistors

VIN = VDD , VIN = GND

-200

200

uA

1

Output High Voltage

VOHSE

Single-ended outputs, IOH = -1mA

V

1

Output Low Voltage

VOLSE

Single-ended outputs, IOL = 1 mA

Output High Voltage

VOHDIF

Differential Outputs

VOLDIF

Differential Outputs

VIH_FS_TEST

3.3 V +/-5%

VIH_FS

VIL_FS

Output Low Voltage

Low Threshold InputHigh Voltage (Test Mode)

Low Threshold InputHigh Voltage

Low Threshold InputLow Voltage

Operating Supply Current

2.4

UNITS Notes

1

0.4

V

1

0.9

V

1

0.4

V

1

2

VDD + 0.3

V

1

3.3 V +/-5%

0.7

1.5

V

1

3.3 V +/-5%

VSS - 0.3

0.35

V

1

0.7

IDD_DEFAULT

3.3V supply, LCDPLL off

80

mA

1

IDD_LCDEN

100

mA

1

25

mA

1

IDD_PD3.3

3.3V supply, LCDPLL enabled

0.8V supply, Differential IO current,

all outputs enabled

3.3V supply, Power Down Mode

1

mA

1

IDD_PDIO

0.8V IO supply, Power Down Mode

0.1

mA

1

Input Frequency

Fi

VDD = 3.3 V

15

MHz

2

Pin Inductance

Lpin

IDD_IO

Power Down Current

Input Capacitance

Spread Spectrum Modulation

Frequency

7

nH

1

5

pF

1

Output pin capacitance

6

pF

1

CINX

X1 & X2 pins

7

pF

1

fSSMOD

Triangular Modulation

33

kHz

1

CIN

Logic Inputs

COUT

1.5

IDT® PC MAIN CLOCK - CK540

30

1247C—06/16/11

6

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

AC Electrical Characteristics - Input/Common Parameters

PARAMETER

SYMBOL

Clk Stabilization

TSTAB

Tdrive_SRC

TDRSRC

Tdrive_PD#

TDRPD

Tdrive_CPU

TDRSRC

Tfall_PD#

TFALL

Trise_PD#

TRISE

CONDITIONS

From VDD Power-Up or deassertion of PD# to 1st clock

SRC output enable after

PCI_STOP# de-assertion

Differential output enable after

PD# de-assertion

CPU output enable after

CPU_STOP# de-assertion

MIN

MAX

UNITS Notes

1.8

ms

1

15

ns

1

300

us

1

10

ns

1

5

ns

1

5

ns

1

Fall/rise time of PD#, PCI_STOP#

and CPU_STOP# inputs

AC Electrical Characteristics - Low Power Differential Outputs

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

Rising Edge Slew Rate

tSLR

Differential Measurement

1

4

UNITS NOTES

V/ns

1,2

1

Falling Edge Slew Rate

tFLR

Differential Measurement

4

V/ns

1,2

Rise/Fall Time Variation

tSLVAR

Single-ended Measurement

125

ps

1

Maximum Output Voltage

VHIGH

Includes overshoot

1150

mV

1

Minimum Output Voltage

VLOW

Includes undershoot

-300

mV

1

Differential Voltage Swing

VSWING

Differential Measurement

300

mV

1

Crossing Point Voltage

VXABS

Single-ended Measurement

300

550

mV

1,3,4

Crossing Point Variation

VXABSVAR

Single-ended Measurement

140

mV

1,3,5

Duty Cycle

DCYC

Differential Measurement

55

%

1

CPU Jitter - Cycle to Cycle

CPUJ C2C

Differential Measurement

85

ps

1

SRC Jitter - Cycle to Cycle

SRCJ C2C

Differential Measurement

125

ps

1

DOT Jitter - Cycle to Cycle

DOTJ C2C

Differential Measurement

250

ps

1

45

CPU[1:0] Skew

CPUSKEW10

Differential Measurement

100

ps

1

CPU[2_ITP:0] Skew

CPUSKEW20

Differential Measurement

150

ps

1

SRC[3:0] Skew

SRCSKEW

Differential Measurement

250

ps

1

Electrical Characteristics - PCICLK/PCICLK_F

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

Long Accuracy

ppm

see Tperiod min-max values

-300

300

Clock period

Tperiod

Absolute min/max period

Tabs

33.33MHz output nominal/spread

29.49100

Output High Voltage

VOH

IOH = -1 mA

2.4

Output Low Voltage

VOL

33.33MHz output nominal

33.33MHz output spread

29.99100

30.00900

ns

6

30.15980

ns

6

30.65980

ns

6

V

1

IOL = 1 mA

0.4

V OH @MIN = 1.0 V

Output High Current

IOH

Output Low Current

IOL

Rising Edge Slew Rate

tSLR

Measured from 0.8 to 2.0 V

Falling Edge Slew Rate

tFLR

Measured from 2.0 to 0.8 V

Duty Cycle

dt1

VT = 1.5 V

-33

VOH@MAX = 3.135 V

VOL @ MIN = 1.95 V

-33

30

Skew

tskew

VT = 1.5 V

tdelay

VT = 1.5 V

Jitter, Cycle to cycle

tjcyc-cyc

VT = 1.5 V

1

1

mA

1

mA

1

mA

1

4

V/ns

1

1

4

V/ns

1

45

55

%

1

1

250

0 nominal

500

IDT® PC MAIN CLOCK - CK540

V

mA

38

VOL @ MAX = 0.4 V

Intentional PCI-PCI delay

UNITS NOTES

1,6

ppm

ps

1

ps

1,9

ps

1

1247C—06/16/11

7

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Electrical Characteristics - USB48MHz

PARAMETER

Long Accuracy

SYMBOL

ppm

CONDITIONS

see Tperiod min-max values

MIN

-100

MAX

100

UNITS NOTES

ppm

1,2

Clock period

Tperiod

48.00MHz output nominal

20.83125

20.83542

ns

2

Absolute min/max period

Tabs

48.00MHz output nominal

20.48130

21.18540

ns

2

Output High Voltage

VOH

IOH = -1 mA

2.4

V

1

Output Low Voltage

VOL

IOL = 1 mA

V

1

mA

1

Output High Current

Output Low Current

IOH

IOL

0.4

V OH @MIN = 1.0 V

-29

VOH@MAX = 3.135 V

VOL @ MIN = 1.95 V

-23

mA

1

mA

1

27

mA

1

29

VOL @ MAX = 0.4 V

Rising Edge Slew Rate

tSLR

Measured from 0.8 to 2.0 V

1

2

V/ns

1

Falling Edge Slew Rate

tFLR

Measured from 2.0 to 0.8 V

1

2

V/ns

1

Duty Cycle

dt1

VT = 1.5 V

45

55

%

1

Jitter, Cycle to cycle

tjcyc-cyc

VT = 1.5 V

350

ps

1

Electrical Characteristics - SMBus Interface

PARAMETER

SYMBOL

SMBus Voltage

VDD

CONDITIONS

Low-level Output Voltage

Current sinking at

VOLSMB = 0.4 V

SCLK/SDATA

Clock/Data Rise Time

SCLK/SDATA

Clock/Data Fall Time

Maximum SMBus Operating

Frequency

VOLSMB

@ IPULLUP

IPULLUP

SMB Data Pin

TFI2C

(Max VIL - 0.15) to

(Min VIH + 0.15)

(Min VIH + 0.15) to

(Max VIL - 0.15)

FSMBUS

Block Mode

TRI2C

IDT® PC MAIN CLOCK - CK540

MIN

MAX

2.7

5.5

V

1

0.4

V

1

mA

1

1000

ns

1

300

ns

1

100

kHz

1

4

UNITS Notes

1247C—06/16/11

8

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Electrical Characteristics - REF-14.318MHz

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

Long Accuracy

ppm

see Tperiod min-max values

-300

300

ppm

1,2

Clock period

Tperiod

14.318MHz output nominal

69.8203

69.8622

ns

2

Absolute min/max period

Tabs

14.318MHz output nominal

69.8203

70.86224

ns

2

Output High Voltage

VOH

IOH = -1 mA

2.4

V

1

Output Low Voltage

VOL

0.4

V

1

-33

-33

mA

1

30

38

mA

1

1

4

V/ns

1

IOL = 1 mA

VOH @MIN = 1.0 V,

UNITS Notes

Output High Current

IOH

Output Low Current

IOL

Rising Edge Slew Rate

tSLR

Measured from 0.8 to 2.0 V

Falling Edge Slew Rate

tFLR

Measured from 2.0 to 0.8 V

1

4

V/ns

1

Duty Cycle

dt1

VT = 1.5 V

45

55

%

1

Jitter

tjcyc-cyc

VT = 1.5 V

1000

ps

1

VOH@MAX = 3.135 V

VOL @MIN = 1.95 V,

VOL @MAX = 0.4 V

Notes on Electrical Characteristics:

1

Guaranteed by design and characterization, not 100% tested in production.

2

Slew rate measured through Vswing centered around differential zero

3

Vxabs is defined as the voltage where CLK = CLK#

4

Only applies to the differential rising edge (CLK rising and CLK# falling)

Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of

CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets

CLK#. The average cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate

calculations

6

All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

5

7

Operation under these conditions is neither implied, nor guaranteed.

8

Maximum input voltage is not to exceed maximum VDD

9

See PCI Clock-to-Clock Delay Figure

IDT® PC MAIN CLOCK - CK540

1247C—06/16/11

9

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

General I2C serial interface information for the 9UMS9001

How to Write:

How to Read:

Controller (host) sends a start bit.

Controller (host) sends the write address D2 (H)

ICS clock will acknowledge

Controller (host) sends the beginning byte location = N

ICS clock will acknowledge

Controller (host) sends the data byte count = X

ICS clock will acknowledge

Controller (host) starts sending Byte N through

Byte N + X -1

(see Note 2)

• ICS clock will acknowledge each byte one at a time

• Controller (host) sends a Stop bit

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Controller (host) will send start bit.

Controller (host) sends the write address D2 (H)

ICS clock will acknowledge

Controller (host) sends the begining byte

location = N

ICS clock will acknowledge

Controller (host) will send a separate start bit.

Controller (host) sends the read address D3 (H)

ICS clock will acknowledge

ICS clock will send the data byte count = X

ICS clock sends Byte N + X -1

ICS clock sends Byte 0 through byte X (if X(H)

was written to byte 8).

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

Index Block Read Operation

Index Block Write Operation

Controller (Host)

starT bit

T

Slave Address D2(H)

WR

WRite

Controller (Host)

T

starT bit

Slave Address D2(H)

WR

WRite

ICS (Slave/Receiver)

ICS (Slave/Receiver)

ACK

ACK

Beginning Byte = N

Beginning Byte = N

ACK

ACK

RT

Repeat starT

Slave Address D3(H)

RD

ReaD

Data Byte Count = X

ACK

Beginning Byte N

ACK

X Byte

ACK

Data Byte Count = X

ACK

Beginning Byte N

Byte N + X - 1

ACK

X Byte

ACK

P

stoP bit

Byte N + X - 1

N

P

IDT® PC MAIN CLOCK - CK540

Not acknowledge

stoP bit

1247C—06/16/11

10

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Byte 0 FS Readback, SS Enable, STOP Control Register

Bit

7

6

5

4

3

2

1

0

Pin

-

Name

FSLC

FSLB

CPU_SS_EN

LCD_Enable

SRC3_STOP

SRC2_STOP

SRC1_STOP

SRC0_STOP

Description

CPU Freq. Sel. Bit MSB

CPU Freq. Sel. Bit LSB

Spread spectrum enable for CPU/SRC/PCI outputs

Turns On LCD PLL

SRC 3 Stop Control

SRC 2 Stop Control

SRC 1 Stop Control

SRC 0 Stop Control

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

See Frequency Select Table

SS Disabled

Off

SS Enabled

On

Free Running

Stops with

PCI_STOP#

Assertion

Default

Latch

Latch

1

1

0

0

0

0

Byte 1 LCD Quick Config and CPU Stop ControlRegister

Bit

7

6

5

4

3

2

1

0

Pin

Name

CPU_ITP_STOP

CPU1_STOP

CPU0_STOP

LCD_SS_EN

LCD_SSC_SEL

LCD_CF2

LCD_CF1

LCD_CF0

Description

CPU_ITP Stop Control

CPU1 Stop Control

CPU0 Stop Control

Turns on SS for LCD PLL

Select down or center SSC

PLL3 Quick Config Bit 2

PLL3 Quick Config Bit 1

PLL3 Quick Config Bit 0

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Free Running

Off

Down spread

1

Stops with

CPU_STOP#

assertion

On

Center spread

See Table 2: LCD Quick Configuration

Default

0

1

1

1

0

0

0

1

Byte 2 Output Enable and Stop Control Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

PCI_F2_STOP

PCI1_STOP

PCI0_STOP

REF_OE

USB_OE

PCIF2_OE

PCI1_OE

PCI0_OE

Description

Free running PCI Stop Control

PCI1 Stop Control

PCI 0 Stop Control

Output enable for REF

Output enable for USB

Output enable for PCI2

Output enable for PCI1

Output enable for PCI0

Type

RW

RW

RW

RW

RW

RW

RW

RW

Description

Output enable for CPU_ITP

Output enable for CPU1

Output enable for CPU0

Reserved

Output enable for SRC4

Output enable for SRC4

Output enable for SRC4

Output enable for SRC4

0

Disabled

Disabled

Disabled

Disabled

Disabled

1

Stops with

PCI_STOP#

assertion

Output Enabled

Output Enabled

Output Enabled

Output Enabled

Output Enabled

Default

0

1

1

1

1

1

1

1

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Output Disabled

Output Disabled

Output Disabled

1

Output Enabled

Output Enabled

Output Enabled

Output

Output

Output

Output

Output

Output

Output

Output

Default

1

1

1

0

1

1

1

1

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

Output Disabled

Output Disabled

1

Output Enabled

Output Enabled

Not controlled by

CLKREQ#

Controlled by

CLKREQ#

Free Running

Output

Output

Output

Output

Output

Byte 3 Output Enable Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

CPU_ITP_OE

CPU1_OE

CPU0_OE

Reserved

SRC3_OE

SRC2_OE

SRC1_OE

SRC0_OE

Disabled

Disabled

Disabled

Disabled

Enabled

Enabled

Enabled

Enabled

Byte 4 Output Enable and CLKREQ# Control Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

DOT96_OE

LCD100_OE

Reserved

Reserved

SRC3_CR

SRC2_CR

SRC1_CR

SRC0_CR

Description

Output enable for DOT96

Output enable for LCD100

Reserved

Reserved

SRC3 CLKREQ3# Enable

SRC2 CLKREQ2# Enable

SRC1 CLKREQ1# Enable

SRC0 CLKREQ0# Enable

IDT® PC MAIN CLOCK - CK540

Default

1

1

0

0

0

0

0

0

1247C—06/16/11

11

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Byte 5 Drive Strength Control Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

PCI_F2 Strength

PCI1 Strength

PCI0 Strength

48MHz Strength

REF Strength

IO_VOUT2

IO_VOUT1

IO_VOUT0

Description

Sets the PCI_F2 output drive strength

Sets the PCI1 output drive strength

Sets the PCI0 output drive strength

Sets the 48MHz output drive strength

Sets the REF output drive strength

IO Output Voltage Select (Most Significant Bit)

IO Output Voltage Select

IO Output Voltage Select (Least Significant Bit)

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

1 Load

2 Loads

2 Loads

3 Loads

Description

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

Default

0

0

0

0

0

0

0

0

Description

Type

R

R

R

R

R

R

R

R

0

1

Default

X

X

X

X

0

0

0

1

0

1

Reserved

Reserved

Reserved

Reserved

Type

R

R

R

R

RW

RW

RW

RW

Default

0

0

1

1

0

0

0

1

Name

Description

Type

0

7

LCD_STOP

LCD Stop Control

RW

Free Running

6

5

4

3

2

1

0

Reserved

Reserved

Test Mode Select

Test Mode Entry

Reserved

Reserved

PLL1_SS

Reserved

Reserved

Allows test select, ignores Test Sel input pin

Enters into test mode, ignores input pin

Reserved

Reserved

PLL1 Spread Spectrum Mode

RW

RW

RW

RW

RW

RW

RW

See Table 3: V_IO Selection

(Default is 0.8V)

Default

1

1

1

1

1

1

0

1

Byte 6 Reserved Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Byte 7 Vendor ID/ Revision ID

Bit

7

6

5

4

3

2

1

0

Pin

Name

Rev Code Bit

Rev Code Bit

Rev Code Bit

Rev Code Bit

Vendor ID bit

Vendor ID bit

Vendor ID bit

Vendor ID bit

3

2

1

0

3

2

1

0

Revision ID

Vendor ID

ICS is 0001, binary

Vendor specific

Byte 8 Device ID Register

Bit

7

6

5

4

3

2

1

0

Pin

Name

Device_ID3

Device_ID2

Device_ID1

Device_ID0

Reserved

Reserved

Reserved

Reserved

Description

Package ID code

Devide ID = 0011 Hex

56-pin QFN

Byte 9 Test Mode Register

Bit

Pin

IDT® PC MAIN CLOCK - CK540

1

Stops with

PCI_STOP#

assertion

Outputs HI-Z

Normal operation

Outputs = REF/N

Test mode

Down-spread

Center-spread

Default

0

0

0

0

0

0

0

0

1247C—06/16/11

12

�9UMS9001

PC MAIN CLOCK - CK540

Advance Information

Test Clarification Table

Comments

TEST_SEL

HW PIN

Power-up w/ TEST_SEL = 1 to enter test mode

Cycle power to disable test mode

TEST_MODE -->low Vth input

TEST_MODE is a real time input

If TEST_SEL HW pin is 0 during power-up,

test mode can be invoked through B9b3.

If test mode is invoked by B9b3, only B9b4

is used to select HI-Z or REF/N

FSLB/TEST_Mode pin is not used.

Cycle power to disable test mode, one shot control

SW

HW

TEST

TEST_MODE ENTRY BIT

HW PIN

B9b3

REF/N or

HI-Z

B9b4

2.0V

>2.0V

>2.0V

X

0

0

1

0

X

X

X

0

0

1

0

OUTPUT

NORMAL

HI-Z

REF/N

REF/N

>2.0V

1

X

1

REF/N