SAM3X / SAM3A Series

Atmel | SMART ARM-based MCU

DATASHEET

Description

The Atmel | SMART SAM3X/A series is a member of a family of Flash

microcontrollers based on the high performance 32-bit ARM Cortex-M3 RISC

processor. It operates at a maximum speed of 84 MHz and features up to

512 Kbytes of Flash and up to 100 Kbytes of SRAM. The peripheral set includes a

High Speed USB Host and Device port with embedded transceiver, an Ethernet

MAC, 2 CANs, a High Speed MCI for SDIO/SD/MMC, an External Bus Interface

with NAND Flash Controller (NFC), 5 UARTs, 2 TWIs, 4 SPIs, as well as a PWM

timer, three 3-channel general-purpose 32-bit timers, a low-power RTC, a lowpower RTT, 256-bit General Purpose Backup Registers, a 12-bit ADC and a 12-bit

DAC.

The SAM3X/A devices have three software-selectable low-power modes: Sleep,

Wait and Backup. In Sleep mode, the processor is stopped while all other

functions can be kept running. In Wait mode, all clocks and functions are stopped

but some peripherals can be configured to wake up the system based on

predefined conditions. In Backup mode, only the RTC, RTT, and wake-up logic

are running.

The SAM3X/A series is ready for capacitive touch thanks to the QTouch library,

offering an easy way to implement buttons, wheels and sliders.

The SAM3X/A architecture is specifically designed to sustain high-speed data

transfers. It includes a multi-layer bus matrix as well as multiple SRAM banks,

PDC and DMA channels that enable it to run tasks in parallel and maximize data

throughput.

The device operates from 1.62V to 3.6V and is available in 100 and 144-lead

LQFP, 100-ball TFBGA and 144-ball LFBGA packages.

The SAM3X/A devices are particularly well suited for networking applications:

industrial and home/building automation, gateways.

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�1.

2

Features

Core

̶ ARM Cortex-M3 revision 2.0 running at up to 84 MHz

̶ Memory Protection Unit (MPU)

̶ Thumb-2 instruction set

̶ 24-bit SysTick Counter

̶ Nested Vector Interrupt Controller

Memories

̶ 256 to 512 Kbytes embedded Flash, 128-bit wide access, memory accelerator, dual bank

̶ 32 to 100 Kbytes embedded SRAM with dual banks

̶ 16 Kbytes ROM with embedded bootloader routines (UART, USB) and IAP routines

̶ Static Memory Controller (SMC): SRAM, NOR, NAND support. NFC with 4 Kbyte RAM buffer and ECC

System

̶ Embedded voltage regulator for single supply operation

̶ Power-on-Reset (POR), Brown-out Detector (BOD) and Watchdog for safe reset

̶ Quartz or ceramic resonator oscillators: 3 to 20 MHz main and optional low power 32.768 kHz for RTC or device

clock

̶ High precision 8/12 MHz factory trimmed internal RC oscillator with 4 MHz default frequency for fast device

startup

̶ Slow Clock Internal RC oscillator as permanent clock for device clock in low-power mode

̶ One PLL for device clock and one dedicated PLL for USB 2.0 High Speed Mini Host/Device

̶ Temperature Sensor

̶ Up to 17 peripheral DMA (PDC) channels and 6-channel central DMA plus dedicated DMA for High-Speed USB

Mini Host/Device and Ethernet MAC

Low-power Modes

̶ Sleep, Wait and Backup modes, down to 2.5 µA in Backup mode with RTC, RTT, and GPBR

Peripherals

̶ USB 2.0 Device/Mini Host: 480 Mbps, 4 Kbyte FIFO, up to 10 bidirectional Endpoints, dedicated DMA

̶ Up to 4 USARTs (ISO7816, IrDA®, Flow Control, SPI, Manchester and LIN support) and one UART

̶ 2 TWI (I2C compatible), up to 6 SPIs, 1 SSC (I2S), 1 HSMCI (SDIO/SD/MMC) with up to 2 slots

̶ 9-channel 32-bit Timer Counter (TC) for capture, compare and PWM mode, Quadrature Decoder Logic and 2-bit

Gray Up/Down Counter for Stepper Motor

̶ Up to 8-channel 16-bit PWM (PWMC) with Complementary Output, Fault Input, 12-bit Dead Time Generator

Counter for Motor Control

̶ 32-bit low-power Real-time Timer (RTT) and low-power Real-time Clock (RTC) with calendar and alarm features

̶ 256-bit General Purpose Backup Registers (GPBR)

̶ 16-channel 12-bit 1 msps ADC with differential input mode and programmable gain stage

̶ 2-channel 12-bit 1 msps DAC

̶ Ethernet MAC 10/100 (EMAC) with dedicated DMA

̶ 2 CAN Controllers with 8 Mailboxes

̶ True Random Number Generator (TRNG)

̶ Register Write Protection

I/O

̶ Up to 103 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and ondie Series Resistor Termination

̶ Up to six 32-bit Parallel Input/Outputs (PIO)

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�

1.1

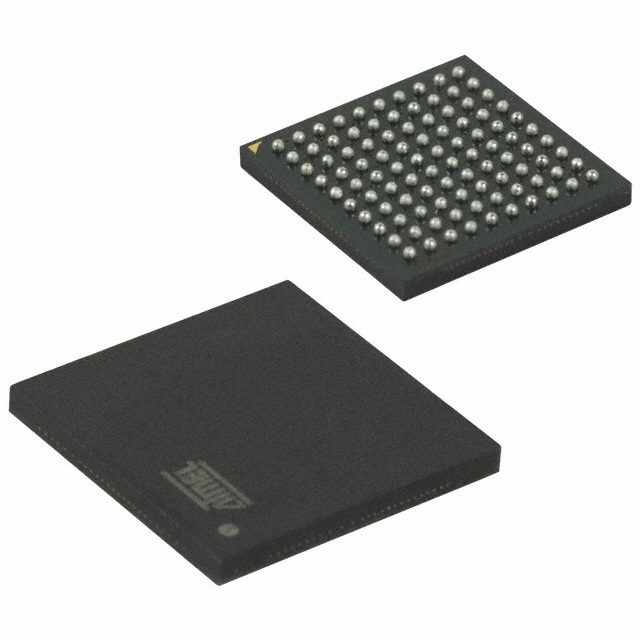

Packages

̶ 100-lead LQFP – 14 x 14 mm, pitch 0.5 mm

̶ 100-ball TFBGA – 9 x 9 mm, pitch 0.8 mm

̶ 144-lead LQFP – 20 x 20 mm, pitch 0.5 mm

̶ 144-ball LFBGA – 10 x 10 mm, pitch 0.8 mm

Configuration Summary

The SAM3X/A series devices differ in memory sizes, package and features list. Table 1-1 summarizes the

configurations.

Table 1-1.

Configuration Summary

Feature

SAM3X8E

SAM3X8C

SAM3X4E

SAM3X4C

SAM3A8C

SAM3A4C

Flash

2 x 256 Kbytes

2 x 256 Kbytes

2 x 128 Kbytes

2 x 128 Kbytes

2 x 256 Kbytes

2 x 128 Kbytes

SRAM

64 + 32 Kbytes

64 + 32 Kbytes

32 + 32 Kbytes

32 + 32 Kbytes

64 + 32 Kbytes

32 + 32 Kbytes

NAND Flash

Controller (NFC)

Yes

–

Yes

–

–

–

NFC SRAM(1)

4 Kbytes

–

4 Kbytes

–

–

–

LQFP144

LQFP100

LQFP144

LQFP100

LQFP100

LQFP100

LFBGA144

TFBGA100

LFBGA144

TFBGA100

TFBGA100

TFBGA100

Number of PIOs

103

63

103

63

63

63

SHDN Pin

Yes

No

Yes

No

No

No

EMAC

MII/RMII

RMII

MII/RMII

RMII

–

–

External Bus

Interface

16-bit data,

8 chip selects,

23-bit address

–

16-bit data,

8 chip selects,

23-bit address

–

–

–

SDRAM Controller(6)

–

–

–

–

–

–

Central DMA

6

Package

4

(2)

12-bit ADC

16 ch.

12-bit DAC

2 ch.

32-bit Timer

PDC Channels

USART/UART

Notes:

9 ch.

(3)

17

3/2

(5)

6

16 ch.

(2)

2 ch.

(4)

4

16 ch.

(2)

2 ch.

(3)

4

16 ch.

(2)

2 ch.

(4)

4

16 ch.

(2)

2 ch.

(3)

2 ch.

9 ch.(3)

9 ch.

9 ch.

9 ch.

15

17

15

15

15

3/1

3/1

3/1

3/1

(5)

3/2

9 ch.

16 ch.(2)

SPI

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

1 SPI controller,

4 chip selects +

3 USART with

SPI mode

HSMCI

1 slot, 8 bits

1 slot, 4 bits

1 slot, 8 bits

1 slot, 4 bits

1 slot, 4 bits

1 slot, 4 bits

1.

2.

3.

4.

5.

6.

4 Kbytes RAM buffer of the NFC which can be used by the core if not used by the NFC

One channel is reserved for internal temperature sensor

Six TC channels are accessible through PIO

Three TC channels are accessible through PIO

USART3 in UART mode (RXD3 and TXD3 available)

Available only on SAM3X8H in LFBGA217 package, which is mounted on SAM3X-EK evaluation kit for SAM3X and SAM3A

series. The SAM3X8H device is not commercially available.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

3

�SAM3X/A Block Diagram

ND NA

AN

A

G

DA

VD

N

DO

DI

VD

VD

UT

SAM3A4/8C (100 pins) Block Diagram

TD

TDI

O

TM /TR

S A

TC /SW CE

K/ D SW

SW IO O

CL

K

Figure 2-1.

JT

AG

SE

L

2.

Voltage

Regulator

System Controller

TST

PCK0-PCK2

PLLA

UPLL

XIN

XOUT

JTAG & Serial Wire

PMC

In-Circuit Emulator

OSC

WDT

RC

12/8/4 M

SM

24-bit

N

Cortex-M3 Processor SysTick Counter V

fmax 84 MHz

I

C

MPU

SUPC

FWUP

XIN32

XOUT32

I/D

OSC 32K

RC 32K

ERASE

Flash

SRAM0

SRAM1

ROM

2x256 Kbytes 64 Kbytes 32 Kbytes

2x128 Kbytes 32 Kbytes 32 Kbytes 16 Kbytes

2x64 Kbytes 16 Kbytes 16 Kbytes

S

6-layer AHB Bus Matrix fmax 84MHz

RTT

Low Power

Peripheral

Bridge

RTC

VDDBU

POR

Peripheral

DMA

Controller

USB

DMA FIFO Mini Host/

Device HS

HS UTMI

Transeiver

8

GPBR

VBUS

DFSDM

DFSDP

DHSDM

DHSDP

UOTGVBOF

UOTGID

VDDCORE

RSTC

VDDUTMI

NRST

PIOA

PIOB

PIOC

4-Channel

DMA

TRNG

TWCK0

TWD0

TWI0

TWCK1

TWD1

TWI1

UART

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

RXD2

TXD2

SCK2

RTS2

CTS2

PDC

DMA

USART0

PDC

DMA

USART1

PDC

USART2

PDC

CANRX0

CANTX0

CAN0

CAN1

PIO

TCLK[0:2]

PDC

DMA

URXD

UTXD

CANRX1

CANTX1

DMA

PDC

TIOA[0:2]

TIOB[0:2]

Timer Counter 0

TC[0..2]

TCLK[3:5]

Timer Counter 1

TIOA[3:5]

TIOB[3:5]

TC[3..5]

High Performance

Peripheral

Bridge

DMA

SPI0

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

Timer Counter 2

TC[6..8]

DMA

PWMH[0:3]

PWML[0:7]

PWMFI[0:1]

ADTRG

AD[0..14]

ADVREF

DAC0

DAC1

DATRG

4

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

DMA

PWM

SSC

PDC

Temp.

Sensor

TF

TK

TD

RD

RK

RF

DMA

ADC

PDC

DAC

PDC

HSMCI

MCCK

MCCDA

MCDA[0..3]

�DO

UT

VD

DA

G N

ND A

AN

A

VD

VD

DI

N

JT

AG

SE

L

TD

TDI

O

TM /TR

S A

TC /SW CE

K/ D SW

SW IO O

CL

K

SAM3X4/8C (100 pins) Block Diagram

Voltage

Regulator

System Controller

TST

PCK0-PCK2

JTAG & Serial Wire

PLLA

UPLL

XIN

XOUT

PMC

OSC

12M

In-circuit Emulator

24-bit

N

Cortex-M3 Processor SysTick Counter V

fmax 84 MHz

I

C

WDT

RC

12/8/4 M

SM

MPU

SUPC

FWUP

XIN32

XOUT32

I/D

OSC 32K

Flash

2x256 Kbytes

2x128 Kbytes

2x64 Kbytes

SRAM1

SRAM0

ROM

64 Kbytes 32 Kbytes

32 Kbytes 32 Kbytes 16 Kbytes

16 Kbytes 16 Kbytes

S

6-layer AHB Bus Matrix fmax 84 MHz

RC 32k

ERASE

RTT

Low Power

Peripheral

Bridge

RTC

VDDBU

POR

Peripheral

DMA

Controller

USB

DMA FIFO Mini Host/

Device HS

HS UTMI

Transceiver

8

GPBR

VDDCORE

RSTC

VDDUTMI

FIFO

Ethernet

MAC

DMADMA

128-byte TX

RMII

NRST

PIOA

128-byte RX

PIOB

PIOC

TWI0

DMA

PDC

TWCK1

TWD1

TWI1

PDC

URXD

UTXD

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

RXD2

TXD2

SCK2

RTS2

CTS2

UART

PDC

DMA

TWCK0

TWD0

USART0

TCLK[0:2]

EREFCK

ETXEN

ECRSDV

ERXER

ERX0-ERX1

ETX0-ETX1

EMDC

EMDIO

PDC

DMA

USART1

PDC

USART2

PDC

CANRX0

CANTX0

CANRX1

CANTX1

VBUS

DFSDM

DFSDP

DHSDM

DHSDP

UOTGVBOF

UOTGID

4-Channel

DMA

TRNG

CAN0

CAN1

PIO

Figure 2-2.

Timer Counter 0

TIOA[0:2]

TIOB[0:2]

TC[0..2]

High Performance

Peripherals

Bridge

SPI0

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

SSC

TF

TK

TD

RD

RK

RF

DMA

Timer Counter 1

TC[3..5]

Timer Counter 2

TC[6..8]

DMA

PWMH[0:3]

PWML[0:3]

PWMFI[0:1]

ADTRG

AD[0..14]

ADVREF

DAC0

DAC1

DATRG

PWM

DMA

PDC

ADC

Temp.

Sensor

DMA

PDC

HSMCI

DAC

PDC

MCCK

MCCDA

MCDA[0..3]

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

5

�UT

D

G AN

ND A

AN

A

DO

VD

VD

JT

VD

AG

DI

N

SE

L

SAM3X4/8E (144 pins) Block Diagram

TD

I

TD

O

TM /TR

S AC

TC /SW ES

K/ D I W

SW O O

CL

K

Figure 2-3.

Voltage

Regulator

System Controller

TST

PCK0-PCK2

JTAG & Serial Wire

PLLA

UPLL

XIN

XOUT

PMC

In-circuit Emulator

OSC

WDT

RC

12/8/4 M

SHDN

FWUP

XIN32

XOUT32

SM

24-bit

N

Cortex-M3 Processor SysTick Counter V

fmax 84 MHz

I

C

MPU

SUPC

I/D

OSC 32K

SRAM1

SRAM0

ROM

64 Kbytes 32 Kbytes

32 Kbytes 32 Kbytes 16 Kbytes

16 Kbytes 16 Kbytes

S

6-layer AHB Bus Matrix fmax 84 MHz

RC 32K

ERASE

Flash

2x256 Kbytes

2x128 Kbytes

2x64 Kbytes

8

GPBR

Low Power

Peripheral

Bridge

RTC

VDDBU

POR

Peripheral

DMA

Controller

USBOTG

DMA FIFO Device

HS

VBUS

DFSDM

DFSDP

DHSDM

DHSDP

UOTGVBOF

UOTGID

HS UTMI

Transceiver

RTT

NRSTB

VDDCORE

FIFO

Ethernet

DMA

MAC

128-byte TX

128-byte RX MII/RMII

NRST

PIOA

PIOB

PIOC

PIOD

PIOE

6-Channel

DMA

TRNG

TWCK0

TWD0

TWI0

DMA

PDC

EBI

TWCK1

TWD1

TWI1

PDC

8-bit/16-bit

URXD

UTXD

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

RXD2

TXD2

SCK2

RTS2

CTS2

UART

PDC

DMA

NAND Flash

USART0

USART1

PDC

Static Memory

Controller

PDC

ECC

Controller

USART3

CAN0

4 Kbyte FIFO

NANDRDY

NANDOE

NANDWE

NWAIT

PIO

CAN1

TIOA[0:2]

TIOB[0:2]

Timer Counter 0

TC[0..2]

High Performance

Peripherals

Bridge

DMA

Timer Counter 1

SPI0

TC[3..5]

TCLK[6:8]

TIOA[6:8]

TIOB[6:8]

TC[6..8]

PWM

DMA

ADVREF

DAC0

DAC1

DATRG

SSC

PDC

Temp.

.

ADTRG

AD[0..14]

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

Timer Counter 2

DMA

PWMH[0:6]

PWML[0:7]

PWMFI[0:2]

6

D[15:0]

A0/NBS0

A[0:23]

A21/NANDALE

A22/NANDCLE

A16

A17

NCS0

NCS1

NCS2

NCS3

NRD

NWR0/NWE

NWR1

USART2

PDC

TCLK[0:2]

PIO

PDC

DMA

RXD3

TXD3

CANRX0

CANTX0

CANRX1

CANTX1

ETXCK-ERXCK-EREFCK

ETXER-ETXDV

ECRS-ECOL, ECRSDV

ERXER-ERXDV

ERX0-ERX3

ETX0-ETX3

EMDC

EMDIO

EF100

RSTC

VDDUTMI

DMA

ADC Sensor

PDC

DAC

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

TF

TK

TD

RD

RK

RF

PDC

HSMCI

MCCK

MCCDA

MCDA[0..7]

�N

ND A

AN

A

UT

G

DA

VD

DO

DI

VD

VD

N

JT

AG

SE

L

TD

I

TD

O

TM /TR

S A

TC /S CE

K/ WD SW

SW IO O

CL

K

SAM3X8H (217 pins) Block Diagram (not commercially available)

Voltage

Regulator

System Controller

TST

PCK0-PCK2

JTAG & Serial Wire

PLLA

UPLL

XIN

XOUT

PMC

In-Circuit Emulator

OSC

WDT

RC

12/8/4 M

SHDN

FWUP

XIN32

XOUT32

SM

24-bit

N

Cortex-M3 Processor SysTick Counter V

fmax 84 MHz

I

C

MPU

SUPC

I/D

OSC 32K

Flash

SRAM0

2x256 Kbytes

2x128 Kbytes

2x64 Kbytes

64 Kbytes

32 Kbytes

16 Kbytes

SRAM1

ROM

32 Kbytes

32 Kbytes 16 Kbytes

16 Kbytes

S

6-layer AHB Bus Matrix fmax 84 MHz

RC 32k

ERASE

8

GPBR

RTT

Low Power

Peripheral

Bridge

RTC

VDDBU

POR

Peripheral

DMA

Controller

USB

DMA FIFO Mini Host/

Device HS

VBUS

DFSDM

DFSDP

DHSDM

DHSDP

UOTGVBOF

UOTGID

HS UTMI

Transceiver

NRSTB

VDDCORE

RSTC

NRST

PIOA

PIOB

PIOC

PIOD

PIOE

PIOF

Mini Host/

Device HS

6-Channel

DMA

TRNG

TWCK0

TWD0

TWI0

DMA

PDC

EBI

TWCK1

TWD1

TWI1

PDC

8-bit/16-bit

DRXD

DTXD

RXD0

TXD0

SCK0

RTS0

CTS0

RXD1

TXD1

SCK1

RTS1

CTS1

RXD2

TXD2

SCK2

RTS2

CTS2

RXD3

TXD3

SCK3

RTS3

CTS3

CANRX0

CANTX0

UART

PDC

DMA

NAND Flash

CANRX1

CANTX1

CAN1

TCLK[0:2]

TIOA[0:2]

TIOB[0:2]

TCLK[3:5]

TIOA[3:5]

TIOB[3:5]

USART0

SDRAM

Controller

PDC

DMA

USART1

PDC

Static Memory

Controller

PDC

ECC

Controller

USART2

USART3

PDC

CAN0

4 Kbyte FIFO

TIOA[6:8]

TIOB[6:8]

TC[0..2]

High Performance

Peripherals

Bridge

DMA

Timer Counter 1

SPI0

TC[3..5]

Timer Counter 2

SPI1

TC[6..8]

DMA

PWMH[0:7]

PWML[0:7]

PWMFI[0:2]

ADTRG

AD[0..14]

ADVREF

DAC0

DAC1

DATRG

PWM

D[15:0]

A0/NBS0

A[0:23]

A21/NANDALE

A22/NANDCLE

A16/BA0

A17/BA1

NCS0

NCS1

NCS2

NCS3

NRD

NWR0/NWE

NWR1/NBS1

SDCKE

RAS

CAS

SDWE

SDCS

NCS4

NCS5

NCS6

NCS7

NANDOE

NANDWE

NWAIT

SDCK

Timer Counter 0

DMA

TCLK[6:8]

ETXCK-ERXC

ETXEN-ETXER

ECRS-ECOL, ECRSDV

ERXER-ERXDV

ERX0-ERX3

ETX0-ETX3

EMDC

EMDIO

EF100

USB

FIFO

Ethernet

Mini Host/

DMA 128-byte

TX HS MAC

Device

128-byteUSB

RX MII/RMII

PIO

VDDUTMI

PIO

Figure 2-4.

DMA

SSC

PDC

Temp.

ADC Sensor

DMA

PDC

DAC

PDC

HSMCI

SPI0_NPCS0

SPI0_NPCS1

SPI0_NPCS2

SPI0_NPCS3

SPI0_MISO

SPI0_MOSI

SPI0_SPCK

SPI1_NPCS0

SPI1_NPCS1

SPI1_NPCS2

SPI1_NPCS3

SPI1_MISO

SPI1_MOSI

SPI1_SPCK

TF

TK

TD

RD

RK

RF

MCDB[0..3]

MCCDB

MCCK

MCCDA

MCDA[0..7]

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

7

�3.

Signal Description

Table 3-1 gives details on the signal names classified by peripheral.

Table 3-1.

Signal Description List

Signal Name

Function

Type

Active

Level

Voltage

Reference

Comments

Power Supplies

VDDIO

Peripherals I/O Lines Power Supply

Power

1.62V to 3.6V

VDDUTMI

USB UTMI+ Interface Power

Supply

Power

3.0V to 3.6V

VDDOUT

Voltage Regulator Output

Power

VDDIN

Voltage Regulator, ADC and DAC

Power Supply

Power

GNDUTMI

USB UTMI+ Interface Ground

Ground

VDDBU

Backup I/O Lines Power Supply

Power

GNDBU

Backup Ground

Ground

VDDPLL

PLL A, UPLL and Oscillator Power

Supply

Power

GNDPLL

PLL A, UPLL and Oscillator Ground

Ground

VDDANA

ADC and DAC Analog Power

Supply

Power

GNDANA

ADC and DAC Analog Ground

Ground

VDDCORE

Core Chip Power Supply

Power

GND

Ground

Ground

1.62V to 3.6V

1.62 V to 1.95V

2.0V to 3.6V

1.62V to 1.95V

Clocks, Oscillators and PLLs

XIN

Main Oscillator Input

Input

XOUT

Main Oscillator Output

XIN32

Slow Clock Oscillator Input

XOUT32

Slow Clock Oscillator Output

Output

VBG

Bias Voltage Reference

Analog

PCK0–PCK2

Programmable Clock Output

Output

Output

Input

VDDPLL

VDDBU

Shutdown, Wakeup Logic

0: Device is in backup mode

SHDN

Shut-Down Control

FWUP

Force Wake-up Input

8

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

Output

VDDBU

1: Device is running (not in

backup mode)

Input

VDDBU

Needs external pull-up

�Table 3-1.

Signal Description List (Continued)

Signal Name

Function

Type

Active

Level

Voltage

Reference

Comments

ICE and JTAG

TCK/SWCLK

Test Clock/Serial Wire Clock

Input

TDI

Test Data In

Input

TDO/TRACESWO

Test Data Out / Trace

Asynchronous Data Out

Reset State:

VDDIO

Output

- SWJ-DP Mode

- Internal pull-up disabled(1)

TMS/SWDIO

Test Mode Select /Serial Wire

Input/Output

JTAGSEL

JTAG Selection

Input / I/O

High

VDDBU

Permanent Internal

pull-down

High

VDDIO

Pull-down resistor

I/O

Low

VDDIO

Pull-up resistor

Low

VDDBU

Pull-up resistor

VDDBU

Pull-down resistor

Input

Flash Memory

ERASE

Flash and NVM Configuration Bits

Erase Command

Input

Reset/Test

NRST

Microcontroller Reset

NRSTB

Asynchronous Microcontroller

Reset

Input

TST

Test Mode Select

Input

Universal Asynchronous Receiver Transceiver - UART

URXD

UART Receive Data

Input

UTXD

UART Transmit Data

Output

PIO Controller - PIOA - PIOB - PIOC - PIOD - PIOE - PIOF

PA0–PA31

PB0–PB31

PC0–PC30

Parallel IO Controller A

Parallel IO Controller B

Parallel IO Controller C

I/O

Schmitt Trigger(3)

Reset State:

- PIO Input

- Internal pull-up enabled

I/O

Schmitt Trigger(4)

Reset State:

- PIO Input

- Internal pull-up enabled

I/O

Schmitt Trigger(5)

Reset State:

- PIO Input

- Internal pull-up enabled

VDDIO

PD0–PD30

PE0–PE31

PF0–PF6

Parallel IO Controller D

Parallel IO Controller E

Parallel IO Controller F

I/O

Schmitt Trigger(6)

Reset State:

- PIO Input

- Internal pull-up enabled

I/O

Schmitt Trigger(7)

Reset State:

- PIO Input

- Internal pull-up enabled

I/O

Schmitt Trigger(7)

Reset State:

- PIO Input

- Internal pull-up enabled

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

9

�Table 3-1.

Signal Description List (Continued)

Signal Name

Function

Type

Active

Level

Voltage

Reference

Comments

External Memory Bus

D0–D15

Data Bus

I/O

A0–A23

Address Bus

Pulled-up input at reset

Output

0 at reset

Static Memory Controller - SMC

NCS0–NCS7

Chip Select Lines

Output

Low

NWR0–NWR1

Write Signal

Output

Low

NRD

Read Signal

Output

Low

NWE

Write Enable

Output

Low

NBS0–NBS1

Byte Mask Signal

Output

Low

NWAIT

External Wait Signal

Input

Low

NAND Flash Controller - NFC

NANDOE

NAND Flash Output Enable

Output

Low

NANDWE

NAND Flash Write Enable

Output

Low

NANDRDY

NAND Ready

NANDCLE

NAND Flash Command Line

Enable

Output

Low

NANDALE

NAND Flash Address Line Enable

Output

Low

Input

SDRAM Controller - SDRAMC

SDCK

SDRAM Clock

Output

Tied low after reset

SDCKE

SDRAM Clock Enable

Output

High

SDCS

SDRAM Controller Chip Select Line

Output

Low

BA[1:0]

Bank Select

Output

SDWE

SDRAM Write Enable

Output

Low

RAS - CAS

Row and Column Signal

Output

Low

NBS[1:0]

Byte Mask Signals

Output

Low

SDA10

SDRAM Address 10 Line

Output

High Speed Multimedia Card Interface - HSMCI

MCCK

Multimedia Card Clock

I/O

MCCDA

Multimedia Card Slot A Command

I/O

MCDA0–MCDA7

Multimedia Card Slot A Data

I/O

MCCDB

Multimedia Card Slot B Command

I/O

MCDB0–MCDB3

Multimedia Card Slot A Data

I/O

Universal Synchronous Asynchronous Receiver Transmitter - USARTx

SCKx

USARTx Serial Clock

I/O

TXDx

USARTx Transmit Data

I/O

RXDx

USARTx Receive Data

Input

RTSx

USARTx Request To Send

CTSx

USARTx Clear To Send

10

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

Output

Input

�Table 3-1.

Signal Name

Signal Description List (Continued)

Function

Type

Active

Level

Voltage

Reference

Comments

Ethernet MAC 10/100 - EMAC

EREFCK

Reference Clock

Input

RMII only

ETXCK

Transmit Clock

Input

MII only

ERXCK

Receive Clock

Input

MII only

ETXEN

Transmit Enable

Output

ETX0–ETX3

Transmit Data

Output

ETX0–ETX1

only in RMII

ETXER

Transmit Coding Error

Output

MII only

ERXDV

Receive Data Valid

Input

MII only

ECRSDV

Carrier Sense and Data Valid

Input

RMII only

ERX0–ERX3

Receive Data

Input

ERX0–ERX1

only in RMII

ERXER

Receive Error

Input

ECRS

Carrier Sense

Input

MII only

ECOL

Collision Detected

Input

MII only

EMDC

Management Data Clock

EMDIO

Management Data Input/Output

Output

I/O

CAN Controller - CANx

CANRXx

CAN Input

CANTXx

CAN Output

Input

Output

Synchronous Serial Controller - SSC

TD

SSC Transmit Data

Output

RD

SSC Receive Data

Input

TK

SSC Transmit Clock

I/O

RK

SSC Receive Clock

I/O

TF

SSC Transmit Frame Sync

I/O

RF

SSC Receive Frame Sync

I/O

Timer/Counter - TC

TCLKx

TC Channel x External Clock Input

Input

TIOAx

TC Channel x I/O Line A

I/O

TIOBx

TC Channel x I/O Line B

I/O

Pulse Width Modulation Controller - PWMC

PWMHx

PWM Waveform Output High for

channel x

PWMLx

PWM Waveform Output Low for

channel x

PWMFIx

PWM Fault Input for channel x

Output

Output

Only output in

complementary mode when

dead time insertion is

enabled

Input

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

11

�Table 3-1.

Signal Description List (Continued)

Signal Name

Function

Type

Active

Level

Voltage

Reference

Comments

Serial Peripheral Interface - SPIx

SPIx_MISO

Master In Slave Out

I/O

SPIx_MOSI

Master Out Slave In

I/O

SPIx_SPCK

SPI Serial Clock

I/O

SPIx_NPCS0

SPI Peripheral Chip Select 0

I/O

Low

Output

Low

SPIx_NPCS1–SPIx_NPCS3 SPI Peripheral Chip Select

Two-Wire Interface - TWIx

TWDx

TWIx Two-wire Serial Data

I/O

TWCKx

TWIx Two-wire Serial Clock

I/O

Analog-to-Digital Converter - ADC

AD0–AD14

Analog Inputs

Analog

ADTRG

ADC Trigger

Input

ADVREF

ADC and DAC Reference

Analog

Digital-to-Analog Converter Controller - DACC

DAC0

DAC channel 0 analog output

Analog

DAC1

DAC channel 1 analog output

Analog

DATRG

DAC Trigger

Fast Flash Programming Interface - FFPI

PGMEN0–PGMEN2

Programming Enabling

Input

VDDIO

PGMM0–PGMM3

Programming Mode

Input

VDDIO

PGMD0–PGMD15

Programming Data

I/O

VDDIO

PGMRDY

Programming Ready

Output

High

VDDIO

PGMNVALID

Data Direction

Output

Low

VDDIO

PGMNOE

Programming Read

Input

Low

VDDIO

PGMCK

Programming Clock

Input

PGMNCMD

Programming Command

Input

VDDIO

Low

VDDIO

USB High Speed Device

VBUS

USB Bus Power Measurement Mini

Host/Device

Analog

DFSDM

USB Full Speed Data -

Analog

VDDUTMI

DFSDP

USB Full Speed Data +

Analog

VDDUTMI

DHSDM

USB High Speed Data -

Analog

VDDUTMI

DHSDP

USB High Speed Data +

Analog

VDDUTMI

UOTGVBOF

USB VBus On/Off: Bus Power

Control Port

USB Identification: Mini Connector

VDDIO

Identification Port

1. TDO pin is set in input mode when the Cortex-M3 Core is not in debug mode. Thus the internal pull-up corresponding to this

PIO line must be enabled to avoid current consumption due to floating input.

2. PIOA: Schmitt Trigger on all, except PA0, PA9, PA26, PA29, PA30, PA31

3. PIOB: Schmitt Trigger on all, except PB14 and PB22

UOTGID

Notes:

12

VDDIO

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�4.

5.

6.

7.

3.1

PIOC: Schmitt Trigger on all, except PC2 to PC9, PC15 to PC24

PIOD: Schmitt Trigger on all, except PD10 to PD30

PIOE: Schmitt Trigger on all, except PE0 to PE4, PE15, PE17, PE19, PE21, PE23, PE25, PE29

PIOF: Schmitt Trigger on all PIOs

Design Considerations

To facilitate schematic capture when using a SAM3X/A design, refer to the application note Atmel AT03462:

ATSAM3X and ATSAM3A Series - Checklist (literature No. 42187) available on www.atmel.com.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

13

�4.

Package and Pinout

4.1

SAM3A4/8C and SAM3X4/8C Package and Pinout

The SAM3A4/8C and SAM3X4/8C are available in 100-lead LQFP and 100-ball TFBGA packages.

4.1.1

100-lead LQFP Package Outline

Figure 4-1.

Orientation of the 100-lead LQFP Package

51

75

76

50

100

26

25

1

4.1.2

100-ball TFBGA Package Outline

Figure 4-2.

Orientation of the 100-ball TFBGA Package

TOP VIEW

10

9

8

7

6

5

4

3

2

1

A B C D E F G H J K

BALL A1

14

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�4.1.3

100-lead LQFP Pinout

Table 4-1.

100-lead LQFP SAM3A4/8C and SAM3X4/8C Pinout

1

PB26

26

DHSDP

51

VDDANA

76

PA26

2

PA9

27

DHSDM

52

GNDANA

77

PA27

3

PA10

28

VBUS

53

ADVREF

78

PA28

4

PA11

29

VBG

54

PB15

79

PA29

5

PA12

30

VDDUTMI

55

PB16

80

PB0

6

PA13

31

DFSDP

56

PA16

81

PB1

7

PA14

32

DFSDM

57

PA24

82

PB2

8

PA15

33

GNDUTMI

58

PA23

83

PB3

9

PA17

34

VDDCORE

59

PA22

84

PB4

10

VDDCORE

35

JTAGSEL

60

PA6

85

PB5

11

VDDIO

36

XIN32

61

PA4

86

PB6

12

GND

37

XOUT32

62

PA3

87

PB7

13

PA0

38

TST

63

PA2

88

PB8

14

PA1

39

VDDBU

64

PB12

89

VDDCORE

15

PA5

40

FWUP

65

PB13

90

VDDIO

16

PA7

41

GND

66

PB17

91

GND

17

PA8

42

VDDOUT

67

PB18

92

PB9

18

PB28

43

VDDIN

68

PB19

93

PB10

19

PB29

44

GND

69

PB20

94

PB11

20

PB30

45

VDDCORE

70

PB21

95

PC0

21

PB31

46

PB27

71

VDDCORE

96

PB14

22

GNDPLL

47

NRST

72

VDDIO

97

PB22

23

VDDPLL

48

PA18

73

GND

98

PB23

24

XOUT

49

PA19

74

PA21

99

PB24

25

XIN

50

PA20

75

PA25

100

PB25

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

15

�4.1.4

100-ball TFBGA Pinout

Table 4-2.

100-ball TFBGA SAM3X4/8E Package and Pinout

A1

PB26

C6

PB11

F1

VDDPLL

H6

NRST

A2

PB24

C7

PB8

F2

GNDPLL

H7

PA19

A3

PB22

C8

PB4

F3

PB30

H8

PA4

A4

PB14

C9

PB0

F4

PB29

H9

PA6

A5

PC0

C10

PA25

F5

GND

H10

PA22

A6

PB9

D1

PA5

F6

GND

J1

VBUS

A7

PB6

D2

PA0

F7

VDDIO

J2

DHSDP

A8

PB2

D3

PA1

F8

PB13

J3

DHSDM

A9

PA28

D4

VDDCORE

F9

PB17

J4

JTAGSEL

A10

PA26

D5

VDDIO

F10

PB18

J5

XIN32

B1

PA11

D6

VDDCORE

G1

XOUT

J6

VDDIN

B2

PB25

D7

VDDCORE

G2

VDDUTMI

J7

PA23

B3

PB23

D8

PB5

G3

PB31

J8

PA24

B4

PA10

D9

PB1

G4

GNDBU

J9

PB16

B5

PA9

D10

PA21

G5

PB27

J10

PA16

B6

PB10

E1

PB28

G6

PA18

K1

VBG

B7

PB7

E2

PA7

G7

PA20

K2

DFSDP

B8

PB3

E3

PA8

G8

PA3

K3

DFSDM

B9

PA29

E4

VDDCORE

G9

PA2

K4

VDDCORE

B10

PA27

E5

GND

G10

PB12

K5

XOUT32

C1

PA12

E6

GND

H1

XIN

K6

VDDOUT

C2

PA14

E7

VDDIO

H2

GNDUTMI

K7

VDDANA

C3

PA13

E8

PB19

H3

TST

K8

GNDANA

C4

PA17

E9

PB20

H4

VDDBU

K9

ADVREF

C5

PA15

E10

PB21

H5

FWUP

K10

PB15

16

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�4.2

SAM3X4/8E Package and Pinout

The SAM3X4/8E is available in 144-lead LQFP and 144-ball LFBGA packages.

4.2.1

144-lead LQFP Package Outline

Figure 4-3.

Orientation of the 144-lead LQFP Package

73

108

109

72

144

37

36

1

4.2.2

144-ball LFBGA Package Outline

The 144-ball LFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are 10 x 10 x

1.4 mm.

Figure 4-4.

Orientation of the 144-ball LFBGA Package

TOP VIEW

12

11

10

9

8

7

6

5

4

3

2

1

A B C D E F G H J

K L M

BALL A1

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

17

�4.2.3

144-lead LQFP Pinout

Table 4-3.

18

144-lead LQFP SAM3X4/8E Pinout

1

PB26

37

DHSDP

73

VDDANA

109

PA26

2

PA9

38

DHSDM

74

GNDANA

110

PA27

3

PA10

39

VBUS

75

ADVREF

111

PA28

4

PA11

40

VBG

76

PB15

112

PA29

5

PA12

41

VDDUTMI

77

PB16

113

PB0

6

PA13

42

DFSDP

78

PA16

114

PB1

7

PA14

43

DFSDM

79

PA24

115

PB2

8

PA15

44

GNDUTMI

80

PA23

116

PC4

9

PA17

45

VDDCORE

81

PA22

117

PC10

10

VDDCORE

46

JTAGSEL

82

PA6

118

PB3

11

VDDIO

47

NRSTB

83

PA4

119

PB4

12

GND

48

XIN32

84

PA3

120

PB5

13

PD0

49

XOUT32

85

PA2

121

PB6

14

PD1

50

SHDN

86

PB12

122

PB7

15

PD2

51

TST

87

PB13

123

PB8

16

PD3

52

VDDBU

88

PB17

124

VDDCORE

17

PD4

53

FWUP

89

PB18

125

VDDIO

18

PD5

54

GNDBU

90

PB19

126

GND

19

PD6

55

PC1

91

PB20

127

PB9

20

PD7

56

VDDOUT

92

PB21

128

PB10

21

PD8

57

VDDIN

93

PC11

129

PB11

22

PD9

58

GND

94

PC12

130

PC0

23

PA0

59

PC2

95

PC13

131

PC20

24

PA1

60

PC3

96

PC14

132

PC21

25

PA5

61

VDDCORE

97

PC15

133

PC22

26

PA7

62

VDDIO

98

PC16

134

PC23

27

PA8

63

PC5

99

PC17

135

PC24

28

PB28

64

PC6

100

PC18

136

PC25

29

PB29

65

PC7

101

PC19

137

PC26

30

PB30

66

PC8

102

PC29

138

PC27

31

PB31

67

PC9

103

PC30

139

PC28

32

PD10

68

PB27

104

VDDCORE

140

PB14

33

GNDPLL

69

NRST

105

VDDIO

141

PB22

34

VDDPLL

70

PA18

106

GND

142

PB23

35

XOUT

71

PA19

107

PA21

143

PB24

36

XIN

72

PA20

108

PA25

144

PB25

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�4.2.4

144-ball LFBGA Pinout

Table 4-4.

144-ball LFBGA SAM3X4/8E Pinout

A1

PA9

D1

PA17

G1

PA5

K1

VDDCORE

A2

PB23

D2

PD0

G2

PA7

K2

GNDUTMI

A3

PB14

D3

PA11

G3

PA8

K3

VDDPLL

A4

PC26

D4

PA15

G4

PA1

K4

NRSTB

A5

PC24

D5

PA14

G5

GND

K5

SHDN

A6

PC20

D6

PC27

G6

GND

K6

PC3

A7

PB10

D7

PC25

G7

GND

K7

PC6

A8

PB6

D8

VDDIO

G8

PC16

K8

PC7

A9

PB4

D9

PB5

G9

PC15

K9

PA18

A10

PC4

D10

PB0

G10

PC13

K10

PA23

A11

PA28

D11

PC30

G11

PB13

K11

PA16

A12

PA27

D12

PC19

G12

PB18

K12

PA24

B1

PA10

E1

PD1

H1

XOUT

L1

DHSDP

B2

PB26

E2

PD2

H2

PB30

L2

DHSDM

B3

PB24

E3

PD3

H3

PB28

L3

VDDUTMI

B4

PC28

E4

PD4

H4

PB29

L4

JTAGSEL

B5

PC23

E5

PD5

H5

VDDBU

L5

GNDBU

B6

PC0

E6

VDDCORE

H6

VDDCORE

L6

PC1

B7

PB9

E7

VDDCORE

H7

VDDIO

L7

PC2

B8

PB8

E8

VDDCORE

H8

PC12

L8

PC5

B9

PB3

E9

PB1

H9

PC11

L9

PC9

B10

PB2

E10

PC18

H10

PA3

L10

PA20

B11

PA26

E11

PB19

H11

PB12

L11

VDDANA

B12

PA25

E12

PB21

H12

PA2

L12

PB16

C1

PA13

F1

PD8

J1

XIN

M1

DFSDP

C2

PA12

F2

PD6

J2

GNDPLL

M2

DFSDM

C3

PB25

F3

PD9

J3

PD10

M3

VBG

C4

PB22

F4

PA0

J4

PB31

M4

VBUS

C5

PC22

F5

PD7

J5

TST

M5

XIN32

C6

PC21

F6

GND

J6

FWUP

M6

XOUT32

C7

PB11

F7

GND

J7

PB27

M7

VDDOUT

C8

PB7

F8

VDDIO

J8

NRST

M8

VDDIN

C9

PC10

F9

PC17

J9

PA19

M9

PC8

C10

PA29

F10

PC14

J10

PA22

M10

GNDANA

C11

PA21

F11

PB20

J11

PA4

M11

ADVREF

C12

PC29

F12

PB17

J12

PA6

M12

PB15

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

19

�5.

Power Considerations

5.1

Power Supplies

The SAM3X/A series product has several types of power supply pins:

VDDCORE pins: Power the core, the embedded memories and the peripherals; voltage ranges from 1.62V

to 1.95V.

VDDIO pins: Power the peripherals I/O lines; voltage ranges from 1.62V to 3.6V.

VDDIN pin: Powers the voltage regulator

VDDOUT pin: Output of the voltage regulator

VDDBU pin: Powers the Slow Clock oscillator and a part of the System Controller; voltage ranges from

1.62V to 3.6V. VDDBU must be supplied before or at the same time as VDDIO and VDDCORE.

VDDPLL pin: Powers the PLL A, UPLL and 3–20 MHz Oscillator; voltage ranges from 1.62V to 1.95V.

VDDUTMI pin: Powers the UTMI+ interface; voltage ranges from 3.0V to 3.6V, 3.3V nominal.

VDDANA pin: Powers the ADC and DAC cells; voltage ranges from 2.0V to 3.6V.

Ground pins GND are common to VDDCORE and VDDIO pins power supplies.

Separated ground pins are provided for VDDBU, VDDPLL, VDDUTMI and VDDANA. These ground pins are

respectively GNDBU, GNDPLL, GNDUTMI and GNDANA.

5.2

Power-up Considerations

5.2.1

VDDIO Versus VDDCORE

VDDIO must always be higher than or equal to VDDCORE.

VDDIO must reach its minimum operating voltage (1.60 V) before VDDCORE has reached VDDCORE(min). The minimum

slope for VDDCORE is defined by (VDDCORE(min) - VT+) / tRST.

If VDDCORE rises at the same time as VDDIO, the VDDIO rising slope must be higher than or equal to 5 V/ms.

If VDDCORE is powered by the internal regulator, all power-up considerations are met.

20

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�Figure 5-1.

VDDCORE and VDDIO Constraints at Startup

Supply (V)

VDDIO

VDDIO(min)

VDDCORE

VDDCORE(min)

VT+

Time (t)

tRST

Core supply POR output

SLCK

5.2.2

VDDIO Versus VDDIN

At power-up, VDDIO needs to reach 0.6 V before VDDIN reaches 1.0 V.

VDDIO voltage needs to be equal to or below (VDDIN voltage + 0.5 V).

5.3

Voltage Regulator

The SAM3X/A series embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3X/A series but can be used to supply other

parts in the application. It features two different operating modes:

In Normal mode, the voltage regulator consumes less than 700 µA static current and draws 150 mA of

output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required

load current. In Wait Mode or when the output current is low, quiescent current is only 7 µA.

In Shutdown mode, the voltage regulator consumes less than 1 µA while its output is driven internally to

GND. The default output voltage is 1.80V and the startup time to reach Normal mode is inferior to 400 µs.

For adequate input and output power supply decoupling/bypassing, refer to Table 45-3 ”1.8V Voltage Regulator

Characteristics”.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

21

�5.4

Typical Powering Schematics

The SAM3X/A series supports a 1.62–3.6 V single supply mode. The internal regulator input connected to the

source and its output feeds VDDCORE. Figure 5-2 shows the power schematics.

Figure 5-2.

Single Supply

VDDBU

VDDUTMI

VDDANA

VDDIO

Main Supply (1.62–3.6 V)

VDDIN

Voltage

Regulator

VDDOUT

VDDCORE

VDDPLL

Note:

22

Restrictions

For USB, VDDUTMI needs to be greater than 3.0V.

For ADC, VDDANA needs to be greater than 2.0V.

For DAC, VDDANA needs to be greater than 2.4V.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�Figure 5-3.

Core Externally Supplied

VDDBU

VDDUTMI

VDDANA

Main Supply (1.62–3.6 V)

VDDIO

VDDIN

Voltage

Regulator

VDDOUT

VDDCORE Supply (1.62–1.95 V)

VDDCORE

VDDPLL

Note:

Restrictions

For USB, VDDUTMI needs to be greater than 3.0V.

For ADC, VDDANA needs to be greater than 2.0V.

For DAC, VDDANA needs to be greater than 2.4V.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

23

�Figure 5-4.

Backup Batteries Used

FWUP

SHDN

Backup Batteries VDDBU

VDDUTMI

VDDANA

VDDIO

VDDIN

Main Supply (1.62–3.6 V)

Voltage

Regulator

VDDOUT

VDDCORE

VDDPLL

Note:

1.

2.

24

Restrictions

For USB, VDDUTMI needs to be greater than 3.0V.

For ADC, VDDANA needs to be greater than 2.0V.

For DAC, VDDANA needs to be greater than 2.4V.

VDDUTMI and VDDANA cannot be left unpowered.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�5.5

Active Mode

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal

oscillator or the PLLA. The power management controller can be used to adapt the frequency and to disable the

peripheral clocks.

5.6

Low Power Modes

The SAM3X/A devices provide the following low-power modes: Backup, Wait, and Sleep.

5.6.1

Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system which is performing

periodic wake-ups to perform tasks but not requiring fast startup time (< 0.5 ms).

The Supply Controller, zero-power power-on reset, RTT, RTC, backup registers and 32 kHz oscillator (RC or

crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are

off.

Backup mode is based on the Cortex-M3 deep-sleep mode with the voltage regulator disabled.

The SAM3X/A series can be awakened from this mode through the Force Wake-up pin (FWUP), and Wake-up

input pins WKUP0–15, Supply Monitor, RTT or RTC wake-up event. Current consumption is 2.5 µA typical on

VDDBU.

Backup mode can be entered by using the WFE instruction.

The procedure to enter Backup mode using the WFE instruction is the following:

1.

Write a 1 to the SLEEPDEEP bit in the Cortex-M3 processor System Control Register (SCR) (refer to

Section 10.21.7 “System Control Register”).

2.

Execute the WFE instruction of the processor.

Exit from Backup mode happens if one of the following enable wake-up events occurs:

5.6.2

Low level, configurable debouncing on FWUP pin

Level transition, configurable debouncing on pins WKUPEN0–15

SM alarm

RTC alarm

RTT alarm

Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a

powered state for a startup time of less than 10 µs.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and

memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC_FSMR).

The Cortex-M3 is able to handle external events or internal events in order to wake-up the core (WFE). This is

done by configuring the external lines WKUP0–15 as fast startup wake-up pins (refer to Section 5.8 “Fast

Startup”). RTC or RTT Alarm and USB wake-up events can be used to wake up the CPU (exit from WFE).

Current consumption in Wait mode is typically 23 µA for total current consumption if the internal voltage regulator

is used or 15 µA if an external regulator is used.

The procedure to enter Wait mode is the following:

1.

Select the 4/8/12 MHz Fast RC Oscillator as Main Clock.

2.

Set the LPM bit in the PMC Fast Startup Mode Register (PMC_FSMR).

3.

Execute the WFE instruction of the processor.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

25

�Note:

5.6.3

Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective

entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to

ensure that the core will not execute undesired instructions.

Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode,

only the core clock is stopped. The peripheral clocks can be enabled.

This mode is entered via Wait for Interrupt (WFI) or WFE instructions with LPM = 0 in PMC_FSMR.

The processor can be awakened from an interrupt if WFI instruction of the Cortex-M3 is used, or from an event if

the WFE instruction is used to enter this mode.

5.6.4

Low Power Mode Summary Table

The modes detailed above are the main low power modes. Each part can be set to on or off separately and wakeup sources can be individually configured. Table 5-1 shows a summary of the configurations of the low power

modes.

26

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�Table 5-1.

Low Power Mode Configuration Summary

VDDBU

Region

Mode

Backup Mode

(1)

Core

Memory

Regulator Peripherals

Mode Entry

Potential Wake-up Sources

Core at

Wake-up

PIO State While in

Low Power Mode

PIO State

at Wake-up

PIOA &

PIOB &

PIOC &

Previous state saved PIOD &

PIOE &

PIOF

Inputs with pull-ups

ON

FWUP pin

Pins WKUP0–15

OFF

OFF

WFE

BOD alarm

SHDN = 0 (not powered) + SLEEPDEEP = 1 RTC alarm

RTT alarm

ON

Any event from Fast Startup:

- through pins WKUP0–15

ON

Powered

+ SLEEPDEEP = 0 - RTC alarm

Clocked back Previous state saved Unchanged

SHDN = 1 (not clocked)

RTT

alarm

+ LPM = 1

- USB wake-up

Reset

Wake-up

Consumption(2) (3) Time(4)

2.5 µA typ(5)

< 0.5 ms

WFE

Wait Mode

18.4 µA/26.6 µA(6) < 10 µs

Entry mode = WFI

interrupt only

Entry mode = WFE

Any enabled interrupt

ON

Powered

+ SLEEPDEEP = 0 and/or

Clocked back Previous state saved Unchanged

SHDN = 1 (not clocked)

any event from Fast Startup:

+ LPM = 0

- through pins WKUP0–15

- RTC alarm

- RTT alarm

- USB wake-up

(7)

Sleep Mode

Notes:

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

1.

2.

3.

4.

ON

WFE or WFI

(7)

(7)

SUPC, 32 kHz Oscillator, RTC, RTT, GPBR, POR.

The external loads on PIOs are not taken into account in the calculation.

BOD current consumption is not included.

When considering the wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz Fast

RC oscillator. The user has to add the PLL startup time if it is needed in the system. The wake-up time is defined as the time taken for wake-up until the first

instruction is fetched.

5. Current consumption on VDDBU.

6. 18.4 µA on VDDCORE, 26.6 µA for total current consumption (using internal voltage regulator).

7. Depends on MCK frequency. In this mode, the core is supplied and not clocked but some peripherals can be clocked.

27

�5.7

Wake-up Sources

The wake-up events allow the device to exit the backup mode. When a wake-up event is detected, the Supply

Controller performs a sequence which automatically reenables the core power supply. See Figure 16-7, "Wake Up

Source" on page 277.

5.8

Fast Startup

The SAM3X/A series allows the processor to restart in a few microseconds while the processor is in wait mode. A

fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0–15 + RTC + RTT +

USB).

The fast restart circuitry (shown in Figure 28-4, "Fast Startup Circuitry" on page 530) is fully asynchronous and

provides a fast startup signal to the Power Management Controller. As soon as the fast startup signal is asserted,

the PMC automatically restarts the embedded 4/8/12 MHz fast RC oscillator, switches the master clock on this

4 MHz clock by default and reenables the processor clock.

6.

Input/Output Lines

The SAM3X/A has different kinds of input/output (I/O) lines, such as general purpose I/Os (GPIO) and system

I/Os. GPIOs can have alternate functions thanks to multiplexing capabilities of the PIO controllers. The same PIO

line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins,

oscillators, erase or analog inputs.

With a few exceptions, the I/Os have input Schmitt triggers. Refer to the footnotes associated with PIOA to PIOF

on page 12, at the end of Table 3-1 “Signal Description List”.

6.1

General Purpose I/O Lines (GPIO)

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up, input

Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these

modes is performed independently for each I/O line through the PIO controller user interface. For more details,

refer to Section 31. “Parallel Input/Output Controller (PIO)”.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3X/A embeds high speed pads able to handle up to 65 MHz for HSMCI and SPI clock lines and 45 MHz

on other lines. See Section 45.10 “AC Characteristics” for more details. Typical pull-up value is 100 kΩ for all I/Os.

Each I/O line also embeds an ODT (On-Die Termination) (see Figure 6-1). ODT consists of an internal series

resistor termination scheme for impedance matching between the driver output (SAM3) and the PCB track

impedance preventing signal reflection. The series resistor helps to reduce IOs switching current (di/dt) thereby

reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect

between devices or between boards. In conclusion, ODT helps reducing signal integrity issues.

Figure 6-1.

On-Die Termination

Z0 ~ ZO + RODT

ODT

36 Ω Typ.

RODT

Receiver

SAM3 Driver with

ZO ~ 10 Ω

28

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

PCB Track

Z0 ~ 50 Ω

�6.2

System I/O Lines

Table 6-1 lists the SAM3X/A system I/O lines shared with PIO lines. These pins are software configurable as

general purpose I/O or system pins. At startup, the default function of these pins is always used.

Table 6-1.

System I/O Configuration Pin List

CCFG_SYSIO

Bit No.

Peripheral

Default Function

After Reset

Other

Function

Constraints for

Normal Start

12

–

ERASE

PC0

Low Level at startup(1)

–

A

TCK/SWCLK

PB28

–

–

A

TDI

PB29

–

–

A

TDO/TRACESWO

PB30

–

–

A

TMS/SWDIO

PB31

–

Configuration

In Matrix User Interface Registers (refer to

System I/O Configuration Register in

Section 21. “Bus Matrix (MATRIX)”)

In PIO Controller

Notes:

1. If PC0 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the

user application sets PC0 into PIO mode.

6.2.1

Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/TRACESWO, TDI and commonly provided on a standard

20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table

3-1 “Signal Description List”.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer

to Section 11. “Debug and Test Features”.

SWJ-DP pins can be used as standard I/Os to provide users with more general input/output pins when the debug

port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general

IO mode is performed through the AHB Matrix Special Function Registers (MATRIX_SFR). Configuration of the

pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a

permanent pull-down resistor of about 15 kΩ to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it

must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and

enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be

used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to

Section 11. “Debug and Test Features”.

All JTAG signals are supplied with VDDIO except JTAGSEL, supplied by VDDBU.

6.3

Test Pin

The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the

SAM3X/A series. The TST pin integrates a permanent pull-down resistor of about 15 kΩ to GND, so that it can be

left unconnected for normal operations. To enter fast programming mode, see Section 19. “Fast Flash

Programming Interface (FFPI)”. For more information on the manufacturing and test mode, refer to Section 11.

“Debug and Test Features”.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

29

�6.4

NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset

signal to the external components, or asserted low externally to reset the microcontroller. It will reset the Core and

the peripherals except the Backup region (RTC, RTT and Supply Controller). There is no constraint on the length

of the reset pulse, and the reset controller can guarantee a minimum pulse length.

The NRST pin integrates a permanent pull-up resistor to VDDIO of about 100 kΩ.

6.5

NRSTB Pin

The NRSTB pin is input only and enables asynchronous reset of the SAM3X/A series when asserted low. The

NRSTB pin integrates a permanent pull-up resistor of about 15 kΩ. This allows connection of a simple push button

on the NRSTB pin as a system-user reset. In all modes, this pin will reset the chip including the Backup region

(RTC, RTT and Supply Controller). It reacts as the Power-on reset. It can be used as an external system reset

source. In harsh environments, it is recommended to add an external capacitor (10 nF) between NRSTB and

VDDBU. (For filtering values, refer to “I/O Characteristics” in Section 45. “Electrical Characteristics”.)

It embeds an anti-glitch filter.

6.6

ERASE Pin

The ERASE pin is used to reinitialize the Flash content (and some of its NVM bits) to an erased state (all bits read

as logic level 1). The ERASE pin and the ROM code ensure an in-situ reprogrammability of the Flash content

without the use of a debug tool. When the security bit is activated, the ERASE pin provides the capability to

reprogram the Flash content. It integrates a pull-down resistor of about 100 kΩ to GND, so that it can be left

unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less than

100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform a Flash erase

operation.

The ERASE pin is a system I/O pin and can be used as a standard I/O. At startup, the ERASE pin is not configured

as a PIO pin. If the ERASE pin is used as a standard I/O, the startup level of this pin must be low to prevent

unwanted erasing. Please refer to Section 9.3 “Peripheral Signal Multiplexing on I/O Lines”. Also, if the ERASE pin

is used as a standard I/O output, asserting the pin to high does not erase the Flash.

30

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�7.

Memories

7.1

Product Mapping

Figure 7-1.

SAM3X/A Product Mapping

Code

0x00000000

0x00000000

Address memory space

Peripherals

0x40000000

Boot Memory

HSMCI

Code

0x00080000

21

0x40004000

Internal Flash 0

SSC

HALF_FLASHSIZE

0x20000000

26

0x40008000

Internal Flash 1

SPI0

SRAM

0x00100000

0x4000C000

Internal ROM

SPI1

0x00200000

0x40000000

0x40080000

Reserved

Peripherals

0x1FFFFFFF

HALF_FLASHSIZE address:

- 512 KB products: 0x000C0000

- 256 KB products: 0x000A0000

- 128 KB products: 0x00090000

+0x40

0x60000000

+0x80

External SRAM

0x40084000

0xA0000000

SRAM

0x20000000

+0x40

Reserved

+0x80

SRAM0

0x20080000

0xE0000000

0x40088000

SRAM1

0x20100000

System

+0x40

NFC (SRAM)

0x20180000

UOTGHS (DMA)

0x20200000

Undefined (Abort)

0xFFFFFFFF

+0x80

System controller

9

0x40000000

External SRAM

0x400E0000

SMC

SDRAM

0x60000000

CS0

10

0x400E0200

0x400E0400

MATRIX

0x61000000

CS1

0x400E0600

PMC

5

0x62000000

CS2

0x400E0800

UART

8

0x63000000

CS3

0x400E0940

CHIPID

0x64000000

CS4

0x400E0A00

EEFC0

6

0x65000000

CS5

0x400E0C00

EEFC1

7

0x66000000

CS6

0x400E0E00

PIOA

11

0x67000000

0x400E1000

PIOB

CS7

12

0x68000000

NFC

0x400E1200

PIOC

13

0x69000000

Reserved

0x400E1400

PIOD

14

0x70000000

CS SDRAMC

0x400E1600

PIOE

15

0x80000000

Reserved

0x400E1800

PIOF

16

0x9FFFFFFF

0x400E1A00

RSTC

1

0x400E1A10

SUPC

0x400E1A30

RTT

WDT

3

4

0x400E1A50

0x400E1A60

RTC

2

TC0

24

25

TC0

27

TC0

TC1

28

TC0

TC2

29

TC1

TC1

TC1

TC2

TC3

TC4

TC5

30

31

32

TC6

33

TC2

TC2

TC7

TC8

0x4008C000

34

35

TWI0

22

0x40090000

TWI1

23

0x40094000

PWM

36

0x40098000

USART0

17

0x4009C000

USART1

18

0x400A0000

USART2

19

0x400A4000

USART3

20

0x400A8000

Reserved

0x400AC000

UOTGHS

40

0x400B0000

EMAC

0x400B4000

42

CAN0

43

0x400B8000

CAN1

0x400BC000

TRNG

0x400C0000

ADC

0x400C4000

44

41

37

DMAC

39

0x400C8000

DACC

38

0x400D0000

Reserved

0x400E0000

System controller

0x400E2600

Reserved

0x400E1A90

GPBR

0x60000000

0x400E1AB0

Reserved

0x4007FFFF

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

31

�7.2

Embedded Memories

7.2.1

Internal SRAM

Table 7-1 shows the embedded high-speed SRAM for the various devices.

Table 7-1.

Embedded High-speed SRAM per Device

Device

Pin Count

SRAM0 (KB)

SRAM1 (KB)

NFC SRAM (KB)

Total SRAM (KB)

144

64

32

4

100

100

64

32

–

96

144

32

32

4

68

100

32

32

–

64

SAM3X8E

SAM3X8H(1)

SAM3A8C

SAM3X8C

SAM3X4E

SAM3A4C

SAM3X4C

Note:

1.

This device is not commercially available. Mounted only on the SAM3X-EK evaluation kit.

SRAM0 is accessible over the system Cortex-M3 bus at address 0x2000 0000 and SRAM1 at address 0x2008

0000. The user can see the SRAM as contiguous thanks to mirror effect, giving 0x2007 0000 - 0x2008 7FFF for

SAM3X/A8, and 0x2007 8000 - 0x2008 7FFF for SAM3X/A4.

SRAM0 and SRAM1 are in the bit band region. The bit band alias region is mapped from 0x2200 0000 to

0x23FF FFFF.

The NAND Flash Controller (NFC) embeds 4224 bytes of internal SRAM. If the NFC is not used, these

4224 Kbytes can be used as general-purpose SRAM. It can be seen at address 0x2010 0000.

7.2.2

Internal ROM

The SAM3X/A series product embeds an Internal ROM, which contains the SAM-BA and FFPI program.

At any time, the ROM is mapped at address 0x0010 0000.

7.2.3

Embedded Flash

7.2.3.1 Flash Overview

Table 7-2 shows the Flash organization for the various devices.

Table 7-2.

Embedded Flash Memory Organization per Device

Device

Flash Size (Kbytes)

Number of Banks

Number of Pages

Page Size (bytes)

Plane

SAM3A8

512

2

1024

256

Dual

SAM3X8

512

2

1024

256

Dual

SAM3A4

256

2

512

256

Dual

SAM3X4

256

2

512

256

Dual

The Flash contains a 128-byte write buffer, accessible through a 32-bit interface.

7.2.3.2 Flash Power Supply

The Flash is supplied by VDDCORE.

32

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

�7.2.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It

enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped within the Memory

Controller on the APB.

The EEFC ensures the interface of the Flash block with the 32-bit internal bus. Its 128-bit wide memory interface

increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit

access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set

of commands.

One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash

organization, thus making the software generic.

7.2.3.4 Lock Regions

Several lock bits are used to protect write and erase operations on lock regions. A lock region is composed of

several consecutive pages, and each lock region has its associated lock bit.

Table 7-3.

Number of Lock Bits

Product

SAM3X8

SAM3A8

SAM3X4

SAM3A4

Number of Lock Bits

Lock Region Size

32

16 Kbytes (64 pages)

16

16 Kbytes (64 pages)

If a locked-region’s erase or program command occurs, the command is aborted and the EEFC triggers an

interrupt.

The lock bits are software programmable through the EEFC User Interface. The “Set Lock Bit” command enables

the protection. The “Clear Lock Bit” command unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

7.2.3.5 Security Bit Feature

The SAM3X/A series features a security bit, based on a specific General Purpose NVM bit (GPNVM bit 0). When

the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash

Programming Interface (FFPI), is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled through the “Set General Purpose NVM Bit 0” command of the EEFC0 User

Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full Flash

erase is performed. When the security bit is deactivated, all accesses to the Flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation.

However, it is safer to connect it directly to GND for the final application.

7.2.3.6 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured

and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

7.2.3.7 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory configured and cannot be changed

by the user. The ERASE pin has no effect on the unique identifier.

SAM3X / SAM3A [DATASHEET]

Atmel-11057C-ATARM-SAM3X-SAM3A-Datasheet_23-Mar-15

33

�7.2.3.8 Fast Flash Programming Interface (FFPI)

The FFPI allows device programming through multiplexed fully-handshaked parallel port. It allows gang

programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

The FFPI is enabled and the Fast Programming Mode is entered when TST, PA0, PA1 are set to high, PA2 and

PA3 are set to low and NRST is toggled from 0 to 1.

The table below shows the signal assignment of the PIO lines in FFPI mode

Table 7-4.

FFPI PIO Assignment

FFPI Signal

PIO Used

PGMNCMD

PA0

PGMRDY

PA1

PGMNOE

PA2

PGMNVALID

PA3

PGMM[0]