ZL30623

Dual-Channel Any Frequency Timing Card

PLL with Ultra Low Jitter

Product Brief

September 2015

Ordering Information

Features

Two Independent Channels

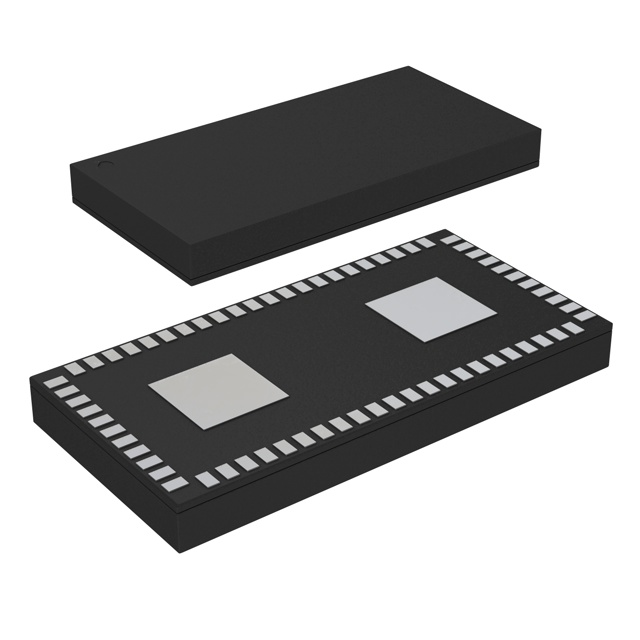

ZL30623LFG7

ZL30623LFF7

Low-Bandwidth DPLL Per Channel

64 Pin LGA

64 Pin LGA

Trays

Tape and Reel

Ni Au

ITU-T G.813/G.8262 compliance (options 1 & 2)

Package size: 5 x 10 mm

Programmable bandwidth, 0.1Hz to 500Hz

-40C to +85C

Attenuates jitter up to several UI

Outputs are CML or 2xCMOS, can interface to

LVDS, LVPECL, HSTL, SSTL and HCS

Freerun or holdover on loss of all inputs

Hitless reference switching

In 2xCMOS mode, the P and N pins can be

different frequencies (e.g. 125MHz and 25MHz)

High-resolution holdover averaging

Per-output supply pin with CMOS output

voltages from 1.5V to 3.3V

Digitally controlled phase adjustment

Three Input Clocks Per Channel

Three inputs, two differential/CMOS, one CMOS

Precise output alignment circuitry and peroutput phase adjustment

Any input frequency from 8kHz to 1250MHz

(8kHz to 300MHz for CMOS)

Per-output enable/disable and glitchless

start/stop (stop high or low)

Per-input activity and frequency monitoring

General Features

Automatic or manual reference switching

Automatic self-configuration at power-up from

internal EEPROM; up to four configurations

pin-selectable

Low-Jitter Fractional-N APLL and 3 Outputs Per

Channel

Numerically controlled oscillator mode

Any output frequency from

很抱歉,暂时无法提供与“ZL30623LFG7”相匹配的价格&库存,您可以联系我们找货

免费人工找货