Sample &

Buy

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

Reference

Design

ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

ADS1220 4-Channel, 2-kSPS, Low-Power, 24-Bit ADC with Integrated PGA and Reference

1 Features

3 Description

•

The ADS1220 is a precision, 24-bit, analog-to-digital

converter (ADC) that offers many integrated features

to reduce system cost and component count in

applications measuring small sensor signals. The

device features two differential or four single-ended

inputs through a flexible input multiplexer (MUX), a

low-noise, programmable gain amplifier (PGA), two

programmable excitation current sources, a voltage

reference, an oscillator, a low-side switch, and a

precision temperature sensor.

1

•

•

•

•

•

•

•

•

•

•

•

•

Low Current Consumption:

As Low as 120 μA (typ) in Duty-Cycle Mode

Wide Supply Range: 2.3 V to 5.5 V

Programmable Gain: 1 V/V to 128 V/V

Programmable Data Rates: Up to 2 kSPS

Up to 20-Bits Effective Resolution

Simultaneous 50-Hz and 60-Hz Rejection at

20 SPS with Single-Cycle Settling Digital Filter

Two Differential or Four Single-Ended Inputs

Dual Matched Programmable Current Sources:

10 μA to 1.5 mA

Internal 2.048-V Reference: 5 ppm/°C (typ) Drift

Internal 2% Accurate Oscillator

Internal Temperature Sensor:

0.5°C (typ) Accuracy

SPI-Compatible Interface (Mode 1)

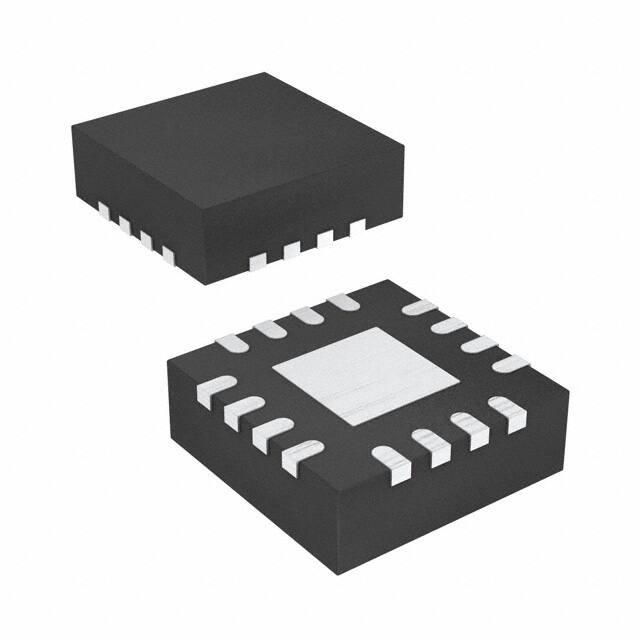

Package: 3.5-mm × 3.5-mm × 0.9-mm VQFN

The device can perform conversions at data rates up

to 2000 samples-per-second (SPS) with single-cycle

settling. At 20 SPS, the digital filter offers

simultaneous 50-Hz and 60-Hz rejection for noisy

industrial applications. The internal PGA offers gains

up to 128 V/V. This PGA makes the ADS1220 ideallysuited for applications measuring small sensor

signals, such as resistance temperature detectors

(RTDs), thermocouples, thermistors, and resistive

bridge sensors. The device supports measurements

of pseudo- or fully-differential signals when using the

PGA. Alternatively, the device can be configured to

bypass the internal PGA while still providing high

input impedance and gains up to 4 V/V, allowing for

single-ended measurements.

2 Applications

•

•

•

•

Temperature Sensor Measurements:

– Thermistors

– Thermocouples

– Resistance Temperature Detectors (RTDs):

2-, 3-, or 4-Wire Types

Resistive Bridge Sensor Measurements:

– Pressure Sensors

– Strain Gauges

– Weigh Scales

Portable Instrumentation

Factory Automation and Process Control

Power consumption is as low as 120 µA when

operating in duty-cycle mode with the PGA disabled.

The ADS1220 is offered in a leadless VQFN-16 or a

TSSOP-16 package and is specified over a

temperature range of –40°C to +125°C.

Device Information(1)

PART NUMBER

ADS1220

PACKAGE

BODY SIZE (NOM)

VQFN (16)

3.50 mm × 3.50 mm

TSSOP (16)

5.00 mm × 4.40 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

K-Type Thermocouple Measurement

3.3 V

3.3 V

0.1 PF

3.3 V

0.1 PF

REFP0

10 A to

1.5 mA

AIN0

REFN0

AVDD

Internal

Reference

DVDD

Reference

MUX

TI Device

PGA

24-Bit

û ADC

Digital Filter

and

SPI

Interface

Precision

Temperature

Sensor

Low-Drift

Oscillator

AIN1

AINP

Thermocouple

MUX

Isothermal

Block

AIN2

AIN3

AINN

AVSS

CLK

CS

SCLK

DIN

DOUT/DRDY

DRDY

DGND

Copyright © 2016, Texas Instruments Incorporated

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

6.1

6.2

6.3

6.4

6.5

6.6

6.7

6.8

1

1

1

2

4

5

Absolute Maximum Ratings ...................................... 5

ESD Ratings.............................................................. 5

Recommended Operating Conditions....................... 6

Thermal Information .................................................. 6

Electrical Characteristics........................................... 7

SPI Timing Requirements ......................................... 9

SPI Switching Characteristics ................................... 9

Typical Characteristics ............................................ 10

7

Parameter Measurement Information ................ 16

8

Detailed Description ............................................ 19

7.1 Noise Performance ................................................. 16

8.1

8.2

8.3

8.4

Overview .................................................................

Functional Block Diagram .......................................

Feature Description.................................................

Device Functional Modes........................................

19

19

20

32

8.5 Programming........................................................... 34

8.6 Register Map........................................................... 39

9

Application and Implementation ........................ 44

9.1 Application Information............................................ 44

9.2 Typical Applications ................................................ 49

10 Power Supply Recommendations ..................... 60

10.1 Power-Supply Sequencing.................................... 60

10.2 Power-Supply Ramp Rate .................................... 60

10.3 Power-Supply Decoupling..................................... 60

11 Layout................................................................... 61

11.1 Layout Guidelines ................................................. 61

11.2 Layout Example .................................................... 62

12 Device and Documentation Support ................. 63

12.1

12.2

12.3

12.4

12.5

12.6

Documentation Support ........................................

Receiving Notification of Documentation Updates

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

63

63

63

63

63

63

13 Mechanical, Packaging, and Orderable

Information ........................................................... 63

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision B (February 2015) to Revision C

Page

•

Changed K-Type Thermocouple Measurement figure ........................................................................................................... 1

•

Added footnote 1 to Pin Functions table and changed descriptions of AIN0/REFP1, AIN1, AIN2, AIN3/REFN1,

REFN0, and REFP0 pins accordingly .................................................................................................................................... 4

•

Changed Functional Block Diagram figure ........................................................................................................................... 19

•

Changed Bypassing the PGA section .................................................................................................................................. 24

•

Added fourth sentence to Temperature Sensor section....................................................................................................... 31

•

Changed last equation in Converting from Digital Codes to Temperature section .............................................................. 31

•

Changed description of bits 5:4 in Configuration Register 2 ................................................................................................ 42

•

Added Unused Inputs and Outputs section ......................................................................................................................... 47

•

Changed Figure 74............................................................................................................................................................... 49

•

Changed Figure 77............................................................................................................................................................... 52

•

Changed Figure 78............................................................................................................................................................... 55

•

Changed Figure 79............................................................................................................................................................... 56

•

Changed Figure 82............................................................................................................................................................... 58

•

Changed Power Supply Recommendations section: changed Power-Supply Sequencing subsection, added PowerSupply Ramp Rate subsection ............................................................................................................................................. 60

2

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Changes from Revision A (July 2013) to Revision B

Page

•

Added TI Design, Device Information, ESD Ratings, Recommended Operating Conditions, and Switching

Characteristics tables and Application and Implementation, Power Supply Recommendations, Layout, Device and

Documentation Support, and Mechanical, Packaging, and Orderable Information sections ................................................. 1

•

Changed document title, QFN to VQFN throughout document, Features, Applications, Description, Pin Configuration

and Functions, Parameter Measurement Information, Feature Description, Device Functional Modes, Programming,

and Register Map sections, and front-page figure ................................................................................................................. 1

•

Deleted Product Family table ................................................................................................................................................ 4

•

Changed format of Absolute Maximum Ratings table, added minimum junction temperature specification, changed

input current parameter name, and removed momentary input current specification ............................................................ 5

•

Changed Analog Inputs and Voltage Reference Inputs sections (specification values were not changed) and added

Internal Oscillator section to Electrical Characteristics table.................................................................................................. 7

•

Changed System Performance section: changed VIO parameter name and added PGA disabled row to Offset drift,

Gain error, and Gain drift parameters in System Performance section of Electrical Characteristics table............................ 7

•

Changed Internal Voltage Reference section: changed Reference drift parameter maximum specification and added

Long-term drift parameter in Electrical Characteristics table.................................................................................................. 7

•

Deleted Clock Sources section and changed Temperature Sensor and Power Supply sections (specification values

were not changed) in Electrical Characteristics table............................................................................................................. 8

•

Changed Digital Inputs/Outputs section, VIL parameter minimum specification in Electrical Characteristics table ............... 8

•

Changed SPI Timing Requirements and Figure 1 (specification values were not changed), added SPI Switching

Characteristics and Figure 2 .................................................................................................................................................. 9

•

Changed format of Typical Characteristics section (actual curves did not change) ............................................................ 10

Changes from Original (May 2013) to Revision A

•

Page

Changed document status to Mixed Status; pre-RTM changes made throughout ................................................................ 1

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

3

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

5 Pin Configuration and Functions

RVA Package

16-Pin VQFN

Top View

CLK

DGND

SCLK

DIN

DOUT/DRDY

16

15

14

13

1

DOUT/DRDY

CS

PW Package

16-Pin TSSOP

Top View

SCLK

1

16

DIN

CS

2

15

DOUT/DRDY

CLK

3

14

DRDY

11 DVDD

DGND

4

13

DVDD

AVSS

5

12

AVDD

AIN3/REFN1

6

11

AIN0/REFP1

AIN2

7

10

AIN1

REFN0

8

9

REFP0

12 DRDY

2

Thermal Pad

4

9

5

6

7

8

AIN1

AIN3/REFN1

REFP0

10 AVDD

REFN0

3

AIN2

AVSS

AIN0/REFP1

Pin Functions

PIN

NO.

RVA

PW

ANALOG OR DIGITAL

INPUT/OUTPUT

AIN0/REFP1

9

11

Analog input

Analog input 0, positive reference input 1

AIN1

8

10

Analog input

Analog input 1

AIN2

5

7

Analog input

Analog input 2

AIN3/REFN1

4

6

Analog input

Analog input 3, negative reference input 1.

Internal low-side power switch connected between AIN3/REFN1 and AVSS.

AVDD

10

12

Analog

Positive analog power supply

AVSS

3

5

Analog

Negative analog power supply

CLK

1

3

Digital input

External clock source pin. Connect to DGND if not used.

CS

16

2

Digital input

Chip select; active low. Connect to DGND if not used.

DGND

2

4

Digital

DIN

14

16

Digital input

Serial data input

DOUT/DRDY

13

15

Digital output

Serial data output combined with data ready; active low

DRDY

12

14

Digital output

Data ready, active low.

Leave unconnected or tie to DVDD using a weak pull-up resistor if not used.

DVDD

11

13

Digital

REFN0

6

8

Analog input

Negative reference input 0

REFP0

7

9

Analog input

Positive reference input 0

SCLK

15

1

Digital input

Serial clock input

—

—

NAME

Thermal pad

(1)

4

DESCRIPTION (1)

Digital ground

Positive digital power supply

Thermal power pad. Do not connect or only connect to AVSS.

See the Unused Inputs and Outputs section for unused pin connections.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

6 Specifications

6.1 Absolute Maximum Ratings (1)

Power-supply voltage

MIN

MAX

UNIT

AVDD to AVSS

–0.3

7

V

DVDD to DGND

–0.3

7

V

AVSS to DGND

–2.8

0.3

V

V

Analog input voltage

AIN0/REFP1, AIN1, AIN2, AIN3/REFN1, REFP0, REFN0

AVSS – 0.3

AVDD + 0.3

Digital input voltage

CS, SCLK, DIN, DOUT/DRDY, DRDY, CLK

DGND – 0.3

DVDD + 0.3

V

Input current

Continuous, any pin except power supply pins

–10

10

mA

Junction, TJ

–40

150

°C

Storage, Tstg

–60

150

°C

Temperature

(1)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2000

Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)

±500

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

5

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

POWER SUPPLY

Unipolar analog power supply

Bipolar analog power supply

Digital power supply

AVDD to AVSS

2.3

AVSS to DGND

–0.1

5.5

0

0.1

AVDD to DGND

2.3

2.5

2.75

AVSS to DGND

–2.75

–2.5

–2.3

DVDD to DGND

2.3

V

V

5.5

V

ANALOG INPUTS (1)

VIN

Differential input voltage

V(AINx)

Absolute input voltage

VCM

Common-mode input voltage

VIN = V(AINP) – V(AINN) (2)

–Vref / Gain

Vref / Gain

V

PGA disabled, gain = 1 to 4

AVSS – 0.1

AVDD + 0.1

V

AVDD + 0.1

V

PGA enabled, gain = 1 to 128

PGA disabled, gain = 1 to 4

See the Low-Noise PGA section

AVSS – 0.1

PGA enabled, gain = 1 to 128

See the Low-Noise PGA section

VOLTAGE REFERENCE INPUTS (3)

Vref

Differential reference input voltage

V(REFNx)

Absolute negative reference voltage

V(REFPx)

Absolute positive reference voltage

Vref = V(REFPx) – V(REFNx)

AVDD

V

AVSS – 0.1

0.75

2.5

V(REFPx) – 0.75

V

V(REFNx) + 0.75

AVDD + 0.1

V

EXTERNAL CLOCK SOURCE

f(CLK)

External clock frequency

0.5

Duty cycle

4.096

4.5

MHz

40%

60%

DGND

DVDD

V

–40

125

°C

DIGITAL INPUTS

Input voltage

TEMPERATURE RANGE

TA

(1)

(2)

(3)

Operating ambient temperature

AINP and AINN denote the positive and negative inputs of the PGA. AINx denotes one of the four available analog inputs.

PGA disabled means the low-noise PGA is powered down and bypassed. Gains of 1, 2, and 4 are still possible in this case.

See the Bypassing the PGA section for more information.

Excluding the effects of offset and gain error.

Limited to ±[(AVDD – AVSS) – 0.4 V] / Gain, when the PGA is enabled.

REFPx and REFNx denote one of two available differential reference input pairs.

6.4 Thermal Information

ADS1220

THERMAL METRIC (1)

VQFN (RVA)

TSSOP (PW)

16 PINS

16 PINS

UNIT

RθJA

Junction-to-ambient thermal resistance

43.4

99.5

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

47.3

35.2

°C/W

RθJB

Junction-to-board thermal resistance

18.4

44.3

°C/W

ψJT

Junction-to-top characterization parameter

0.6

2.4

°C/W

ψJB

Junction-to-board characterization parameter

18.4

43.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.0

n/a

°C/W

(1)

6

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

6.5 Electrical Characteristics

Minimum and maximum specifications apply from TA = –40°C to +125°C. Typical specifications are at TA = 25°C.

All specifications are at AVDD = 3.3 V, AVSS = 0 V, DVDD = 3.3 V, PGA enabled, DR = 20 SPS, and external Vref = 2.5 V

(unless otherwise noted). (1)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

ANALOG INPUTS

Absolute input current

See the Typical Characteristics

Differential input current

See the Typical Characteristics

SYSTEM PERFORMANCE

Resolution (no missing codes)

24

Normal mode

DR

Data rate

Duty-cycle mode

5, 11.25, 22.5, 44, 82.5, 150, 250

Turbo mode

40, 90, 180, 350, 660, 1200, 2000

Noise (input-referred)

INL

Integral nonlinearity

Input offset voltage

–15

Gain = 1, differential inputs, TA = 25°C

Offset match

Gain error

Gain drift

NMRR

CMRR

PSRR

Normal-mode rejection ratio (2)

Common-mode rejection ratio

Power-supply rejection ratio

±6

–30

±4

0.25

Gain = 1 to 128, TA = –40°C to +85°C (2)

0.08

Gain = 1 to 128

0.25

Match between any two inputs

µV

0.3

µV/°C

µV

±0.015%

–0.1%

±0.015%

PGA disabled, gain = 1 to 4

1

Gain = 1 to 128 (2)

1

50 Hz ±3%, DR = 20 SPS, external CLK,

50/60 bit = 10

105

60 Hz ±3%, DR = 20 SPS, external CLK,

50/60 bit = 11

105

0.1%

4

ppm/°C

dB

50 Hz or 60 Hz ±3%, DR = 20 SPS,

external CLK, 50/60 bit = 01

90

At dc, gain = 1

90

105

f(CM) = 50 Hz, DR = 2000 SPS (2)

95

115

f(CM) = 60 Hz, DR = 2000 SPS (2)

95

115

DVDD at dc, VCM = 0.5 AVDD, gain = 1 (2)

30

±20

PGA disabled, gain = 1 to 4

AVDD at dc, VCM = 0.5 AVDD, gain = 1

ppmFSR

±4

PGA disabled, gain = 1 to 4

Gain = 1 to 128, TA = 25°C

15

±4

Gain = 2 to 128, differential inputs

Offset drift

SPS

See the Noise Performance section

Gain = 1 to 128, VCM = 0.5 AVDD, best fit (2)

PGA disabled, gain = 1 to 4, differential inputs

VIO

Bits

20, 45, 90, 175, 330, 600, 1000

dB

80

105

100

115

2.045

2.048

2.051

5

30

dB

INTERNAL VOLTAGE REFERENCE

Initial accuracy

TA = 25°C

Reference drift (2)

Long-term drift

V

ppm/°C

1000 hours

110

ppm

REFP0 = Vref, REFN0 = AVSS

±10

nA

VOLTAGE REFERENCE INPUTS

Reference input current

INTERNAL OSCILLATOR

Internal oscillator accuracy

(1)

(2)

Normal mode

–2%

±1%

2%

PGA disabled means the low-noise PGA is powered down and bypassed. Gains of 1, 2, and 4 are still possible in this case.

See the Bypassing the PGA section for more information.

Minimum and maximum values are ensured by design and characterization data.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

7

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

Electrical Characteristics (continued)

Minimum and maximum specifications apply from TA = –40°C to +125°C. Typical specifications are at TA = 25°C.

All specifications are at AVDD = 3.3 V, AVSS = 0 V, DVDD = 3.3 V, PGA enabled, DR = 20 SPS, and external Vref = 2.5 V

(unless otherwise noted).(1)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

EXCITATION CURRENT SOURCES (IDACs)

Current settings

10, 50, 100, 250, 500, 1000, 1500

µA

Compliance voltage

All current settings

AVDD – 0.9

Accuracy

All current settings, each IDAC

Current match

Between IDACs (not valid for 10-µA setting)

Temperature drift

Each IDAC (not valid for 10-µA setting)

50

ppm/°C

Temperature drift matching

Between IDACs (not valid for 10-µA setting)

10

ppm/°C

14

Bits

–6%

±1%

V

6%

±0.3%

TEMPERATURE SENSOR

Conversion resolution

Temperature resolution

Accuracy

0.03125

TA = 0°C to +75°C

TA = –40°C to +125°C

°C

–0.5

±0.25

0.5

–1

±0.5

1

0.0625

0.25

3.5

5.5

Ω

30

mA

Accuracy vs analog supply voltage

°C

°C/V

LOW-SIDE POWER SWITCH

RON

On-resistance

Current through switch

DIGITAL INPUTS/OUTPUTS

VIH

High-level input voltage

VIL

Low-level input voltage

VOH

High-level output voltage

IOH = 3 mA

VOL

Low-level output voltage

IOL = 3 mA

IH

Input leakage, high

VIH = 5.5 V

IL

Input leakage, low

VIL = DGND

0.7 DVDD

DVDD

V

DGND

0.3 DVDD

V

0.8 DVDD

V

0.2 DVDD

V

–10

10

µA

–10

10

µA

POWER SUPPLY

Power-down mode

0.1

Duty-cycle mode, PGA disabled

65

Duty-cycle mode, gain = 1 to 16

IAVDD

IDVDD

PD

(3)

8

Analog supply current (3)

Digital supply current (3)

Power dissipation (3)

3

95

Duty-cycle mode, gain = 32

115

Duty-cycle mode, gain = 64, 128

135

Normal mode, PGA disabled

240

Normal mode, gain = 1 to 16

340

Normal mode, gain = 32

425

Normal mode, gain = 64, 128

510

Turbo mode, PGA disabled

360

Turbo mode, gain = 1 to 16

540

Turbo mode, gain = 32

715

Turbo mode, gain = 64, 128

890

Power-down mode

0.3

Duty-cycle mode

55

Normal mode

75

Turbo mode

95

Duty-cycle mode, PGA disabled

0.4

Normal mode, gain = 1 to 16

1.4

Turbo mode, gain = 1 to 16

2.1

490

µA

5

110

µA

mW

Internal voltage reference selected, internal oscillator enabled, IDACs turned off, and continuous conversion mode.

Analog supply current increases by 70 µA, typ (normal mode, turbo mode) when selecting an external reference.

Analog supply current increases by 190 µA (typ) when enabling the IDACs (excludes the actual IDAC current).

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

6.6 SPI Timing Requirements

over operating ambient temperature range and DVDD = 2.3 V to 5.5 V (unless otherwise noted)

MIN

MAX

UNIT

td(CSSC)

Delay time, CS falling edge to first SCLK rising edge (1)

50

ns

td(SCCS)

Delay time, final SCLK falling edge to CS rising edge

25

ns

tw(CSH)

Pulse duration, CS high

50

ns

tc(SC)

SCLK period

150

ns

tw(SCH)

Pulse duration, SCLK high

60

ns

tw(SCL)

Pulse duration, SCLK low

60

ns

tsu(DI)

Setup time, DIN valid before SCLK falling edge

50

ns

th(DI)

Hold time, DIN valid after SCLK falling edge

25

SPI timeout (2)

(1)

(2)

ns

Normal mode, duty-cycle mode

13955

t(MOD)

Turbo mode

27910

t(MOD)

CS can be tied low permanently in case the serial bus is not shared with any other device.

See the SPI Timeout section for more information.

t(MOD) = 1 / f(MOD). Modulator frequency f(MOD) = 256 kHz (normal mode, duty-cycle mode) and 512 kHz (turbo mode), when using the

internal oscillator or an external 4.096-MHz clock.

tw(CSH)

CS

ttd(CSSC)t

ttc(SC)t

tw(SCH)

ttd(SCCS)t

SCLK

tsu(DI)

th(DI)

tw(SCL)

DIN

NOTE: Single-byte communication is shown. Actual communication may be multiple bytes.

Figure 1. Serial Interface Timing Requirements

6.7 SPI Switching Characteristics

over operating ambient temperature range, DVDD = 2.3 V to 5.5 V (unless otherwise noted)

PARAMETER

TEST CONDITIONS

tp(CSDO)

Propagation delay time,

CS falling edge to DOUT driven

DOUT load = 20 pF || 10 kΩ to DGND

tp(SCDO)

Propagation delay time,

SCLK rising edge to valid new DOUT

DOUT load = 20 pF || 10 kΩ to DGND

tp(CSDOZ)

Propagation delay time,

CS rising edge to DOUT high impedance

DOUT load = 20 pF || 10 kΩ to DGND

MIN

0

TYP

MAX

UNIT

50

ns

50

ns

50

ns

CS

SCLK

tp(CSDO)

DOUT/DRDY

tp(SCDO)

tp(CSDOZ)

Hi-Z

Hi-Z

NOTE: Single-byte communication is shown. Actual communication may be multiple bytes.

Figure 2. Serial Interface Switching Characteristics

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

9

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

6.8 Typical Characteristics

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

40

40

Gain = 1

Gain = 1

Gain = 128

Gain = 128

30

PGA Disabled

Offset Voltage (µV)

Offset Voltage (µV)

30

20

10

0

PGA Disabled

20

10

0

±10

±10

±40

±20

0

20

40

60

80

100

120

Temperature (ƒC)

±40

±20

0

20

40

60

AVDD = 3.3 V

C018

Figure 4. Input-Referred Offset Voltage vs Temperature

500

500

Gain = 1

400

Gain = 1

Gain = 128

PGA Disabled

Gain Error (ppm of FS)

Gain Error (ppm of FS)

120

Figure 3. Input-Referred Offset Voltage vs Temperature

300

200

100

0

400

PGA Disabled

300

200

100

0

±40

±20

0

20

40

60

80

100

Temperature (ƒC)

120

±40

±20

0

15

Gain = 1

Gain = 32

PGA Disabled

80

100

120

C020

Gain = 1

Gain = 32

PGA Disabled

10

5

0

±5

±10

±15

±100

60

Figure 6. Gain Error vs Temperature

INL (ppm of FS)

10

40

AVDD = 5.0 V

Figure 5. Gain Error vs Temperature

15

20

Temperature (ƒC)

C019

AVDD = 3.3 V

INL (ppm of FS)

100

AVDD = 5.0 V

Gain = 128

5

0

±5

±10

±75

±50

±25

0

25

50

75

VIN (% of FS)

100

±15

±100

±75

±50

±25

0

25

50

75

VIN (% of FS)

C025

AVDD = 3.3 V, external 2.5-V reference, normal mode

100

C029

AVDD = 5.0 V, external 2.5-V reference, normal mode

Figure 7. Integral Nonlinearity vs

Differential Input Signal

10

80

Temperature (ƒC)

C017

Submit Documentation Feedback

Figure 8. Integral Nonlinearity vs

Differential Input Signal

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Typical Characteristics (continued)

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

20

20

Gain = 1

Gain = 32

PGA Disabled

15

10

INL (ppm of FS)

10

INL (ppm of FS)

Gain = 1

Gain = 32

PGA Disabled

15

5

0

±5

5

0

±5

±10

±10

±15

±15

±20

±100

±75

±50

±25

0

25

50

75

±20

±100

100

VIN (% of FS)

±75

±50

±25

0

25

50

75

100

VIN (% of FS)

C043

AVDD = 3.3 V, internal reference, normal mode

C044

AVDD = 5.0 V, internal reference, normal mode

Figure 9. Integral Nonlinearity vs

Differential Input Signal

Figure 10. Integral Nonlinearity vs

Differential Input Signal

2.051

1000

AVDD = 3.3 V

Reference Voltage (V)

Counts

AVDD = 5.0 V

2.050

800

600

400

200

2.049

2.048

2.047

2.051

2.050

2.049

2.048

2.047

2.046

2.045

2.046

0

Initial Reference Voltage (V)

2.045

±40

±20

0

20

40

60

80

100

Temperature (ƒC)

C042

120

C021

TA = 25°C, data from 5490 devices

Figure 12. Internal Reference Voltage vs Temperature

Figure 11. Internal Reference Voltage Histogram

1.00

0

0.75

±20

0.50

±40

0.25

±60

PSRR (dB)

Frequency Error (%)

Gain = 1

0.00

±0.25

±80

±100

±0.50

±120

±0.75

±140

±1.00

Gain = 128

±160

±40

±20

0

20

40

60

Temperature (ƒC)

80

100

120

0.1

1

10

100

Frequency (kHz)

C002

1000

C016

DVDD = 3.3 V, normal mode

Figure 13. Internal Oscillator Accuracy vs Temperature

Figure 14. AVDD Power-Supply Rejection Ratio vs

Frequency

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

11

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

Typical Characteristics (continued)

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

15

AIN0

AIN1

AIN2

AIN3

10

Absolute Input Current (nA)

Absolute Input Current (nA)

15

5

0

±5

±10

±15

AIN0

AIN1

AIN2

AIN3

10

5

0

±5

±10

±15

0.5

1.0

1.5

2.0

2.5

3.0

Absolute Input Voltage V(AINx) (V)

0.5

1.0

AVDD = 3.3 V, PGA enabled, TA = –40°C

2.5

3.0

C031

Figure 16. Absolute Input Current vs

Absolute Input Voltage

100

AIN0

AIN1

AIN2

AIN3

10

0

Absolute Input Current (nA)

Absolute Input Current (nA)

20

±10

±20

±30

±40

AIN0

AIN1

AIN2

AIN3

50

0

±50

±100

±150

±200

±50

±250

0.5

1.0

1.5

2.0

2.5

3.0

Absolute Input Voltage V(AINx) (V)

0.5

40

Differential Input Current (nA)

±20

±40

±1.5

±1.0

±0.5

0.0

0.5

1.0

2.5

3.0

C033

Figure 18. Absolute Input Current vs

Absolute Input Voltage

0

±60

±2.0

2.0

AVDD = 3.3 V, PGA enabled, TA = 125°C

Ta = ±40ƒC

Ta = 25°C

Ta = 85°C

Ta = 125°C

20

1.5

Absolute Input Voltage V(AINx) (V)

Figure 17. Absolute Input Current vs

Absolute Input Voltage

40

1.0

C032

AVDD = 3.3 V, PGA enabled, TA = 85°C

Differential Input Current (nA)

2.0

AVDD = 3.3 V, PGA enabled, TA = 25°C

Figure 15. Absolute Input Current vs

Absolute Input Voltage

1.5

2.0

Differential Input Voltage VIN (V)

Ta = ±40ƒC

Ta = 25°C

Ta = 85°C

Ta = 125°C

20

0

±20

±40

±60

±2.0

±1.5

±1.0

±0.5

0.0

0.5

1.0

1.5

2.0

Differential Input Voltage VIN (V)

C038

AVDD = 3.3 V, PGA enabled, AINP = AIN0, AINN = AIN1

C039

AVDD = 3.3 V, PGA enabled, AINP = AIN3, AINN = AIN2

Figure 19. Differential Input Current vs

Differential Input Voltage

12

1.5

Absolute Input Voltage V(AINx) (V)

C030

Submit Documentation Feedback

Figure 20. Differential Input Current vs

Differential Input Voltage

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Typical Characteristics (continued)

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

15

AIN0

AIN1

AIN2

AIN3

10

Absolute Input Current (nA)

Absolute Input Current (nA)

15

5

0

±5

±10

±15

AIN0

AIN1

AIN2

AIN3

10

5

0

±5

±10

±15

0.5

1.0

1.5

2.0

2.5

3.0

Absolute Input Voltage V(AINx) (V)

0.5

1.0

AVDD = 3.3 V, PGA disabled, TA = –40°C

20

2.5

3.0

C035

Figure 22. Absolute Input Current vs

Absolute Input Voltage

100

AIN0

AIN1

AIN2

AIN3

10

0

Absolute Input Current (nA)

Absolute Input Current (nA)

2.0

AVDD = 3.3 V, PGA disabled, TA = 25°C

Figure 21. Absolute Input Current vs

Absolute Input Voltage

±10

±20

±30

±40

AIN0

AIN1

AIN2

AIN3

50

0

±50

±100

±150

±200

±50

±250

0.5

1.0

1.5

2.0

2.5

3.0

Absolute Input Voltage V(AINx) (V)

0.5

40

Differential Input Current (nA)

±20

±40

±1.5

±1.0

±0.5

0.0

0.5

1.0

2.5

3.0

C037

Figure 24. Absolute Input Current vs

Absolute Input Voltage

0

±60

±2.0

2.0

AVDD = 3.3 V, PGA disabled, TA = 125°C

Ta = ±40ƒC

Ta = 25°C

Ta = 85°C

Ta = 125°C

20

1.5

Absolute Input Voltage V(AINx) (V)

Figure 23. Absolute Input Current vs

Absolute Input Voltage

40

1.0

C036

AVDD = 3.3 V, PGA disabled, TA = 85°C

Differential Input Current (nA)

1.5

Absolute Input Voltage V(AINx) (V)

C034

1.5

2.0

Differential Input Voltage VIN (V)

20

0

±20

±40

±60

±2.0

±1.5

±1.0

±0.5

0.0

0.5

1.0

1.5

2.0

Differential Input Voltage VIN (V)

C040

AVDD = 3.3 V, PGA disabled, AINP = AIN0, AINN = AIN1

Ta = ±40ƒC

Ta = 25°C

Ta = 85°C

Ta = 125°C

C041

AVDD = 3.3 V, PGA disabled, AINP = AIN3, AINN = AIN2

Figure 25. Differential Input Current vs

Differential Input Voltage

Figure 26. Differential Input Current vs

Differential Input Voltage

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

13

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

Typical Characteristics (continued)

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

6

6

IDAC = 1000 µA

IDAC = 500 µA

4

Absolute IDAC Error (%)

4

IDAC Error (%)

IDAC = 100 µA

2

0

±2

2

0

±2

±4

±4

±6

±6

0.5

0.6

0.7

0.8

0.9

±40

1.0

Compliance Voltage (V)

IDAC = 500 µA

0.50

IDAC = 100 µA

40

60

80

100

120

C005

Figure 28. IDAC Accuracy vs Temperature

IDAC = 1000 µA

0.75

20

600

500

400

0.25

IAVDD (µA)

IDAC Matching Error (%)

0

Temperature (ƒC)

Figure 27. IDAC Accuracy vs Compliance Voltage

1.00

±20

C006

0.00

±0.25

300

200

Gain = 64, 128

±0.50

100

±0.75

±1.00

Gain = 1 to 16

PGA Disabled

0

±40

±20

0

20

40

60

80

100

120

Temperature (ƒC)

±40

±20

0

20

40

60

80

100

120

Temperature (ƒC)

C007

C011

AVDD = 3.3 V, internal reference, normal mode

Figure 29. IDAC Matching vs Temperature

Figure 30. IAVDD vs Temperature

150

1000

125

800

IAVDD (µA)

IAVDD (µA)

100

600

400

75

50

Gain = 64, 128

200

PGA Disabled

0

±40

±20

0

20

40

60

80

100

Temperature (ƒC)

Gain = 64, 128

25

Gain = 1 to 16

Gain = 1 to 16

PGA Disabled

0

120

±40

AVDD = 3.3 V, internal reference, turbo mode

0

20

40

60

80

100

120

C013

AVDD = 3.3 V, internal reference, duty-cycle mode

Figure 31. IAVDD vs Temperature

14

±20

Temperature (ƒC)

C012

Submit Documentation Feedback

Figure 32. IAVDD vs Temperature

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Typical Characteristics (continued)

600

120

500

100

400

80

IDVDD (µA)

IAVDD (µA)

At TA = 25°C, AVDD = 3.3 V, AVSS = 0 V, and PGA enabled using external Vref = 2.5 V (unless otherwise noted).

300

200

60

40

Gain = 64, 128

100

Turbo Mode

20

Gain = 1 to 16

Normal Mode

PGA Disabled

0

Duty-Cycle Mode

0

2.5

3.0

3.5

4.0

4.5

5.0

5.5

AVDD (V)

2.5

3.0

3.5

4.0

4.5

5.0

DVDD (V)

C004

5.5

C010

Normal mode, internal reference

Figure 33. IAVDD vs AVDD

Figure 34. IDVDD vs DVDD

120

1.00

Temperature Error (ƒC)

100

IDVDD (µA)

80

60

40

Turbo Mode

20

Normal Mode

±40

±20

0

20

40

60

80

Mean

0.50

Mean - 61

0.25

0.00

±0.25

±0.50

±0.75

Duty-Cycle Mode

0

Mean + 61

0.75

100

±1.00

120

Temperature (ƒC)

±40

±20

0

20

40

60

80

100

Temperature (ƒC)

C014

120

C015

DVDD = 3.3 V

Figure 35. IDVDD vs Temperature

Figure 36. Internal Temperature Sensor Accuracy vs

Temperature

6

5

RON (

4

3

2

AVDD = 2.3 V

1

AVDD = 3.3 V

AVDD = 5.0 V

0

±40

±20

0

20

40

60

Temperature (ƒC)

80

100

120

C001

Figure 37. Low-Side Power Switch RON vs Temperature

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

15

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

7 Parameter Measurement Information

7.1 Noise Performance

Delta-sigma (ΔΣ) analog-to-digital converters (ADCs) are based on the principle of oversampling. The input

signal of a ΔΣ ADC is sampled at a high frequency (modulator frequency) and subsequently filtered and

decimated in the digital domain to yield a conversion result at the respective output data rate. The ratio between

modulator frequency and output data rate is called oversampling ratio (OSR). By increasing the OSR, and thus

reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the inputreferred noise drops when reducing the output data rate because more samples of the internal modulator are

averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is

particularly useful when measuring low-level signals.

Table 1 to Table 8 summarize the device noise performance. Data are representative of typical noise

performance at TA = 25°C using the internal 2.048-V reference. Data shown are the result of averaging readings

from a single device over a time period of approximately 0.75 seconds and are measured with the inputs

internally shorted together. Table 1, Table 3, Table 5 and Table 7 list the input-referred noise in units of μVRMS for

the conditions shown. Note that µVPP values are shown in parenthesis. Table 2, Table 4, Table 6 and Table 8 list

the corresponding data in effective number of bits (ENOB) calculated from μVRMS values using Equation 1. Note

that noise-free bits calculated from peak-to-peak noise values using Equation 2 are shown in parenthesis.

The input-referred noise (Table 1, Table 3, Table 5 and Table 7) only changes marginally when using an external

low-noise reference, such as the REF5020. To calculate ENOB numbers and noise-free bits when using a

reference voltage other than 2.048 V, use Equation 1 to Equation 3:

ENOB = ln (Full-Scale Range / VRMS-Noise) / ln(2)

Noise-Free Bits = ln (Full-Scale Range / VPP-Noise) / ln(2)

Full-Scale Range = 2 · Vref / Gain

(1)

(2)

(3)

Table 1. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, and Internal Reference = 2.048 V

DATA

RATE

(SPS)

GAIN (PGA Enabled)

1

2

4

8

16

32

64

128

20

3.71 (13.67)

1.54 (5.37)

1.15 (4.15)

0.80 (3.36)

0.35 (1.16)

0.23 (0.73)

0.10 (0.35)

0.09 (0.41)

45

7.36 (29.54)

2.93 (13.06)

1.71 (9.28)

0.88 (4.06)

0.50 (2.26)

0.29 (1.49)

0.19 (0.82)

0.12 (0.51)

90

10.55 (47.36)

4.50 (20.75)

2.43 (11.35)

1.51 (6.65)

0.65 (3.62)

0.42 (2.14)

0.27 (1.22)

0.18 (0.85)

175

11.90 (63.72)

6.45 (34.06)

3.26 (17.76)

1.82 (11.20)

1.01 (5.13)

0.57 (3.09)

0.34 (2.14)

0.26 (1.60)

330

19.19 (106.93)

9.38 (50.78)

4.25 (26.25)

2.68 (14.13)

1.45 (7.52)

0.79 (4.66)

0.50 (2.69)

0.34 (1.99)

600

24.78 (151.61)

13.35 (72.27)

6.68 (39.43)

3.66 (19.26)

2.10 (12.77)

1.14 (6.87)

0.70 (4.76)

0.55 (3.34)

1000

37.53 (227.29)

18.87 (122.68)

9.53 (58.53)

5.37 (31.52)

2.95 (18.08)

1.65 (10.71)

1.03 (6.52)

0.70 (4.01)

Table 2. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, and Internal Reference = 2.048 V

16

DATA

RATE

(SPS)

GAIN (PGA Enabled)

1

2

4

8

16

32

64

128

20

20.08 (18.19)

20.34 (18.54)

19.76 (17.91)

19.28 (17.22)

19.48 (17.75)

19.10 (17.42)

19.33 (17.49)

18.49 (16.26)

45

19.09 (17.08)

19.42 (17.26)

19.19 (16.75)

19.15 (16.94)

18.95 (16.79)

18.74 (16.39)

18.38 (16.25)

18.00 (15.49)

90

18.57 (16.40)

18.80 (16.59)

18.68 (16.46)

18.37 (16.23)

18.60 (16.11)

18.20 (15.87)

17.87 (15.67)

17.44 (15.20)

175

18.39 (15.97)

18.28 (15.88)

18.26 (15.82)

18.10 (15.48)

17.96 (15.61)

17.78 (15.34)

17.53 (14.87)

16.91 (14.29)

330

17.70 (15.23)

17.74 (15.30)

17.88 (15.25)

17.54 (15.15)

17.43 (15.05)

17.30 (14.74)

16.96 (14.54)

16.50 (13.97)

600

17.33 (14.72)

17.23 (14.79)

17.23 (14.66)

17.09 (14.70)

16.89 (14.29)

16.77 (14.18)

16.48 (13.72)

15.83 (13.23)

1000

16.74 (14.14)

16.73 (14.03)

16.71 (14.09)

16.54 (13.99)

16.41 (13.79)

16.25 (13.54)

15.92 (13.26)

15.49 (12.96)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Table 3. Noise in μVRMS (μVPP) with PGA Disabled

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, and Internal Reference = 2.048 V

GAIN (PGA Disabled)

DATA RATE

(SPS)

1

2

4

20

3.89 (13.43)

1.85 (6.84)

1.26 (3.91)

45

6.97 (31.98)

2.94 (12.94)

1.41 (5.62)

90

8.50 (42.48)

4.49 (18.92)

2.07 (9.95)

175

12.99 (65.92)

6.24 (35.40)

3.04 (18.92)

330

18.18 (94.24)

8.12 (50.17)

4.71 (28.75)

600

25.29 (138.67)

12.77 (78.13)

6.27 (39.79)

1000

38.04 (260.50)

18.40 (120.97)

9.48 (63.72)

Table 4. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) with PGA Disabled

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, and Internal Reference = 2.048 V

GAIN (PGA Disabled)

DATA RATE

(SPS)

1

2

4

20

20.01 (18.22)

20.08 (18.19)

19.63 (18.00)

45

19.61 (16.97)

19.41 (17.27)

19.47 (17.48)

90

18.88 (16.56)

18.80 (16.72)

18.91 (16.65)

175

18.27 (15.92)

18.32 (15.82)

18.36 (15.72)

330

17.78 (15.41)

17.94 (15.32)

17.73 (15.12)

600

17.31 (14.85)

17.29 (14.68)

17.32 (14.65)

1000

16.72 (13.94)

16.76 (14.05)

16.72 (13.97)

Table 5. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, and Internal Reference = 2.048 V

DATA

RATE

(SPS)

GAIN (PGA Enabled)

1

2

4

8

16

32

64

128

40

4.56 (24.17)

2.40 (11.35)

1.22 (4.94)

0.71 (2.84)

0.35 (1.60)

0.19 (0.85)

0.16 (0.71)

0.09 (0.55)

90

5.74 (25.88)

2.97 (14.40)

1.47 (5.80)

1.13 (5.52)

0.50 (2.67)

0.32 (1.32)

0.23 (1.13)

0.15 (0.69)

180

8.49 (46.88)

4.66 (21.36)

2.30 (12.88)

1.24 (7.23)

0.72 (4.82)

0.42 (2.57)

0.28 (1.47)

0.24 (1.34)

350

13.42 (84.72)

5.86 (40.04)

3.39 (19.04)

1.88 (10.13)

1.05 (6.15)

0.64 (3.59)

0.43 (2.29)

0.28 (1.39)

660

17.09 (120.36)

9.34 (47.36)

4.81 (27.83)

2.97 (17.36)

1.54 (10.21)

0.82 (4.43)

0.58 (3.67)

0.41 (2.93)

1200

25.71 (162.35)

12.31 (85.94)

6.81 (44.01)

3.72 (21.55)

2.09 (15.14)

1.23 (7.58)

0.80 (5.31)

0.57 (3.51)

2000

36.23 (265.14)

18.24 (127.32)

9.24 (65.43)

5.49 (37.02)

2.89 (18.89)

1.77 (12.00)

1.13 (7.60)

0.82 (5.81)

Table 6. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, and Internal Reference = 2.048 V

DATA

RATE

(SPS)

GAIN (PGA Enabled)

1

2

4

8

16

32

64

128

40

19.78 (17.37)

19.71 (17.46)

19.68 (17.66)

19.45 (17.46)

19.47 (17.29)

19.37 (17.21)

18.65 (16.46)

18.40 (15.83)

90

19.45 (17.27)

19.39 (17.12)

19.41 (17.43)

18.79 (16.50)

18.97 (16.55)

18.62 (16.57)

18.11 (15.80)

17.75 (15.49)

180

18.88 (16.42)

18.75 (16.55)

18.76 (16.28)

18.65 (16.11)

18.43 (15.70)

18.23 (15.60)

17.79 (15.41)

17.05 (14.54)

350

18.22 (15.56)

18.42 (15.64)

18.21 (15.71)

18.05 (15.62)

17.89 (15.35)

17.62 (15.12)

17.20 (14.77)

16.78 (14.49)

660

17.87 (15.05)

17.74 (15.40)

17.70 (15.17)

17.39 (14.85)

17.34 (14.61)

17.25 (14.82)

16.75 (14.09)

16.25 (13.42)

1200

17.28 (14.62)

17.34 (14.54)

17.20 (14.51)

17.07 (14.54)

16.90 (14.05)

16.67 (14.04)

16.28 (13.56)

15.77 (13.15)

2000

16.79 (13.92)

16.78 (13.97)

16.76 (13.93)

16.51 (13.76)

16.44 (13.73)

16.14 (13.38)

15.79 (13.04)

15.25 (12.43)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

17

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

Table 7. Noise in μVRMS (μVPP) with PGA Disabled

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, and Internal Reference = 2.048 V

GAIN (PGA Disabled)

DATA RATE

(SPS)

1

2

4

40

4.22 (22.46)

2.30 (10.74)

0.93 (3.91)

90

6.57 (31.01)

3.53 (14.28)

1.59 (6.84)

180

8.41 (55.66)

4.30 (22.09)

2.31 (14.59)

350

12.68 (75.20)

6.02 (34.18)

3.22 (17.64)

660

17.81 (111.08)

9.06 (56.76)

4.24 (27.47)

1200

25.43 (176.03)

12.70 (89.23)

6.28 (40.95)

2000

36.11 (250.98)

17.30 (131.35)

8.77 (68.18)

Table 8. ENOB from RMS Noise (Noise-Free Bits from Peak-to-Peak Noise) with PGA Disabled

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, and Internal Reference = 2.048 V

18

GAIN (PGA Disabled)

DATA RATE

(SPS)

1

2

4

40

19.89 (17.48)

19.76 (17.54)

20.07 (18.00)

90

19.25 (17.01)

19.15 (17.13)

19.29 (17.19)

180

18.89 (16.17)

18.86 (16.50)

18.76 (16.10)

350

18.30 (15.73)

18.38 (15.87)

18.28 (15.83)

660

17.81 (15.17)

17.79 (15.14)

17.88 (15.19)

1200

17.30 (14.51)

17.30 (14.49)

17.31 (14.61)

2000

16.79 (13.99)

16.85 (13.93)

16.83 (13.87)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

8 Detailed Description

8.1 Overview

The ADS1220 is a small, low-power, 24-bit, ΔΣ ADC that offers many integrated features to reduce system cost

and component count in applications measuring small sensor signals.

In addition to the ΔΣ ADC core and single-cycle settling digital filter, the device offers a low-noise, high input

impedance, programmable gain amplifier (PGA), an internal voltage reference, and a clock oscillator. The device

also integrates a highly linear and accurate temperature sensor as well as two matched programmable current

sources (IDACs) for sensor excitation. All of these features are intended to reduce the required external circuitry

in typical sensor applications and improve overall system performance. An additional low-side power switch

eases the design of low-power bridge sensor applications. The device is fully configured through four registers

and controlled by six commands through a mode 1 SPI-compatible interface. The Functional Block Diagram

section shows the device functional block diagram.

The ADS1220 ADC measures a differential signal, VIN, which is the difference in voltage between nodes AINP

and AINN. The converter core consists of a differential, switched-capacitor, ΔΣ modulator followed by a digital

filter. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the

input voltage. This architecture results in a very strong attenuation of any common-mode signal.

The device has two available conversion modes: single-shot and continuous conversion mode. In single-shot

mode, the ADC performs one conversion of the input signal upon request and stores the value in an internal data

buffer. The device then enters a low-power state to save power. Single-shot mode is intended to provide

significant power savings in systems that require only periodic conversions, or when there are long idle periods

between conversions. In continuous conversion mode, the ADC automatically begins a conversion of the input

signal as soon as the previous conversion is completed. New data are available at the programmed data rate.

Data can be read at any time without concern of data corruption and always reflect the most recently completed

conversion.

8.2 Functional Block Diagram

REFP0

AVDD

REFN0

DVDD

10 A to

1.5 mA

Internal

Reference

AIN0/REFP1

AIN1

TI Device

24-Bit

û ADC

Digital Filter

and

SPI

Interface

CS

AINP

MUX

AIN2

Reference

MUX

PGA

AINN

AIN3/REFN1

SCLK

DIN

DOUT/DRDY

DRDY

Precision

Temperature

Sensor

AVSS

Low-Drift

Oscillator

CLK

DGND

Copyright © 2016, Texas Instruments Incorporated

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

19

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

8.3 Feature Description

8.3.1 Multiplexer

The device contains a very flexible input multiplexer, as shown in Figure 38. Either four single-ended signals, two

differential signals, or a combination of two single-ended signals and one differential signal can be measured.

The multiplexer is configured by four bits (MUX[3:0]) in the configuration register. When single-ended signals are

measured, the negative ADC input (AINN) is internally connected to AVSS by a switch within the multiplexer. For

system-monitoring purposes, the analog supply (AVDD – AVSS) / 4 or the currently-selected external reference

voltage (V(REFPx) – V(REFNx)) / 4 can be selected as inputs to the ADC. The multiplexer also offers the possibility to

route any of the two programmable current sources to any analog input (AINx) or to any dedicated reference pin

(REFP0, REFN0).

System Monitors

(V(REFPx) ± V(REFNx)) / 4

(AVDD ± AVSS) / 4

AVDD

AVDD

IDAC1

AVDD

AVSS

AVDD

AVSS

IDAC2

(AVDD + AVSS) / 2

AIN0/REFP1

AVDD

AIN1

Burnout Current Source (10 µA)

AVDD

AVSS

AVDD

AVSS

AIN2

AINP

PGA

To ADC

AINN

AIN3/REFN1

AVDD

AVSS

Burnout Current Source (10 µA)

REFP0

AVDD

AVSS

AVSS

AVSS

REFN0

Figure 38. Analog Input Multiplexer

Electrostatic discharge (ESD) diodes to AVDD and AVSS protect the inputs. To prevent the ESD diodes from

turning on, the absolute voltage on any input must stay within the range provided by Equation 4:

AVSS – 0.3 V < V(AINx) < AVDD + 0.3 V

(4)

If the voltages on the input pins have any potential to violate these conditions, external Schottky clamp diodes or

series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings

table). Overdriving an unused input on the device may affect conversions taking place on other input pins. If any

overdrive on unused inputs is possible, TI recommends clamping the signal with external Schottky diodes.

20

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

Feature Description (continued)

8.3.2 Low-Noise PGA

The device features a low-noise, low-drift, high input impedance, programmable gain amplifier (PGA). The PGA

can be set to gains of 1, 2, 4, 8, 16, 32, 64, or 128. Three bits (GAIN[2:0]) in the configuration register are used

to configure the gain. A simplified diagram of the PGA is shown in Figure 39. The PGA consists of two chopperstabilized amplifiers (A1 and A2) and a resistor feedback network that sets the PGA gain. The PGA input is

equipped with an electromagnetic interference (EMI) filter.

200 O

AINP

+

25 pF

A1

RF

OUTP

VIN

RG

VOUT = Gain·VIN

RF

OUTN

A2

200 O

AINN

+

25 pF

Figure 39. Simplified PGA Diagram

VIN denotes the differential input voltage VIN = (V(AINP) – V(AINN)). The gain of the PGA can be calculated with

Equation 5:

Gain = 1 + 2 · RF / RG

(5)

Gain is changed inside the device using a variable resistor, RG. The differential full-scale input voltage range

(FSR) of the PGA is defined by the gain setting and the reference voltage used, as shown in Equation 6:

FSR = ±Vref / Gain

(6)

Table 9 shows the corresponding full-scale ranges when using the internal 2.048-V reference.

Table 9. PGA Full-Scale Range

GAIN SETTING

FSR

1

±2.048 V

2

±1.024 V

4

±0.512 V

8

±0.256 V

16

±0.128 V

32

±0.064 V

64

±0.032 V

128

±0.016 V

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

21

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

8.3.2.1 PGA Common-Mode Voltage Requirements

To stay within the linear operating range of the PGA, the input signals must meet certain requirements that are

discussed in this section.

The outputs of both amplifiers (A1 and A2) in Figure 39 can not swing closer to the supplies (AVSS and AVDD)

than 200 mV. If the outputs OUTP and OUTN are driven to within 200 mV of the supply rails, the amplifiers

saturate and consequently become nonlinear. To prevent this nonlinear operating condition the output voltages

must meet Equation 7:

AVSS + 0.2 V ≤ V(OUTN), V(OUTP) ≤ AVDD – 0.2 V

(7)

Translating the requirements of Equation 7 into requirements referred to the PGA inputs (AINP and AINN) is

beneficial because there is no direct access to the outputs of the PGA. The PGA employs a symmetrical design,

therefore the common-mode voltage at the output of the PGA can be assumed to be the same as the commonmode voltage of the input signal, as shown in Figure 40.

AINP

+

A1

½ V IN

OUTP

RF

½ Gain·V IN

VCM = ½ (V (AINP) + V(AINN))

RG

½ Gain·V IN

RF

OUTN

½ V IN

A2

AINN

+

Figure 40. PGA Common-Mode Voltage

The common-mode voltage is calculated using Equation 8:

VCM = ½ (V(AINP) + V(AINN)) = ½ (V(OUTP) + V(OUTN))

(8)

The voltages at the PGA inputs (AINP and AINN) can be expressed as Equation 9 and Equation 10:

V(AINP) = VCM + ½ VIN

V(AINN) = VCM – ½ VIN

(9)

(10)

The output voltages (V(OUTP) and V(OUTN)) can then be calculated as Equation 11 and Equation 12:

V(OUTP) = VCM + ½ Gain · VIN

V(OUTN) = VCM – ½ Gain · VIN

(11)

(12)

The requirements for the output voltages of amplifiers A1 and A2 (Equation 7) can now be translated into

requirements for the input common-mode voltage range using Equation 11 and Equation 12, which are given in

Equation 13 and Equation 14:

VCM (MIN) ≥ AVSS + 0.2 V + ½ Gain · VIN (MAX)

VCM (MAX) ≤ AVDD – 0.2 V – ½ Gain · VIN (MAX)

(13)

(14)

In order to calculate the minimum and maximum common-mode voltage limits, the maximum differential input

voltage (VIN (MAX)) that occurs in the application must be used. VIN (MAX) can be less than the maximum possible

FS value.

In addition to Equation 13, the minimum VCM must also meet Equation 15 because of the specific design

implementation of the PGA.

VCM

22

(MIN)

≥ AVSS + ¼ (AVDD – AVSS)

(15)

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

3.30

3.30

2.75

2.75

2.20

2.20

VCM Range (V)

VCM Range (V)

Figure 41 and Figure 42 show a graphical representation of the common-mode voltage limits for AVDD = 3.3 V

and AVSS = 0 V, with gain = 1 and gain = 16, respectively.

1.65

AVDD / 4

1.10

0.55

1.65

AVDD / 4

1.10

0.55

0.00

0.0

0.5

1.0

1.5

2.0

2.5

0.00

0.00

3.0

VIN (V)

0.03

0.06

0.09

0.12

0.15

VIN (V)

C009

AVDD = 3.3 V

0.18

C008

AVDD = 3.3 V

Figure 41. Common-Mode Voltage Limits (Gain = 1)

Figure 42. Common-Mode Voltage Limits (Gain = 16)

The following discussion explains how to apply Equation 13 through Equation 15 to a hypothetical application.

The setup for this example is AVDD = 3.3 V, AVSS = 0 V, and gain = 16, using an external reference,

Vref = 2.5 V. The maximum possible differential input voltage VIN = (V(AINP) – V(AINN)) that can be applied is then

limited to the full-scale range of FSR = ±2.5 V / 16 = ±0.156 V. Consequently, Equation 13 through Equation 15

yield an allowed VCM range of 1.45 V ≤ VCM ≤ 1.85 V.

If the sensor signal connected to the inputs in this hypothetical application does not make use of the entire fullscale range but is limited to VIN (MAX) = ±0.1 V, for example, then this reduced input signal amplitude relaxes the

VCM restriction to 1.0 V ≤ VCM ≤ 2.3 V.

In the case of a fully-differential sensor signal, each input (AINP, AINN) can swing up to ±50 mV around the

common-mode voltage (V(AINP) + V(AINN)) / 2, which must remain between the limits of 1.0 V and 2.3 V. The

output of a symmetrical wheatstone bridge is an example of a fully-differential signal. Figure 43 shows a situation

where the common-mode voltage of the input signal is at the lowest limit. V(OUTN) is exactly at 0.2 V in this case.

Any further decrease in common-mode voltage (VCM) or increase in differential input voltage (VIN) drives V(OUTN)

below 0.2 V and saturates amplifier A2.

V(AINP) = 1.05 V

+

A1

50 mV

RF

V(OUTP) = 1.8 V

800 mV

VCM = 1.0 V

RF/7.5

RF

800 mV

V(OUTN) = 0.2 V

50 mV

A2

V(AINN) = 0.95 V

+

Figure 43. Example where VCM is at Lowest Limit

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

23

�ADS1220

SBAS501C – MAY 2013 – REVISED AUGUST 2016

www.ti.com

In contrast, the signal of an RTD is of a pseudo-differential nature (if implemented as shown in the RTD

Measurement section), where the negative input is held at a constant voltage other than 0 V and only the voltage

on the positive input changes. When a pseudo-differential signal must be measured, the negative input in this

example must be biased at a voltage between 0.95 V and 2.25 V. The positive input can then swing up to

VIN (MAX) = 100 mV above the negative input. Note that in this case the common-mode voltage changes at the

same time the voltage on the positive input changes. That is, while the input signal swings between 0 V ≤ VIN ≤

VIN (MAX), the common-mode voltage swings between V(AINN) ≤ VCM ≤ V(AINN) + ½ VIN (MAX). Satisfying the

common-mode voltage requirements for the maximum input voltage VIN (MAX) ensures the requirements are met

throughout the entire signal range.

Figure 44 and Figure 45 show examples of both fully-differential and pseudo-differential signals, respectively.

AINP

AINP

VCM

VCM

1.0 V

100 mV

1.0 V

100 mV

AINN

AINN

0V

0V

Figure 44. Fully-Differential Input Signal

Figure 45. Pseudo-Differential Input Signal

NOTE

Remember, common-mode voltage requirements with PGA enabled (Equation 13 to

Equation 15) are as follows:

• VCM (MIN) ≥ AVSS + ¼ (AVDD – AVSS)

• VCM (MIN) ≥ AVSS + 0.2 V + ½ Gain · VIN (MAX)

• VCM (MAX) ≤ AVDD – 0.2 V – ½ Gain · VIN (MAX)

8.3.2.2 Bypassing the PGA

At gains of 1, 2, and 4, the device can be configured to disable and bypass the low-noise PGA by setting the

PGA_BYPASS bit in the configuration register. Disabling the PGA lowers the overall power consumption and

also removes the restrictions of Equation 13 through Equation 15 for the common-mode input voltage range,

VCM. The usable absolute and common-mode input voltage range is (AVSS – 0.1 V ≤ V(AINx), VCM ≤ AVDD +

0.1 V) when the PGA is disabled.

In order to measure single-ended signals that are referenced to AVSS (AINP = VIN, AINN = AVSS), the PGA must

be bypassed. Configure the device for single-ended measurements by either connecting one of the analog inputs

to AVSS externally or by using the internal AVSS connection of the multiplexer (MUX[3:0] settings 1000 through

1011). When configuring the internal multiplexer for settings where AINN = AVSS (MUX[3:0] = 1000 through

1011) the PGA is automatically bypassed and disabled irrespective of the PGA_BYPASS setting and gain is

limited to 1, 2, and 4. In case gain is set to greater than 4, the device limits gain to 4.

When the PGA is disabled, the device uses a buffered switched-capacitor stage to obtain gains of 1, 2, and 4. An

internal buffer in front of the switched-capacitor stage ensures that the effect on the input loading resulting from

the capacitor charging and discharging is minimal. See Figure 21 to Figure 26 for the typical values of absolute

input currents (current flowing into or out of each input) and differential input currents (difference in absolute

current between positive and negative input) when the PGA is disabled.

For signal sources with high output impedance, external buffering may still be necessary. Note that active buffers

introduce noise and also introduce offset and gain errors. Consider all of these factors in high-accuracy

applications.

24

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: ADS1220

�ADS1220

www.ti.com

SBAS501C – MAY 2013 – REVISED AUGUST 2016

8.3.3 Modulator

A ΔΣ modulator is used in the ADS1220 to convert the analog input voltage into a pulse code modulated (PCM)

data stream. The modulator runs at a modulator clock frequency of f(MOD) = f(CLK) / 16 in normal and duty-cycle

mode and f(MOD) = f(CLK) / 8 in turbo mode, where f(CLK) is either provided by the internal oscillator or the external

clock source. Table 10 shows the modulator frequency for each operating mode using either the internal

oscillator or an external clock of 4.096 MHz.

Table 10. Modulator Clock Frequency for Different

Operating Modes (1)

(1)

OPERATING MODE

f(MOD)

Duty-cycle mode

256 kHz

Normal mode

256 kHz

Turbo mode

512 kHz

Using the internal oscillator or an external 4.096-MHz clock.

8.3.4 Digital Filter

The device uses a linear-phase finite impulse response (FIR) digital filter that performs both filtering and

decimation of the digital data stream coming from the modulator. The digital filter is automatically adjusted for the

different data rates and always settles within a single cycle. At data rates of 5 SPS and 20 SPS, the filter can be

configured to reject 50-Hz or 60-Hz line frequencies or to simultaneously reject 50 Hz and 60 Hz. Two bits

(50/60[1:0]) in the configuration register are used to configure the filter accordingly. The frequency responses of

the digital filter are illustrated in Figure 46 to Figure 59 for different output data rates using the internal oscillator

or an external 4.096-MHz clock.

0

0

±40

±40

Magnitude (dB)

Magnitude (dB)

The filter notches and output data rate scale proportionally with the clock frequency. For example, a notch that

appears at 20 Hz when using a 4.096-MHz clock appears at 10 Hz if a 2.048-MHz clock is used. Note that the

internal oscillator can vary over temperature as specified in the Electrical Characteristics table. The data rate or

conversion time, respectively, and filter notches consequently vary by the same amount. Consider using an

external precision clock source if a digital filter notch at a specific frequency with a tighter tolerance is required.

±80

±120

±160

±80

±120

±160

±200

±200

0

20

40

60

80

100 120 140 160 180 200

Frequency (Hz)

Simultaneous 50-Hz and 60-Hz Rejection, 50/60[1:0] = 01

Figure 46. Filter Response

(DR = 20 SPS)

46

48

50

52

54

56

58

60

62

Frequency (Hz)

C049

64

C050

Simultaneous 50-Hz and 60-Hz Rejection, 50/60[1:0] = 01

Figure 47. Detailed View of Filter Response

(DR = 20 SPS)

Submit Documentation Feedback