CSD16323Q3C

www.ti.com

SLPS248 – AUGUST 2010

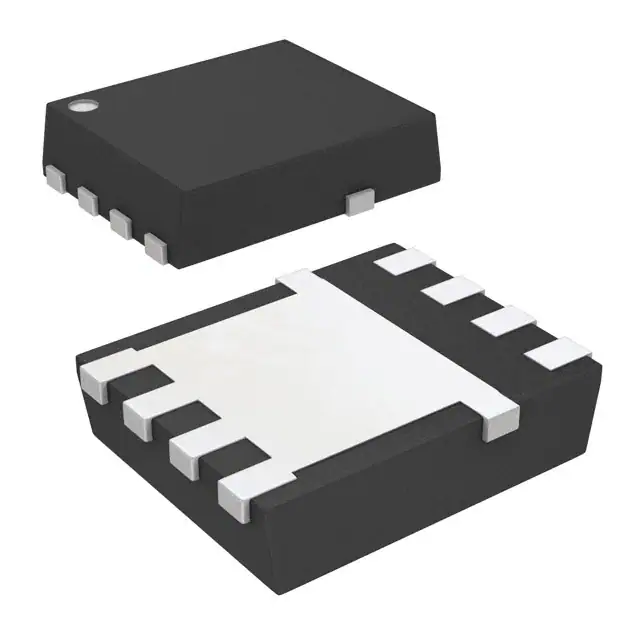

N-Channel NexFET™ Power MOSFETs

Check for Samples: CSD16323Q3C

PRODUCT SUMMARY

FEATURES

1

•

•

•

•

•

•

•

•

•

2

DualCool™ Package

Optimized for 5V Gate Drive

Ultra Low Qg and Qgd

Low Thermal Resistance

Avalanche Rated

Pb Free Terminal Plating

RoHS Compliant

Halogen Free

SON 3.3-mm × 3.3-mm Plastic Package

VDS

Drain to Source Voltage

25

V

Qg

Gate Charge Total (4.5V)

6.2

nC

Qgd

Gate Charge Gate to Drain

RDS(on)

1.1

Drain to Source On Resistance

Vth

nC

VGS = 3V

5.4

mΩ

VGS = 4.5V

4.4

mΩ

VGS = 8V

3.8

mΩ

Threshold Voltage

1.1

V

ORDERING INFORMATION

Device

Package

Media

CSD16323Q3C

SON 3.3-mm × 3.3-mm

Plastic Package

13-Inch

Reel

Qty

Ship

2500

Tape and

Reel

APPLICATIONS

•

•

Point-of-Load Synchronous Buck Converter

for Applications in Networking, Telecom and

Computing Systems

Optimized for Control or Synchronous FET

Applications

ABSOLUTE MAXIMUM RATINGS

TA = 25°C unless otherwise stated

VALUE

UNIT

VDS

Drain to Source Voltage

25

V

VGS

Gate to Source Voltage

+10 / –8

V

Continuous Drain Current, TC = 25°C

60

A

Continuous Drain Current(1)

21

A

IDM

Pulsed Drain Current, TA = 25°C(2)

112

A

PD

Power Dissipation(1)

3

W

TJ,

TSTG

Operating Junction and Storage

Temperature Range

–55 to 150

°C

EAS

Avalanche Energy, single pulse

ID = 50A, L = 0.1mH, RG = 25Ω

125

mJ

ID

DESCRIPTION

The NexFET™ power MOSFET has been designed

to minimize losses in power conversion and optimized

for 5V gate drive applications. Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

Text

Added

For

Spacing

(1) Typical RqJA = 43°C/W when mounted on a 1-inch2

(6.45-cm2), 2-oz. (0.071-mm thick) Cu pad on a 0.06-inch

(1.52-mm) thick FR4 PCB.

(2) Pulse duration ≤300ms, duty cycle ≤2% Text Added For

Spacing

Text

Added

For

Spacing

RDS(ON) vs VGS

GATE CHARGE

10

ID = 24A

14

12

10

TC = 125°C

8

ID = 24A

VDS = 12.5V

9

VG − Gate Voltage − V

RDS(on) − On-State Resistance − mW

16

6

4

8

7

6

5

4

3

2

2

TC = 25°C

1

0

0

0

1

2

3

4

5

6

7

8

VGS − Gate to Source Voltage − V

9

10

G006

0

2

4

6

8

10

12

14

Qg − Gate Charge − nC

G003

1

2

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DualCool, NexFET are trademarks of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2010, Texas Instruments Incorporated

�CSD16323Q3C

SLPS248 – AUGUST 2010

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

ELECTRICAL CHARACTERISTICS

(TA = 25°C unless otherwise stated)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Static Characteristics

BVDSS

Drain to Source Voltage

VGS = 0V, ID = 250mA

IDSS

Drain to Source Leakage Current

VGS = 0V, VDS = 20V

IGSS

Gate to Source Leakage Current

VDS = 0V, VGS = +10/-8V

VGS(th)

Gate to Source Threshold Voltage

VDS = VGS, ID = 250mA

RDS(on)

gfs

Drain to Source On Resistance

Transconductance

25

0.9

V

1

mA

100

nA

1.1

1.4

V

VGS = 3V, ID = 24A

5.4

7.2

mΩ

VGS = 4.5V, ID = 24A

4.4

5.5

mΩ

VGS = 8V, ID = 24A

3.8

4.5

mΩ

VDS = 12.5V, ID = 24A

108

S

Dynamic Characteristics

CISS

Input Capacitance

COSS

Output Capacitance

1020

1300

pF

740

960

CRSS

pF

Reverse Transfer Capacitance

50

65

pF

Rg

Series Gate Resistance

1.4

2.8

Ω

Qg

Gate Charge Total (4.5V)

6.2

8.4

nC

Qgd

Gate Charge Gate to Drain

Qgs

Gate Charge Gate to Source

Qg(th)

Gate Charge at Vth

QOSS

Output Charge

td(on)

Turn On Delay Time

tr

Rise Time

td(off)

Turn Off Delay Time

tf

Fall Time

VGS = 0V, VDS = 12.5V, f = 1MHz

VDS = 12.5V, ID = 24A

VDS = 12.5V, VGS = 0V

VDS = 12.5V, VGS = 4.5V ID = 24A

RG = 2Ω

1.1

nC

1.8

nC

1

nC

14

nC

5.3

ns

15

ns

13

ns

6.3

ns

Diode Characteristics

VSD

Diode Forward Voltage

IS = 24A, VGS = 0V

Qrr

Reverse Recovery Charge

VDD = 12.5V, IF = 24A, di/dt = 300A/ms

0.85

21

1

nC

V

trr

Reverse Recovery Time

VDD = 12.5V, IF = 24A, di/dt = 300A/ms

16

ns

THERMAL CHARACTERISTICS

(TA = 25°C unless otherwise stated)

PARAMETER

qJC(top)

qJC(bot)

Junction-to-case (bottom) thermal resistance

q JA

Junction to Ambient thermal resistance

(1)

(2)

2

MIN

Junction-to-case (top) thermal resistance

(1)

(1) (2)

2

TYP

MAX

UNIT

3.5

°C/W

2.7

°C/W

58

°C/W

2

RqJC is determined with the device mounted on a 1-inch (6.45-cm ), 2-oz. (0.071-mm thick) Cu pad on a 1.5-inch × 1.5-inch (3.81-cm ×

3.81-cm), 0.06-inch (1.52-mm) thick FR4 PCB. RqJC is specified by design, whereas RqJA is determined by the user’s board design.

Device mounted on FR4 material with 1-inch2 (6.45-cm2), 2-oz. (0.071-mm thick) Cu.

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

�CSD16323Q3C

www.ti.com

SLPS248 – AUGUST 2010

GATE

GATE

Source

Source

Max RqJA = 58°C/W

when mounted on 1

inch2 (6.45 cm2) of

2-oz. (0.071-mm thick)

Cu.

Max RqJA = 162°C/W

when mounted on a

minimum pad area of

2-oz. (0.071-mm thick)

Cu.

DRAIN

DRAIN

M0161-02

M0161-01

TYPICAL MOSFET CHARACTERISTICS

(TA = 25°C unless otherwise stated)

ZqJA – NormalizedThermal Impedance

10

1

0.5

0.3

0.1

Duty Cycle = t1/t2

0.1

0.05

0.01

P

0.02

0.01

t1

t2

Typical RqJA = 138°C/W (min Cu)

TJ = P ´ ZqJA ´ RqJA

Single Pulse

0.001

0.001

0.01

0.1

1

10

100

1k

tP – Pulse Duration–s

G012

Figure 1. Transient Thermal Impedance

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

3

�CSD16323Q3C

SLPS248 – AUGUST 2010

www.ti.com

TYPICAL MOSFET CHARACTERISTICS (continued)

(TA = 25°C unless otherwise stated)

60

60

50

VGS = 4.5V

40

ID − Drain Current − A

50

ID − Drain Current − A

VDS = 5V

VGS = 8V

VGS = 2V

VGS = 3.5V

30

20

VGS = 2.5V

10

40

TC = 125°C

30

TC = 25°C

20

TC = −55°C

10

0

0.0

0

0.5

1.0

1.5

1

2.0

VDS − Drain to Source Voltage − V

1.25

1.75

2

2.25

2.5

VGS − Gate to Source Voltage − V

G001

Figure 2. Saturation Characteristics

G002

Figure 3. Transfer Characteristics

10

2.5

f = 1MHz

VGS = 0V

ID = 24A

VDS = 12.5V

9

8

C − Capacitance − nF

VG − Gate Voltage − V

1.5

7

6

5

4

3

2.0

CISS = CGD + CGS

1.5

COSS = CGD + CGS

1.0

CRSS = CGD

0.5

2

1

0

0.0

0

2

4

6

8

10

12

14

Qg − Gate Charge − nC

0

5

G003

Figure 4. Gate Charge

RDS(on) − On-State Resistance − mW

VGS(th) − Threshold Voltage − V

20

25

G004

16

ID = 250mA

1.2

1.0

0.8

0.6

0.4

0.2

ID = 24A

14

12

10

TC = 125°C

8

6

4

2

TC = 25°C

0

−25

25

75

125

175

TC − Case Temperature − °C

0

1

2

3

4

5

6

7

8

VGS − Gate to Source Voltage − V

G005

Figure 6. Threshold Voltage vs. Temperature

4

15

Figure 5. Capacitance

1.4

0.0

−75

10

VDS − Drain to Source Voltage − V

9

10

G006

Figure 7. On-State Resistance vs. Gate-to-Source Voltage

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

�CSD16323Q3C

www.ti.com

SLPS248 – AUGUST 2010

TYPICAL MOSFET CHARACTERISTICS (continued)

(TA = 25°C unless otherwise stated)

1.4

100

ID = 24A

VGS = 10V

ISD − Source to Drain Current − A

Normalized On-State Resistance

1.6

1.2

1.0

0.8

0.6

0.4

0.2

0.0

−75

10

1

TC = 125°C

0.1

TC = 25°C

0.01

0.001

0.0001

−25

25

75

125

175

TC − Case Temperature − °C

0.0

0.2

1.0

G008

1k

I(AV) − Peak Avalanche Current − A

ID − Drain Current − A

0.8

Figure 9. Typical Diode Forward Voltage

1k

100

100ms

10

1ms

Area Limited

by RDS(on)

10ms

100ms

0.1

0.01

0.01

0.6

VSD − Source to Drain Voltage − V

G007

Figure 8. Normalized On-State Resistance vs. Temperature

1

0.4

Single Pulse

RqJA = 138°C/W (min Cu)

0.1

DC

1

10

TC = 125°C

10

1

0.01

100

VDS − Drain To Source Voltage − V

TC = 25°C

100

0.1

1

10

t(AV) − Time in Avalanche − ms

G009

Figure 10. Maximum Safe Operating Area

100

G010

Figure 11. Single Pulse Unclamped Inductive Switching

80

ID − Drain Current − A

70

60

50

40

30

20

10

0

−50

−25

0

25

50

75

100

125

TC − Case Temperature − °C

150

175

G011

Figure 12. Maximum Drain Current vs. Temperature

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

5

�CSD16323Q3C

SLPS248 – AUGUST 2010

www.ti.com

MECHANICAL DATA

Q3C Package Dimensions

D

N

D2

H

7

2

M

3

4

6

5

M1

5

3

4

6

Pin 9

b

E2

7

2

Exposed

Heat Slug

L

8

8

1

q

e

E

c1

1

N1

q

L1

A1

Top View

Bottom View

Side View

Pinout

Label

Source

A

c

Pin #

1, 2, 3, 9

4

Gate

5, 6, 7, 8

Drain

Front View

M0198-01

DIM

MILLIMETERS

NOM

MAX

MIN

NOM

MAX

A

0.950

1.000

1.100

0.037

0.039

0.043

A1

0.000

0.000

0.050

0.000

0.000

0.002

b

0.280

0.340

0.400

0.011

0.013

0.016

c

0.150

0.200

0.250

0.006

0.008

0.010

c1

0.150

0.200

0.250

0.006

0.008

0.010

D

3.200

3.300

3.400

0.126

0.130

0.134

D2

1.650

1.750

1.800

0.065

0.069

0.071

E

3.200

3.300

3.400

0.126

0.130

0.134

E2

2.350

2.450

2.550

0.093

0.096

0.100

e

6

INCHES

MIN

0.650 TYP

0.026

H

0.35

0.450

0.550

0.014

0.018

0.022

L

0.35

0.450

0.550

0.014

0.018

0.022

L1

–

–

–

–

–

–

M

1.561

1.661

1.761

0.061

0.065

0.069

M1

1.130

1.230

1.330

0.044

0.048

0.052

N

1.854

1.954

2.054

0.073

0.077

0.081

N1

0.846

0.946

1.046

0.033

0.037

0.041

q

–

–

–

–

–

–

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

�CSD16323Q3C

www.ti.com

SLPS248 – AUGUST 2010

2.31

1

8

8

1

0.65 Typ.

2.45

5

4

5

3.50

0.56

0.41

4

0.50 Typ.

Recommended PCB Pattern

0.63

M0143-01

For recommended circuit layout for PCB designs, see application note SLPA005 – Reducing Ringing Through

PCB Layout Techniques.

1.75 ±0.10

Text Added For Spacing

Text Added For Spacing

Q3 Tape and Reel Information

4.00 ±0.10 (See Note 1)

2.00 ±0.05

Ø 1.50

+0.10

–0.00

1.30

3.60

5.50 ±0.05

12.00

+0.30

–0.10

8.00 ±0.10

3.60

M0144-01

NOTES: 1. 10-sprocket hole-pitch cumulative tolerance ±0.2

2. Camber not to exceed 1mm in 100mm, noncumulative over 250mm

3. Material: black static-dissipative polystyrene

4. All dimensions are in mm, unless otherwise specified.

5. Thickness: 0.30 ±0.05mm

6. MSL1 260°C (IR and convection) PbF reflow compatible

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

Product Folder Link(s): CSD16323Q3C

7

�PACKAGE OPTION ADDENDUM

www.ti.com

17-Nov-2018

PACKAGING INFORMATION

Orderable Device

Status

(1)

CSD16323Q3C

NRND

Package Type Package Pins Package

Drawing

Qty

VSON-CLIP

DQV

8

Eco Plan

Lead/Ball Finish

MSL Peak Temp

(2)

(6)

(3)

TBD

Call TI

Call TI

Op Temp (°C)

Device Marking

(4/5)

0 to 0

A323C

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance

do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may

reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of