Order

Now

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

TPS55330 Integrated 5-A, 24-V Boost/SEPIC/Flyback DC-DC Regulator

1 Features

3 Description

•

•

•

•

•

•

•

•

•

•

The TPS55330 is a monolithic nonsynchronous

switching regulator with integrated 5-A, 24-V power

switch. The device can be configured in several

standard switching-regulator topologies, including

boost, SEPIC, and isolated flyback. The device has a

wide input voltage range to support applications with

input voltage from multicell batteries or regulated 3.3V, 5-V, and 12-V power rails.

1

•

•

•

•

Internal 5-A, 24-V Low-Side MOSFET Switch

2.9-V to 16-V Input Voltage Range

±0.7% Reference Voltage

0.5-mA Operating Quiescent Current

2.7-µA Shutdown Supply Current

Fixed-Frequency-Current-Mode PWM Control

Frequency Adjustable From 100 kHz to 1.2 MHz

Synchronization Capability to External Clock

Adjustable Soft-Start Time

Pulse-Skipping for Higher Efficiency at Light

Loads

Cycle-by-Cycle Current Limit, Thermal Shutdown,

and UVLO Protection

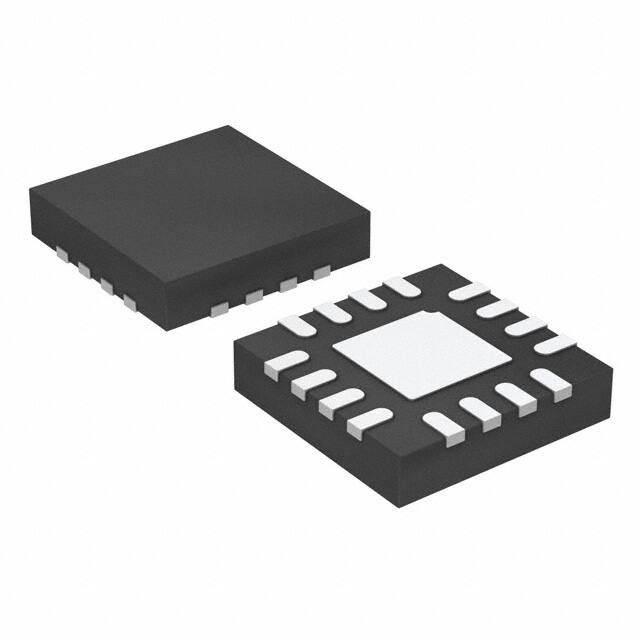

QFN-16 (3 mm × 3 mm) With PowerPAD™

Wide –40°C to +150°C Operating TJ Range

Create a Custom Design Using the TPS55330

With the WEBENCH® Power Designer

2 Applications

•

•

•

•

•

3.3-V, 5-V, 12-V Power Conversion

Boost, SEPIC, and Flyback Topologies

Thunderbolt Port, Power Docking for Tablets and

Portable PCs

Industrial Power Systems

ADSL Modems

The TPS55330 regulates the output voltage with

current mode PWM (pulse width modulation) control,

and has an internal oscillator. The switching

frequency of PWM is set by either an external resistor

or by synchronizing to an external clock signal. The

user can program the switching frequency from

100 kHz to 1.2 MHz.

The device features a programmable soft-start

function to limit inrush current during start up and has

other built-in protection features including cycle-bycycle overcurrent limit and thermal shutdown.

The TPS55330 is available in a small 3-mm × 3-mm

16-pin QFN with PowerPAD for enhanced thermal

performance.

Device Information(1)

PART NUMBER

TPS55330

VIN

BODY SIZE (NOM)

WQFN (16)

3.00 mm × 3.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Application (Boost)

L

PACKAGE

Efficiency vs Output Current

D

100

VOUT

95

CO

TPS55330

VIN

SW

EN

SW

FREQ

SW

RSH

SS

FB

COMP

PGND

SYNC

PGND

AGND

PGND

CSS

RFREQ

RC

CC

90

Efficiency (%)

CI

85

80

75

fSW = 600 kHz

VOUT = 5 V

70

65

RSL

VIN = 2.9 V

VIN = 3.6 V

VIN = 4.2 V

60

55

50

0

0.5

1

1.5

2

Output Current (A)

2.5

3

G017

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

4

4

4

4

5

6

Absolute Maximum Ratings ......................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics...........................................

Typical Characteristics ..............................................

Detailed Description .............................................. 9

7.1

7.2

7.3

7.4

Overview ................................................................... 9

Functional Block Diagram ......................................... 9

Feature Description................................................... 9

Device Functional Modes........................................ 12

8

Application and Implementation ........................ 13

8.1 Application Information............................................ 13

8.2 Typical Application .................................................. 13

9 Power Supply Recommendations...................... 22

10 Layout................................................................... 22

10.1 Layout Guidelines ................................................. 22

10.2 Layout Example .................................................... 22

10.3 Thermal Considerations ........................................ 23

11 Device and Documentation Support ................. 24

11.1

11.2

11.3

11.4

11.5

11.6

Device Support......................................................

Receiving Notification of Documentation Updates

Community Resources..........................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

24

24

24

24

24

25

12 Mechanical, Packaging, and Orderable

Information ........................................................... 25

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (October 2014) to Revision B

Page

•

Added links for Webench ....................................................................................................................................................... 1

•

Added text note under pin configuration diagram................................................................................................................... 3

Changes from Original (May 2013) to Revision A

•

2

Page

Added Pin Configuration and Functions section, ESD Rating table, Feature Description section, Device Functional

Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device

and Documentation Support section, and Mechanical, Packaging, and Orderable Information section .............................. 1

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

�TPS55330

www.ti.com

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

5 Pin Configuration and Functions

SW

1

VIN

2

SW

SW

NC

PGND

16-Pin RTE

QFN Package

Top View

16

15

14

13

12

PGND

11

PGND

NC

PowerPAD

4

9

5

6

7

8

FB

SS

COMP

10

AGND

3

SYNC

EN

FREQ

TI recommends connecting NC with AGND.

Pin Functions

PIN

NAME

VIN

DESCRIPTION

NUMBER

2

The input supply pin to the IC. Connect VIN to a supply voltage between 2.9 V and 16 V. It is acceptable for

the voltage on the pin to be different from the boost power stage input.

SW

1, 15, 16

FB

8

Error amplifier input and feedback pin for positive voltage regulation. Connect to the center tap of a resistor

divider to program the output voltage.

EN

3

Enable pin. When the voltage of this pin falls below the enable threshold for more than 1 ms, the IC turns

off.

COMP

7

Output of the transconductance error amplifier. An external RC network connected to this pin compensates

the regulator feedback loop.

SS

4

Soft-start programming pin. A capacitor between the SS pin and AGND pin programs soft-start timing.

FREQ

9

Switching frequency program pin. An external resistor connected between the FREQ pin and AGND sets the

switching frequency.

AGND

6

Signal ground of the IC.

PGND

11, 12, 13

SYNC

5

NC

PowerPAD

10, 14

17

SW is the drain of the internal power MOSFET. Connect SW to the switched side of the boost or SEPIC

inductor or the flyback transformer.

Power ground of the IC. It is connected to the source of the internal power MOSFET switch.

Switching frequency synchronization pin. An external clock signal can be used to set the switching frequency

between 200 kHz and 1 MHz. If not used, this pin should be tied to AGND.

Reserved pin that must be connected to ground.

Solder the PowerPAD to the AGND. If possible, use thermal vias to connect to internal ground plane for

improved power dissipation.

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

3

�TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings (1)

over operating temperature range (unless otherwise noted)

Supply voltages on pin VIN (2)

Voltage on pin EN

(2)

(1)

(2)

MAX

UNIT

18

V

–0.3

18

V

Voltage on pins FB, FREQ, and COMP (2)

–0.3

3

V

Voltage on pin SS (2)

–0.3

5

V

V

Voltage on pin SYNC

Tstg

MIN

–0.3

(2)

–0.3

7

Voltage on pin SW (2)

–0.3

24

V

Operating junction temperature range

–40

150

°C

Storage temperature range

–65

150

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltage values are with respect to network ground pin

6.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2000

Charged-device model (CDM), per JEDEC specification JESD22C101 (2)

±500

UNIT

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

MIN

MAX

UNIT

VIN

Input voltage range

2.9

16

V

VOUT

Output voltage range

VIN

22

V

VEN

EN voltage range

0

16

V

VSYN

External switching frequency logic input range

0

5

V

TA

Operating free-air temperature

–40

125

°C

TJ

Operating junction temperature

–40

150

°C

6.4 Thermal Information

TPS55330

THERMAL METRIC (1)

QFN

UNIT

16 PINS

RθJA

Junction-to-ambient thermal resistance

43.3

RθJC(top)

Junction-to-case (top) thermal resistance

38.7

RθJB

Junction-to-board thermal resistance

14.5

ψJT

Junction-to-top characterization parameter

0.4

ψJB

Junction-to-board characterization parameter

14.5

RθJC(bot)

Junction-to-case (bottom) thermal resistance

3.5

(1)

4

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

�TPS55330

www.ti.com

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

6.5 Electrical Characteristics

VIN = 5 V, TJ = –40°C to +150°C, unless otherwise noted. Typical values are at TA = 25°C.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SUPPLY CURRENT

VIN

Input voltage range

IQ

Operating quiescent current into VIN

Device non-switching, VFB = 2 V

2.9

0.5

16

ISD

Shutdown current

EN = GND

2.7

VUVLO

Under-voltage lockout threshold

VIN falling

Vhys

Under-voltage lockout hysteresis

V

mA

10

µA

2.5

2.7

V

120

140

160

mV

ENABLE AND REFERENCE CONTROL

VEN(r)

EN threshold voltage

EN rising input

0.9

1.08

1.30

V

VEN(f)

EN threshold voltage

EN falling input

0.74

0.92

1.125

V

VENh

EN threshold hysteresis

REN

EN pulldown resistor

Toff

Shutdown delay, SS discharge

VSYNh

SYN logic high voltage

VSYNl

SYN logic low voltage

0.16

400

EN high to low

950

V

1600

1.0

kΩ

ms

1.2

0.4

V

VOLTAGE AND CURRENT CONTROL

1.204

1.229

1.254

1.220

1.229

1.238

TA = 25°C

1.6

20

VFB = VREF + 200 mV, VCOMP = 1 V

42

µA

Comp pin source current

VFB = VREF – 200 mV, VCOMP = 1 V

42

µA

VCCLP

Comp pin Clamp Voltage

High Clamp, VFB = 1 V

Low Clamp, VFB = 1.5 V

3.1

0.75

V

VCTH

Comp pin threshold

Duty cycle = 0%

1.04

V

Gea

Error amplifier transconductance

Rea

Error amplifier output resistance

fea

Error amplifier crossover frequency

VREF

Voltage feedback regulation voltage

IFB

Voltage feedback input bias current

Isink

Comp pin sink current

Isource

TA = 25°C

240

360

440

V

nA

µS

10

MΩ

500

kHz

FREQUENCY

fSW

Frequency

Dmax

Maximum duty cycle

VFREQ

FREQ pin voltage

Tmin_on

Minimum on pulse width

RFREQ = 480 kΩ

75

94

RFREQ = 80 kΩ

460

577

740

RFREQ = 40 kΩ

920

1140

1480

89%

96%

VFB = 1.0 V, RFREQ = 80 kΩ

130

kHz

1.25

V

RFREQ = 80 kΩ

77

ns

60

70

POWER SWITCH

RDS(ON)

N-channel MOSFET on-resistance

VIN = 5 V

VIN = 3 V

ILN_NFET

N-channel leakage current

VDS = 25 V, TA = 25°C

110

120

mΩ

2.1

µA

7.75

A

OCP and SS

ILIM

N-Channel MOSFET current limit

D = Dmax

ISS

Soft-start bias current

VSS = 0 V

5.25

6.6

6

µA

THERMAL SHUTDOWN

Tshutdown

Thermal shutdown threshold

165

°C

Thysteresis

Thermal shutdown threshold

hysteresis

15

°C

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

5

�TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

www.ti.com

6.6 Typical Characteristics

VIN = 5 V, TA = 25°C (unless otherwise noted)

8

Current Limit Threshold (A)

Transconductance (µA/V)

400

380

360

340

320

7

6

5

4

3

2

300

−50

−25

0

25

50

75

Temperature (°C)

100

125

1

−50

150

Figure 1. Error Amplifier Transconductance vs Temperature

125

150

G002

VIN = 3 V

Resistance (mΩ)

Voltage Reference (V)

100

100

1.228

1.226

1.224

80

60

VIN = 12 V

40

VIN = 5 V

20

1.22

−50

−25

0

25

50

75

Temperature (°C)

100

125

0

−50

150

−25

0

G003

Figure 3. Feedback Voltage Reference vs Temperature

1600

1400

1400

1200

Frequency (kHz)

1000

800

600

400

25

50

75

Temperature (°C)

30

100

Resistance (kΩ)

500

125

150

G004

1000

800

600

RFREQ = 40 kΩ

RFREQ = 80 kΩ

RFREQ = 480 kΩ

400

200

200

100

Figure 4. RDS(ON) vs Temperature

1200

Frequency (kHz)

25

50

75

Temperature (°C)

120

1.222

0

−50

G005

Figure 5. Frequency vs FREQ Resistance

6

0

Figure 2. Switch Current Limit vs Temperature

1.23

0

−25

G001

Submit Documentation Feedback

−25

0

25

50

75

Temperature (°C)

100

125

150

G006

Figure 6. Frequency vs Temperature

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

�TPS55330

www.ti.com

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

Typical Characteristics (continued)

VIN = 5 V, TA = 25°C (unless otherwise noted)

400

700

350

600

300

500

Frequency (kHz)

Frequency (kHz)

RFREQ = 80 kΩ

250

200

150

100

400

Non-Foldback

Foldback

300

200

100

50

0

−50

0

0

5

10

15

20

25

30

Voltage on the VIN Pin (V)

35

−25

0

40

25

50

75

Temperature (°C)

100

125

150

G007

D006

TA = 25°C

Figure 7. Minimum Switching Frequency for Quick Recovery

from Frequency Foldback

Figure 8. Non-Foldback Frequency vs Foldback Frequency

3.5

2.7

2.66

Input Voltage (V)

COMP Voltage (V)

3

2.5

COMP Pin Clamp High

COMP Pin Clamp Low

2

1.5

2.62

UVLO Start

UVLO Stop

2.58

2.54

1

0.5

−50

−25

0

25

50

75

Temperature (°C)

100

125

2.5

−50

150

Figure 9. COMP Clamp Voltage vs Temperature

25

50

75

Temperature (°C)

100

125

150

G009

100

RFREQ = 80 kΩ

EN Voltage Rising

EN Voltage Falling

Maximum Duty Cycle (%)

1.2

Enable Voltage (V)

0

Figure 10. Input Voltage UVLO vs Temperature

1.3

1.1

1

0.9

0.8

0.7

−50

−25

G008

99

98

97

96

95

−25

0

25

50

75

Temperature (°C)

100

125

150

94

−50

G010

Figure 11. Enable Voltage vs Temperature

−25

0

25

50

75

Temperature (°C)

100

125

150

G011

Figure 12. Maximum Duty Cycle vs Temperature

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

7

�TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

www.ti.com

Typical Characteristics (continued)

VIN = 5 V, TA = 25°C (unless otherwise noted)

100

8

RFREQ = 80 kΩ

7

Shutdown Current (µA)

Minimum On Time (ns)

95

90

85

80

75

6

5

4

3

2

70

−50

−25

0

25

50

75

Temperature (°C)

100

125

1

−50

150

−25

0

25

50

75

Temperature (°C)

G012

Figure 13. Minimum On Time vs Temperature

100

125

150

G013

Figure 14. Shutdown Current vs Temperature

2.1

Supply Current (mA)

1.8

1.5

Switching

Non-Switching

1.2

0.9

0.6

0.3

−50

−25

0

25

50

75

Temperature (°C)

100

125

150

G014

Figure 15. Supply Current vs Temperature

8

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

�TPS55330

www.ti.com

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

7 Detailed Description

7.1 Overview

The TPS55330 device is a monolithic nonsynchronous switching regulator with an integrated 5-A, 24-V power

switch. The device can be configured in several standard switching-regulator topologies, including boost, SEPIC,

and isolated flyback. The device has a wide input voltage range to support applications with input voltage from

multicell batteries or regulated 3.3-V, 5-V, and 12-V power rails.

7.2 Functional Block Diagram

VIN

SW

FB

Error

Amp

EN

1.229V

Reference

COMP

PWM

Control

Ramp

Generator

Gate

Driver

Lossless

Current Sense

S

Oscillator

SS

FREQ

SYNC

AGND

PGND

7.3 Feature Description

7.3.1 Operation

If designed as a boost converter, the TPS55330 device regulates the output with current-mode pulse-widthmodulation (PWM) control. The PWM-control circuitry turns on the switch at the beginning of each oscillator clock

cycle. The input voltage is applied across the inductor and stores the energy as inductor current ramps up.

During this portion of the switching cycle, the load current is provided by the output capacitor. When the inductor

current reaches a threshold level set by the error amplifier output, the power switch turns off and the external

Schottky diode is forward biased to allow the inductor current to flow to the output. The inductor transfers stored

energy to replenish the output capacitor and supply the load current. This operation repeats every switching

cycle. The duty cycle of the converter is determined by the PWM-control comparator which compares the error

amplifier output and the current signal. The oscillator frequency is programmed by the external resistor or

synchronized to an external clock signal.

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

9

�TPS55330

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

www.ti.com

Feature Description (continued)

A ramp signal from the oscillator is added to the inductor current ramp to provide slope compensation. Slope

compensation is required to avoid subharmonic oscillation that is intrinsic to peak-current mode control at duty

cycles higher than 50%. If the inductor value is too small, the internal slope compensation may not be adequate

to maintain stability.

The PWM control feedback loop regulates the FB pin to a reference voltage through a transconductance error

amplifier. The output of the error amplifier is connected to the COMP pin. An external RC-compensation network

connected to the COMP pin is chosen for feedback loop stability and optimum transient response.

7.3.2 Switching Frequency

The switching frequency is set by a resistor (RFREQ) connected to the FREQ pin of the TPS55330. The

relationship between the timing resistance RFREQ and frequency is shown in the Figure 5. Do not leave this pin

open. A resistor must always be connected from the FREQ pin to ground for proper operation. The resistor value

required for a desired frequency can be calculated using Equation 1.

RFREQ(kΩ) = 57500 × ƒsw(kHz)–1.03

(1)

For the given resistor value, the corresponding frequency can be calculated by Equation 2.

ƒsw(kHz) = 41600 × RFREQ(kΩ)–0.97

(2)

The TPS55330 switching frequency can be synchronized to an external clock signal that is applied to the SYNC

pin. The required logic levels of the external clock are shown in the specification table. The recommended duty

cycle of the clock is in the range of 10% to 90%. A resistor must be connected from the FREQ pin to ground

when the converter is synchronized to the external clock and the external clock frequency must be within ±20%

of the corresponding frequency set by the resistor. For example, if the frequency programmed by the FREQ pin

resistor is 600kHz, the external clock signal should be in the range of 480kHz to 720kHz.

With a switching frequency below 280 kHz (typical) after the TPS55330 enters frequency foldback as described

in the section, if a load remains when the overcurrent condition is removed the output may not recover to the set

value. For the output to return to the set value the load must be removed completely or the TPS55330 power

cycled with the EN pin or VIN pin. Select a nominal switching frequency of 350 kHz for quicker recovery from

frequency foldback.

7.3.3 Overcurrent Protection and Frequency Foldback

The TPS55330 provides cycle-by-cycle over-current protection that turns off the power switch once the inductor

current reaches the over-current limit threshold. The PWM circuitry resets itself at the beginning of the next

switch cycle. During an over-current event, the output voltage begins to droop as a function of the load on the

output. When the FB voltage through the feedback resistors, drops lower than 0.9 V, the switching frequency is

automatically reduced to 1/4 of the normal value. Figure 8 shows the non-foldback frequency with an 80kΩ timing

resistor and the corresponding foldback frequency. The switching frequency does not return to normal until the

over-current condition is removed and the FB voltage increases above 0.9 V. The frequency foldback feature is

disabled during soft-start.

7.3.3.1 Minimum On-Time and Pulse Skipping

The TPS55330 PWM control system has a minimum PWM pulse width of 77ns (typical). This minimum on-time

determines the minimum duty cycle of the PWM, for any set switching frequency. When the voltage regulation

loop of the TPS55330 requires a minimum on-time pulse width less than 77ns, the IC enters pulse-skipping

mode. In this mode, the device will hold the power switch off for several switching cycles to prevent the output

voltage from rising above the desired regulated voltage. This operation typically occurs in light load conditions

when the PWM operates in discontinuous conduction mode. Pulse skipping increases the output ripple as shown

in Figure 22.

7.3.4 Voltage Reference and Setting Output Voltage

An internal voltage reference provides a precise 1.229 V voltage reference at the error amplifier non-inverting

input. To set the output voltage, select the FB pin resistor RSH and RSL according to Overcurrent Protection and

Frequency Foldback.

10

Submit Documentation Feedback

Copyright © 2013–2019, Texas Instruments Incorporated

Product Folder Links: TPS55330

�TPS55330

www.ti.com

SLVSBX8B – MAY 2013 – REVISED JANUARY 2019

Feature Description (continued)

æR

ö

VOUT = 1.229 V ´ ç SH + 1÷

è R SL

ø

(3)

7.3.5 Soft-Start

The TPS55330 has a built-in soft-start circuit which significantly reduces the start-up current spike and output

voltage overshoot. When the IC is enabled, an internal bias current source (6 µA typical) charges a capacitor

(CSS) on the SS pin. The voltage at the capacitor clamps the output of the internal error amplifier that determines

the peak current and duty cycle of PWM controller. Limiting the peak switch current during start-up with a slow

ramp on the SS pin will reduce in-rush current and output voltage overshoot. Once the capacitor reaches 1.8V,

the soft-start cycle is completed and the soft-start voltage no longer clamps the error amplifier output. When the

EN is pulled low for at least 1ms, the IC enters the shutdown mode and the SS capacitor is discharged through a

5kΩ resistor to prepare for the next soft-start sequence.

7.3.6 Slope Compensation

The TPS55330 has internal slope compensation to prevent subharmonic oscillations. The sensed current slope

of boost converter can be expressed as Equation 4:

V

Sn = IN ´ RSENSE

(4)

L

The slope compensation dv/dt can be calculated using Equation 5.

0.32 V RFREQ 0.5 mA

Se =

+

16 ´ (1 - D) ´ 6 pF

6 pF

(5)

In a converter with current mode control, in addition to the output voltage feedback loop, the inner current loop

including the inductor current sampling effect as well as the slope compensation on the small signal response

should be taken into account, which can be modeled as seen in Equation 6:

1

He(s) =

éæ

ù

S ö

s ´ êç 1 + e ÷ ´ (1 - D) - 0.5 ú

Sn ÷ø

êëçè

úû

s2

1+

+

2

fsw

p ´ fsw

(

)

where

•

•

•

RSENSE (15mΩ) is the equivalent current sense resistor

RFREQ is timing resistor used to set frequency

D is the duty cycle

(6)

NOTE

If Sn