TPS65400

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

TPS65400 4.5- to 18-V Input Flexible Power Management Unit With PMBus/I2C

Interface

1 Features

2 Applications

•

•

•

•

•

•

•

•

•

•

Efficiency up to 95% for each switching regulator

Switching regulator specifications:

– Input voltage range: 4.5 to 18 V

– VOUT range: 0.6 V-90%VIN

– SW1, SW2 IOUT: 4-A max

– SW3, SW4 IOUT: 2-A max

Prebias start-up algorithm minimizes voltage dip

during start-up

Internal undervoltage lockout (UVLO), overcurrent

protection (OCP), overvoltage protection (OVP),

and overtemperature protection (OTP)

AECQ-100 grade 1 option

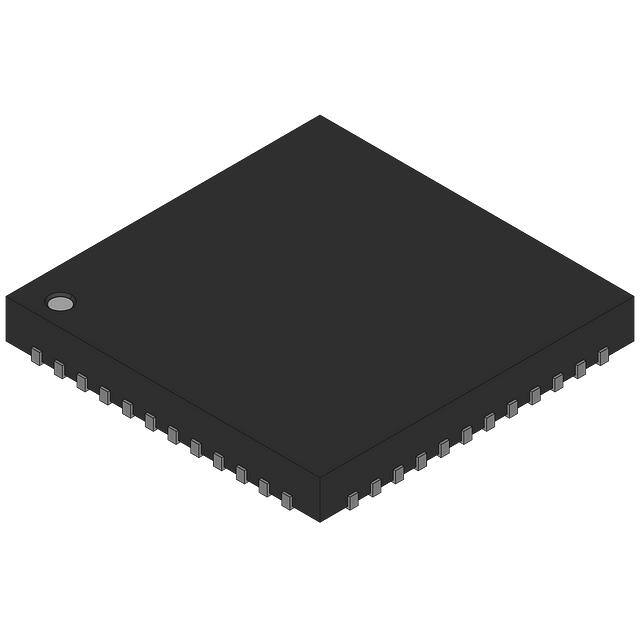

Thermally enhanced 7-mm × 7-mm 48-pin, 0.5-mm

pitch VQFN package

Pin accessible features:

– Adjustable VOUT with external feedback

resistors

– Sequencing control through precision enable

pins for each switcher

– Resistor adjustable PWM switching frequency

from 275 kHz to 2.2 MHz

– Clock sync input and clock output

– Soft-start delay through external capacitor

– Current sharing between SW1 and SW2 and

between SW3 and SW4 allows support of

higher current needs if required

PMBus runtime control and status

– Runtime voltage positioning through adjustment

of VREF

– Enable and disable of each switcher

– Fault and status monitoring

User-configurable PMBus/I2C options, saved in

EEPROM

– Power supply turn-on and turn-off sequencing

– Sequencing can be based on fixed time delays

or PGOOD dependence

– Initial voltage positioning through VREF

configuration

– PWM frequency adjustment for each switcher

– Individual PWM phase alignment for each

switcher to minimize ripple and capacitor size

– Adjustable current limit on each regulator

enables size and cost optimization of inductors

– Soft-start time

•

•

•

•

•

Small cellular base stations (BTS) (for example:

picocells and microcells); macro BTS (using

multiple PMUs)

Power over ethernet (PoE) powered

communications infrastructure equipment

Automotive infotainment and telematics

Powering DSP and MCUs

Industrial and factory automation

Systems requiring small form factor, highefficiency, high-ambient operating temperature,

and flexible power management

3 Description

The TPS65400 is an integrated PMU optimized for

applications requiring small form factor and high

power conversion efficiency, enabling small spaceconstrained equipment with high ambient operating

temperature without cooling. The device provides

high-power efficiency at a system level by enabling

a single stage conversion from an intermediate

distribution bus with an optimized combination of

regulators.

Device Information

(1)

PART NUMBER

PACKAGE(1)

BODY SIZE (NOM)

TPS65400

VQFN (48)

7.00 mm × 7.00 mm

For all available packages, see the orderable addendum at

the end of the data sheet.

Vin: 4.5 to 18 V

4A

4A

BUCK1

BUCK4

BUCK2

BUCK3

2A

2A

PMBus/I2C

Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Table of Contents

1 Features............................................................................1

2 Applications..................................................................... 1

3 Description.......................................................................1

4 Revision History.............................................................. 2

5 Description (continued).................................................. 3

6 Pin Configuration and Functions...................................3

7 Specifications.................................................................. 6

7.1 Absolute Maximum Ratings........................................ 6

7.2 ESD Ratings............................................................... 6

7.3 Recommended Operating Conditions.........................6

7.4 Thermal Information....................................................7

7.5 Electrical Characteristics.............................................7

7.6 System Characteristics............................................... 9

7.7 Operational Parameters............................................10

7.8 Package Dissipation Ratings.................................... 10

7.9 Typical Characteristics: System Efficiency................10

8 Detailed Description...................................................... 11

8.1 Overview................................................................... 11

8.2 Functional Block Diagrams....................................... 12

8.3 Feature Description...................................................13

8.4 Device Functional Modes..........................................28

8.5 Programming............................................................ 29

8.6 Register Maps...........................................................34

9 Application and Implementation.................................. 54

9.1 Application Information............................................. 54

9.2 Typical Applications.................................................. 55

10 Power Supply Recommendations..............................67

11 Layout........................................................................... 68

11.1 Layout Guidelines................................................... 68

11.2 Layout Example...................................................... 69

12 Device and Documentation Support..........................70

12.1 Documentation Support.......................................... 70

12.2 Receiving Notification of Documentation Updates..70

12.3 Glossary..................................................................70

12.4 Trademarks............................................................. 70

12.5 Electrostatic Discharge Caution..............................70

12.6 Glossary..................................................................70

13 Mechanical, Packaging, and Orderable

Information.................................................................... 70

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision D (July 2018) to Revision E (March 2022)

Page

• Updated the numbering format for tables, figures, and cross-references throughout the document. ................1

Changes from Revision C (May 2018) to Revision D (July 2018)

Page

• Added soldering and storage temperature ........................................................................................................ 6

• Added minimum value for TJ ..............................................................................................................................6

• Updated the default timing for tON_DELAY and tOFF_DELAY to 5 ms in the External Sequencing section.............14

2

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

5 Description (continued)

The TPS65400 implements a PMBus-I2C-compatible digital interface. It helps Core Chip optimize system

performance by run-time changing regulated voltage, power sequence, phase interleaving, operating frequency,

read back operating status, and so forth.

The TPS65400 consists of four high-current buck switching regulators (SW1, SW2, SW3, and SW4) with

integrated FETs. The switching power supplies are intended for powering high-current digital circuits such as the

processor, FPGA, ASIC, memory, and digital I/Os. SW1 and SW2 support 4 A each, and SW3 and SW4 support

2 A each. The switching frequency of each regulator is independently adjustable up to 2.2 MHz.

Current limit programmability on each switcher enables optimization of inductor ratings for a particular

application configuration not requiring the maximum current capability.

The TPS65400 can be powered from a single-input voltage rail between 4.5 and 18 V, making it suitable for

applications running off a 5- or 12-V intermediate power distribution bus.

Sequencing requirements can be met using the individual enable terminals or by programming the sequence

through the I2C bus into the on-board EEPROM. Output voltages can be set through external resistor networks

and VREF can be programmed from 0.6 V to 1.87 V in 10-mV steps. All control and status info can be accessed

through a PMBus-compatible I2C bus.

The TPS65400 provides a high level of flexibility for monitoring and control through the I2C bus while providing

the option of programmability through the use of external components and voltage levels for systems not using

I2C.

CB1

1

SW1

2

SW1

3

SW1

VFB1

COMP1

SS1/PG1

CLK_OUT

SCL

SDA

I2CALERT

RCLOCK_SYNC

RST_N

I2CADDR

SS4/PG4

47

46

45

44

43

42

41

40

39

38

37

ENSW1/ENSEQ

48

6 Pin Configuration and Functions

36

COMP4

35

VFB4

34

ENSW4

4

33

CB4

PVIN1

5

32

SW4

PGND(thermal pad)

A.

23

24

SS3/PG3

COMP3

CE

25

22

12

21

CB2

VIN

VFB3

AGND

26

20

11

VDDD

SW2

19

ENSW3

VDDA

CB3

27

18

28

10

17

9

SW2

VDDG

SW2

PGOOD

SW3

16

29

SS2/PG2

8

15

PGND2

14

PVIN3

VFB2

PVIN4

30

COMP2

31

7

13

6

ENSW2

PVIN2

PGND1

Thermal pad must be soldered to PCB as SW3 and SW4 power ground.

Figure 6-1. 48-Pin VQFN RGZ Package (Top View)

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

3

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Table 6-1. Pin Functions

PIN

NAME

CB1

DESCRIPTION

NO.

1

Bootstrap pin for the high-side MOSFET gate drive for SW1

2

SW1

3

Switch pin for SW1

4

PVIN1

5

Power input for the buck switching regulator SW1

PVIN2

6

Power input for SW2

PGND1

7

Power ground for buck converters

PGND2

8

Power ground for buck converters

SW2

10

CB2

12

Bootstrap pin for the SW2 high-side MOSFET gate drive

ENSW2

13

Enable input pin for SW2. Active high. A 2-µA internal pullup current is inside.

VFB2

14

Feedback input pin for SW2

COMP2

15

Compensation pin for external compensation network for SW2. Pulling this line high to VDDA configures the

SW1 controller to control both SW1 and SW2.

SS2/PG2

16

Soft start for SW2 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured

through I2C to display the PGOOD2 signal instead.

PGOOD

17

Default PGOOD signal is for all switchers. It can be changed according to (D2h) PIN_CONFIG_00. If all

switchers are disabled, PGOOD is low.

VDDG

18

Supply for gate drives. Bypass locally to PGND.

VDDA

19

Output of internal regulator for analog controls

VDDD

20

3.3-V output of internal regulator digital controls

AGND

21

Ground connection for analog controls

VIN

22

Analog VIN. Power input pin for the VDDD, VDDA, and VGATE subregulator power

CE

23

Chip enables. Internal pullup current will default to high if the pin is left floating. Connect to an open-drain

output to pull low to disable. Driving with a push-pull output is not recommended. When low, internal regulators

are shutdown to minimize power, and functions are disabled. Configuration is reloaded from EEPROM as part

of the power-up sequence when CE goes high.

SS3/PG3

24

Soft-start for SW3 (default). A capacitor is used to set the startup time. This pin can also be reconfigured

through I2C to display the PGOOD3 signal instead.

COMP3

25

Compensation pin for external compensation network for SW3

VFB3

26

Feedback input pin for SW3

ENSW3

27

Enable input pin for SW3. Active high. A 2-µA internal pullup current is inside.

CB3

28

Bootstrap pin for SW3 high-side MOSFET gate drive

SW3

29

Switch pin for SW3. The maximum rated output current is 2 A.

PVIN3

30

Power input for buck switching regulator SW3

PVIN4

31

Power input for SW4

SW4

32

Switch pin for SW4. The maximum rated output current is 2 A.

CB4

33

Bootstrap pin for SW4 high-side MOSFET gate drive

ENSW4

34

Enable input pin for SW4. Active high. A 2-µA internal pullup current is inside.

VFB4

35

Feedback input pin for SW4

COMP4

36

Compensation pin for external compensation network for SW4. Pulling this line high to VDDA configures the

SW3 controller to control both SW3 and SW4.

SS4/PG4

37

Soft start for SW4 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured

through I2C to display the PGOOD4 signal instead.

I2CADDR

38

Select I2C address with a resistor to AGND.

9

Switch pin for SW2

11

4

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Table 6-1. Pin Functions (continued)

PIN

NAME

DESCRIPTION

NO.

RST_N

39

Reset of digital logic. When low, all switchers are disabled. Configuration is reloaded from EEPROM when

RESET_N is deasserted.

RCLOCK_SYNC

40

Resistor for setting primary clock frequency from 275 kHz to 2.2 MHz or for clock sync

I2CALERT

41

Open-drain output that is pulled low for 200 µs when a timeout condition is detected by the I2C watchdog on

either SDA or SCL.

SDA

42

Data input/output pin for I2C bus

SCL

43

Clock input pin for I2C bus

CLK_OUT

44

Clock output signal. Open-collector output, requires pull up

SS1/PG1

45

Soft start for SW1 (default). A capacitor is used to set the start-up time. This pin can also be reconfigured

through I2C to display the PGOOD1 signal instead.

COMP1

46

Compensation pin for external compensation network for SW1

VFB1

47

Feedback input pin for SW1

ENSW1/ENSEQ

48

Enable input pin for SW1. Active high. A 2-µA internal pullup current is inside.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

5

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1)

MIN

MAX

UNIT

PVIN1, PVIN2, PVIN3, PVIN4, VIN

–0.3

20.0

V

CB1, CB2, CB3, CB4 referenced to SWx

–0.3

7.5

V

CLK_OUT, VFB1, VFB2, VFB3, VFB4, RST_N, I2CALERT, CLK_OUT,

I2CADDR, RCLOCK_SYNC

–0.3

VDDD or 3.6

V

SW1, SW2, SW3, SW4

–1.0

20.0

V

VDDA, VDDG

–0.3

7.5

V

PGOOD, SS1/PG1, SS2/PG2, SS3/PG3, SS4/PG4, COMP1, COMP2,

COMP3, COMP4, CE

–0.3

VDDA or 7.5

V

VDDD

–0.3

3.6

V

SCL, SDA, ENSW1, ENSW2, ENSW3, ENSW4

–0.3

4.0

V

Junction temperature, TJ-max

150

°C

Maximum lead temperature (soldering, 10 s)

260

°C

150

°C

Input voltage

Storage temperature, Tstg

(1)

–55

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under

Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device

reliability.

7.2 ESD Ratings

VALUE

V(ESD)

(1)

(2)

Electrostatic

discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all

pins(1)

UNIT

±2000

Charged device model (CDM), per JEDEC specification JESD22-C101, all pins(2)

V

±750

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

Input voltage

MIN

MAX

UNIT

PVIN1, PVIN2, PVIN3, PVIN4, VIN

–0.3

18.0

V

CB1, CB2, CB3, CB4 referenced to SWx

–0.3

7.0

V

ENSW1, ENSW2, ENSW3, ENSW4, SCL, SDA, CLK_OUT, RST_N,

SCL, SDA, I2CALERT, CLK_OUT, I2CADDR, RCLOCK_SYNC, VDDD

–0.3

3.3

V

SW1, SW2, SW3, SW4

–1.0

18.0

V

VDDA, VDDG

–0.3

7.0

V

PGOOD, SS1/PG1, SS2/PG2, SS3/PG3, SS4/PG4, COMP1, COMP2,

COMP3, COMP4, CE

–0.3

7.0

V

0.6

1.87

V

VFB1, VFB2, VFB3, VFB4

Load current

IOUT1, IOUT2

0

4

A

Load current

IOUT3, IOUT4

0

2

A

–40

125

°C

Junction temperature

6

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

7.4 Thermal Information

TPS65400

THERMAL

METRIC(1)

UNIT

RGZ (VQFN)

48 PINS

RθJA

Junction-to-ambient thermal resistance

29.8

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

14.9

°C/W

RθJB

Junction-to-board thermal resistance

6.3

°C/W

ψJT

Junction-to-top characterization parameter

0.2

°C/W

ψJB

Junction-to-board characterization parameter

6.3

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

0.8

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

7.5 Electrical Characteristics

VIN = 12 V, Frequency = 500 kHz, TJ = –40°C to 125°C, typical values are at TJ = 25°C, unless otherwise indicated

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SWITCHER 1 AND SWITCHER 2

Ilimit1, Ilimit2

SW1, SW2 high-side current limit

adjustment range

Ilimit-accuracy

Accuracy to nominal current limit value

Rdson HS

SW1, SW2 HS Rds(on)

66

mΩ

Rdson LS

SW1, SW2 LS Rds(on)

42

mΩ

2

Ilimit = 4 A, 5 A, 6 A

6

–25%

A

25%

SWITCHER 3 AND SWITCHER 4

Ilimit3, Ilimit4

SW3 and SW4 current limit

Ilimit accuracy

Accuracy to nominal current limit value

Rdson HS

SW3 and SW4 HS Rds(on)

Rdson LS

SW3/4 LS Rds(on)

Ilimit = 1 A, 2 A, 3 A

0.5

3

–25%

25%

A

120

mΩ

90

mΩ

FEEDBACK AND ERROR AMPLIFIERS FOR SW1 – SW4

VFB

Accuracy

VREF = 1 V

–1%

VREFn

Error amplifier reference voltage

Default value

VREF_STEP

I2C programmable VREF step size

Gm

Error amplifier transconductance

Isink

Sink

12

µA

Isource

Source

12

µA

95

1%

800

mV

10

mV

133

165

µS

PWM SWITCHING CHARACTERISTICS

Phase_err12(1) Phase error between SW1 and SW2

Fsw = 1.1 MHz

5⁰

Phase_err34(1) Phase error between SW3 and SW4

Fsw = 1.1 MHz

5⁰

Fsw

Resistor-configurable PWM switching

configuration

Fsw-accuracy

PWM switching frequency accuracy

Vrclock_sync

Voltage reference for RCLOCK_SYNC

0.8

tON_min

Lower duty cycle limit

80

tOFF_min

Minimum off-time limit (constrains the

maximum achievable duty cycle)

ROSC = 165 kΩ

(Fsw = 1.1 MHz)

275

2200

–10%

10%

kHz

V

150

150

ns

ns

CLOCK SYNC

V_HSYNC

High signal threshold

V_LSYNC

Low signal threshold

2.6

V

1

V

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

7

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

VIN = 12 V, Frequency = 500 kHz, TJ = –40°C to 125°C, typical values are at TJ = 25°C, unless otherwise indicated

PARAMETER

TEST CONDITIONS

ICLKOUT

Max current sink/source for CLK_OUT

tmin_ SYNC

Minimum detectable time for sync pulse

FSYNC

Frequency synchronization range

TSYNC_DELAY

Delay between input pulse to

RCLOCK_SYNC and rising edge of

CLK_OUT and PWM output

MIN

TYP

MAX

2

275

UNIT

mA

150

ns

2200

kHz

20

ns

20

ms

TIMING CHARACTERISTICS

Delay for restart during repeated OCP

condition

trestart

INTERNAL REGULATORS AND UVLO

VDDA

Internal subregulator output

VDDD

Output of internal subregulator

Vin > 6.6 V

6.1

4.5 V < Vin 6.6 V

V

Vin – 0.1

3.2

Vin > 6.6 V

VDDG

Output of internal regulator for gate

drivers

IVIN

Quiescent non-switching, no load current

CE high, VFB >> VREF, (no

switching)

ISD

Quiescent shutdown current

CE low

VIN_UVLO

Input voltage UVLO

Rising

VIN_UVLO

Input voltage UVLO

Falling

V

6.1

4.5 V < Vin 6.6 V

V

Vin – 0.1

8

3.4

mA

12

27

µA

4.25

4.48

V

3.75

V

PGOOD, ENSWx, RST_N, SSx, PG

R_LPGOOD

Resistance of PGOOD outputs when low

V_OLPGOOD

Logic output low voltage

500

ISS

Soft-start current

4.1

VEN

Enable logic high threshold (for ENSW1,

VEN rising

ENSW2, ENSW3, ENSW4)

VEN_L

Enable logic low threshold (for ENSW1,

EN_L ENSW2, ENSW3, ENSW4)

VEN_HYS

Enable hysteresis (for ENSW1, ENSW2,

VEN falling

ENSW3, ENSW4)

IEN

ENSWx pin pullup current

VEN = 0

ICE

CE pin pullup current

VCE = 0

VIH_CE

Logic input high for CE

VIL_CE

Logic input low CE

VIH_RSTN

Logic input high RST_N

VIL_RSTN

Logic input low RST_N

I_OL = 100 µA

VEN falling

Ω

0.1

V

5.6

7.3

µA

1.12

1.20

1.28

V

0.97

1.07

V

130

mV

2

µA

2

µA

1.3

V

0.4

1.3

V

V

0.4

V

0.8

V

I2C MODULE (SDA, SCL, I2CALERT, I2CADDR)

V_ILI2C

Logic input low SCL, SDA

V_IHI2C

Logic input high for SCL, SDA

R_LI2C

ON resistance of I2C pins (SDA, SCL,

I2CALERT) to GND

I2CALERT = 1

V_OLI2C

Logic output low voltage for SCL, SDA,

I2CALERT pins

I_OL = 350 µA

ILEAK

Input leakage current

SDA, SCL = 3.3 V

II2CADDR

Source current of I2CADDR pin

VDDD = 3.3 V, VIN > 4.5 V

tTIMEOUT

Timeout detection on SDA or SCL low

2.1

tTIMEOUT_PULSE Duration of timeout pulse on I2CALERT

8

Submit Document Feedback

V

85

Ω

0.1

V

1

µA

20

µA

30

ms

200

µs

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

VIN = 12 V, Frequency = 500 kHz, TJ = –40°C to 125°C, typical values are at TJ = 25°C, unless otherwise indicated

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

FAULTS

TTSD (2)

Thermal shutdown threshold

160

⁰C

TTSD_restart (2)

Thermal shutdown hysteresis

20

⁰C

VFB_OVP

tOVPSDOWN

VFB UVP

tUVPSDOWN

(1)

(2)

OVP threshold rising (fault latched,

PGOOD asserted)

0.6V < VREF < 1.87 V

111

% of VREF

OVP threshold falling (fault cleared,

PGOOD deasserted)

0.6 V < VREF < 1.87 V

104

% of VREF

Time after OVP before protection

activation and PGOOD fall

55

95

µs

Undervoltage threshold (PGOOD

deasserted)

0.6 V < VREF < 1.87 V

92

% of VREF

Undervoltage threshold (PGOOD

asserted)

0.6 V < VREF < 1.87 V

83

% of VREF

Time after UVP before PGOOD fall

55

95

µs

Specified by design

Specified by lab validation

7.6 System Characteristics

The following specification table entries are specified by the design (component values provided in the typical application

circuit are used). These parameters are not specified by production testing. minimum and max values apply over the full

operating ambient temperature range (–40°C ≤ TJ ≤ 125°C), over the VIN range = 5 to 12 V, and IOUT range unless otherwise

specified. L = 3.3 µH, DCR = 10.4 mΩ, VOUT = 1.2 V, 1% FB resistor.

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VLINEREG

Line regulation

VLOADREG

Load regulation

tr

VOUT step duration (tr)

For 50-mV step

ts

VOUT step settling time (ts)

For 50-mV step

30

µs

VOVUV

VOUT step overshoot/undershoot

For 50-mV step

6

mV

Efficiency (SW1 and SW2)

Efficiency (SW3 and SW4)

%/A

30

µs

VIN = 12 V, VO = 1.2 V, IOUT = 4 A,

ƒsw = 500 kHz

76%

VIN = 5 V, VO = 1.2 V, IOUT = 2 A,

ƒsw= 500 kHz

77%

VIN = 12 V, VO = 1.2 V, IOUT = 2 A,

ƒsw= 500 kHz

74%

IPKmatch

Peak current ((2)) sharing accuracy

(SW1 and SW2, SW3 and SW4)

tacc

Timing accuracy for delays and

restarts

treset_delay

Time after RSTn or CE is released

for power sequence to begin

Default value

Minimum delay after reset is

released for power sequence to

begin

treset_delay set to 0 ms

(1)

(2)

0.1

77%

IOUTmatch

0

%/V

VIN = 5 V, VO = 1.2 V, IOUT = 4 A,

ƒsw = 500 kHz

Average ((1)) current sharing

accuracy (SW1 and SW2, SW3 and Iload = IOUTmax

SW4)

treset_delay_max

0.1

20%

Iload = IOUTmax

20%

–10%

10%

1

ms

1.1

ms

Average current sharing accuracy is highly dependent on the matching of the inductor and capacitor.

Peak current sharing accuracy refers to the max inductor current in each phase.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

9

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

7.7 Operational Parameters

Values recommended that ensure proper system behavior

PARAMETER

MIN

TYP

MAX

UNIT

CA

Stabilization capacitor to be connected to VDDA

4.7

µF

CD

Stabilization capacitor to be connected to VDDD

3.3

µF

CG

Stabilization capacitor to be connected to VDDG

Vin1, Vin2, Vin3, Vin4

SW1 to SW4 input voltage

4.5

18

V

Vout1, Vout2, Vout3, Vout4

SW1 to SW4 output voltage

0.6

90% of

VIN

V

10

µF

7.8 Package Dissipation Ratings

(1)

PACKAGE

RθJA (°C/W)(1)

TA = 25°C

TA = 55°C

TA = 85°C

RGZ

29.8

4.5 W

3.14 W

1.77 W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report, SPRA953.

100%

100%

90%

90%

80%

80%

70%

70%

60%

60%

Efficiency

Efficiency

7.9 Typical Characteristics: System Efficiency

50%

40%

VIN = 12 V; VOUT = 1V8

VIN = 12 V; VOUT = 1V5

VIN = 12 V; VOUT = 1V2

VIN = 12 V; VOUT = 1V

20%

10%

0

0.5

1

1.5

2

2.5

3

3.5

IOUT

VIN = 5 V; VOUT = 1V8

VIN = 5 V; VOUT = 1V5

VIN = 5 V; VOUT = 1V2

VIN = 5 V; VOUT = 1V

20%

10%

0

0

0

4

0.5

1

1.5

D001

Figure 7-1. Buck1 and Buck2 Power Efficiency, VIN

= 12 V

90%

80%

80%

70%

70%

60%

60%

Efficiency

100%

90%

40%

30%

2.5

3

3.5

4

D002

Figure 7-2. Buck1 and Buck2 Power Efficiency, VIN

=5V

100%

50%

2

IOUT

With 500 kHz and XAL6060-472 4.7-µH, 13.2-mΩ inductor

With 500 kHz and XAL6060-472 4.7-µH, 13.2-mΩ inductor

Efficiency

40%

30%

30%

50%

40%

30%

VIN = 12 V; VOUT = 1V8

VIN = 12 V; VOUT = 1V5

VIN = 12 V; VOUT = 1V2

VIN = 12 V; VOUT = 1V

20%

10%

VIN = 5 V; VOUT = 1V8

VIN = 5 V; VOUT = 1V5

VIN = 5 V; VOUT = 1V2

VIN = 5 V; VOUT = 1V

20%

10%

0

0

0

0.25

0.5

0.75

1

1.25

1.5

1.75

IOUT

2

0

0.25

D004

With 500 kHz FSW and 4.7-µH, 34-mΩ inductor

Figure 7-3. Buck3 and Buck4 Power Efficiency, VIN

= 12 V

10

50%

0.5

0.75

1

IOUT

1.25

1.5

1.75

2

D001

With 500 kHz FSW and 4.7-µH, 34-mΩ inductor

Figure 7-4. Buck3 and Buck4 Power Efficiency, VIN

=5V

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8 Detailed Description

8.1 Overview

The TPS65400 is an integrated PMU optimized for applications that require small form factor and high-power

conversion efficiency enabling small space-constrained equipment with high-ambient operating temperature

without cooling. It provides high-power efficiency at a system level by enabling a single-stage conversion from an

intermediate distribution bus with an optimized combination of regulators.

The TPS65400 consists of four high-current buck-switching regulators (SW1, SW2, SW3, and SW4) with

integrated FETs. The switching power supplies are intended for powering high-current digital circuits such as

the processor, FPGA, ASIC, memory, and digital I/Os. SW1 and SW2 support 4 A each, and SW3 and SW4

support 2 A each. Each regulator’s switching frequency is independently adjustable up to 2.2 MHz.

Current limit programmability on each switcher enables optimization of inductor ratings for a particular

application configuration not requiring the maximum current capability.

The TPS65400 can be powered from a single-input voltage rail between 4.5 and 18 V, making it suitable for

applications running off a 5- or 12-V intermediate power distribution bus.

Sequencing requirements can be met using the individual enable pins or by programming the sequence through

the I2C bus into the onboard EEPROM. Output voltages can be set through external resistor networks and VREF

can be programmed from 0.6 to 1.87 V in 10-mV steps. All control and status info can be accessed through a

PMBus-compatible I2C bus.

The TPS65400 provides a high level of flexibility for monitoring and control through the I2C bus while providing

the option of programmability through the use of external components and voltage levels for systems not using

I2C.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

11

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8.2 Functional Block Diagrams

COMP2

COMP1

PVIN1

SS DAC VREF DAC

SDA

SCL

I2C

I2CADDR

EEPROM

and

Charge Pump

PWM Controller

CB1

Gate Driver

SW1

I2CALERT

RCLOCK_SYNC

CLOCK

(Adj Fsw and )

OVP

UVP

OCP

ISENSE

VFB1

CLK_OUT

PVIN2

ENSW1

ENSW2

ENSW3

ENSW4

PGND1

Enable

and

PGOOD

Sequencing

Controller

SS DAC VREF DAC

PWM Controller

CB2

Gate Driver

SW2

PGOOD

OVP

UVP

SS1/PG1

SS2/PG2

SS3/PG3

Soft-Start

or

PGOOD#

OCP

ISENSE

PGND2

VFB2

TPS65400

SS4/PG4

PVIN3

CB3

SS DAC VREF DAC

RST_N

PWM Controller

CE

VIN

OVP

UVP

VDDD

VDDA

VDDG

Internal

Sub-Reg

and

Bias

AGND

Gate Driver

OCP

ISENSE

PWM Controller

OVP

UVP

COMP3

PGND (Thermal Pad)

VFB3

PVIN4

CB4

SS DAC VREF DAC

VREF

UVLO

OTP

SW3

Gate Driver

OCP

ISENSE

SW4

PGND (Thermal Pad)

VFB4

COMP4

Figure 8-1. TPS65400 Functional Block Diagram

12

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

INPUT+

VDDG

VIN

VDDA

VDDD

VDDA

Regulator

RCLOCK_SYNC

VDDG

Regulator

0

PVIN1

Oscillator

CB1

VDDD

Regulator

UVLO

VREF1

Generator

VREF1

SS1

OUTPUT+

UVLO

COMP

Precharge

OVP1

SW1

Logic

GM1

FB1

0.5V

COMP1

OVP1/UVP1

Detector

Slope

Comp.1

OCP1

High Side

Current

Sense

Zero Cross

Detect

High Side

Current

Limit

Low Side

Current

Limit

OCP1

Control

AGND

A.

UVP1

PGND1

Soft-Start

Control 1

SS1/PG1

SS1/PG1

Function

OVP1

All other switchers follow the same pattern

Figure 8-2. Simplified Control Block Diagram for Switcher1

8.3 Feature Description

8.3.1 Startup Timing and Power Sequencing

8.3.1.1 Startup Timing

Figure 8-3 shows the startup timing of the TPS65400. Upon power-up or the rising edge of CE, the internal

power rails VDDA, VDDG, and VDDD startup during the time labeled tstart. Following tstart, a delay of t1 follows

(which is defined by the user through the timing of RST_N). During time tstart and t1, the COMP terminal is

internally discharged through a 2-kΩ resistor. At the rising edge of RST_N, the TPS65400 begins two actions:

1. The TPS65400 begins its precharge of the COMP terminal (indicated by tprecharge). The length of tprecharge

needed to precharge the COMP terminal depends on the time constant of the R and C components. The

internal precharge voltage source remains on even during normal operation, preventing the COMP terminal

from falling below 0.6 V except during faults (OVP, OCP, and so forth).

2. The TPS65400 begins its configuration sequence (indicated by tconfig), and loads parameters from the

EEPROM. Parameters to be set include Vout, switching frequency, soft-start timing, and current limit.

After tconfig is complete, treset_delay begins. The length of treset_delay is user-configurable through PMBus register

DCh. After treset_delay is complete, the TPS65400 begins its startup sequence. The startup sequence is

EEPROM-configurable, so any of the four switchers could be the first to startup with a configurable delay. In

this particular example, SW1 is configured to startup first after a delay of tSW1_TON_DELAY, which is configurable

through PMBus register (DDh) TON_TOFF_DELAY.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

13

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

VIN

CE

VDDA

VDDG

VDDD

tstart

t1

RST_N

tconfig

treset_delay

COMP

ENSW1

VOUT1

tprecharge

t2

tSW1_TON_DELAY

t

A.

PGOOD1 and ENSW2 are tied together externally, and tON_DELAY1 and tON_DELAY2 are configured through PMBus.

Figure 8-3. Timing Showing Startup from CE

To summarize, the length of time from rising edge of CE to soft-start of the first switcher in the sequence is:

tCE_to_SS = tstart + t1 + tconfig + treset_delay + t2 + tSW1_ON_DELAY

(1)

The delays, treset_delay and tSW1_ON_DELAY, are both configurable through PMBus. The delay, tconfig, is typically 1.1

ms. The delays, t1 and t2, are determined by the user-defined timing of RST_N and ENSW1. They can both be

set to 0 by pulling RST_N high before the end of tstart and ENSW1 high before the end of treset_delay. One simple

way to do this would be to tie both signals to VDDD.

8.3.1.2 External Sequencing

To use external sequencing, either connect all the enable pins (ENSW1, ENSW2, ENSW3, and ENSW4) to an

external sequencing controller, or connect them to PGOOD outputs as shown in Figure 8-4. By default, tON_DELAY

and tOFF_DELAY are both set to 5 ms. This allows the user complete flexibility of sequencing order and timing with

the ENSWx pins without modifying any of the default settings in the TPS65400.

14

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

ENSW1

ENSW2

ENSW3

ENSW4

VOUT1

1

2

VOUT2

3

VOUT3

4

VOUT4

PGOOD1

PGOOD2

PGOOD3

PGOOD4

PGOOD

t

1. tSS1

A.

2. tSS2

3. tSS3

4. tSS4

Default behavior (external sequencing)

Figure 8-4. Example of Sequencing Where Timing is Controlled by an External Sequencer With ENSWx

Pins

8.3.1.3 Internal Sequencing

The default settings for SEQUENCE_ORDER (see (D5h SEQUENCE_ORDER)) effectively disable sequencing

by setting all switchers to start at the same time. Therefore, to use internal sequencing, the default values for

SEQUENCE_ORDER must be changed to the desired sequence. In addition, the user can configure the start or

stop sequence to have a dependence on the PGOOD output of the previous switcher, or to wait for a set delay.

If configured to have a dependence on PGOOD, the soft-start for the next switcher begins after PGOOD of the

previous goes high and the wait time determined by tON_DELAY is complete. If configured to wait for a set delay,

the wait time determined by tON_DELAY begins immediately upon the enabling of the previous switcher.

In addition, each supply can be disabled such that it is bypassed in the power-up sequence. For example, if the

sequence is SW1-SW2-SW3-SW4, and SW2 is disabled, then SW3 will be powered up after SW1. The initial

configuration of the TPS65400 (for first-time power-up) needs to be done using one of the methods described in

Section 8.3.14.

8.3.2 UVLO and Precision Enables

The TPS65400 implements a UVLO function that prevents startup when the voltage at VIN (terminal 22) is below

4 V. In most applications, VIN and all of the power rails (PVIN1, PVIN2, PVIN3, and PVIN4) are tied to the same

source and this single UVLO function is sufficient. However, in some applications, the power rails may be tied

to different input voltages, and there is the possibility that the TPS65400 may attempt to startup a switcher even

when its associated PVINx rail has not reached a high-enough voltage. In these cases, the precision enable

threshold on each ENSWx can be used to precisely set the startup threshold for each individual switcher with a

simple resistor divider to PVINx.

In cases where a single UVLO threshold is needed for all four switchers, but at a different level than 4 V, the

TPS65400 can be configured for single-terminal enable (PMBus register D2h, bits 0:1 = 10) where the ENSW1/

ENSEQ terminal is used as a sequence enable terminal. Then, a resistor divider to the appropriate PVINx rail

can be used to set a precise UVLO threshold that applies to all four switchers.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

15

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8.3.3 Soft-Start and Prebiased Startup

The TPS65400 implements a soft-start function that minimizes discharge of the output when starting up in

a prebiased condition. Soft-start time, tSS, is set by tON_TRANSITION_RATE (digital soft-start) or by a capacitor

connected to the corresponding SSx pin (analog soft-start). In this setup, the SSx pin sources a 5-µA current

charging the capacitor, and the voltage at the SSx pin limits the reference voltage at the input of the error

amplifier.

At the beginning of the soft-start, the soft-start input to the error amplifier is set to 0. The SSx input is raised

gradually and reaches its target value during the time tss. If VFB > VSS, then no switching occurs. After the

Soft-Start signal crosses VFB, the switching begins. The first switching pulse is on the low-side FET, which

charges the high-side bootstrap capacitor. The unit runs in discontinuous conduction mode (DCM) with the

zero-cross detector enabled on the low side (diode emulation). The high-side FET is pulsed according to the

error amplifier output on the COMP pin. If the IC is configured for continuous conduction mode (CCM) operation

(default), the low-side FET pulses gradually transition to normal CCM operation; at each successive switching

cycle, the low-side gate pulse is gradually ramped until full synchronous switching occurs. At this point, the

switcher enters normal CCM operation.

VREF

FB

SS

tss

HS_GATE

LS_GATE

Initial bootstrap capacitor

charge pulse

Pulse extension into regular CCM operation

Figure 8-5. Soft-Start Under Prebiased Condition and CCM Mode Programmed

16

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

VREF

FB

SS

HS_GATE

LS_GATE

Initial Bootstrap capacitor

charge pulse

tss

Figure 8-6. Soft-Start Under Prebiased Condition and DCM Mode Programmed

8.3.3.1 Analog Soft-Start (Default) and Digital Soft-Start

The TPS65400 has the ability to use an analog-based soft-start ramp based on external capacitors (one input for

each switcher) or to use internal signals based on digital logics and DACs to perform the soft-start function.

When using external soft-start configuration (default configuration), the SSx pins are connected to the soft-start

input of the error amplifier.

When using the internal digital soft-start signal, the soft-start input to the error amplifier increases step-by-step at

a rate set according to the value set in TON_RAMP_RATE (see (DEh) TON_TRANSITION_RATE).

VREF

tss_step

¨9ss_step

Soft-Start

Done

Figure 8-7. Internal Soft-Start Input to Error Amplifier When Digital Soft-Start is Selected

ΔVSS_step is 10 mV. Tss_step depends

TON_TRANSITION_RATE for more details.

on

the

soft-start

time

option

selected.

See

(DEh)

8.3.3.2 Soft-Start Capacitor Selection

When using external soft-start capacitor to set the soft-start time, use Equation 2.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

17

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

t ss

Css

u Vref

Iss

(2)

Css is the value of the capacitor connected between the SSx pin and AGND. VREF is the value of the reference

voltage (default is 0.8 V). ISS is the current sourced by the SS1/PG1 pin during soft-start.

8.3.4 PWM Switching Frequency Selection

The master clock frequency, FOSC, can be set by external resistor on the RCLOCK_SYNC terminal, or by

synchronizing with an external clock. To set using an external resistor, use this formula.

FSW (kHz) = 138664 ROSC (kΩ)–0.948

(3)

2500

Frequency (kHz)

2000

1500

1000

500

0

0

80

160

240

320 400

ROSC (k:)

480

560

640

720

D003

Figure 8-8. Frequency vs Rosc

To sync to an external source, an AC-coupled signal should be applied to the terminal. A fixed resistor should

still be connected to set a minimum frequency. The frequency of the input signal to synchronize with should

always be higher than the minimum frequency. If the internal PLL cannot synchronize, the switchers will fall back

to the minimum frequency set by the resistor. The CLK_OUT terminal outputs the master clock FOSC.

The PWM frequency of each switcher is determined by this master clock frequency and an I2C-programmable

choice of 4 divider ratios (1, 2, 4, or 8) by setting CLK_DIV (see (D7h) FREQUENCY_PHASE).

18

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

CLK_OUT

SW1

CLK_DIV

To clock input

SW1

DELAY_SELECT

VFreq_ref

ROSC

OSCILLATOR

4 × Master CLK

/4

/1, 2, 4, 8

4

Delay

SW1 FREQ

RCLOCK_SYNC

Frequency

Modulator

SW2

CLK_DIV

SW2

DELAY_SELECT

Delay

SW3

CLK_DIV

SW3

DELAY_SELECT

Delay

SW4

CLK_DIV

SW3 FREQ

SW4

DELAY_SELECT

Delay

A.

SW2 FREQ

SW4 FREQ

The frequency modulator is used for external clock synchronization.

Figure 8-9. Diagram of PWM Clock Generation

The intent of the individual divider ratios is to allow users to set the frequency of each switcher independently.

For example, with a master clock FOSC of 1.1 MHz, SW1 and SW2 have a divider ratio of 4 for a 275-kHz PWM,

and SW3 and SW4 have a divider ratio of 1 for a PWM frequency of 1.1 MHz. Select the divider ratio so that the

PWM frequency stays within the range of 275 kHz to 2.2 MHz for whichever master clock frequency is set.

In addition to selecting the frequency, each switcher can have its PWM frequency delayed. This enables the

designer to minimize ripple current by properly selecting the delays so that the switching frequencies are out

of phase. The default switching frequency is at CLK_DIV = FOSC / 1 with PHASE_DELAY for SW1 at 0°, SW2

at 180°, SW3 at 90°, and SW4 at 270°. More information on frequency selection and delay is given in (D7h)

FREQUENCY_PHASE.

8.3.5 Clock Synchronization

The RCLOCK_SYNC terminal can be used to synchronize the master clock switching frequency, FOSC, with an

external clock source or another TPS65400. The external clock signal (which can come from another TPS65400

CLK_OUT terminal) should be AC coupled to the RCLOCK_SYNC terminal as shown in Figure 8-10. Choose the

ROSC value so that the fixed frequency is nominally 30% lower than the external synchronizing clock frequency.

An internal protection diode clamps the low level of the synchronizing signal to approximately –0.5 V. The

internal clock synchronizes to the rising edge of the external clock.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

19

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

CCLK

To RCLOCK_SYNC

ROSC

AGND

Figure 8-10. AC-Coupled Clock Synchronization

TI recommends to choose an AC-coupling capacitance in the range of 50 to 100 pF. Exceeding the

recommended capacitance may inject excessive energy through the internal clamping diode structure present

on the RCLOCK_SYNC terminal. The typical trip level of the synchronization terminal is 1.5 V. To ensure proper

synchronization and to avoid damaging the IC, the peak-to-peak value (amplitude) should be between 2.5 V and

VDDA. The minimum duration of this pulse must be greater than 200 ns, and its maximum duration must be 200

ns less than the period of the switching cycle.

The external clock synchronization process begins after the TPS65400 is enabled and an external clock signal

is detected. The frequency modulator adjusts the oscillator frequency to match the frequency of the pulses into

the RCLOCK_SYNC terminal. It generally takes 50 cycles before the PWM frequency locks. If the external clock

signal is removed after frequency synchronization, the master clock FOSC drifts to the frequency selected by

ROSC.

8.3.6 Phase Interleaving

The TPS65400 offers the ability to output rails of higher currents by connecting SW1 and SW2 in parallel, or by

connecting SW3 and SW4 in parallel. To configure this option, the COMP2 or COMP4 terminal must be tied to

VDDA through a 1-kΩ resistor.

Upon the initialization sequence after a reset, the TPS65400 attempts to discharge the COMP terminal through

a 2-kΩ internal resistor. When it detects that the COMP terminal is pulled high, it configures itself to operate in

current sharing mode. If SW2 is set to current sharing mode, its PWM output is controlled by the error amplifier

and COMP1 terminal of SW1 and set to the same frequency as SW1. Likewise, if SW4 is set to current sharing

mode, its PWM output is controlled by the error amplifier and COMP3 terminal of SW3 and set to the same

frequency as SW3. This means that the frequency settings for SW2 and SW4 in the EEPROM are ignored in that

mode of operation.

When current sharing mode is detected on a particular pair, the output slave’s I2C access is invalid and the

output slave’s default settings follow that of its master (see (00h) PAGE). The only exception is that the slave

switcher PWM is a fixed 180° phase-shift from its master.

Table 8-1. Programmable Options When Current Sharing Enabled

Pair

SW1-SW2

SW3-SW4

Output

Current Sharing Relationship

Switching Frequency

Switching Phase

SW1

SW2

Master

Programmable

Programmable

Slave

Follows master

Master + 180°

SW3

SW4

Master

Programmable

Programmable

Slave

Follows master

Master + 180°

8.3.7 Fault Handling

OVP, OCP, and undervoltage protection (UVP) are handled for each switcher independently. OVP or OCP faults

that occur on one switcher do not affect the other outputs. There are two exceptions:

• If current-sharing mode (ISHARE) is detected for a switcher that faults, both switchers in parallel have the

same response to OVP or OCP.

20

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

•

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

When using internal sequencing, in the case of faults occurring during the initial power-up sequence, all

switchers are disabled for 500 ms, after which, the startup sequence is restarted.

During the soft-start time for a switcher, all fault signals (OVP, OCP, and UVP) are disabled and reset to the

unfaulted condition. The first moment when faults can be triggered is after the end of the soft-start sequence.

OVP thresholds are set as a percentage of VREF. A deglitching time of 50 μs is used for the overvoltage. When

an overvoltage occurs at the OVP upper threshold limit, the high-side FET and the low-side FET are disabled for

that switcher until the OVP falling threshold is reached. When the OVP falling threshold is reached, the low-side

FET turns on for 200 ns to ensure that the bootstrap capacitor is recharged before resuming normal operation of

the converter.

Output voltage falling below the UVP thresholds causes the corresponding PGOOD output to fall, but the

switcher continues to operate as it tries to increase the output voltage. However, if the PGOOD terminal is

tied to the enable ENSWx signal of another switcher on the PCB (for external sequencing), the output for that

ENSWx-PGOOD-tied switcher is disabled until output voltage is nominal and PGOOD is good.

OTP shuts down all switchers. When the temperature drops below the hysteresis level, a soft reset is triggered

and the chip restarts from the startup sequence.

Section 8.5.2.4 describes fault reporting and clearing of fault status registers.

The OVP and UVP sensing is deglitched to prevent unwanted tripping. The faults need to be sustained for more

than 55 μs typically (60 μs max) to be registered and trigger protection circuits and PGOOD output to fall. Fault

detection is disabled on a given switcher when its VREF is being ramped (as result of an I2C command to

change VREF). An additional 100-μs fault blanking time results after VREF has been adjusted to its target level.

8.3.8 OCP for SW1 to SW4

The OCP is I2C-programmable and set by the IOUT_MAX command. By default, the peak current IOUT_MAX

for SW1 and SW2 is 6 A, and for SW3 and SW4 it is 3 A. When the current reaches this threshold, the unit

immediately turns off the high-side FET and keeps the low-side FET off for the remainder of the switching cycle.

The following cycle are skipped (high-side FET off, low-side FET off) regardless of the inductor current. If the

current in the inductor is still higher than the IOUT_MAX after the skipped cycle, the following cycles are also

skipped until the current reach below the IOUT_MAX.

If the IOUT_MAX is reached more than 256 active cycles continuously, the switcher shut downs for 20 ms

and restarts. If the switcher is running in interleaved operation, both the switcher that tripped the IOUT_MAX

threshold and its interleaved counterpart shut down for 20 ms. After that period of time, the unit restarts and

goes through soft-start operation. For very-low duty cycle operation and faulty operation with very-fast current

increase during the high-side FET on-time (due to inductor saturation and so forth), OCP is also enforced on the

low side to ensure no runaway condition exists.

Table 8-2. Current Limit

Options

SWITCHER

IOUT_MAX

2A

3A

SW1, SW2

4A

5A

6 A (default)

0.5 A

SW3, SW4

1A

2A

3 A (default)

While the converter is shut down following an OCP event spanning more than 256 cycles, the COMP terminal

is pulled low for 1.1 ms prior to precharge and re-enabling of the converter. At the same time, the SSx pin is

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

21

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

discharged to AGND for 1.1 ms. If the soft-start is digital (SSx pins used as PGOODx outputs), the soft-start

value is reset.

256th consecutive OCP detect

First OCP detect

A

OCP Limit

t

Figure 8-11. Inductor Current During Overcurrent Event

At high switching frequency (>1 MHz) and particularly when there is a fault in the converter such as saturation

of the inductor, the current sensor might not sense the overcurrent event. To ensure that current protection is

provided in all operating scenarios, low-side current sensing is also present to provide overcurrent detection and

protection when the low-side FET is on. If over-current is detected when the low-side FET is on, the low-side

FET stays on (and the high-side FET off) until the current drops below the threshold. A new cycle will then begin

(high side on, low side off) when the next switching cycle occurs as driven by the internal clock derived from

the oscillator (internal or external synchronization). A dedicated counter records the low-side OCP events and

initiates a shutdown of the converter after 256 OCP event counts. Six consecutive cycles without a low-side OCP

event resets the counter.

A

Triggered Low Side OC

Low Side OCP Limit

t

Figure 8-12. Inductor Current During Overcurrent Event With Low-Side Detection

8.3.9 Overcurrent Protection for SW1 to SW4 in Current Sharing Operation

When the converter is running in interleaved operation, an OCP event will not trigger the COMP terminal to be

pulled low to 0.6 V. Instead, the error amplifier is switched off (tri-stated). This ensures that the COMP terminal

voltage remains constant so that the other phase continues to operate during the OCP event. An OCP event on

one switcher lasting more than 256 cycles triggers the shutdown of both switchers running in interleaved mode.

8.3.10 Recovery on Power Loss

All contents of the registers are saved and stored in the data store (non-volatile memory) with the exceptions

listed in Table 8-6 (Supported PMBus Commands) when STORE_DEFAULT_ALL is issued. Contents of the

registers are copied from the data store when power is restored. This allows the system processor to turn on the

power supplies as needed with the same default settings before power was lost.

22

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8.3.11 Feedback Compensation

Current Sense Gmps = 10 A/V (default)

and Peak

Current Control

VOUT

IL

RFB1

C1

FB

EA VREF

+

COMP

Rc

RLoad

RESR

RFB2

Gm = 120 µA/V

CRoll

Co

Cc

Figure 8-13. Simplified Equivalent Feedback Compensation Network

A typical compensation circuit could be type II (RC and CC) to have a phase margin between 60° and 90°,

or type III (RC, CC, and Cff) to improve the converter transient response. CRoll adds a high-frequency pole to

attenuate high-frequency noise when needed. CRoll should be set to at least twice the crossover frequency to

avoid interacting with the feedback compensation. It may also prevent noise coupling from other rails if there is

possibility of cross coupling in between rails when layout is very compact.

Table 8-3 shows the recommended values for the compensation network components as an initial start. These

result in the compensating zero of the Type II to match the dominant pole of the converter.

Table 8-3. Compensation Calculation Table

TYPE II

Select cross over frequency to be less than 1/5 of

switching frequency (typical is 1/10)

FC

RC

Set RC

FSW

10

FC

FSW

10

2S u FC u VOUT u CO

Gm u GmPS u VREF

RC

2S u FC u CO

Gm u GmPS

RLOAD u CO

RC

CC

RLOAD u CO

RC

Set CC

CC

Add CRoll if needed to remove large signal coupling to

high impedance COMP node.

CRoll

Cff compensating capacitor for type III compensation

network. Choose ƒzff same as FC.

TYPE III

Resr u Co

RC

N/A

CRoll

Cff

Resr u Co

RC

1

2S u fz ff u RFB1

8.3.12 Adjusting Output Voltage

The output voltage of each buck is set with a resistor divider from BUCK output to FB pin and ground. TI

recommends to use a 1% tolerance resistor or better one to get higher output voltage accuracy.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

23

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Vout

Vref

RFB1

RFB2

EA

FB Pin

±

TPS65400

Figure 8-14.

With RFB1 and RFB2, output voltage is determined by:

Vout

§

Vref u ¨ 1

©

RFB1 ·

RFB2 ¸¹

(4)

Default Vref in TPS65400 is 0.8 V. It can be programed from 0.6 to 1.87 V by digital interface PMBus. See (D8h)

VREF_COMMAND for more detailed information.

8.3.13 Digital Interface – PMBus

TPS65400 implements a PMBus-compatible I2C digital interface. The PMBus specification referenced by this

section is PMBus Power System Management Protocol Specification Part I – General Requirements, Transport

and Electrical Interface, Revision 1.2, dated 6 September 2010. The specification is published by the Power

Management Bus Implementers Forum and is available from http://pmbus.org/Specifications. See details in

Section 8.5.1 and Section 8.6.

8.3.14 Initial Configuration

The recommended method of configuring the TPS65400 the first time is through an external programmer

through a separate I2C programming header (as shown in Figure 8-15). The programming header needs to

connect to the SCL, SDA, CE, VDDD, and DGND lines, and can be done using a USB-to-I2C tool. This enables

the user to tailor the settings of the TPS65400 for each PCB specifically after PCB assembly, before the first

power-up of the board.

An alternative method is to use the firmware in an on-board microcontroller to do the initial configuration. To do

this, the user has two options:

•

•

Power the microcontroller and the TPS65400 (VDDD, CE, and DGND connections needed) from an external

source not controlled by the TPS65400.

Design the PCB so that the default settings of the TPS65400 allow the microcontroller to be powered when

power is applied to the TPS65400 the first time. The designer also needs to ensure that the default power-up

sequence, ramp-rates, and other default parameters do not damage any components when power is applied

the first time. After configuration, the microcontroller should pull CE low, and then all future power-ups result

in the newly configured power-up scheme to occur.

Using either method for the microcontroller requires the firmware to check if the TPS65400 has been previously

configured, or if a modification needs to be made to an already programmed configuration. Users may use

USER_DATA_BYTE_00 and/or USER_DATA_BYTE_01 to store a version number to identify which version of

the configuration is stored in the TPS65400.

A hybrid option may also be done where the initial configuration is done using an external programmer, and

the subsequent revisions are done through the microcontroller firmware. This eliminates the risk from damage

caused by the default configuration during the first power-up, but still allows the microcontroller firmware to

modify settings such as the VREF settings for subsequent power-ups.

24

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

User-Issued ON

OPERATION

User-Issued Soft-OFF

PAGE = 0xFF

VOUT1

1

VOUT2

2

VOUT3

5

3

VOUT4

4

PGOOD1

8

PGOOD2

PGOOD3

7

PGOOD4

6

t

1.

2.

3.

4.

A.

SW1 TON_DELAY

SW2 TON_DELAY

SW3 TON_DELAY

SW4 TON_DELAY

5.

6.

7.

8.

SW4 TOFF_DELAY

SW3 TOFF_DELAY

SW2 TOFF_DELAY

SW1 TOFF_DELAY

Configuration:

1.

2.

3.

Enable pins ENSWx set to inactive in PIN_CONFIG_00

Start sequence order SW1-SW2-SW3-SW4 in SEQUENCE_ORDER

Stop sequence order SW4-SW3-SW2-SW1 in SEQUENCE_ORDER

Figure 8-15. Example of Internal On Sequencing and Off Sequencing With the Default START_PGOOD

Dependence

OPERATION (SWx) refers to OPERATION register in the corresponding PMBus PAGE. See (01h) OPERATION

for more information on the OPERATION register.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

25

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

ENSW1

PVIN1

ENSW2

12 V

CB1

ENSW3

VOUT1

ENSW4

VDDD

PGOOD1

VDDD

PGOOD2

VDDD

PGOOD3

VDDD

PGOOD4

SW1

SS1/PG1

PGND1

SS2/PG2

VFB1

SS3/PG3

PVIN2

12 V

SS4/PG4

CB2

VOUT2

VDDD

Host

(Optional)

PGOOD(Global)

SW2

PGOOD

VDDD

PGND2

SDA

VDDD

SCL

TPS65400

VFB2

VDDD

PVIN3

I2CALERT

I2CADDR

CB3

RCLOCK_SYNC

SW3

12 V

VOUT3

CLK_OUT

VDDD

PGND (Thermal Pad)

RST_N

VFB3

CE

PVIN4

12 V

VIN

12 V

CB4

VDDD

SW4

VDDA

VDDG

PGND (Thermal Pad)

AGND

VFB4

COMP3

COMP1

COMP4

COMP2

Figure 8-16. Internal Sequencing Schematic With Host

26

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

ENSW1

PVIN1

ENSW2

VIN1

CB1

ENSW3

VOUT1

ENSW4

SW1

SS1/PG1

PGND1

SS2/PG2

VFB1

SS3/PG3

PVIN2

VIN2

SS4/PG4

CB2

VOUT2

SW2

PGOOD

VDDD

PGND2

SDA

Programmer

VDDD

TPS65400

SCL

VFB2

PVIN3

I2CALERT

I2CADDR

CB3

RCLOCK_SYNC

SW3

VIN3

VOUT3

CLK_OUT

VDDD

PGND (Thermal Pad)

RST_N

VFB3

CE

PVIN4

VIN

VIN

CB4

VDDD

SW4

VDDA

VDDG

PGND (Thermal Pad)

AGND

VFB4

COMP3

COMP1

COMP4

COMP2

Figure 8-17. Internal Sequencing Schematic Without Host

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

27

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8.4 Device Functional Modes

8.4.1 CCM Operation Mode

When the VIN/PVINx are above UVLO threshold and ENSWx are above the threshold, all four switchers operate

in continuous current mode(CCM) with IOUT_MODE (see (D6h) IOUT_MODE) setting default. In CCM, the

converters work in peak current mode for easy loop compensation and cycle-by-cycle high side MOSFET current

limit.

8.4.2 CCM/DCM Operation Mode

When DCM mode is enabled by setting IOUT_MODE (see (D6h) IOUT_MODE), the switchers transition to DCM

operation at light loads. During DCM mode, the low-side FET is turned off to prevent negative inductor current.

This increases light-load efficiency, but output ripple and transient response during DCM or during transitions

between DCM and CCM mode can be degraded.

At light load, the COMP terminal is driven by the error amplifier to the minimum clamp voltage. When the

COMP voltage reaches below 0.6 V and the error amplifier is sinking more than 5 μA, both the high-side and

low-side FET will be tri-stated to prevent the output voltage from rising above the set value. The FET function

is re-enabled when the GM amplifier sinks less than 3 μA. This results in a burst mode operation at light load.

The low-side FET has a 200-ns one-shot ON-time to ensure that the bootstrap capacitor is charged before the

normal function of the converter is resumed.

8.4.3 Current Sharing Mode

When SW1/SW2 pair output and/or SW3/SW4 pair output are shared, the responding pairs current sharing

mode is enabled and the ENABLE_PIN_CONFIG is set to single ENABLE. For the detail configuration, see

Section 9.2.2.

28

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

8.5 Programming

8.5.1 PMBus

8.5.1.1 Overview

The TPS65400 implements a lightweight PMBus-compliant layer supporting packet error checking, high-speed

bus, and group commands.

8.5.1.2 PMBus Protocol

The PMBus specification follows SMBus version 2.0. Figure 8-18 through Figure 8-25 show all supported

command transactions.

8.5.1.2.1 PMBus Protocol

Figure 8-18. Send Byte Protocol With PEC

1

7

1

1

8

1

8

1

1

Start

Slave address

Wr

Ack

Command

code

Ack

PEC

Ack

Stop

Figure 8-19. Write Byte Protocol With PEC

1

7

1

1

8

1

8

1

8

1

1

Start

Slave

address

Wr

Ack

Command

code

Ack

Data byte

Ack

PEC

Ack

Stop

Figure 8-20. Read Byte Protocol With PEC

1

7

1

1

8

1

1

Start

Slave address

Wr

Ack

Command code

Ack

Restart

7

1

1

8

1

8

1

1

Slave address

Rd

Ack

Data byte

Ack

PEC

Nack

Stop

Figure 8-21. Read Word Protocol With PEC

1

7

1

1

8

1

1

7

1

1

Start

Slave

address

Wr

Ack

Command

code

Ack

Restart

Slave

address

Rd

Ack

8

1

8

1

8

1

1

Data word (low)

Ack

Data word (high)

Ack

PEC

Nack

Stop

8.5.1.2.2 Transactions (No PEC)

Figure 8-22. Send Byte Protocol

1

7

1

1

8

1

1

Start

Slave address

Wr

Ack

Command code

Ack

Stop

Figure 8-23. Write Byte Protocol

1

7

1

1

8

1

8

1

1

Start

Slave address

Wr

Ack

Command

code

Ack

Data byte

Ack

Stop

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

29

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Figure 8-24. Read Byte Protocol

1

7

1

1

8

1

1

Start

Slave address

Wr

Ack

Command code

Ack

Restart

7

1

1

8

1

1

Slave address

Rd

Ack

Data byte

Nack

Stop

Figure 8-25. Read Word Protocol

1

7

1

1

8

1

8

7

1

1

Start

Slave

address

Wr

Ack

Command

code

Ack

Restart

Slave

address

Rd

Ack

8

1

8

1

1

Data word (low)

Ack

Data word (high)

Nack

Stop

8.5.1.2.3 Addressing

The 7-bit I2C address is set through the I2CADDR terminal with a resistor RADDR connected to AGND. Table

8-4 shows the connection between the voltage at the I2CADDR terminal and the set I2C address at VDDD =

3 V. The I2C address is determined only upon startup during tRESET_DELAY after rising edge of CE or RST_N.

This makes it immune to noise that may occur during normal operation. TI recommends resistors with 5% or

lower tolerance. If I2C is not necessary in the application, TI recommends to tie the I2CADDR terminal directly to

VDDD.

Table 8-4. I2C Address Selection

RADDR

7-BIT ADDRESS

180 kΩ

1101 111

120 kΩ

1101 110

82 kΩ

1101 101

56 kΩ

1101 100

39 kΩ

1101 011

22 kΩ

1101 010

10 kΩ

1101 001

2 kΩ

Test mode (factory-use only)

8.5.1.2.4 Startup

After CE is asserted and VDDD has reached 3.3 V, there is approximately a 320 μs delay before the PMBus

interface is active. During this time the TPS65400 is restoring its configuration from the EEPROM.

8.5.1.2.5 Bus Speed

100- and 400-kHz bus speeds are supported.

8.5.1.2.6 I2CALERT Terminal

When a timeout condition occurs, the I2CALERT terminal is pulsed low for 200 μs. A timeout condition is

defined as per SMBUS 2.0, tTIMEOUT. In addition to SCL, a timeout condition also occurs when the SDA line

is asserted low. If the timeout condition persists, I2CALERT continues to pulse every tTIMEOUT. The TPS65400

never intentionally pulls the SCL low beyond tLOW:SEXT 1, as that violates timing specifications. Therefore, the

I2CALERT terminal acts as a watchdog for other devices sharing the same bus that violate the cumulative clock

low extend time. On a system level, it can be seen as a non-maskable interrupt (NMI) signal for the I2C bus.

1

30

tLOW:SEXT: Cumulative clock low extend time (slave device). See more details on SMBus specification http://smbus.org/specs/.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: TPS65400

�TPS65400

www.ti.com

SLVSCQ9E – NOVEMBER 2014 – REVISED MARCH 2022

Table 8-5. Timeout Specifications

PARAMETER

MIN

MAX

tTIMEOUT:SCL

Detect clock low timeout

25

35

UNIT

ms

tTIMEOUT:SDA

Detect data low timeout

25

35

ms

8.5.1.2.7 CONTROL Terminal

The TPS65400 enable terminals ENSWx are equivalent to the CONTROL terminals in the fault handling. The

enable terminals behave as follows:

•

•

•

•