UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

www.ti.com

HIGH-SPEED VOLTAGE MODE PULSE WIDTH MODULATOR

Check for Samples: UCC25705-Q1, UCC25706-Q1

FEATURES

1

•

•

•

•

•

•

•

•

•

•

Qualified for Automotive Applications

Greater Than 4-MHz Operation

Integrated Oscillator / Voltage Feed Forward

Compensation

>4:1 Input Voltage Range

25-ns Current Limit Delay

Programmable Maximum Duty Cycle Clamp

Optocoupler Interface

50-µA Start-Up Current

4.2-mA Operating Current at 1 MHz

Latch-Up Exceeds 100mA per JESD78 Class I

•

Smallest Footprint of the 8-pin MSOP

Package Minimizes Board Area and Height

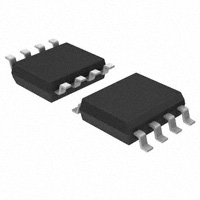

D PACKAGE

(TOP VIEW)

ILIM

FB

VFF

DISCH

1

8

2

7

3

6

4

5

VDD

OUT

GND

RC

DESCRIPTION

The UCC25705-Q1 and UCC25706-Q1 devices are 8-pin voltage mode primary side controllers with fast

over-current protection. These devices are used as core high-speed building blocks in high performance isolated

and non-isolated power converters.

UCC25705-Q1/UCC25706-Q1 devices feature a high speed oscillator with integrated feed-forward compensation

for improved converter performance. A typical current sense to output delay time of 25 ns provides fast response

to overload conditions. The IC also provides an accurate programmable maximum duty cycle clamp for increased

protection which can also be disabled for the oscillator to run at maximum possible duty cycle.

Two UVLO options are offered. The UCC25705-Q1 with lower turn-on voltage is intended for dc-to-dc converters

while the higher turn-on voltage and the wider UVLO range of the UCC25706-Q1 is better suited for offline

applications.

The UCC2570x-Q1 family is offered in an 8-pin SOIC (D) package.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2011, Texas Instruments Incorporated

�UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

www.ti.com

Figure 1. TYPICAL APPLICATION SCHEMATIC

+

VOUT

--

+

VIN

--

4

VDD

8

FB

2

DISCH

TPS2829

5

RC

3

VFF

6

GND

OUT

7

FET DRIVER

ILIM

SOFT

START

CIRCUIT

1

UCC2570x-Q1

MODE =1

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature (unless otherwise noted) (1) (2)

VALUE

UNIT

Supply voltage

15

V

Input voltage (VFF,RC,ILIM)

7

V

Input voltage (FB)

15

V

Input current (DISCH)

1

mA

Output current (OUT) dc

±20

mA

Storage temperature, Tstg

–65 to 150

°C

Junction temperature, TJ

–55 to 150

°C

300

°C

Lead temperature (soldering, 10 sec)

(1)

(2)

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. Consult ti.com/packaging for more

information.

RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

TA

Operating ambient temperature

VALUE

UNIT

–40 to 105

°C

ORDERING INFORMATION TABLE

TA

2

PACKAGE

ORDERABLE PART NUMBER

TOP-SIDE

MARKING

-–40°C to 125°C

SOIC-8 – D

Reel of 2500

UCC25706QDRQ1

25706Q

-–40°C to 125°C

SOIC-8 – D

Reel of 2500

UCC25705QDRQ1

Preview

Copyright © 2011, Texas Instruments Incorporated

�UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

www.ti.com

ESD RATINGS TABLE

PARAMETER

ESD

VALUE

UNIT

Human Body Model (HBM)

1000

V

Charged- Device Model (CDM)

1000

V

Machine Model ( MM)

200

V

Copyright © 2011, Texas Instruments Incorporated

3

�UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

www.ti.com

ELECTRICAL CHARACTERISTICS

VDD = 11 V, VIN = 30 V, RT = 47 k, RDISCH = 400 k, RFF = 14 k, CT = 220 pF, CVDD = 0.1 µF, and no load on the outputs, TA =

-–40° to 125°C, (unless otherwise specified)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Start threshold

8.0

8.8

9.6

V

Stop threshold

7.4

8.2

9.0

V

Hysteresis

0.3

0.6

1.0

V

Start threshold

11.2

12.0

12.8

V

Stop threshold

7.2

8.0

8.8

V

Hysteresis

3.2

4.0

4.5

V

UVLO section (UCCx5705)

UVLO section (UCCx5706)

Supply Current Section

Start-up current

VDD = UVLO start – 1 V, VDD comparator off

30

90

µA

IDD active

VDD comparator on, oscillator running at 1 MHz

4.2

5.0

mA

1.00

1.15

V

100

nA

1.1

MHz

Line Sense Section

Low line comparator threshold

0.95

Input bias current (VFF)

–100

Oscillator Section

Frequency

CT peak voltage

CT valley voltage

VFF = 1.2 V to 4.8 V

0.9

1.0

VFF = 1.2 V,

See

(1)

1.2

V

VFF = 4.8 V,

See

(1)

4.8

V

0

V

See

(1)

Current Limit Section

Input bias current

Current limit threshold

Propagation delay, ILIM to OUT

0.2

–0.2

–1

µA

180

200

220

mV

25

35

ns

30

50

90

kΩ

0

%

70

75

80

%

50 mV overdrive

Pulse Width Modulator Section

FB input impedance

VFB = 3 V

Minimum duty cycle

VFB < 2 V

Maximum duty cycle

PWM gain

VFB = VDD,

FOSC = 1 MHz

VDISCH = 0 V,

FOSC = 1 MHz

93

VFF = 2.5 V,

MODE = 1

12

Propagation delay, PWM to OUT

%

%/V

65

130

ns

V

Output Section

VOH

IOUT = –5 mA,

VOL

IOUT = 5 mA

Rise time

Fall time

(1)

4

VDD – output

0.3

0.6

0.15

0.4

V

CLOAD = 50 pF

10

25

ns

CLOAD = 50 pF

10

25

ns

Specified by design.

Copyright © 2011, Texas Instruments Incorporated

�UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

www.ti.com

PIN DESCRIPTIONS

DISCH: A resistor to VIN sets the oscillator discharge current programming a maximum duty cycle. When

grounded, an internal comparator switches the oscillator to a quick discharge mode. A small 100-pF capacitor

between DISCH and GND may reduce oscillator jitter without impacting feed-forward performance. IDISCH must

be between 25 µA and 250 µA over the entire VIN range.

FB: Input to the PWM comparator. This pin is intended to interface with an optocoupler. Input impedance is

50-kΩ typical.

GND: Ground return pin.

ILIM: Provides a pulse-by-pulse current limit by terminating the PWM pulse when the input is above 200 mV. This

provides a high speed (25 ns typical) path to reset the PWM latch, allowing for a pulse-by-pulse current limit.

OUT: The output is intended to drive an external FET driver or other high impedance circuits, but is not intended

to directly drive a power MOSFET. This improves the controller’s noise immunity. The output resistance of the

PWM controller, typically 60 Ω pull-up and 30 Ω pull-down, will result in excessive rise and fall times if a power

MOSFET is directly driven at the speeds for which the UCC2570x-Q1 is optimized.

RC: The oscillator can be configured to provide a maximum duty cycle clamp. In this mode the on-time is set by

RT and CT, while the off-time is set by RDISCH and CT.Since the voltage ramp on CTis proportional to VIN,

feed-forward action is obtained. Since the peak oscillator voltage is also proportional to VIN, constant frequency

operation is maintained over the full power supply input range. When theDISCH pin is grounded, the duty cycle

clamp is disabled. The RC pin then provides a low impedance path to ground CT during the off time.

VDD: Power supply pin. This pin should be bypassed with a 0.1-µF capacitor for proper operation. The

undervoltage lockout function of the UCC2570x-Q1 allows for a low current startupmode and ensures that all

circuits become active in a known state. The UVLO thresholds on the UCC25705-Q1 are appropriate for a

dc-to-dc converter application. The wider UVLO hysteresis of the UCC25706-Q1 (typically 4 V) is optimized for a

bootstrap startup mode from a high impedance source.

VFF: The feed-forward pin provides the controllerwith a voltage proportional to the power supply input voltage.

When the oscillator is providing a duty cycle clamp, a current of 2 × IDISCH is sourced from the VFF pin. A single

resistor RFF between VFF and GND then set VFF to:

æ

ö

2 ´ RFF

VFF » VIN ´ ç

÷

è 2 ´ RFF + RDISCH ø

When the DISCH pin is grounded and the duty cycle clamp is not used, the internal current source is disabled

and a resistor divider from VIN is used to set VFF. In either case, when the voltage on VFF is less than 1.0 V,

both the output and oscillator are disabled.

Copyright © 2011, Texas Instruments Incorporated

5

�UCC25705-Q1, UCC25706-Q1

SLUSAI1 – MAY 2011

50 mV

DISCH

4

www.ti.com

-+

MODE

1.0 V

VDD

I

LOW LINE

2 * I (MODE = 1)

0 (MODE = 0)

CLK

3

RC

5

Q

RD

RD

RD

Q

-+

VFF

S

PWM

LATCH

7

OUT

8

VDD

6

GND

1

ILIM

--

30 *I(MODE=1)

80 Ω (MODE =0)

Q

+

S

+

RD Q

UVLO

UCC25705-Q1 (8.8V/8V)

UCC25706-Q1 (12V/8V)

--

100 mV

+

0.7 V

FB

2

PWM

-+

30 kΩ

20 kΩ

200 mV

CURRENT LIMIT

+

1 pF

--

Figure 2. Block Diagram

FUNCTIONAL DESCRIPTION

Oscillator and PWM

The oscillator can be programmed to provide a duty cycle clamp or be configured to run at the maximum

possible duty cycle.

The PWM latch is set during the oscillator discharge and is reset by the PWM comparator when the CT waveform

is greater than the feedback voltage. The voltage at the FB pin is attenuated before it is applied to the PWM

comparator. The oscillator ramp is shifted by approximately 0.65-V at room temperature at the PWM comparator.

The offset has a temperature coefficient of approximately -–2 mV/°C.

The ILIM comparator adds a pulse by pulse current limit by resetting the PWM latch when VILIM > 200 mV. The

PWM latch is also reset by a low line condition (VFF