The following document contains information on Cypress products. The document has the series

name, product name, and ordering part numbering with the prefix “MB”. However, Cypress will

offer these products to new and existing customers with the series name, product name, and

ordering part number with the prefix “CY”.

How to Check the Ordering Part Number

1. Go to www.cypress.com/pcn.

2. Enter the keyword (for example, ordering part number) in the SEARCH PCNS field and click

Apply.

3. Click the corresponding title from the search results.

4. Download the Affected Parts List file, which has details of all changes

For More Information

Please contact your local sales office for additional information about Cypress products and

solutions.

About Cypress

Cypress is the leader in advanced embedded system solutions for the world's most innovative

automotive, industrial, smart home appliances, consumer electronics and medical products.

Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable,

high-performance memories help engineers design differentiated products and get them to market

first. Cypress is committed to providing customers with the best support and development

resources on the planet enabling them to disrupt markets by creating new product categories in

record time. To learn more, go to www.cypress.com.

�MB91460T Series

FR60 32-bit Microcontroller

MB91460T series is a line of general-purpose 32-bit RISC microcontrollers designed for embedded control applications which require

high-speed real-time processing, such as consumer devices and on-board vehicle systems. This series uses the FR60 CPU, which

is compatible with the FR family of CPUs.

This series contains the LIN-USART and CAN controllers.

Features

FR60 CPU core

■

32-bit RISC, load/store architecture, five-stage pipeline

■

16-bit fixed-length instructions (basic instructions)

■

Instruction execution speed: 1 instruction per cycle

■

Instructions including memory-to-memory transfer, bit

manipulation, and barrel shift instructions: Instructions suitable

for embedded applications

■

Function entry/exit instructions and register data multi-load

store instructions : Instructions supporting C language

■

External interrupt inputs : 12 channels *1

❐ 8 channels shared with A/D converter AN8-15

■

Bit search module (for REALOS)

❐ Function to search from the MSB (most significant bit) for the

position of the first “0”, “1”, or changed bit in a word

■

LIN-USART (full duplex double buffer): 11 channels *1

❐ Clock synchronous/asynchronous selectable

❐ Sync-break detection

❐ Internal dedicated baud rate generator

■

I2C bus interface (supports 400 kbps): 4 channels *1

❐ Master/slave transmission and reception

❐ Arbitration function, clock synchronization function

■

Register interlock function: Facilitating assembly-language

coding

■

Built-in multiplier with instruction-level support

❐ Signed 32-bit multiplication: 5 cycles

❐ Signed 16-bit multiplication: 3 cycles

■

CAN controller (C-CAN): Maximum of 2 channels

❐ Maximum transfer speed: 1 Mbps

❐ 32 transmission/reception message buffers

■

Interrupts (save PC/PS) : 6 cycles (16 priority levels)

■

■

Harvard architecture enabling program access and data

access to be performed simultaneously

Sound generator : 1 channel

❐ Tone frequency : PWM frequency divide-by-two (reload value

+ 1)

■

Instructions compatible with the FR family

■

Monitor external voltage

❐ Generate an interrupt in case of voltage lower/higher than

the defined thresholds (reference voltage)

■

16-bit PPG timer : 14 channels *1

■

16-bit PFM timer : 1 channel *1

■

16-bit reload timer: 8 channels

■

16-bit free-run timer: 8 channels (1 channel each for ICU and

OCU) *1

■

Input capture: 8 channels (operates in conjunction with the

free-run timer)

■

Output compare: 8 channels (operates in conjunction with the

free-run timer)

■

Up/Down counter: 2 channels (4*8-bit or 2*16-bit) *1

■

Watchdog timer

■

Real-time clock

■

Low-power consumption modes : Sleep/stop mode function

■

Low voltage detection circuit

Internal peripheral resources

■

General-purpose ports : Maximum 109 ports

■

DMAC (DMA Controller)

❐ Maximum of 5 channels able to operate simultaneously

❐ 2 transfer sources (internal peripheral/software)

❐ Activation source can be selected using software

❐ Addressing mode specifies full 32-bit addresses

(increment/decrement/fixed)

❐ Transfer mode (demand transfer/burst transfer/step

transfer/block transfer)

❐ Transfer data size selectable from 8/16/32-bit

❐ Multi-byte transfer enabled (by software)

❐ DMAC descriptor in I/O areas (200H to 240H, 1000H to

1024H)

■

A/D converter (successive approximation type)

❐ 10-bit resolution: 32 channels *1

❐ Conversion time: minimum 1 s

Note:

• MB91F469TA device is planned

*1:

The maximum channel count is given; the real number depends on port multiplexing.

Cypress Semiconductor Corporation

Document Number: 002-04631 Rev. *A

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised April 12, 2016

�MB91460T Series

■

Clock supervisor

❐ Monitors the sub-clock (32 kHz) and the main clock

(4 MHz) , and switches to a recovery clock (CR oscillator,

etc.) when the oscillations stop.

■

■

Clock modulator

Package and technology

■

Clock monitor

■

Sub-clock calibration

❐ Corrects the real-time clock timer when operating with the

32 kHz or CR oscillator

■

Main oscillator stabilization timer

❐ Generates an interrupt in sub-clock mode after the

stabilization wait time has elapsed on the 23-bit stabilization

wait time counter

Sub-oscillator stabilization timer

❐ Generates an interrupt in main clock mode after the

stabilization wait time has elapsed on the 15-bit stabilization

wait time counter

■

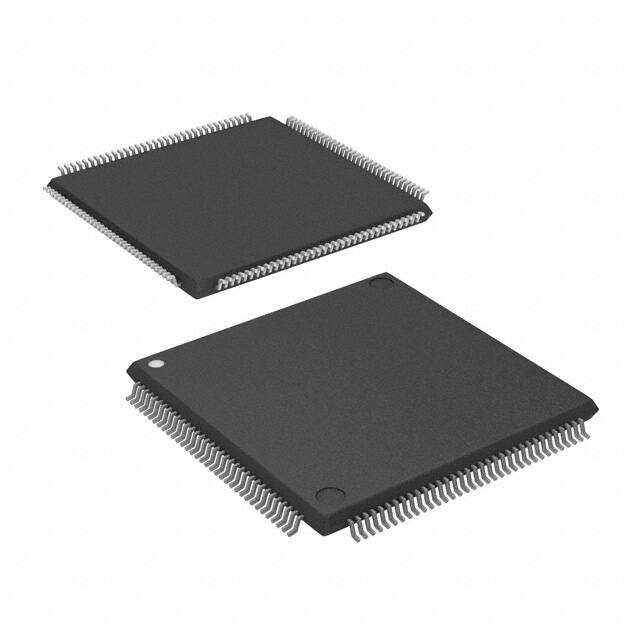

Package: QFP-144

■

CMOS 0.18 m technology

■

Power supply range 3 V to 5 V (1.8 V internal logic provided by

a step-down voltage converter)

■

Operating temperature range: between - 40°C and + 105°C /

+ 125°C *2

Note:

*2:

For maximum ambient temperature TA(max), please refer to 17. Ordering Information.

Document Number: 002-04631 Rev. *A

Page 2 of 137

�MB91460T Series

Contents

Product Lineup ................................................................. 4

Pin Assignment ................................................................ 7

MB91F467TA, MB91F469TA ...................................... 7

Pin Description ................................................................. 8

MB91F467TA, MB91F469TA ...................................... 8

I/O Circuit Types ............................................................. 20

Port Multiplexing ............................................................ 26

PPMUX Register ....................................................... 26

Multiplex Pinout MB91F467TA, MB91F469TA .......... 27

Handling Devices ............................................................ 28

Preventing Latch-up .................................................. 28

Handling of unused input pins ................................... 28

Power supply pins ..................................................... 28

Crystal oscillator circuit .............................................. 28

Notes on using external clock ................................... 28

Mode pins (MD_x) ..................................................... 28

Notes on operating in PLL clock mode ...................... 29

Pull-up control ........................................................... 29

Notes on PS register ................................................. 29

Notes on Debugger ........................................................ 30

Execution of the RETI Command .............................. 30

Break function ........................................................... 30

Operand break .......................................................... 30

Block Diagram ................................................................ 31

MB91F467TA, MB91F469TA .................................... 31

CPU and Control Unit ..................................................... 32

Features .................................................................... 32

Internal architecture ................................................... 32

Programming model .................................................. 33

Registers ................................................................... 34

Document Number: 002-04631 Rev. *A

Embedded Program/Data Memory (Flash) ................... 37

Flash features ............................................................ 37

Operation modes ....................................................... 37

Flash access in CPU mode ....................................... 38

Parallel Flash programming mode ............................ 42

Poweron Sequence in parallel programming mode .. 46

Flash Security ............................................................ 46

Notes About Flash Memory CRC Calculation ........... 49

Memory Space ................................................................ 50

Memory Maps .................................................................. 51

MB91F467TA, MB91F469TA .................................... 51

I/O Map ............................................................................. 52

MB91F467TA, MB91F469TA .................................... 52

Flash memory and external bus area ........................ 77

Interrupt Vector Table .................................................... 81

Recommended Settings ................................................. 87

PLL and Clockgear settings ...................................... 87

Clock Modulator settings ........................................... 88

Electrical Characteristics ............................................... 93

Absolute maximum ratings ........................................ 93

Recommended operating conditions ......................... 96

DC characteristics ..................................................... 96

A/D converter characteristics .................................. 101

FLASH memory program/erase characteristics ...... 105

AC characteristics ................................................... 106

Ordering Information .................................................... 129

Package Dimension ...................................................... 130

Revision History ........................................................... 131

Major Changes .............................................................. 134

Document History ......................................................... 136

Page 3 of 137

�MB91460T Series

1. Product Lineup

Feature

MB91V460A

MB91FV460B *4

MB91F467TA

MB91F469TA *3

Max. core frequency (CLKB)

80MHz

100MHz

100MHz

100MHz

Max. resource frequency

(CLKP)

40MHz

50MHz

50MHz

50MHz

Max. external bus freq.

(CLKT)

40MHz

50MHz

50MHz

50MHz

Max. CAN frequency

(CLKCAN)

20MHz

50MHz

50MHz

50MHz

-

-

-

-

0.35m

0.18um

0.18m

0.18m

yes

yes

yes

yes

yes (disengageable)

yes (disengageable)

yes

yes

Bit Search

yes

yes

yes

yes

Reset input (INITX)

yes

yes

yes

yes

Hardware Standby input

(HSTX)

yes

yes

no

no

Clock Modulator

yes

yes

yes

yes

Clock Monitor

yes

yes

yes

yes

Low Power Mode

yes

yes

yes

yes

DMA

5 ch

5 ch

5 ch

5 ch

Max. FlexRay frequency

(SCLK)

Technology

Watchdog

Watchdog (RC osc. based)

MAC (DSP)

MMU/MPU

no

MPU (16 ch)

no

1)

MPU (16

no

ch) 1)

MPU (8 ch)

no

1)

MPU (8 ch) 1)

Emulation SRAM 32bit

read data

Internal Flash memory

2112KB +external

emulation SRAM with

64bit read data

1088 KByte

2112 KByte

Satellite Flash

-

-

no

no

Flash Protection

-

yes

yes

yes

D-RAM

64 KByte

64 KByte

32 KByte

64 KByte

ID-RAM

64 KByte

64 KByte

32 KByte

64 KByte

Flash-Cache (Instruction

cache)

16 KByte

16 KByte

8 KByte

16 KByte

4 KByte fixed

16 KByte Boot Flash

+ 1KB Boot ROM

4 KByte

4 KByte

1 ch

1 ch

1 ch

1 ch

Flash

Boot-ROM / BI-ROM

RTC

Free Running Timer

Document Number: 002-04631 Rev. *A

8 ch

12 ch

8

ch*2

8 ch*2

Page 4 of 137

�MB91460T Series

MB91V460A

MB91FV460B *4

MB91F467TA

MB91F469TA *3

ICU

8 ch

10 ch

8 ch*2

8 ch*2

OCU

8 ch

8 ch

8 ch*2

8 ch*2

Reload Timer

8 ch

16 ch

8 ch

8 ch

Feature

*2

14 ch*2

PPG 16-bit

16 ch

32 ch

14 ch

PFM 16-bit

1 ch

1 ch

1 ch*2

1 ch*2

Sound Generator

1 ch

1 ch (old) + 1 ch (new)

1 ch

1 ch

4 ch (8-bit) / 2 ch (16-bit)

4 ch (8-bit) / 2 ch

(16-bit)

4 ch (8-bit) / 2 ch

(16-bit)*2

4 ch (8-bit) / 2 ch

(16-bit)*2

6 ch (128msg)

6 ch (128msg)

2 ch (32msg)

2 ch (32msg)

4 ch + 4 ch FIFO + 8 ch

16 ch FIFO

4 ch + 4 ch FIFO + 3

ch*2

4 ch + 4 ch FIFO + 3

ch*2

4 ch

8 ch

4 ch*2

4 ch*2

yes (32bit addr, 32bit data)

yes (32bit addr, 32bit

data)

yes (24bit addr, 16bit

data)

yes (24bit addr, 16bit

data)

External Interrupts

16 ch

32 ch

12 ch*2

12 ch*2

NMI Interrupts

1 ch

1 ch

1 ch

1 ch

SMC

6 ch

6 ch

-

-

LCD controller (40x4)

1 ch

1 ch

-

-

ADC (10 bit)

32 ch

32 ch + 22 ch

32 ch*2

32 ch*2

Alarm Comparator

2 ch

2 ch

-

-

Supply Supervisor

yes

yes

yes

yes

Clock Supervisor

yes

yes

yes

yes

Main clock oscillator

4MHz

4MHz

4MHz

4MHz

Sub clock oscillator

32kHz

32kHz

32kHz

32kHz

RC Oscillator

100kHz

100kHz

100kHz / 2MHz

100kHz / 2MHz

PLL

x 20

x 25

x 25

x 25

DSU4

yes

DSU4

-

Up/Down Counter (8/16-bit)

C_CAN

LIN-USART

I2C (400k)

FR external bus

EDSU

yes (32 BP)

Supply Voltage

Regulator

Document Number: 002-04631 Rev. *A

*1

yes (32 BP) *1

yes (16 BP)

*1

yes (16 BP) *1

3V / 5V

1.8V + 3V / 5V

3V / 5V

3V / 5V

yes

-

yes

yes

Page 5 of 137

�MB91460T Series

MB91V460A

MB91FV460B *4

MB91F467TA

MB91F469TA *3

n.a.

16 ...100MHz)

ESD Protection

(Human body model)

Remarks

Typ

Power supply slew rate

Operating temperature

Unit

Min

100

2

200

4

ms

kV

Rdischarge = 1.5kΩ

Cdischarge = 100pF

kHz

MHz

VDDCORE > 1.65V

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor

device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges.

Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet.

Users considering application outside the listed conditions are advised to contact their representatives beforehand.

VCC18C

VSS5

AVSS5

CS

Document Number: 002-04631 Rev. *A

Page 96 of 137

�MB91460T Series

16.3 DC characteristics

Note: In the following tables, “VDD” means VDD35 for pins of ext. bus or VDD5 for other pins.

In the following tables, “VSS” means VSS5 for all pins.

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40 °C to TA(max))

Parameter

Symbol

Pin name

Value

Unit

Remarks

Min

Typ

Max

0.8 VDD

—

VDD + 0.3

V

CMOS

hysteresis

input

0.7 VDD

—

VDD + 0.3

V

4.5 V < VDD < 5.5 V

0.74 VDD

—

VDD + 0.3

V

3 V < VDD < 4.5 V

—

Port inputs if CMOS

Hysteresis 0.8/0.2

input is selected

—

Port inputs if CMOS

Hysteresis 0.7/0.3

input is selected

—

AUTOMOTIVE

Hysteresis input is

selected

0.8 VDD

—

VDD + 0.3

V

—

Port inputs if TTL

input is selected

2.0

—

VDD + 0.3

V

VIH

Input “H”

voltage

Condition

VIHR

INITX

—

0.8 VDD

—

VDD + 0.3

V

INITX input pin

(CMOS Hysteresis)

VIHM

MD_2 to MD_0

—

VDD - 0.3

—

VDD + 0.3

V

Mode input pins

VIHX0S

X0, X0A

—

2.5

—

VDD + 0.3

V

External clock in

“Oscillation mode”

VIHX0F

X0

—

0.8 VDD

—

VDD + 0.3

V

External clock in “Fast

Clock Input mode”

—

Port inputs if CMOS

Hysteresis 0.8/0.2

input is selected

VSS - 0.3

—

0.2 VDD

V

—

Port inputs if CMOS

Hysteresis 0.7/0.3

input is selected

VSS - 0.3

—

0.3 VDD

V

VSS - 0.3

—

0.5 VDD

V

4.5 V < VDD < 5.5 V

—

Port inputs if

AUTOMOTIVE

Hysteresis input is

selected

VSS - 0.3

—

0.46 VDD

V

3 V < VDD < 4.5 V

—

Port inputs if TTL

input is selected

VSS - 0.3

—

0.8

V

VIL

Input “L”

voltage

VILR

INITX

—

VSS - 0.3

—

0.2 VDD

V

INITX input pin

(CMOS Hysteresis)

VILM

MD_2 to MD_0

—

VSS - 0.3

—

VSS + 0.3

V

Mode input pins

VILXDS

X0, X0A

—

VSS - 0.3

—

0.5

V

External clock in

“Oscillation mode”

Document Number: 002-04631 Rev. *A

Page 97 of 137

�MB91460T Series

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40 °C to TA(max))

Parameter

Symbol

Pin name

Condition

Input “L” voltage

VILXDF

X0

—

VOH2

Normal

outputs

Output “H”

voltage

Output “L“

voltage

Input leakage

current

VOH5

Normal

outputs

VOH3

I2C

outputs

VOL2

Normal

outputs

VOL5

Normal

outputs

VOL3

I2C

outputs

IIL

Pnn_m

*1

Analog input

leakage current

IAIN

Pull-up

resistance

RUP

Pnn_m *4,

INITX

Pull-down

resistance

RDOWN

Pnn_m *4

Input

capacitance

CIN

ANn *3

Unit

Remarks

Min

Typ

Max

VSS0.3

—

0.2VDD

V

External clock in “Fast

Clock Input mode”

VDD0.5

—

—

V

Driving strength set to

2 mA

VDD0.5

—

—

V

Driving strength set to

5 mA

VDD0.5

—

—

V

—

—

0.4

V

Driving strength set to

2 mA

—

—

0.4

V

Driving strength set to

5 mA

3.0V VDD 5.5V,

IOL = + 3mA

—

—

0.4

V

3.0V VDD 5.5V

VSS5 < VI < VDD

TA=25 °C

1

—

+1

3.0V VDD 5.5V

VSS5 < VI < VDD

TA=TA(max)

3

—

+3

3.0V VDD 5.5V

TA=25 °C

1

—

+1

μA

3.0V VDD 5.5V

TA=TA(max)

3

—

+3

μA

3.0V VDD 3.6V

40

100

160

4.5V VDD 5.5V

25

50

100

3.0V VDD 3.6V

40

100

180

4.5V VDD 5.5V

25

50

100

-

5

15

4.5V VDD 5.5V,

IOH = - 2mA

3.0V VDD 4.5V,

IOH = - 1.6mA

4.5V VDD 5.5V,

IOH = - 5mA

3.0V VDD 4.5V,

IOH = - 3mA

3.0V VDD 5.5V,

IOH = - 3mA

4.5V VDD 5.5V,

IOL = + 2mA

3.0V VDD 4.5V,

IOL = + 1.6mA

4.5V VDD 5.5V,

IOL = + 5mA

3.0V VDD 4.5V,

IOL = + 3mA

All except

VDD5,

VDD5R,

f = 1 MHz

VSS5,

AVCC5,

AVSS,

AVRH5

Document Number: 002-04631 Rev. *A

Value

μA

kΩ

kΩ

pF

Page 98 of 137

�MB91460T Series

Parameter

Symbol

ICC

ICCH

Pin name

VDD5R

VDD5R

Power supply

current

MB91F467TA

Condition

Value

Unit

Min

Typ

Max

CLKB:

100 MHz

CLKP:

50 MHz

CLKT:

50 MHz

CLKCAN: 50 MHz

—

110

140

mA

TA = + 25 °C

—

30

150

μA

TA = + 105 °C

—

300

2000

μA

TA = + 125 °C

—

600

4000

μA

TA = + 25 °C

—

100

500

μA

TA = + 105 °C

—

500

2200

μA

TA = + 125 °C

—

800

4400

μA

TA = + 25 °C

—

50

250

μA

TA = + 105 °C

—

400

2100

TA = + 125 °C

—

700

4200

μA

Remarks

Code fetch from Flash

At stop mode *2

RTC :

4 MHz mode *2

RTC :

100 kHz mode *2

32 kHz mode *5

ILVE

VDD5

—

—

70

150

μA

External low voltage

detection

ILVI

VDD5R

—

—

50

100

μA

Internal low voltage

detection

—

—

250

500

μA

Main clock

(4 MHz)

—

—

20

40

μA

Sub clock

(32 kHz)

CLKB: 100 MHz

CLKP:

50 MHz

CLKT:

50 MHz

CLKCAN: 50 MHz

—

140

170

mA

Code fetch from Flash

TA = + 25 °C

—

50

210

μA

TA = + 105 °C

—

0.6

2.8

mA

TA = + 25 °C

—

120

560

μA

TA = + 105 °C

—

0.7

3.2

mA

TA = + 25 °C

—

70

310

μA

TA = + 105 °C

—

0.65

3.0

mA

IOSC

ICC

ICCH

VDD5

VDD5R

VDD5R

Power supply

current

MB91F469TA

(target data)

At stop mode*2

RTC :

4 MHz mode*2

RTC :

100 kHz mode*2

32 kHz mode *5

ILVE

VDD5

—

—

70

150

μA

External low voltage

detection

ILVI

VDD5R

—

—

50

100

μA

Internal low voltage

detection

—

—

250

500

μA

Main clock

(4 MHz)

—

—

20

40

μA

Sub clock

(32 kHz)

IOSC

VDD5

*1 Pnn_m includes all pins unless the pins, which include analog inputs.

*2 Main regulator OFF, sub regulator set to 1.2V, Low voltage detection disabled.

Document Number: 002-04631 Rev. *A

Page 99 of 137

�MB91460T Series

*3 ANn includes all pins where AN channels are enabled.

*4 Pnn_m includes all GPIO pins. The pull down resistors must be enabled by PPER/PPCR setting and the pins must be in input

direction.

*5 Main regulator OFF, sub regulator set to 1.2V, Low voltage detection disabled, RC oscillator enabled.

Additional current consumption of Sub oscillator IOSC has to be taken into account.

Document Number: 002-04631 Rev. *A

Page 100 of 137

�MB91460T Series

16.4 A/D converter characteristics

Parameter

(VDD5 = AVCC5 = 3.0 V to 5.5 V, VSS5 = AVSS5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

Resolution

—

Total error

Value

Unit

Remarks

Min

Typ

Max

—

—

—

10

bit

—

—

-3

—

+3

LSB

Nonlinearity error

—

—

- 2.5

—

+ 2.5

LSB

Differential nonlinearity

error

—

—

- 1.9

—

+ 1.9

LSB

Zero reading voltage

VOT

ANn

AVRL1.5

LSB

AVRL + 0.5

LSB

AVRL + 2.5

LSB

V

Full scale reading voltage

VFST

ANn

AVRH3.5

LSB

AVRH1.5

LSB

AVRH + 0.5

LSB

V

0.6

—

16,500

μs

4.5 V < AVCC5 <

5.5 V

2.0

—

—

μs

3.0 V < AVCC5 <

4.5 V

0.4

—

—

μs

4.5 V < AVCC5 <

5.5 V,

REXT < 2 kΩ

1.0

—

—

μs

3.0 V < AVCC5 <

4.5 V,

REXT < 1 kΩ

1.0

—

—

μs

4.5 V < AVCC5 <

5.5 V

3.0

—

—

μs

3.0 V < AVCC5 <

4.5 V

—

—

11

pF

—

—

2.6

kΩ

4.5 V < AVCC5 <

5.5 V

—

—

12.1

kΩ

3.0 V < AVCC5 <

4.5 V

-1

—

+1

μA

TA = + 25 °C

-3

—

+3

μA

TA = + 105 °C

Compare time

Sampling time

Conversion time

Input capacitance

Input resistance

Tcomp

Tsamp

Tconv

CIN

RIN

—

—

—

ANn

ANn

Analog input leakage

current

IAIN

ANn

Analog input voltage range

VAIN

ANn

AVRL

—

AVRH

V

—

ANn

—

—

4

LSB

Offset between input channels

(Continued)

Note : The accuracy gets worse as AVRH - AVRL becomes smaller

Document Number: 002-04631 Rev. *A

Page 101 of 137

�MB91460T Series

(Continued)

Parameter

Reference voltage range

Power supply current

per ADC macro *3

Reference voltage current

per ADC macro *3

Symbol

Pin name

AVRH

Value

Unit

Remarks

Min

Typ

Max

AVRH5

0.75AVCC5

—

AVCC5

V

AVRL

AVSS5

AVSS5

—

AVCC50.25

V

IA

AVCC5

—

2.5

5

mA

A/D Converter

active

IAH

AVCC5

—

—

5

μA

A/D Converter not

operated *1

IR

AVRH5

—

0.7

1

mA

A/D Converter

active

IRH

AVRH5

—

—

5

μA

A/D Converter not

operated *2

*1 : Supply current at AVCC5, if A/D converter and ALARM comparator are not operating,

(VDD5 = AVCC5 = AVRH = 5.0 V)

*2 : Input current at AVRH5, if A/D converter is not operating, (VDD5 = AVCC5 = AVRH = 5.0 V)

*3 : The current consumption per ADC macro is given here. On devices having more then one A/D converter, the current values have

to be multiplied by the number of macros.

Sampling Time Calculation

Tsamp = (2.25 kOhm + REXT) × 10.7pF × 7;

Tsamp = (13.6 kOhm + REXT) × 10.7pF × 7;

for 4.5V ≤ AVCC5 ≤ 5.5V

for 3.0V ≤ AVCC5 ≤ 4.5V

Conversion Time Calculation

Tconv = Tsamp + Tcomp

Document Number: 002-04631 Rev. *A

Page 102 of 137

�MB91460T Series

Definition of A/D converter terms

• Resolution

Analog variation that is recognizable by the A/D converter.

• Nonlinearity error

Deviation between actual conversion characteristics and a straight line connecting the zero transition point

(00 0000 0000B 00 0000 0001B) and the full scale transition point (11 1111 1110B 11 1111 1111B).

• Differential nonlinearity error

Deviation of the input voltage from the ideal value that is required to change the output code by 1 LSB.

• Total error

This error indicates the difference between actual and theoretical values, including the zero transition error, full scale transition

error, and nonlinearity error.

Total error

3FFH

3FEH

1.5 LSB’

Actual conversion

characteristics

3FDH

{1 LSB’ (N - 1) + 0.5 LSB’}

004H

VNT

(measurement value)

003H

Actual conversion

characteristics

Digital output

002H

Ideal characteristics

001H

0.5 LSB'

AVSS5

Analog input

1LSB' (ideal value) =

AVRHAVSS5

1024

Total error of digital output N =

AVRH

[V]

VNT{1 LSB' (N - 1) + 0.5 LSB'}

1 LSB'

N : A/D converter digital output value

VOT' (ideal value) = AVSS5 + 0.5 LSB' [V]

VFST' (ideal value) = AVRH1.5 LSB' [V]

VNT : Voltage at which the digital output changes from (N + 1) H to NH

(Continued)

Document Number: 002-04631 Rev. *A

Page 103 of 137

�MB91460T Series

(Continued)

Nonlinearity error

3FFH

Differential nonlinearity error

Actual conversion characteristics

Actual conversion characteristics

(N+1)H

3FEH

{1 LSB (N - 1) + VOT}

VFST

(measurement value)

3FDH

Ideal

characteristics

NH

004H

VNT

(measurement value)

002H

(N-1)H

Actual conversion

characteristics

Digital output

Digital output

003H

Ideal characteristics

001H

VTO (measurement value)

AVSS5

VNT

(measurement value)

(measurement value)

(N-2)H

Actual conversion

characteristics

AVSS5

AVRH

Analog input

AVRH

Analog input

Nonlinearity error of digital output N =

VNT{1LSB (N1) + VOT}

1LSB

Differential nonlinearity error of digital output N =

1LSB =

VFST

VFSTVOT

1022

V (N + 1) TVNT

1LSB

[LSB]

1 [LSB]

[V]

N

: A/D converter digital output value

VOT : Voltage at which the digital output changes from 000H to 001H.

VFST : Voltage at which the digital output changes from 3FEH to 3FFH.

Document Number: 002-04631 Rev. *A

Page 104 of 137

�MB91460T Series

16.5 FLASH memory program/erase characteristics

16.5.1 MB91F467TA, MB91F469TA

(TA = 25oC, Vcc = 5.0V)

Value

Parameter

Unit

Remarks

2.0

s

Erasure programming time not included

n*0.5

n*2.0

s

n is the number of Flash sector of the

device

6

100

μs

System overhead time not included

Min

Typ

Max

Sector erase time

-

0.5

Chip erase time

-

Word programming time

-

Programme/Erase cycle

10 000

cycle

Flash data retention time

20

year

*1

*1:This value was converted from the results of evaluating the reliability of the technology

(using Arrhenius equation to convert high temperature measurements into normalized value at 85oC)

Document Number: 002-04631 Rev. *A

Page 105 of 137

�MB91460T Series

16.6 AC characteristics

16.6.1 Clock timing

Parameter

Clock frequency

(VDD5 = 3.0 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

fC

Value

Pin name

Unit

Condition

16

MHz

Opposite phase external

supply or crystal

100

kHz

Min

Typ

Max

X0

X1

3.5

4

X0A

X1A

32

32.768

Clock timing condition

tC

X0,

X1,

X0A,

X1A

0.8 VCC

0.2 VCC

PWH

Document Number: 002-04631 Rev. *A

PWL

Page 106 of 137

�MB91460T Series

16.6.2 Reset input ratings

Parameter

INITX input time

(at power-on)

INITX input time

(other than the above)

(VDD5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

Condition

tINTL

INITX

—

Value

Unit

Min

Max

10

—

ms

20

—

μs

tINTL

INITX

Document Number: 002-04631 Rev. *A

0.2 VCC

Page 107 of 137

�MB91460T Series

16.6.3 LIN-USART Timings at VDD5 = 3.0 to 5.5 V

• Conditions during AC measurements

• All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD5 = 3.0 V to 5.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = -40 to TA(max)

- Cl = 50 pF (load capacity value of pins when testing)

- VOL = 0.2 x VDD5,

- VOH = 0.8 x VDD5

- EPILR = 0, PILR = 1 (Automotive Level = worst case)

(VDD5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40°C to TA(max))

Parameter

Symbol

Pin name

Serial clock

cycle time

tSCYCI

SCKn

SCK ↓ → SOT

delay time

tSLOVI

SCKn

SOTn

SOT → SCK ↓

delay time

tOVSHI

SCKn

SOTn

Valid SIN →

SCK ↑ setup time

tIVSHI

SCKn

SINn

SCK ↑ →valid SIN

hold time

tSHIXI

Serial clock

“H” pulse width

Condition

VDD5 = 3.0 V to 4.5 V

VDD5 = 4.5 V to 5.5 V

Unit

Min

Max

Min

Max

4 tCLKP

—

4 tCLKP

—

ns

- 30

30

- 20

20

ns

m×

tCLKP - 30*

—

m×

tCLKP - 20*

—

ns

tCLKP + 55

—

tCLKP + 45

—

ns

SCKn

SINn

0

—

0

—

ns

tSHSLE

SCKn

tCLKP + 10

—

tCLKP + 10

—

ns

Serial clock

“L” pulse width

tSLSHE

SCKn

tCLKP + 10

—

tCLKP + 10

—

ns

SCK ↓ →SOT

delay time

tSLOVE

SCKn

SOTn

—

2 tCLKP + 55

—

2 tCLKP + 45

ns

Valid SIN →

SCK ↑ setup time

tIVSHE

SCKn

SINn

10

—

10

—

ns

SCK ↑ →valid SIN

hold time

tSHIXE

SCKn

SINn

tCLKP + 10

—

tCLKP + 10

—

ns

SCK rising time

tFE

SCKn

—

20

—

20

ns

SCK falling time

tRE

SCKn

—

20

—

20

ns

Internal

clock

operation

(master

mode)

External

clock

operation

(slave mode)

* : Parameter m depends on tSCYCI and can be calculated as :

if tSCYCI = 2*k*tCLKP, then m = k, where k is an integer > 2

if tSCYCI = (2*k + 1)*tCLKP, then m = k + 1, where k is an integer > 1

Notes : • The above values are AC characteristics for CLK synchronous mode.

• tCLKP is the cycle time of the peripheral clock.

Document Number: 002-04631 Rev. *A

Page 108 of 137

�MB91460T Series

Internal clock mode (master mode)

tSCYCI

SCKn

for ESCR:SCES = 0

VOH

VOL

VOL

VOH

SCKn

for ESCR:SCES = 1

VOH

VOL

tSLOVI

tOVSHI

VOH

VOL

SOTn

tIVSHI

tSHIXI

VIH

VIL

SINn

VIH

VIL

External clock mode (slave mode)

tSLSHE

SCKn

for ESCR:SCES = 0

VOH

SCKn

for ESCR:SCES = 1

VOL

tSHSLE

VOH

VOL

VOL

VOH

VOH

VOL

VOH

VOL

tRE

tFE

tSLOVE

SOTn

VOH

VOL

tIVSHE

SINn

Document Number: 002-04631 Rev. *A

VIH

VIL

tSHIXE

VIH

VIL

Page 109 of 137

�MB91460T Series

16.6.4 I2C AC Timings at VDD5 = 3.0 to 5.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 3 mA

- VDD5 = 3.0 V to 5.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = 40°C to TA(max)

- Cl = 50 pF

- VOL = 0.3VDD5

- VOH = 0.7VDD5

- EPILR = 0, PILR = 0 (CMOS Hysteresis 0.3VDD5/0.7VDD5)

Fast mode:

(VDD5 = 3.5 V to 5.5 V, VSS5 = 0 V, TA = 40°C to TA(max))

Parameter

Symbol

Pin name

fSCL

Value

Unit

Min

Max

SCLn

0

400

kHz

tHD;STA

SCLn, SDAn

0.6

—

μs

LOW period of the SCL clock

tLOW

SCLn

1.3

—

μs

HIGH period of the SCL clock

tHIGH

SCLn

0.6

—

μs

Setup time for a repeated START

condition

tSU;STA

SCLn, SDAn

0.6

—

μs

Data hold time for I2C-bus devices

tHD;DAT

SCLn, SDAn

0

0.9

μs

Data setup time

tSU;DAT

SCLn SDAn

100

—

ns

Rise time of both SDA and SCL signals

tr

SCLn, SDAn

20 + 0.1Cb

300

ns

Fall time of both SDA and SCL signals

tf

SCLn, SDAn

20 + 0.1Cb

300

ns

tSU;STO

SCLn, SDAn

0.6

—

μs

tBUF

SCLn, SDAn

1.3

—

μs

Capacitive load for each bus line

Cb

SCLn, SDAn

—

400

pF

Pulse width of spike suppressed by input

filter

tSP

SCLn, SDAn

0

(1..1.5)

tCLKP

ns

SCL clock frequency

Hold time (repeated) START

condition. After this period, the first clock

pulse is generated

Setup time for STOP condition

Bus free time between a STOP and

START condition

Remark

*1

*1 : The noise filter will suppress single spikes with a pulse width of 0ns and between (1 to 1.5) cycles of peripheral clock, depending

on the phase relationship between I2C signals (SDA, SCL) and peripheral clock.

Note:

tCLKP is the cycle time of the peripheral clock.

Document Number: 002-04631 Rev. *A

Page 110 of 137

�Document Number: 002-04631 Rev. *A

SCL

SDA

tHD;STA

tf

S

tr

tHD;DAT

tLOW

tHIGH

tSU;DAT

tSU;STA

Sr

tHD;STA

tSP

tr

P

tSU;STO

tBUF

S

tf

MB91460T Series

Page 111 of 137

�MB91460T Series

16.6.5 Free-run timer clock

Parameter

(VDD5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

Condition

tTIWH

tTIWL

CKn

—

Input pulse width

Value

Min

Max

4tCLKP

—

Unit

ns

Note : tCLKP is the cycle time of the peripheral clock.

CKn

tTIWH

tTIWL

16.6.6 Trigger input timing

Parameter

(VDD5 = 3.0 V to 5.5 V, VSS5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

Condition

tINP

ICUn

tATGX

ATGX

Input capture input trigger

A/D converter trigger

Value

Unit

Min

Max

—

5tCLKP

—

ns

—

5tCLKP

—

ns

Note : tCLKP is the cycle time of the peripheral clock.

tATGX, tINP

ICUn,

ATGX

Document Number: 002-04631 Rev. *A

Page 112 of 137

�MB91460T Series

16.6.7 External Bus AC Timings at VDD35 = 4.5 to 5.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD35 = 4.5 V to 5.5 V, Iload = 5 mA

- VSS5 = 0 V

- TA = 40°C to TA(max)

- Cl = 50 pF

- VOL = 0.2VDD35

- VOH = 0.8VDD35

- EPILR = 0, PILR = 1 (Automotive Level = worst case)

Basic Timing

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to Address valid delay time

Symbol

tCLCH

tCHCL

Pin name

SYSCLK

tCLCSL

tCLCSH

SYSCLK

CSXn

tCHCSL

tCLASL

tCLASH

SYSCLK

ASX

tCLAV

SYSCLK

A23 to A0

Value

Unit

Min

Max

1/2tCLKT - 7

1/2tCLKT + 7

ns

1/2tCLKT - 7

1/2tCLKT + 7

ns

—

9

ns

—

8

ns

5

+2

ns

—

8

ns

—

8

ns

—

11

ns

Note : tCLKT is the cycle time of the external bus clock.

Document Number: 002-04631 Rev. *A

Page 113 of 137

�MB91460T Series

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

Document Number: 002-04631 Rev. *A

Page 114 of 137

�MB91460T Series

Synchronous/Asynchronous read access

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin name

TCHRL

SYSCLK

RDX

TCHRH

Value

Unit

Min

Max

5

2

ns

5

2

ns

Data valid to RDX ↑ setup time

TDSRH

RDX

D31 to D16

20

—

ns

RDX ↑ to Data valid hold time

TRHDX

RDX

D31 to D16

0

—

ns

—

9

ns

1

—

ns

—

9

ns

—

8

ns

TCLWRL

SYSCLK ↓ to WRXn

(as byte enable) delay time

TCLWRH

TCLCSL

SYSCLK ↓ to CSXn delay time

SYSCLK

WRXn

SYSCLK

CSXn

TCLCSH

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

Document Number: 002-04631 Rev. *A

Page 115 of 137

�MB91460T Series

Synchronous write access - byte control type

Parameter

SYSCLK ↓ to WEX delay time

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

TCLWL

SYSCLK

WEX

TCLWH

Value

Unit

Min

Max

—

9

ns

2

—

ns

Data valid to WEX ↓ setup time

TDSWL

WEX

D31 to D16

11

—

ns

WEX ↑ to Data valid hold time

TWHDH

WEX

D31 to D16

tCLKT10

—

ns

SYSCLK ↓ to WRXn (as byte enable) delay

time

TCLWRL

—

9

ns

1

—

ns

—

9

ns

—

8

ns

SYSCLK ↓ to CSXn delay time

SYSCLK

WRXn

TCLWRH

TCLCSL

SYSCLK

CSXn

TCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 116 of 137

�MB91460T Series

Synchronous write access - no byte control type

Parameter

SYSCLK ↓ to WRXn delay time

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

TCLWRL

SYSCLK

WRXn

TCLWRH

Value

Unit

Min

Max

—

9

ns

1

—

ns

Data valid to WRXn ↓ setup time

TDSWRL

WRXn

D31 to D16

12

—

ns

WRXn ↑ to Data valid hold time

TWRHDH

WRXn

D31 to D16

tCLKT8

—

ns

—

9

ns

—

8

ns

SYSCLK ↓ to CSXn delay time

TCLCSL

TCLCSH

SYSCLK

CSXn

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 117 of 137

�MB91460T Series

Asynchronous write access - byte control type

Parameter

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

WEX ↓ to WEX ↑ pulse width

TWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT2

—

ns

TDSWL

WEX

D31 to D16

1/2tCLKT13

—

ns

TWHDH

WEX

D31 to D16

1/2tCLKT10

—

ns

—

1/2tCLKT + 2

ns

1/2tCLKT4

—

ns

—

1/2tCLKT

ns

1/2tCLKT5

—

ns

TWRLWL

TWHWRH

TCLWL

WEX

WRXn

WEX

CSXn

TWHCH

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 118 of 137

�MB91460T Series

Asynchronous write access - no byte control type

Parameter

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

WRXn ↓ to WRXn ↑ pulse width

TWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT1

—

ns

TDSWRL

WRXn

D31 to D16

1/2tCLKT14

—

ns

TWRHDH

WRXn

D31 to D16

1/2tCLKT7

—

ns

—

1/2tCLKT1

ns

1/2tCLKT3

—

ns

TCLWRL

WRXn

CSXn

TWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 119 of 137

�MB91460T Series

RDY waitcycle insertion

Parameter

(VDD35 = 4.5 V to 5.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

RDY setup time

TRDYS

RDY hold time

TRDYH

Value

Unit

Min

Max

SYSCLK

RDY

21

—

ns

SYSCLK

RDY

0

—

ns

SYSCLK

tRDYS

tRDYH

RDY

Document Number: 002-04631 Rev. *A

Page 120 of 137

�MB91460T Series

16.6.8 External Bus AC Timings at VDD35 = 3.0 to 4.5 V

• Conditions during AC measurements

All AC tests were measured under the following conditions:

- IOdrive = 5 mA

- VDD35 = 3.0 V to 4.5 V, Iload = 3 mA

- VSS5 = 0 V

- TA = 40°C to TA(max)

- Cl = 50 pF

- VOL = 0.2VDD35

- VOH = 0.8VDD35

- EPILR = 0, PILR = 1 (Automotive Level = worst case)

Basic Timing

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Parameter

SYSCLK

SYSCLK ↓ to CSXn delay time

SYSCLK ↑ to CSXn delay time

(Addr → CS delay)

SYSCLK ↓ to ASX delay time

SYSCLK ↓ to Address valid delay time

Document Number: 002-04631 Rev. *A

Symbol

TCLCH

TCHCL

Pin name

SYSCLK

TCLCSL

TCLCSH

SYSCLK

CSXn

TCHCSL

TCLASL

TCLASH

TCLAV

SYSCLK

ASX

SYSCLK

A23 to A0

Value

Unit

Min

Max

1/2tCLKT13

1/2tCLKT + 13

ns

1/2tCLKT13

1/2tCLKT + 13

ns

—

6

ns

—

7

ns

11

0

ns

—

6

ns

—

9

ns

—

13

ns

Page 121 of 137

�MB91460T Series

tCLCH

tCHCL

tCYC

SYSCLK

tCLCSL

tCLCSH

CSXn

tCHCSL

delayed CSXn

tCLASH

tCLASL

ASX

tCLAV

ADDRESS

Document Number: 002-04631 Rev. *A

Page 122 of 137

�MB91460T Series

Synchronous/Asynchronous read access

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Parameter

SYSCLK ↑ to RDX delay time

Symbol

Pin name

TCHRL

SYSCLK

RDX

TCHRH

Value

Unit

Min

Max

12

0

ns

9

1

ns

Data valid to RDX ↑ setup time

TDSRH

RDX

D31 to D16

29

—

ns

RDX ↑ to Data valid hold time

(internal SYSCLK → MCLKI /

/MCLKI feedback)

TRHDX

RDX

D31 to D16

0

—

ns

SYSCLK

WRXn

—

6

ns

0

—

ns

SYSCLK

CSXn

—

6

ns

—

7

ns

TCLWRL

SYSCLK ↓ to WRXn

(as byte enable) delay time

TCLWRH

TCLCSL

SYSCLK ↓ to CSXn delay time

TCLCSH

SYSCLK

tCLCSL

tCLCSH

CSXn

tCLWRL

tCLWRH

WRXn

(as byte enable)

tCHRH

tCHRL

RDX

tDSRH

tRHDX

DATA IN

Document Number: 002-04631 Rev. *A

Page 123 of 137

�MB91460T Series

Synchronous write access - byte control type

Parameter

SYSCLK ↓ to WEX delay time

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

TCLWL

SYSCLK

WEX

TCLWH

Value

Unit

Min

Max

—

7

ns

1

—

ns

Data valid to WEX ↓ setup time

TDSWL

WEX

D31 to D16

20

—

ns

WEX ↑ to Data valid hold time

TWHDH

WEX

D31 to D16

tCLKT19

—

ns

SYSCLK ↓ to WRXn (as byte enable) delay

time

TCLWRL

SYSCLK

WRXn

—

6

ns

0

—

ns

SYSCLK

CSXn

—

6

ns

—

7

ns

SYSCLK ↓ to CSXn delay time

TCLWRH

TCLCSL

TCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

(as byte enable)

tCLWH

tCLWL

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 124 of 137

�MB91460T Series

Synchronous write access - no byte control type

Parameter

SYSCLK ↓ to WRXn delay time

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

TCLWRL

SYSCLK

WRXn

TCLWRH

Value

Unit

Min

Max

—

6

ns

0

—

ns

Data valid to WRXn ↓ setup time

TDSWRL

WRXn

D31 to D16

20

—

ns

WRXn ↑ to Data valid hold time

TWRHDH

WRXn

D31 to D16

tCLKT14

—

ns

—

6

ns

—

7

ns

SYSCLK ↓ to CSXn delay time

TCLCSL

SYSCLK

CSXn

TCLCSH

SYSCLK

tCLCSH

tCLCSL

CSXn

tCLWRH

tCLWRL

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 125 of 137

�MB91460T Series

Asynchronous write access - byte control type

Parameter

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

WEX ↓ to WEX ↑ pulse width

TWLWH

Data valid to WEX ↓ setup time

WEX ↑ to Data valid hold time

WEX to WRXn delay time

WEX to CSXn delay time

Value

Unit

Min

Max

WEX

tCLKT2

—

ns

TDSWL

WEX

D31 to D16

1/2tCLKT20

—

ns

TWHDH

WEX

D31 to D16

1/2tCLKT20

—

ns

—

1/2tCLKT + 3

ns

1/2tCLKT7

—

ns

—

1/2tCLKT1

ns

1/2tCLKT4

—

ns

TWRLWL

WEX

WRXn

TWHWRH

TCLWL

WEX

CSXn

TWHCH

CSXn

tWHCH

tCLWL

WRXn

(as byte enable)

tWHWRH

tWRLWL

tWLWH

WEX

tDSWL

tWHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 126 of 137

�MB91460T Series

Asynchronous write access - no byte control type

Parameter

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

WRXn ↓ to WRXn ↑ pulse width

TWRLWRH

Data valid to WRXn ↓ setup time

WRXn ↑ to Data valid hold time

WRXn to CSXn delay time

Value

Unit

Min

Max

WRXn

tCLKT2

—

ns

TDSWRL

WRXn

D31 to D16

1/2tCLKT21

—

ns

TWRHDH

WRXn

D31 to D16

1/2tCLKT18

—

ns

—

1/2tCLKT1

ns

1/2tCLKT4

—

ns

TCLWRL

WRXn

CSXn

TWRHCH

CSXn

tWRHCH

tCLWRL

tWRLWRH

WRXn

tDSWRL

tWRHDH

DATA OUT

Document Number: 002-04631 Rev. *A

Page 127 of 137

�MB91460T Series

RDY waitcycle insertion

Parameter

(VDD35 = 3.0 V to 4.5 V, Vss5 = 0 V, TA = 40°C to TA(max))

Symbol

Pin name

RDY setup time

TRDYS

RDY hold time

TRDYH

Value

Unit

Min

Max

SYSCLK

RDY

37

—

ns

SYSCLK

RDY

0

—

ns

SYSCLK

tRDYS

tRDYH

RDY

Document Number: 002-04631 Rev. *A

Page 128 of 137

�MB91460T Series

17. Ordering Information

Part number

MB91F467TAPMC-GSE2

MB91F469TAPMC-GSE2 *

1

Package

144-pin plastic QFP

(FPT-144P-M08)

Maximum

ambient

temperature

TA(max)

+ 125°C

+ 105°C

Remarks

Lead-free package

* 1: This device is planned.

Document Number: 002-04631 Rev. *A

Page 129 of 137

�MB91460T Series

18. Package Dimension

144-pin plastic LQFP

(FPT-144P-M08)

144-pin plastic LQFP

(FPT-144P-M08)

0.50 mm

Package width ×

package length

20.0 × 20.0 mm

Lead shape

Gullwing

Sealing method

Plastic mold

Mounting height

1.70 mm MAX

Weight

1.20 g

Code

(Reference)

P-LFQFP144-20×20-0.50

Note 1) *:Values do not include resin protrusion.

Resin protrusion is +0.25(.010)Max(each side).

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

22.00±0.20(.866±.008)SQ

* 20.00±0.10(.787±.004)SQ

108

Lead pitch

0.145±0.055

(.006±.002)

73

109

72

0.08(.003)

Details of "A" part

+0.20

1.50 –0.10

+.008

.059 –.004

0°~8°

INDEX

144

37

"A"

LEAD No.

1

36

0.50(.020)

C

0.22±0.05

(.009±.002)

2003-2010 FUJITSU SEMICONDUCTOR LIMITED F144019S-c-4-8

Document Number: 002-04631 Rev. *A

0.08(.003)

0.50±0.20

(.020±.008)

0.60±0.15

(.024±.006)

(Mounting height)

0.10±0.10

(.004±.004)

(Stand off)

0.25(.010)

M

Dimensions in mm (inches).

Note: The values in parentheses are reference values.

Page 130 of 137

�MB91460T Series

19. Revision History

Version

Date

2.0

2008-09-02

2.1

2008-11-17

Remark

Initial version

Pinout re-drawn

Port Multiplexing: Chapter updated and pinout re-drawn

Chapter Memo and Disclaimer added

Notes on PS register: Updated for better readability

Embedded Program/Data Memory:

- Corrected Flash and Boot security vector addresses

- Added note about flash memory operation mode switching

- Added section Poweron Sequence in parallel programming mode

Flash Security:

- Corrected FSV2 table header

- Sector SA23 is available on F467TA

Absolute Maximum Ratings:

- corrected Relationship of the supply voltages (Remarks only)

- added maximal output currents

DC Characteristics:

- Added Analog input leakage current

- Corrected Pull-Up and Pull Down resistance

A/D converter characteristics

- added Offset between input channels

- updated drawings (regarding nonlinearity error)

Chapter Memo and Disclaimer added

2.2

2009-01-09

Flash Security: added Notes About Flash Memory CRC Calculation

F469T: DC characteristics: corrected the current consumption values ICC, ICCH

Version 1E

Page

6

2009-06-01

Section

Pin Assignment

1. MB91F467TA, MB91F469TA

Change Results

Corrected the pin name (No.38) in figure.

(P10_0/SYSCLK/SYSCLK P10_0/SYSCLK)

Corrected "Pin name" and "Function" of the pin no.10 in the table.

(A16, A17 A16

(bit16, bit17) (bit16)

8

Pin Description

1. MB91F467TA, MB91F469TA

PPG8, PPG9 PPG8)

Corrected "Pin name" and "Function" of the pin no.11 in the table.

(A16, A17 A17

(bit16, bit17) (bit17)

PPG8, PPG9 PPG9)

Corrected "Function" of the pin no.51 in the table.

(SG0 SGO)

11

26

Port Multiplexing

2. Multiplex Pinout MB91F467TA,

MB91F469TA

Corrected the pin name(No.38 and No.87 to No.89) in figure.

(VDD5R_2 VDD5R

VDD5R_1 VDD5R

VCC18C_1 VCC18C

P10_0/SYSCLK/SYSCLK P10_0/SYSCLK)

Document Number: 002-04631 Rev. *A

Page 131 of 137

�MB91460T Series

Version 1E

Page

30

2009-06-01

Section

Block Diagram

1. MB91F467TA, MB91F469TA

Change Results

Corrected the pin name in figure.

(SG0 SGO)

Corrected the table of MB91F467TA external pins.

(MD2 MD_2

43

Embedded Program/Data Memory

(Flash)

4.2. Pin connections in parallel

programming mode

44

MD1 MD_1

MD0 MD_0)

Corrected the table of MB91F469TA external pins.

(MD2 MD_2

MD1 MD_1

MD0 MD_0)

Deleted the line of "000080H" of the table.

53

71

99

I/O Map

1. MB91F467TA, MB91F469TA

Corrected "Block" in the table.

(Flash Memory/-Cache Control Register

Flash Memory/ F-Cache Control Register)

Electrical Characteristics

3. DC characteristics

Corrected "Condition" of Output “L” voltage.

(IOH IOL)

Corrected "Value" and "Unit" of Zero reading voltage.

(AVRL 1.5 AVRL 1.5 LSB

AVRL 0.5 AVRL 0.5 LSB

AVRL 2.5 AVRL 2.5 LSB

102

4. A/D converter characteristics

LSB V)

Corrected "Value" and "Unit" of Full scale reading voltage.

(AVRH 3.5 AVRH 3.5 LSB

AVRH 1.5 AVRH 1.5 LSB

AVRH 0.5 AVRH 0.5 LSB

LSB V)

109

6.3. LIN-USART Timings at VDD5 = 3.0 Corrected the sentences.

(- Ta = -40 to +105 °C - Ta = -40 to +105°C)

to 5.5 V

Internal clock mode (master mode)

110

111

External clock mode (slave mode)

6.4. I2C AC Timings at VDD5 = 3.0 to

5.5 V

112

Document Number: 002-04631 Rev. *A

Corrected the figure.

(VOH VIH

VOL VIL)

Corrected "Value" of Rise time of both SDA and SCL signals.

(20 + 0.1Cb 20 + 0.1Cb)

Corrected "Value" of Fall time of both SDA and SCL signals.

(20 + 0.1Cb 20 + 0.1Cb)

Corrected the position of figure.

Page 132 of 137

�MB91460T Series

Version 1E

Page

Section

115

6.7.1. Basic Timing

116

6.7.2. Synchronous/Asynchronous

read access

117

6.7.3. Synchronous write access - byte

control type

118

6.7.4. Synchronous write access - no

byte control type

121

6.7.7. RDY waitcycle insertion

123

6.8.1. Basic Timing

124

6.8.2. Synchronous/Asynchronous

read access

125

6.8.3. Synchronous write access - byte

control type

126

6.8.4. Synchronous write access - no

byte control type

129

6.8.7. RDY waitcycle insertion

Document Number: 002-04631 Rev. *A

2009-06-01

Change Results

Corrected "Pin name" in the figure.

(MCLKO SYSCLK)

Page 133 of 137

�MB91460T Series

20. Major Changes

Spansion Publication Number: DS705-00001-2v1-E

Version 2E

Page

2

Section

Features

Package and technology

2010-04-30

Changes for TA = 125°C

Introduced maximal ambient temperature TA(max),

defined in chapter ORDERING INFORMATON,

for parameters at TA=125°C

129

Ordering Information

6

Product Lineup,

Power Consumption

87

Recommended Settings

15.1 PLL and Clockgear settings

88

Recommended Settings

15.2 Clock Modulator settings

94

Electrical Characteristics

16.1 Absolute maximum ratings

Added permitted operating frequency and permitted power dissipation per

device, depending on TA(max) ; changed operating temperature to TA(max)

96

Electrical Characteristics

16.2 Recommended operating

conditions

Changed operating temperature to TA(max)

97

Electrical Characteristics

16.3 DC characteristics

Table head lines: Changed TA from 105°C to TA(max)

98

Electrical Characteristics

16.3 DC characteristics

Input leakage current, Analog input leakage current:

changed hi temp condition from 105°C to TA(max)

99

Electrical Characteristics

16.3 DC characteristics

Power supply current MB91F467TA:

Added ICCH values for TA=125°C

Added ICCH remark for 32kHz mode (same as RTC 100 kHz mode)

99

Electrical Characteristics

16.3 DC characteristics

Power supply current MB91F469TA (target data):

Added ICCH remark for 32kHz mode (same as RTC 100 kHz mode)

101

Electrical Characteristics

16.4 A/D converter characteristics

Table head lines: Changed TA from 105°C to TA(max)

106

Electrical Characteristics

16.6 AC characteristics

Table head lines and condition listings:

Changed max TA from 105°C to TA(max).

Version 2E

Page

Section

1

Front page note

6

Product Lineup

129

Ordering Information

Changed MB91F467T and MB91F469T from