Freescale Semiconductor

Data Sheet: Technical Data

Document Number: MC9S08SF4

Rev. 4, 9/2011

MC9S08SF4

MC9S08SF4 Series

Features

• 8-Bit S08 Central Processor Unit (CPU)

– Up to 40 MHz CPU at 2.7 V to 5.5 V across temperature

range of –40 C to 125 C

– HC08 instruction set with added BGND instruction

– Support for up to 32 interrupt/reset sources

• On-Chip Memory

– 4 KB flash read/program/erase over full operating

voltage and temperature

– 128-byte random-access memory (RAM)

– Security circuitry to prevent unauthorized access to

RAM and flash contents

• Power-Saving Modes

– Two low power stop modes; reduced power wait mode

– Allows clocks to remain enabled to specific peripherals

in stop3 mode

• Clock Source Options

– Internal Clock Source (ICS) — Internal clock source

module containing a frequency-locked-loop (FLL)

controlled by an internal or external reference; precision

trimming of internal reference allows 0.2% resolution

and 1% deviation over 0–70 C and voltage, 2%

deviation over –40–85 C and voltage, or 3% deviation

over –40–125 C and voltage; supporting bus

frequencies up to 20 MHz

• System Protection

– Watchdog computer operating properly (COP) reset

with option to run from dedicated 1 kHz internal clock

source or bus clock

– Low-voltage detection with reset or interrupt; selectable

trip points

– Illegal opcode detection with reset

– Illegal address detection with reset

– Flash block protection

• Development Support

– Single-wire background debug interface

– Breakpoint capability to allow single breakpoint setting

during in-circuit debugging (plus two more breakpoints)

– On-chip in-circuit emulator (ICE) debug module

containing two comparators and nine trigger modes

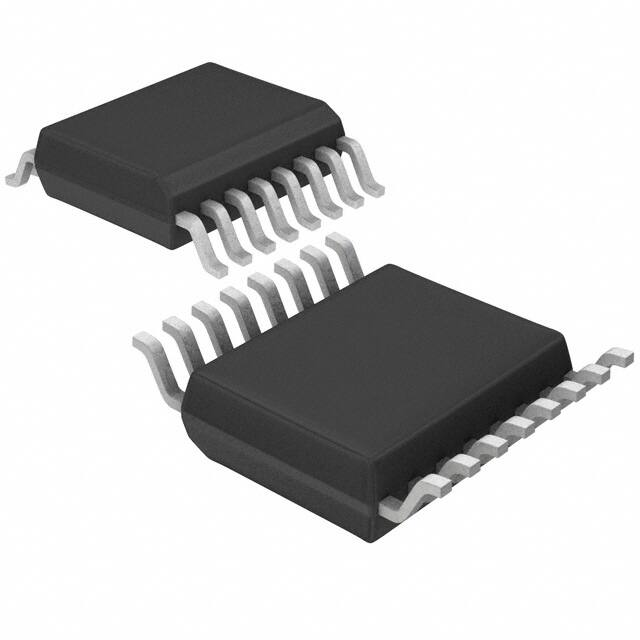

20-Pin TSSOP

Case 948E

• Peripherals

– IPC — Prioritize interrupt sources besides inherent

CPU interrupt table; support up to 32 interrupt sources

and up to 4-level preemptive interrupt nesting

– ADC — 8-channel, 10-bit resolution; 2.5 s conversion

time; automatic compare function; temperature sensor;

internal bandgap reference channel; operation in stop;

fully functional from 2.7 V to 5.5 V

– TPM — One 40 MHz 6-channel and one 40 MHz

1-channel timer/pulse-width modulators (TPM)

modules; selectable input capture, output compare, or

buffered edge- or center-aligned PWM on each channel

– MTIM16 — Two 16-bit modulo timers

– PWT — Two 16-bit pulse width timers (PWT);

selectable driving clock, positive/negative/period

capture

– PRACMP — Two programmable reference analog

comparators with eight optional inputs for both positive

and negative inputs; 32-level internal reference voltages

scaled by selectable reference inputs

– IIC — Inter-integrated circuit bus module capable of

operation up to 100 kbps with maximum bus loading;

multi-master operation; programmable slave address;

interrupt-driven byte-by-byte data transfer; broadcast

mode; 10-bit addressing

– KBI — 4-pin keyboard interrupt module with software

selectable polarity on edge or edge/level modes

– FDS — Shut down output pin upon fault detection; the

fault sources can be optional enabled separately; the

output pin can be configured as output 1,0 and high

impedance when a fault occurs based on module

configuration

• Input/Output

– 18 GPIOs including one input-only pin and one

output-only pin

– Hysteresis and configurable pullup device on all input

pins; schmitt trigger on PWT input pins; configurable

slew rate and drive strength on all output pins.

• Package Options

– 16-pin TSSOP

– 20-pin TSSOP

This document contains information on a product under development. Freescale reserves the

right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2009-2011. All rights reserved.

16-Pin TSSOP

Case 948F

�Table of Contents

1

2

3

MCU Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.2 Parameter Classification . . . . . . . . . . . . . . . . . . . 5

3.3 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . 5

3.4 Thermal Characteristics. . . . . . . . . . . . . . . . . . . . 6

3.5 ESD Protection and Latch-Up Immunity . . . . . . . 7

3.6 DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . 8

3.7 Supply Current Characteristics . . . . . . . . . . . . . 14

3.8 ICS Characteristics . . . . . . . . . . . . . . . . . . . . . . 16

3.9 AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . 17

3.9.1 Control Timing . . . . . . . . . . . . . . . . . . . . . 18

3.9.2 Timer/PWM (TPM) Module Timing . . . . . 19

3.10 ADC Characteristics . . . . . . . . . . . . . . . . . . . . . 20

4

5

3.11 PRACMP Characteristics . . . . . . . . . . . . . . . . . .21

3.12 Flash Specifications . . . . . . . . . . . . . . . . . . . . . .22

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . .23

Package Information . . . . . . . . . . . . . . . . . . . . . . . . . .23

5.1 Mechanical Drawings . . . . . . . . . . . . . . . . . . . . .23

Revision History

The following revision history table summarizes changes contained in this document.

Revision

Date

Description of Changes

2

4/30/2009

Initial public release.

3

8/18/2009

Polished.

4

9/19/2011

Updated VAIN in the Table 12.

Related Documentation

Reference Manual

(MC9S08SF4RM)

Contains extensive product information including modes of operation, memory,

resets and interrupts, register definition, port pins, CPU, and all module information.

MC9S08SF4 Series MCU Data Sheet, Rev. 4

2

Freescale Semiconductor

�1

MCU Block Diagram

The block diagram, Figure 1, shows the structure of the MC9S08SF4 MCU.

DEBUG MODULE

(DBG)

16-BIT MODULO TIMER

INTERRUPT PRIORITY

CONTROLLER (IPC)

TCLK

PTA0/KBI0/TCLK/IRQ

(MTIM16-1)

PTA1/KBI1/RESET

16-BIT MODULO TIMER

BDC

IRQ

WAKEUP

LVD

RESET

MODULE (TPM1)

FAULT DETECTION

& SHUTDOWN (FDS)

MODULE (TPM2)

PULSE WIDTH TIMER

(PWT1)

USER RAM

128 BYTES

PTA6/TPM1C4/FDSOUT4

FDSOUT[6:0]

PWTI1

TCLK

PWTI2

(PWT2)

TCLK

ANALOG COMPARATOR

(PRACMP2)

VDD

PTB0/TPM2C0/FDSOUT6

PTB1/PWTI1/ADC0

TPM2C0

TCLK

PULSE WIDTH TIMER

ANALOG COMPARATOR

(PRACMP1)

40 MHz INTERNAL CLOCK

SOURCE (ICS)

PTA4/TPM1C2/FDSOUT2

PTA7/TPM1C5/FDSOUT5

1-CH TIMER/PWM

PTB2/PWTI2/ADC1

PTB3/ACMP3/ADC2

PTB4/ACMP2/ADC3

PTB5/ACMP1/ADC4

ACMP3

ACMP2

ACMP1

ACMP0

ACMP3

ACMP2

ACMP1

ACMP0

PTB6/ACMP0/ADC5

PTB7/BKGD/MS

VOLTAGE REGULATOR

8-CH 10-BIT

ANALOG-TO-DIGITAL

CONVERTER(ADC)

INTER-INTERGRATED

CIRCUIT (IIC)

ADP[5:0]

ADP[6:7]

SCL

SDA

PORT C

VSS

TCLK

IRQ

USER Flash

4096 BYTES

PTA3/KBI3/TPM1C1/FDSOUT1

PTA5/TPM1C3/FDSOUT3

TPM1C[5:0]

PORT B

COP

KBI[3:0]

INTERRUPT (KBI)

6-CH TIMER/PWM

HCS08 SYSTEM CONTROL

RESETS AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

PTA2/KBI2/TPM1C0/FDSOUT0

PORT A

4-PIN KEYBOARD

CPU

TCLK

(MTIM16-2)

HCS08 CORE

PTC0/ADC6/SCL

PTC1/ADC7/SDA

= Not available in the 16-pin TSSOP package

Figure 1. MC9S08SF4 Series Block Diagram

2

Pin Assignments

This section shows the pin assignments for the MC9S08SF4 series devices.

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

3

�VDD

PTA0/KBI0/TCLK/IRQ

PTA1/KBI1/RESET

PTA2/KBI2/TPM1C0/FDSOUT0

PTA3/KBI3/TPM1C1/FDSOUT1

PTA4/TPM1C2/FDSOUT2

PTA5/TPM1C3/FDSOUT3

PTA6/TPM1C4/FDSOUT4

PTA7/TPM1C5/FDSOUT5

PTB0/TPM2C0/FDSOUT6

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

VSS

PTC1/SDA/ADC7

PTC0/SCL/ADC6

PTB7/BKGD/MS

PTB6/ACMP0/ADC5

PTB5/ACMP1/ADC4

PTB4/ACMP2/ADC3

PTB3/ACMP3/ADC2

PTB2/PWTI2/ADC1

PTB1/PWTI1/ADC0

Figure 2. MC9S08SF4 in 20-Pin TSSOP Package

VDD

PTA0/KBI0/TCLK/IRQ

PTA1/KBI1/RESET

PTA2/KBI2/TPM1C0/FDSOUT0

PTA3/KBI3/TPM1C1/FDSOUT1

PTA4/TPM1C2/FDSOUT2

PTA5/TPM1C3/FDSOUT3

PTB0/TPM2C0/FDSOUT6

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

VSS

PTB7/BKGD/MS

PTB6/ACMP0/ADC5

PTB5/ACMP1/ADC4

PTB4/ACMP2/ADC3

PTB3/ACMP3/ADC2

PTB2/PWTI2/ADC1

PTB1/PWTI1/ADC0

Figure 3. MC9S08SF4 in 16-Pin TSSOP Package

MC9S08SF4 Series MCU Data Sheet, Rev. 4

4

Freescale Semiconductor

�Introduction

3

Electrical Characteristics

3.1

Introduction

This section contains electrical and timing specifications for the MC9S08SF4 series of microcontrollers

available at the time of publication.

3.2

Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the

customer a better understanding the following classification is used and the parameters are tagged

accordingly in the tables where appropriate:

Table 1. Parameter Classifications

P

Those parameters are guaranteed during production testing on each individual device.

C

Those parameters are achieved by the design characterization by measuring a statistically relevant

sample size across process variations.

T

Those parameters are achieved by design characterization on a small sample size from typical devices

under typical conditions unless otherwise noted. All values shown in the typical column are within this

category.

D

Those parameters are derived mainly from simulations.

NOTE

The classification is shown in the column labeled “C” in the parameter

tables where appropriate.

3.3

Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not

guaranteed. Stress beyond the limits specified in Table 2 may affect device reliability or cause permanent

damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields;

however, it is advised that normal precautions be taken to avoid application of any voltages higher than

maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused

inputs are tied to an appropriate logic voltage level (for instance, either VSS or VDD) or the programmable

pullup resistor associated with the pin is enabled.

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

5

�Thermal Characteristics

Table 2. Absolute Maximum Ratings

Rating

Symbol

Value

Unit

Supply voltage

VDD

–0.3 to 5.8

V

Maximum current into VDD

IDD

120

mA

Digital input voltage

VIn

–0.3 to VDD + 0.3

V

Instantaneous maximum current

Single pin limit (applies to all port pins)1, 2, 3

ID

25

mA

Tstg

–55 to 150

C

Storage temperature range

1

Input must be current limited to the value specified. To determine the value of the required

current-limiting resistor, calculate resistance values for positive (VDD) and negative (VSS) clamp

voltages, then use the larger of the two resistance values.

2

All functional non-supply pins are internally clamped to VSS and VDD.

3 Power supply must maintain regulation within operating V

DD range during instantaneous and

operating maximum current conditions. If positive injection current (VIn > VDD) is greater than

IDD, the injection current may flow out of VDD and could result in the external power supply going

out of regulation. Ensure external VDD load shunts current greater than the maximum injection

current. This will be the greatest risk when the MCU is not consuming power. Examples are: if

no system clock is present, or if the clock rate is very low (which would reduce overall power

consumption).

3.4

Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package

thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in

on-chip logic and voltage regulator circuits and it is user-determined rather than being controlled by the

MCU design. To take PI/O into account in power calculations, determine the difference between actual pin

voltage and VSS or VDD and multiply by the pin current for each I/O pin. Except in cases of unusually high

pin current (heavy loads), the difference between pin voltage and VSS or VDD will be small.

Table 3. Thermal Characteristics

Rating

Symbol

Value

Unit

Operating temperature range

(packaged)

TA

TL to TH

–40 to 125

C

Thermal resistance (single-layer board)

20-pin TSSOP

16-pin TSSOP

JA

115

123

C/W

Thermal resistance (four-layer board)

20-pin TSSOP

16-pin TSSOP

JA

76

75

C/W

The average chip-junction temperature (TJ) in C can be obtained from:

TJ = TA + (PD JA)

Eqn. 1

MC9S08SF4 Series MCU Data Sheet, Rev. 4

6

Freescale Semiconductor

�ESD Protection and Latch-Up Immunity

Where:

TA = Ambient temperature, C

JA = Package thermal resistance, junction-to-ambient, C/W

PD = Pint PI/O

Pint = IDD VDD, Watts — chip internal power

PI/O = Power dissipation on input and output pins — user determined

For most applications, PI/O Pint and can be neglected. An approximate relationship between PD and TJ

(if PI/O is neglected) is:

PD = K (TJ + 273C)

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

K = PD (TA + 273C) + JA (PD)2

Eqn. 3

Where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring

PD (at equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by

solving Equation 1 and Equation 2 iteratively for any value of TA.

3.5

ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early

CMOS circuits, normal handling precautions must be used to avoid exposure to static discharge.

Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels

of static without suffering any permanent damage.

During the device qualification ESD stresses were performed for the human body model (HBM) and the

charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device

specification. Complete DC parametric and functional testing is performed per the applicable device

specification at room temperature followed by hot temperature, unless specified otherwise in the device

specification.

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

7

�DC Characteristics

Table 4. ESD and Latch-up Test Conditions

Model

Human

Body

Description

Symbol

Value

Unit

Series resistance

R1

1500

Storage capacitance

C

100

pF

Number of pulses per pin

—

1

Minimum input voltage limit

—

–2.5

V

Maximum input voltage limit

—

7.5

V

Latch-up

Table 5. ESD and Latch-Up Protection Characteristics

No.

1

3.6

Rating1

Symbol

Min

Max

Unit

1

Human body model (HBM)

VHBM

2000

—

V

2

Charge device model (CDM)

VCDM

500

—

V

3

Latch-up current at TA = 125 C

ILAT

100

—

mA

Parameter is achieved by design characterization on a small sample size from typical devices

under typical conditions unless otherwise noted.

DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

Table 6. DC Characteristics (Temperature Range = –40 to 125 C Ambient)

Num

C

Symbol

Min

Typical

Max

Unit

1

P

Supply voltage (run, wait, and stop modes.)

VDD

2.7

—

5.5

V

P

Low-voltage detection threshold — high range

(VDD falling)

(VDD rising)

VLVDH

3.9

4.0

—

—

4.1

4.2

V

V

P

Low-voltage detection threshold — low range

(VDD falling)

(VDD rising)

VLVDL

2.48

2.54

2.56

2.62

2.64

2.7

V

V

P

Low-voltage warning threshold — high range

(VDD falling)

(VDD rising)

VLVWH

2.66

2.72

—

—

2.82

2.88

V

V

P

Low-voltage warning threshold — low range

(VDD falling)

(VDD rising)

VLVWL

2.84

2.90

—

—

3.00

3.06

V

V

4

D

Low-voltage inhibit reset/recover hysteresis

5V

3V

Vhys

—

—

100

60

—

—

mV

mV

5

P

Bandgap voltage reference

Factory trimmed at VDD = 3.0 V, Temp = 25 C

VBG

1.185

1.200

1.215

V

6

P

Input high voltage (2.7 V VDD 5.5 V) (all

digital inputs)

VIH

0.65 × VDD

—

VDD + 0.3

V

2

3

Parameter

MC9S08SF4 Series MCU Data Sheet, Rev. 4

8

Freescale Semiconductor

�DC Characteristics

Table 6. DC Characteristics (Temperature Range = –40 to 125 C Ambient) (continued)

Num

C

7

P

8

9

Parameter

Symbol

Min

Typical

Max

Unit

Input low voltage (2.7 V VDD 5.5 V) (all

digital inputs)

VIL

VSS – 0.3

—

0.35 × VDD

V

D

Input hysteresis (all digital inputs)

Vhys

0.06 × VDD

—

0.30 × VDD

V

P

Input Leakage Current (pins in high ohmic

input mode)1

or V

V =V

Iin

–1

—

A

P

Internal pullup resistors2

RPU

17.5

40.0

52.5

k

P

Internal pulldown resistor (IRQ)

RPD

12.5

—

62.5

k

C

Output high voltage All I/O pins, low-drive

strength, 5 V, Iload = –4 mA

VDD – 1.5

—

—

V

P

Output high voltage All I/O pins, low-drive

strength, 5 V, Iload = –2 mA

VDD – 0.8

—

—

V

C

Output high voltage All I/O pins, low-drive

strength, 3 V, Iload = –1 mA

VDD – 0.8

—

—

V

VDD – 1.5

—

—

V

in

10

11

DD5

SS5

V

OH

C

Output high voltage All I/O pins, high-drive

strength, 5 V, Iload = –15 mA

P

Output high voltage All I/O pins, high-drive

strength, 5 V, Iload = –10 mA

VDD – 0.8

—

—

V

C

Output high voltage All I/O pins, high-drive

strength, 3 V, Iload = –5 mA

VDD – 0.8

—

—

V

C

Output low voltage All I/O pins, low-drive

strength, 5 V, Iload = 4 mA

—

—

1.5

V

P

Output low voltage All I/O pins, low-drive

strength, 5 V, Iload = 2 mA

—

—

0.8

V

C

Output low voltage All I/O pins, low-drive

strength, 3 V, Iload = 1 mA

—

—

0.8

V

C

Output low voltage All I/O pins, high-drive

strength, 5 V, Iload = 15 mA

—

—

1.5

V

P

Output low voltage All I/O pins, high-drive

strength, 5 V, Iload = 10 mA

—

—

0.8

V

C

Output low voltage All I/O pins, high-drive

strength, 3 V, Iload = 5 mA

—

—

0.8

V

12

V

OL

Maximum total IOH for all port pins

D

13

5V

3V

|IOHT|

—

—

—

—

100

60

mA

5V

3V

|IOLT|

—

—

—

—

100

60

mA

—

—

—

—

0.2

5

mA

mA

—

—

7

pF

Maximum total IOL for all port pins

D

14

D

dc injection current2, 3, 4, 5

VIN < VSS, VIN > VDD

Single pin limit

Total MCU limit, includes sum of all stressed

pins

15

D

Input capacitance (all non-supply pins)

|IIC|

CIn

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

9

�DC Characteristics

1

2

3

4

5

Maximum leakage current occurs at a maximum operating temperature. The current decreases by approximately one-half for

each 8 C to 12 C in the temperature range from 50 C to 125 C.

Measurement condition for pull resistors: VIn = VSS for pullup and VIn = VDD for pulldown.

All functional non-supply pins are internally clamped to VSS and VDD.

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate

resistance values for positive and negative clamp voltages, then use the larger of the two values.

Power supply must maintain regulation within operating VDD range during instantaneous and operating maximum current

conditions. If positive injection current (VIn > VDD) is greater than IDD, the injection current may flow out of VDD and could result

in external power supply going out of regulation. Ensure external VDD load shunts current greater than maximum injection

current. This is the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the

clock rate is very low (which reduces overall power consumption).

Typical Low-Side Driver (LDS) Characteristics

VDD = 5 V, PORTA, VOL Vs IOL

6

5

T=-40C

V OL(V)

4

T=0C

T=25C

3

T=85C

T=105C

2

T=125C

1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

IOL(mA)

Figure 4. Typical Low-Side Driver (Sink) Characteristics

Low Drive (PTxDSn = 0), VDD = 5.0 V, VOL vs. IOL

MC9S08SF4 Series MCU Data Sheet, Rev. 4

10

Freescale Semiconductor

�DC Characteristics

Typical Low-Side Driver (LDS) Characteristics

VDD = 3 V, PORTA, VOL Vs IOL

3.5

3

T=-40C

V OL(V)

2.5

T=0C

2

T=25C

T=85C

1.5

T=105C

1

T=125C

0.5

0

1

2

3

4

5

IOL(mA)

Figure 5. Typical Low-Side Driver (Sink) Characteristics

Low Drive (PTxDSn = 0), VDD = 3.0 V, VOL vs. IOL

Typical Low-Side Driver (HDS) Characteristics

VDD = 5 V, PORTA, VOL Vs IOL

1.20

1.00

T=-40C

V OL(V)

0.80

T=0C

T=25C

0.60

T=85C

T=105C

0.40

T=125C

0.20

0.00

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

IOL(mA)

Figure 6. Typical Low-Side Driver (Sink) Characteristics

High Drive (PTxDSn = 1), VDD = 5.0 V, VOL vs. IOL

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

11

�DC Characteristics

Typical Low-Side Driver (HDS) Characteristics

VDD = 3 V, PORTA, VOL Vs IOL

1.8

V OL(V)

1.6

1.4

T=-40C

1.2

T=0C

1

T=25C

0.8

T=85C

0.6

T=85

0.4

T=125C

0.2

0

1

2

3

4

5

6

7

8

9

10

11

12

13

IOL(mA)

Figure 7. Typical Low-Side Driver (Sink) Characteristics

High Drive (PTxDSn = 1), VDD = 3.0 V, VOL vs. IOL

Typical High-Side Driver (LDS) Characteristics

VDD = 5 V, PORTA, VOH Vs IOH

6.00

5.00

T=-40C

V OH(V)

4.00

T=0C

T=25C

3.00

T=85C

T=105C

2.00

T=125C

1.00

0.00

0

-1

-2

-3

-4

-5

-6

-7

-8

-9

IOH(mA)

Figure 8. Typical High-Side Driver (Source) Characteristics

Low Drive (PTxDSn = 0), VDD = 5.0 V, VOH vs. IOH

MC9S08SF4 Series MCU Data Sheet, Rev. 4

12

Freescale Semiconductor

�DC Characteristics

Typical High-Side Driver (LDS) Characteristics

VDD = 3 V, PORTA, VOH Vs IOH

3.5

3

T=-40C

V OH(V)

2.5

T=0C

2

T=25C

T=85C

1.5

T=105C

1

T=125C

0.5

0

0

-1

-2

-3

IOH(mA)

Figure 9. Typical High-Side Driver (Source) Characteristics

Low Drive (PTxDSn = 0), VDD = 3.0 V, VOH vs. IOH

Typical High-Side Driver (HDS) Characteristics

VDD = 5 V, PORTA, VOH Vs IOH

5.20

5.00

V OH(V)

4.80

4.60

T=-40C

4.40

T=0C

4.20

T=25C

4.00

T=85C

3.80

T=105C

3.60

T=125C

3.40

3.20

3.00

0

-1

-2

-3

-4

-5

-6

-7

-8

-9

-10

-11

-12

-13

-14

-15

-16

-17

-18

-19

-20

IOH(mA)

Figure 10. Typical High-Side Driver (Source) Characteristics

High Drive (PTxDSn = 1), VDD = 5.0 V, VOH vs. IOH

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

13

�Supply Current Characteristics

Typical High-Side Driver (HDS) Characteristics

VDD = 3 V, PORTA, VOH Vs IOH

3.5

3

T=-40C

V OH(V)

2.5

T=0C

2

T=25C

1.5

T=85C

T=105C

1

T=125C

0.5

0

0

-1

-2

-3

-4

-5

-6

-7

-8

-9

-10

-11

-12 -13

-14

-15

IOH(mA)

Figure 11. Typical High-Side Driver (Source) Characteristics

High Drive (PTxDSn = 1), VDD = 3.0 V, VOH vs. IOH

3.7

Supply Current Characteristics

This section includes information about power supply current in various operating modes.

Table 7. Supply Current Characteristics

Num

1

2

3

4

5

6

C

P

Parameter

Symbol

Run supply current3 measured at

(CPU clock = 2 MHz, fBus = 1 MHz)

RIDD

Run supply current3 measured at

(CPU clock = 16 MHz, fBus = 8 MHz)

RIDD

Run mode supply current3 measured at

(CPU clock = 40 MHz, fBus = 20 MHz)

RIDD

Wait mode supply current4 measured at

(fBus = 8 MHz)

WIDD

D

Wait mode supply current4 measured at

( fBus = 20 MHz)

WIDD

P

Stop2 mode supply current

D

P

D

P

D

P

D

P

P

D

D

–40 to 85 C

–40 to 125 C

–40 to 85C

–40 to 125C

VDD (V)

Typical1

Max2

5

1.75

1.77

3

1.71

1.73

5

5.69

6.25

3

4.63

4.66

5

11.53

12.00

3

10.39

11.00

5

3.95

4.54

3

3.58

4.00

5

8.36

9.62

3

7.97

8.07

5

1.99

18.47

100

S2IDD

3

1.95

Unit

mA

mA

mA

mA

mA

A

16.9

90

MC9S08SF4 Series MCU Data Sheet, Rev. 4

14

Freescale Semiconductor

�Supply Current Characteristics

Table 7. Supply Current Characteristics (continued)

Num

C

P

7

Parameter

–40 to 85 C

–40 to 125 C

P

–40 to 85 C

–40 to 125 C

D

9

10

11

12

13

14

15

16

17

18

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

VDD (V)

Typical1

Max2

5

2

18.4

Unit

Stop3 mode supply current

D

8

Symbol

100

S3IDD

PRACMP (PRG disabled) adder to stop3,

25 C

—

PRACMP (PRG enabled) adder to stop3,

25 C

—

ADC adder to stop2 or stop3, 25 C

—

LVD adder to stop3 (LVDE = LVDSE = 1)

—

Adder to stop3 for oscillator enabled

(IREFSTEN = 1)

—

TPM1 and TPM2 adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

PWT1 and PWT2 adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

PRACMP adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

MTIM1 and MTIM2 adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

ADC adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

IIC adder to run mode, 25 C

(CPU clock = 40 MHz, fBus = 20 MHz)

—

A

16.82

3

1.97

5

28.87

—

nA

3

27.06

—

nA

5

79.42

—

nA

3

57.4

—

nA

5

25

—

nA

3

6

—

nA

5

83.52

—

nA

3

83.52

—

nA

5

0.03

—

A

3

0.01

—

A

5

0.16

—

mA

3

0.18

—

mA

5

0.43

—

mA

3

0.41

—

mA

5

0.35

—

mA

3

0.35

—

mA

5

0.26

—

mA

3

0.24

—

mA

5

0.42

—

mA

3

0.32

—

mA

5

0.56

—

mA

3

0.53

—

mA

90

Typicals are measured at 25 C.

Values given here are preliminary estimates prior to completing characterization.

3 All modules except ADC active, and does not include any dc loads on port pins.

4 Most customers are expected to find that the auto-wakeup from a stop mode can be used instead of the higher current wait mode.

1

2

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

15

�ICS Characteristics

Typical RIDD (VDD = 5 V, ADC off) Vs Bus Frequency

12.0000

10.0000

T=-40C

T=0C

T=25C

T=85C

T=125C

mA

8.0000

6.0000

4.0000

2.0000

0.0000

1

4

8

20

Bus Frequency

Figure 12. Typical Run IDD vs. Bus Freq. (FEI) (ADC off)

3.8

ICS Characteristics

Refer to Figure 13 for crystal or resonator circuits.

Table 8. ICS Specifications (Temperature Range = –40 to 125 C Ambient )

No.

C

Characteristic

Symbol

Minimum Typical1 Maximum

Unit

1

T Internal reference start-up time

tIRST

—

60

100

s

2

P Average internal reference frequency — trimmed

fint_t

—

39.0625

—

kHz

P DCO output frequency

range — trimmed

P

fdco_t

16

—

20

3

32

—

40

–1.0 to 0.5

3

–1.0 to 0.5

2

0.5

Low range (DRS = 00)

Middle range (DRS = 10)

4

Total deviation of DCO output from trimmed

2

P frequency

Over full voltage and temperature range of –40 C

to 125 C

5

Total deviation of DCO output from trimmed

frequency

D

Over full voltage and temperature range of –40 C

to 85 C

6

Total deviation of DCO output from trimmed

frequency

D

Over fixed voltage and temperature range of 0 to

70 C

7

C FLL acquisition time2,3

8

C

Long term jitter of DCO output clock (averaged

over a 2 ms interval) 4

fdco_t

MHz

—

%fdco

tAcquire

—

—

1

ms

CJitter

—

0.02

0.2

%fdco

MC9S08SF4 Series MCU Data Sheet, Rev. 4

16

Freescale Semiconductor

�AC Characteristics

Data in the Typical column was characterized at 5.0 V, 25 C, or the typical recommended value.

This parameter is characterized and not tested on each device.

3

This specification applies to any time the FLL reference source or reference divider is changed, trim value changed,

DMX32 bit changed, DRS bit changed, or changing from FLL disabled (FBELP, FBILP) to FLL enabled (FEI, FEE, FBE,

and FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

4 Jitter is the average deviation from the programmed frequency measured over the specified interval at the maximum

fBus. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal.

Noise injected into the FLL circuitry via VDD and VSS and a variation in the crystal oscillator frequency increases the

CJitter percentage for a given interval.

1

2

1.00%

0.50%

Deviation (%)

0.00%

-60

-40

-20

0

20

40

60

80

100

120

-0.50%

-1.00%

TBD

-1.50%

-2.00%

Temperature

Figure 13. Deviation of DCO Output from Trimmed Frequency (20 MHz, 5.0 V)

3.9

AC Characteristics

This section describes AC timing characteristics for each peripheral system.

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

17

�AC Characteristics

3.9.1

Control Timing

Table 9. Control Timing

Symbol

Minimum

Typical1

Maximum

Unit

fBus

1

—

20

MHz

textrst

100

—

—

ns

IRQ pulse width

Asynchronous path2

Synchronous path3

tILIH, tIHIL

100

1.5 tcyc

—

—

ns

KBIPx pulse width

Asynchronous path2

Synchronous path3

tILIH, tIHIL

100

1.5 tcyc

—

—

ns

tRise, tFall

—

—

3

30

—

—

ns

BKGD/MS setup time after issuing background debug force

reset to enter user or BDM modes

tMSSU

500

—

—

ns

BKGD/MS hold time after issuing background debug force

reset to enter user or BDM modes 5

tMSH

100

—

—

s

Parameter

Bus frequency (tcyc = 1/fBus)

2

External reset pulse width

Port rise and fall time (load = 50 pF)4

Slew rate control disabled (PTxSE = 0)

Slew rate control enabled (PTxSE = 1)

Data in Typical column was characterized at 5.0 V, 25 C.

This is the shortest pulse that is guaranteed to be recognized.

3 This is the minimum pulse width that is guaranteed to pass through the pin synchronization circuitry. Shorter pulses may or

may not be recognized. In stop mode, the synchronizer is bypassed so shorter pulses can be recognized in that case.

4 Timing is shown with respect to 20% V

DD and 80% VDD levels. Temperature range –40 C to 125 C.

5 To enter BDM mode following a POR, BKGD/MS should be held low during the power-up and for a hold time of t

MSH after VDD

rises above VLVD.

1

2

textrst

RESET PIN

Figure 14. Reset Timing

tIHIL

IRQ/KBIPx

IRQ/KBIPx

tILIH

Figure 15. IRQ/KBIPx Timing

MC9S08SF4 Series MCU Data Sheet, Rev. 4

18

Freescale Semiconductor

�AC Characteristics

3.9.2

Timer/PWM (TPM) Module Timing

Synchronizer circuits determine the shortest input pulses that can be recognized or the fastest clock that

can be used as the optional external source to the timer counter. These synchronizers operate from the

current bus rate clock.

Table 10. TPM/MTIM Input Timing

Function

Symbol

Min

Max

Unit

External clock frequency

fTCLK

dc

ftimer/4

MHz

External clock period

tTCLK

4

—

tcyc

External clock high time

tclkh

1.5

—

tcyc

External clock low time

tclkl

1.5

—

tcyc

Input capture pulse width for TPM

tICPW

1.5

—

tcyc

Timer clock frequency

ftimer

—

40

MHz

tText

tclkh

TCLK

tclkl

Figure 16. Timer External Clock

tICPW

TPMCHn

TPMCHn

tICPW

Figure 17. Timer Input Capture Pulse

MC9S08SF4 Series MCU Data Sheet, Rev. 4

Freescale Semiconductor

19

�ADC Characteristics

3.10

ADC Characteristics

Table 11. ADC Characteristics

Num

C

D

1

D

D

2

D

D

3

D

Supply current

ADLPC = 1

ADLSMP = 0

ADCO = 1

Supply current

ADLPC = 0

ADLSMP = 1

ADCO = 1

VDDA 3.6 V

(3.0 V Typ)

VDDA 5.5 V

(5.0 V Typ)

VDDA 3.6 V

(3.0 V Typ)

VDDA 5.5 V

(5.0 V Typ)

VDDA 3.6 V

(3.0 V Typ)

VDDA 5.5 V

(5.0 V Typ)

VDDA 3.6V

(3.0 V Typ)

Min

Typical1

Max

—

110

—

—

130

—

—

200

—

—

220

—

—

320

—

—

360

—

—

580

—

—

660

—

IDDA

—