DATASHEET

6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK

WITH 66.66M DDR CLOCK

General Description

The 6V49205A is a main clock for Freescale P10xx and

P20xx-based systems. It has a selectable System CCB

clock and a 66.66MHz DDRCLK. The 6V49205A also

provides LP-HCSL PCIe outputs for low power and reduced

board space.

Output Features

System Clock for Freescale P10xx and P20xx-based

designs

Features

• Replaces 11 crystals, 2 oscillators and 3 clock

generators; lowers cost, power and area

• Integrated terminations on LP-HCSL PCIe outputs;

• 1 - Sys_CCB 3.3V LVCMOS output at 100M/83.33M/

•

•

•

•

•

•

Recommended Application

80M/66.66M

1 - DDRCLK 3.3V LVCMOS output at 66.66M

1 - 125M 3.3V LVCMOS output

6 - LP-HCSL PCIe pairs selectable at 100M or 125M

6 - 25MHz 3.3V LVCMOS outputs

2 - 2.048M 3.3V LVCMOS outputs

2 - USB 3.3V LVCMOS outputs at 12M or 24M

•

•

•

•

eliminate 24 resistors, saving 41mm2 of board area

Industrial temperature range operation; supports

demanding environmental conditions

Advanced 3.3V CMOS process; high-performance,

low-power

Supports independent spread spectrum on

Sys_CCB/DDRCLK and PCIe outputs

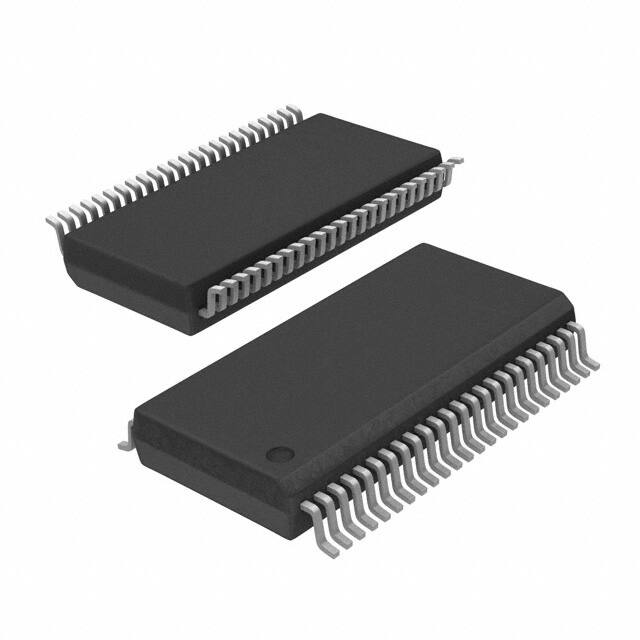

Packaged as 48-pin TSSOP, Pb-free, RoHS compliant

Key Specifications

• PCIe Gen1–3 compliant

• < 3ps rms phase noise on REF outputs

Block Diagram

SCLK

SDATA

^FS0

^FS1

Control

Logic

PLL4

(SS)

^SELPCIE125#_100

66M_SS

100MHz

PCIe_LR(5:0)

PLL3

(nonSS)

X1

Crystal

Oscillator

25MHz

Crystal

Sys_CCB

PLL1

(SS)

USB_CLK(2:1)

2.048M(1:0)

PLL2

(nonSS)

X2

125M

REF(5:0)

GND

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

1

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

X2_25

X1_25

GNDREF

REF5

REF4

REF3

VDDREF

GNDREF

REF2

REF1

REF0

AVDD12_24

^FS0/USB_CLK1

^FS1/USB_CLK2

GND12_24

GND2.048

CK2.048_0

CK2.048_1

VDD2.048

AVDD125

125M

GND125M

PCIeT_LR0

PCIeC_LR0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

6V49205A

Pin Assignment

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

VDDREF

SDATA

SCLK

GND66

66M_SS

VDD66

AVDDSYS

Sys_CCB

GNDSYS

GNDPCIe

PCIeT_LR5

PCIeC_LR5

PCIeT_LR4

PCIeC_LR4

GNDPCIe

AVDDPCIe

PCIeT_LR3

PCIeC_LR3

PCIeT_LR2

PCIeC_LR2

GNDPCIe

VDDPCIe

PCIeT_LR1

PCIeC_LR1

48-Pin TSSOP

^ Indicates Internal 100kohm pull up resistor

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

2

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Pin Descriptions

PIN #

1

2

3

4

5

6

7

8

9

10

11

12

15

16

17

18

19

20

21

22

23

PIN NAME

PIN TYPE

X2_25

OUT

X1_25

IN

GNDREF

PWR

REF5

OUT

REF4

OUT

REF3

OUT

VDDREF

PWR

GNDREF

PWR

REF2

OUT

REF1

OUT

REF0

OUT

AVDD12_24

PWR

^FS0/USB_CLK

I/O

1

^FS1/USB_CLK

I/O

2

GND12_24

PWR

GND2.048

PWR

CK2.048_0

OUT

CK2.048_1

OUT

VDD2.048

PWR

AVDD125

PWR

125M

OUT

GND125M

PWR

PCIeT_LR0

OUT

24

PCIeC_LR0

OUT

25

PCIeC_LR1

OUT

26

27

28

PCIeT_LR1

VDDPCIe

GNDPCIe

OUT

PWR

PWR

29

PCIeC_LR2

OUT

30

PCIeT_LR2

OUT

31

PCIeC_LR3

OUT

32

33

34

PCIeT_LR3

AVDDPCIe

GNDPCIe

OUT

PWR

PWR

35

PCIeC_LR4

OUT

36

PCIeT_LR4

OUT

37

PCIeC_LR5

OUT

38

39

40

41

42

43

44

45

46

47

48

PCIeT_LR5

GNDPCIe

GNDSYS

Sys_CCB

AVDDSYS

VDD66

66M_SS

GND66

SCLK

SDATA

VDDREF

OUT

PWR

PWR

OUT

PWR

PWR

OUT

PWR

IN

I/O

PWR

13

14

DESCRIPTION

Crystal output, Nominally 25.00MHz.

Crystal input, Nominally 25.00MHz.

Ground pin for the REF outputs.

Copy of crystal input

Copy of crystal input

Copy of crystal input

Ref, XTAL power supply, nominal 3.3V

Ground pin for the REF outputs.

Copy of crystal input

Copy of crystal input

Copy of crystal input

Power for 12_24MHz PLL core, and outputs. Nominal 3.3V

Frequency select latch for Sys_CCB / 12 or 24MHz USB clock output. 3.3V. This pin has an

internal pull up resistor.

Frequency select latch for Sys_CCB / 12 or 24MHz USB clock output. 3.3V. This pin has an

internal pull up resistor.

Ground pin for 12_24M outputs.

Ground pin for 2.048M outputs.

2.048M output, nominal 3.3V.

2.048M output, nominal 3.3V.

Power supply for 2.048M outputs, nominal 3.3V.

Power for 125MHz PLL core and output, nominal 3.3V

125M output, nominal 3.3V.

Ground pin for 125M outputs.

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Power supply for PCI Express outputs, nominal 3.3V

Ground pin for the PCIe outputs.

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Analog Power supply for PCI Express clocks, nominal 3.3V

Ground pin for the PCIe outputs.

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Complement clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series

resistor

True clock of 0.8V differential push-pull PCI_Express pair with integrated 33ohm series resistor

Ground pin for the PCIe outputs.

Ground pin for the Sys_CCB output

System CCB clock output

Analog Power supply for Sys_CCB clock and outputs, nominal 3.3V

Power supply for 66.66M output(s), nominal 3.3V.

66.66M spread-spectrum capable output, nominal 3.3V

Ground pin for 66.66M output(s).

Clock pin of SMBus circuitry.

Data pin for SMbus circuitry.

Ref, XTAL power supply, nominal 3.3V

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

3

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Table 1: PCIEX Spread Table (selectable via SMBUS)

SELPCIE125#_100

B0b4

B0b3

Spread %

B6b4

0 (125MHz)

x

x

No Spread

1 (100MHz)

0

0

No Spread (default)

1 (100MHz)

0

1

Down -0.5%

1 (100MHz)

1

0

Down -0.75%

1 (100MHz)

1

1

No Spread

*Once in spread mode, do not return to non spread without reset

Table 2: Sys_CCB and DDR Spread Table (selectable via SMBUS)

B0b7

0

0

0

0

1

1

1

1

B0b6

0

0

1

1

0

0

1

1

B0b5

0

1

0

1

0

1

0

1

Spread %

No Spread (default)

Down -0.5%

Down -0.75%

Down -0.25%

Reserved

Reserved

Reserved

Reserved

Table 3: Sys_CCB Frequency Select Table (Latched and selectable via SMBUS)

FS1 /

B4b3

FS0 /

B4b2

Sys_CCB (MHz)

0

0

66.66

0

1

100

1

0

80

1

1

83.33

Table 4: PCI Express Amplitude Control

B6b7

0

0

1

1

B6b6

0

1

0

1

PCIe Amplitude

700mV

800mV

900mV

1000mV

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

4

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Absolute Maximum Ratings

Stresses above the ratings listed below can cause permanent damage to the 6V49205A. These ratings, which are standard

values for Renesas commercially rated parts, are stress ratings only. Functional operation of the device at these or any other

conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over

the recommended operating temperature range.

PARAMETER

Maximum Supply Voltage

Maximum Input Voltage

SYMBOL

VDDxxx

VIH

CONDITIONS

Supply Voltage

Referenced to GND

MIN

Minimum Input Voltage

V IL

Referenced to GND

GND - 0.5

Storage Temperature

Ts

JunctionTemperature

Tj

Input ESD protection

ESD prot

Human Body Model

NOTES on Absolute Max Parameters

1

Operation under these conditions is neither implied, nor guaranteed.

TYP

-65

MAX

4.6

VDD + 0.5

UNITS

V

V

Notes

1

1

V

1

°

150

125

C

°C

V

2000

1

1

Electrical Characteristics - Input/Supply/Common Output DC Parameters

TAMB = -40 to +85°C; V DD = 3.3 V +/-5%, All outputs driving test loads (unless noted otherwise).

PARAMETER

SYMBOL

CONDITIONS

Ambient Operating Temp

TAMB

Supply Voltage

VDDxxx

Supply Voltage

Power supply ramp must be montonic

Power supply Ramp Time

TPWRRMP

MIN

-40

3.135

TYP

25

3.3

MAX

85

3.465

4

UNITS

°C

V

ms

Latched Input High Voltage

V IH_LI

Single-ended Latched Inputs

2.1

V DD + 0.3

V

Latched Input Low Voltage

VIL_LI

Single-ended Latched Inputs

V SS - 0.3

0.8

V

-5

Input Leakage Current

IIN

VIN = V DD , V IN = GND

Operating Supply Current

IDDOP3.3

All outputs loaded and running

Input Frequency

Fi

Pin Inductance

Lpin

CIN

Logic Inputs

3

5

pF

Input Capacitance

COUT

Output pin capacitance

5

6

pF

CINX

X1 & X2 pins

From VDD Power-Up or de-assertion of PD

to 1st clock

5

6

pF

3.2

5

ms

10

ns

1

1

Clk Stabilization

TSTAB

Tfall_SE

TFALL

23

1.5

Fall/rise time of all 3.3V control inputs from

20-80%

Trise_SE

TRISE

SMBus Voltage

VDD

Low-level Output Voltage

Current sinking at

V OLSMB = 0.4 V

VOLSMB

@ IPULLUP

IPULLUP

SMB Data Pin

2.7

5

uA

119

155

mA

25

27

MHz

5

7

nH

Notes

10

ns

3.3

V

0.4

V

4

2

3

mA

SCLK/SDATA

(Max VIL - 0.15) to

TRI2C

1000

ns

Clock/Data Rise Time

(Min VIH + 0.15)

(Min VIH + 0.15) to

SCLK/SDATA

300

ns

TFI2C

(Max VIL - 0.15)

Clock/Data Fall Time

Maximum SMBus Operating

100

kHz

FSMBUS

Frequency

NOTES on DC Parameters: (unless otherwise noted, guaranteed by design and characterization, not 100% tested in production).

1

Signal is required to be monotonic in this region.

2

Input leakage current does not include inputs with pull-up or pull-down resistors

3

For margining purposes only. Normal operation should have Fin =25MHz

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

5

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

AC Electrical Characteristics - Low Power HCSL-Compatible PCIe Outputs

PARAMETER

SYMBOL

CONDITIONS

Clock Frequency

f

Spread off

ppmSSof f

PCIe 100MHz or 125MHz

TYP

100.00

125.00

0

ppmSSon

PCIe @ -0.5% spread, 100MHz only

+/-100

Rising/Falling Edge Slew Rate

t SLEW

Differential Measurement

Slew Rate Variation

t SLVAR

Single-ended Measurement

1

20

%

1,6

Maximum Output Voltage

V HIGH

Includes overshoot

793

1150

mV

6,7

Synthesis error

MIN

2.2

4.1

Minimum Output Voltage

VLOW

Includes undershoot

-300

Differential Voltage Swing

V SWING

Differential Measurement

300

Crossing Point Voltage

V XABS

Single-ended Measurement

300

419

Crossing Point Variation

VXABSVAR

Single-ended Measurement

Duty Cycle

DCYC

Differential Measurement

45

PCIe Jitter - Cycle to Cycle

PCIeJC2C

Differential Measurement

TSKEwPCIe50

Differential Measurement

fSSMOD

Triangular Modulation

PCIe[5:0] Skew

Spread Spectrum Modulation

Frequency

Notes for PCIe Clocks:

MAX

UNITS

MHz

MHz

ppm

ppm

1,2

5.7

V/ns

1,3,6

-22

30

NOTES

2,3

2,3

1,2

mV

6,7

mV

1,6

550

mV

1,4,6

115

140

mV

1,4,5

50.1

55

%

1

36

125

ps

1

1172

1500

ps

1,6,8

31.5

33

kHz

1

Guaranteed by design and characterization, not 100% tested in production.

Clock Frequency specifications are guaranteed assuming that REF is at 25MHz

3

Slew rate measured through V_swing voltage range centered about differential zero

4

Vcross is defined at the voltage where Clock = Clock#.

5

Only applies to the differential rising edge (Clock rising, Clock# falling.)

6

At default SMBus settings.

7

The Freescale P-series CPU's have internal terminations on their SerDes Reference Clock inputs. The resulting amplitude at these inputs will be 1/2 of the

values listed, which are well within the 800mV Freescale specification for these inputs.

8

This value includes an intentional output-to-output skew of approximately 250ps.

2

Electrical Characteristics - Phase Jitter, PCIe Outputs at 100MHz

PARAMETER

SYMBOL

t jphPCIe1

t jphPCIe2Lo

Jitter, Phase

tjphPCIe2Hi

t jphPCIe3

CONDITIONS

PCIe Gen 1 phase jitter

PCIe Gen 2 phase jitter

Lo-band content

PCIe Gen 2 phase jitter

Hi-band content

PCIe Gen 3 phase jitter

MIN

TYP

35

MAX

56

1.6

2.4

1.9

2.8

0.5

0.83

INDUSTRY

SPEC LIMIT UNITS NOTES

86

ps

1,2,3

ps

3

1,2,3

(RMS)

ps

3.1

1,2,3

(RMS)

ps

1

1,2,3

(RMS)

Notes on Phase Jitter:

1

See http://www.pcisig.com for complete specs. Guaranteed by design and characterization, not tested in production.

2

Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12

3

Applies to PCIe outputs @ default amplitude and 100MHz with spread off or at -0.5%.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

6

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Electrical Characteristics - DDR Clock

PARAMETER

DDR Clock Frequency

SYMBOL

fDDR

CONDITIONS

V T = OVDD/2 V

ppmSSof f

Spread off

ppmSSon

Spread on

Output High Voltage

VOH

VOH at the selected operating frequency

Output Low Voltage

V OL

V OL at the selected operating frequency

Synthesis error

Slew Rate

VDDO = 3.3V

MIN

TYP

66.666

MAX

UNITS

MHz

NOTES

2,3,6

0

ppm

1,2,5

+/-150

ppm

1,2,5

2.4

V

1

0.4

V

1

Hi-Z

tSLEW00

'00' = Hi-Z

tSLEW01

'01' Slow Slew Rate (Averaging on)

1.1

1.6

2.3

V/ns

1,3,8

tSLEW10

'10' Fast Slew Rate (Averaging on)

1.6

2.3

3.2

V/ns

1,3,8

V/ns

tSLEW11

'11' Fastest Slew Rate (Averaging on)

1.8

2.7

3.7

V/ns

1,3,8

Duty Cycle

dt1

V T = OVDD/2 V

40

51.4

60

%

1,6

Jitter, Peak period jitter

t jpeak

V T = OVDD/2 V

±96

±150

ps

1,6

Phase Noise

t phasenoise

-56dBc

10

500

kHz

1,7

AC Input Swing Limits @ 3.3V

OVDD

ΔVAC

This is the difference between VOL and

VOH at the selected operating frequency.

1.9

3.4

V

1

Spread Spectrum Modulation

Frequency

fSSMOD

Triangular Modulation

30

32.3

60

kHz

MIN

TYP

66.666

100.00

80.00

83.333

0

MAX

UNITS

MHz

MHz

MHz

MHz

ppm

NOTES

2,3,6

2,3,6

2,3,6

2,3,6

1,2,5

ppm

1,2,5

V

1

V

1

Electrical Characteristics - Sys_CCB

PARAMETER

Clock Frequency

Synthesis error

SYMBOL

CONDITIONS

FS(1:0) = 00, VT = OVDD/2

FS(1:0) = 01, VT = OVDD/2

FS(1:0) = 10, VT = OVDD/2

FS(1:0) = 11, VT = OVDD/2

Spread off

fSy s_CCB

ppmSSof f

V

V

V

V

ppmSSon

Spread on

Output High Voltage

VOH

VOH at the selected operating frequency

Output Low Voltage

V OL

V OL at the selected operating frequency

tSLEW00

'00' = Hi-Z

tSLEW01

'01' Slow Slew Rate (Averaging on)

Slew Rate

VDDO = 3.3V

+/-150

2.4

0.4

Hi-Z

0.8

1.4

V/ns

2.1

V/ns

1,3,8

tSLEW10

'10' Fast Slew Rate (Averaging on)

0.9

1.6

2.5

V/ns

1,3,8

tSLEW11

'11' Fastest Slew Rate (Averaging on)

1.1

1.9

3.1

V/ns

1,3,8

40

1,6

Duty Cycle

dt1

V T = OVDD/2 V

51.4

60

%

Jitter, Peak period jitter

t jpeak

V T = OVDD/2 V, SSC < 0.75%

±116

±150

ps

1

Phase Noise

tphasenoise

-56dBc

10

500

kHz

1,7

AC Input Swing Limits @ 3.3V

OVDD

ΔVAC

This is the difference between VOL and

VOH at the selected operating frequency.

1.9

V

1

Spread Spectrum Modulation

Frequency

fSSMOD

Triangular Modulation

0

31.5

60

kHz

TYP

125.00

MAX

UNITS

ns

ppm

V

NOTES

2,3,6

1,2,5

1

0.5

V

1

0.7

1

ns

1,3

52

53

%

1

±150

ps

1

Electrical Characteristics - 125M

PARAMETER

Clock frequency

Synthesis error

Output High Voltage

SYMBOL

f125M

ppm

VOH

CONDITIONS

V T = OVDD/2 V

MIN

VOH at the selected operating frequency

2.2

Output Low Voltage

Rise/Fall time

VDDO = 3.3V

Duty Cycle

V OL

V OL at the selected operating frequency

tRF125M3.3V

Measured between 0.6V and 2.7V

dt1

V T = OVDD/2 V

Jitter, Peak period jitter

t jpeak

V T = OVDD/2 V

0

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

47

7

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Electrical Characteristics - REF(5:0)

PARAMETER

Clock Frequency

Crystal Frequency Error

Output High Voltage

SYMBOL

f

ppm

VOH

CONDITIONS

V T = OVDD/2 V

Including all aging and tuning effects

VOH at the selected operating frequency

Output Low Voltage

Slew Rate

VDDO

3 3V

Duty Cycle

V OL

V OL at the selected operating frequency

0.4

V

1

tSLEW

'00' = Hi-Z

1.0

1.7

2.7

V/ns

1,3,4

V T = OVDD/2 V

40

51

60

%

1

ps

1

dt1

Jitter, Peak period jitter

t jpeak

V T = 1.5 V, odd/even outputs have an

intentional 180degree phase shift.

V T = OVDD/2 V

Jitter, Phase

t jphase

(12kHz-5MHz), VT = 1.5 V

Pin to Pin Skew

tskew

MIN

TYP

25.00

-50

2.2

MAX

50

N/A

UNITS

MHz

ppm

V

NOTES

2,3

1,2

1

±78

±200

ps

1

1.7

3

ps rms

1

TYP

12.00

MAX

UNITS

MHz

MHz

ppm

NOTES

2,3

2,3

1,2,5

V

1

V

1

Electrical Characteristics - USB_CLK(2:1)

PARAMETER

SYMBOL

CONDITIONS

Clock Frequency

fUSB_CLK

V T = OVDD/2 V

Synthesis error

ppm

Output High Voltage

VOH

VOH at the selected operating frequency

Output Low Voltage

V OL

V OL at the selected operating frequency

t SLEW00

'00' = Hi-Z

t SLEW01

'01' Slow Slew Rate (Averaging on)

1.0

1.4

1.8

V/ns

1,3,4

t SLEW10

'10' Fast Slew Rate (Averaging on)

1.5

2.0

2.7

V/ns

1,3,4

tSLEW11

'11' Fastest Slew Rate (Averaging on)

1.8

2.3

3.1

V/ns

1,3,4

Duty Cycle

dt1

V T = OVDD/2 V

45

50.3

55

%

1

Jitter, RMS

tjRMS

12kHz to Nyquist

23

120

ps

1

Jitter, Cycle to cycle

t jcy c-cy c

V T = OVDD/2 V

142

350

ps

1

TYP

2.048

MAX

UNITS

MHz

NOTES

2,3,6

ppm

1,2,5

V

1

V

1

Slew Rate

VDDO = 3.3V

MIN

24.00

0

2.2

0.4

Hi-Z

V/ns

Electrical Characteristics - 2.048M(1:0)

PARAMETER

Clock Frequency

SYMBOL

fUSB_CLK

CONDITIONS

V T = OVDD/2 V

MIN

2.2

0

Synthesis error

ppm

Output High Voltage

VOH

VOH at the selected operating frequency

Output Low Voltage

V OL

V OL at the selected operating frequency

tSLEW00

'00' = Hi-Z

0.4

Hi-Z

V/ns

t SLEW01

'01' Slow Slew Rate (Averaging on)

1.1

1.7

2.5

V/ns

1,3,4

t SLEW10

'10' Fast Slew Rate (Averaging on)

1.6

2.3

3.2

V/ns

1,3,4

tSLEW11

'11' Fastest Slew Rate (Averaging on)

1.8

2.6

3.6

V/ns

1,3,4

Duty Cycle

dt1

V T = OVDD/2 V

45

46.7

55

%

1

Pin to Pin Skew

tskew

V T = OVDD/2 V

108

250

ps

1

Jitter, RMS

tjRMS

12kHz to Nyquist

47

70

ps

1

Jitter, Peak period jitter

t jpeak

V T = OVDD/2 V

±170

±250

ps

1

Slew Rate

VDDO = 3.3V

Notes for single-ended clocks:

1

Guaranteed by design and characterization, not 100% tested in production.

2

Clock Frequency specifications are guaranteed assuming that REF is at 25MHz

3

At default SMBus settings

4

Measured between 20% and 80% of OVDD

5

This is the frequency error with respect to the crystal frequency.

6

Measured at the rising and/or falling edge at OVDD/2 V.

7

Phase noise is calculated as the FFT of the TIE jitter.

8

Slew rate is measured from ±0.3ΔV AC at the center of peak to peak voltage at the clock input.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

8

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

General SMBus Serial Interface Information for 6V49205A

How to Write

•

•

•

•

•

•

•

•

•

•

How to Read

Controller (host) sends a start bit

Controller (host) sends the write address

Renesas clock will acknowledge

Controller (host) sends the beginning byte location = N

Renesas clock will acknowledge

Controller (host) sends the byte count = X

Renesas clock will acknowledge

Controller (host) starts sending Byte N through Byte

N+X-1

Renesas clock will acknowledge each byte one at a

time

Controller (host) sends a Stop bit

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Controller (host) will send a start bit

Controller (host) sends the write address

Renesas clock will acknowledge

Controller (host) sends the beginning byte location = N

Renesas clock will acknowledge

Controller (host) will send a separate start bit

Controller (host) sends the read address

Renesas clock will acknowledge

Renesas clock will send the data byte count = X

Renesas clock sends Byte N+X-1

Renesas clock sends Byte 0 through Byte X (if X(H)

was written to Byte 8)

Controller (host) will need to acknowledge each byte

Controller (host) will send a not acknowledge bit

Controller (host) will send a stop bit

Index Block Write Operation

Controller (Host)

T

Renesas (Slave/Receiver)

starT bit

Controller (Host)

T

Slave Address D2(H)

WR

Index Block Read Operation

Renesas (Slave/Receiver)

starT bit

Slave Address D2(H)

WR

WRite

WRite

ACK

ACK

Beginning Byte = N

Beginning Byte = N

ACK

ACK

RT

Data Byte Count = X

ACK

RD

Beginning Byte N

X Byte

O

O

O

Repeat starT

Slave Address D3(H)

ReaD

ACK

ACK

O

Data Byte Count=X

O

ACK

Beginning Byte N

O

ACK

Byte N + X - 1

P

O

stoP bit

Note: I2C compatible. Native mode is SMBus Block mode

protocol. To use I2C Byte mode set the 2^7 bit in the

command Byte. No Byte count is used.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

X Byte

ACK

O

O

O

O

O

Byte N + X - 1

N

Not acknowledge

P

stoP bit

9

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Byte 0 Frequency and Spread Select Register

Bit

7

6

5

4

3

2

1

0

Name

SS4

SS3

SS2

SS1

SS0

REF_5_EN

REF_4_EN

REF_3_EN

Description

0

Output enable for REF_5

Output enable for REF_4

Output enable for REF_5

Type

RW

RW

RW

RW

RW

RW

RW

RW

Output Disabled

Output Disabled

Output Disabled

Description

Output enable for REF_2

Output enable for REF_1

Output enable for REF_0

Output enable for USB_CLK1

Output enable for USB_CLK2

Output enable for CK2.048_0

Output enable for CK2.048_1

Output enable for DDRCLK

Type

RW

RW

RW

RW

RW

RW

RW

RW

Output

Output

Output

Output

Output

Output

Output

Output

0

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Type

RW

RW

RW

RW

RW

RW

RW

RW

Output

Output

Output

Output

Output

Output

Output

Output

0

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Sys_CCB and DDRCLK Spread

Selection Table

PCIE Spread Selection Table

1

Output Enabled

Output Enabled

Output Enabled

Default

0

0

0

0

0

1

1

1

Output

Output

Output

Output

Output

Output

Output

Output

1

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Default

1

1

1

1

1

1

1

1

Output

Output

Output

Output

Output

Output

Output

Output

1

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Default

1

1

1

1

1

1

1

1

1

Default

0

1

0

1

1

1

0

1

See Table 2: Sys_CCB and DDRCLK

Spread Table

See Table 1: PCIE Spread Table

Byte 1 Output Enable Register

Bit

7

6

5

4

3

2

1

0

Name

REF_2_EN

REF_1_EN

REF_0_EN

USB_CLK1_EN

USB_CLK2_EN

CK2.048_0_EN

CK2.048_1_EN

DDRCLK_EN

Byte 2 Output Enable Register

Bit

7

6

5

4

3

2

1

0

Name

Sys_CCB_EN

PCIe5_EN

PCIe4_EN

PCIe3_EN

PCIe2_EN

PCIe1_EN

PCIe0_EN

125M_EN

Description

Output enable for Sys_CCB

Output enable for PCIe5

Output enable for PCIe4

Output enable for PCIe3

Output enable for PCIe2

Output enable for PCIe1

Output enable for PCIe0

Output enable for 125M

Byte 3 Slew Rate Control Register

Bit

7

6

5

4

3

2

1

0

Name

USB1_SLEW1

USB1_SLEW0

USB2_SLEW1

USB2_SLEW0

CK2.048_SLEW1

CK2.048_SLEW0

Sys_CCB_SLEW1

Sys_CCB_SLEW0

Description

USB_CLK1 Slew Rate Control

USB_CLK2 Slew Rate Control

CK2.048_0 and CK2.048_1 Slew Rate

Control

Sys_CCB Slew Rate Control

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

See USB Electrical Tables

See USB Electrical Tables

See CK2.048 Electrical Tables

See Sys_CCB Electrical Tables

Byte 4 Slew Rate Control Register

Bit

7

6

5

4

3

2

1

0

Name

66M_Slew1

66M_Slew0

Description

66MCLK Slew Rate Control

Type

RW

RW

0

1

See 66M Electrical Tables

Reserved

Reserved

FS1

FS0

USB1_fSel

USB2_fSel

Sys_CCB Frequency Select Latch

USB_CLK1 Clock Frequency Select

USB_CLK2 Clock Frequency Select

RW

RW

RW

RW

See Table 3: Sys_CCB Frequency

Selection

12MHz

24MHz

12MHz

24MHz

Default

0

1

0

1

Latch

Latch

0

1

Byte 5 is Reserved

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

10

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Byte 6 PCI Express Amplitude Control Register

Bit

7

6

5

4

3

2

1

0

Name

PCIE_AMP1

PCIE_AMP0

Reserved

SELPCIE125#_100

Reserved

Reserved

Reserved

Reserved

Description

PCI Express Amplitude Control

Reserved

PCI Express latch select

Reserved

Reserved

Reserved

Reserved

0

1

See Table 4 PCIe Amplitude Selection

Table

125MHz

100MHz

-

Type

RW

RW

R

R

RW

RW

RW

RW

Default

0

1

1

latch

0

1

0

1

Byte 7 Revision and Vendor ID Register

Bit

7

6

5

4

3

2

1

0

Name

REV ID

REV ID

REV ID

REV ID

Vendor ID

Vendor ID

Vendor ID

Vendor ID

Description

Revision ID

Vendor ID

Type

R

R

R

R

R

R

R

R

0

-

1

-

Default

0

0

0

0

0

0

0

1

Type

RW

RW

RW

RW

RW

RW

RW

RW

0

1

Default

0

0

0

0

0

1

0

1

Byte 8 Byte Count Register

Bit

7

6

5

4

3

2

1

0

Name

BC7

BC6

BC5

BC4

BC3

BC2

BC1

BC0

Description

Byte Count Programming b(7:0)

Writing to this register will configure how

many bytes will be read back.

Recommended Crystal Characteristics

PARAMETER

VALUE

UNITS

NOTES

Frequency

Resonance Mode

Frequency Tolerance @ 25°C

Frequency Stability, ref @ 25°C Over

Operating Temperature Range

Temperature Range (commercial)

Temperature Range (industrial)

Equivalent Series Resistance (ESR)

Shunt Capacitance (CO)

25

Fundamental

±20

MHz

PPM Max

1

1

1

±20

PPM Max

1

0~70

-40~85

50

7

°C

°C

Ω Max

pF Max

1

1

1

1

Load Capacitance (CL)

Drive Level

Aging per year

8

0.3

±5

pF Max

mW Max

PPM Max

1

1

1

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

11

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Test Loads

Device

Low-Power push-pull HCSL Output test load

(standard PCIe test load)

L inches

CL=4.7pF

except

66M_SS

outputs

where

CL=15pf

Zo

Rs=39

Differential Zo

2pF

Test Load

2pF

Single-ended

Output

Differential Test Load, Zo = 100ohm, L = 5 inches

Thermal Characteristics (48-TSSOP) PAG48

PARAMETER

SYMBOL

CONDITIONS

Thermal Resistance

θJC

θJb

θJA0

θJA1

θJA3

Junction to Case

Junction to Base

Junction to Air, still air

Junction to Air, 1 m/s air flow

Junction to Air, 3 m/s air flow

TYP

UNITS NOTES

VALUE

28

°C/W

1

C/W

42

°

1

PAG48

62

°C/W

1

54

°C/W

1

51

°C/W

1

PKG

Marking Diagrams

25

48

IDT

6V49205APAGI

YYWW$

IDT

6V49205APAG

YYWW$

24

1

48TSSOP

25

48

24

1

48TSSOP

Notes:

1. ‘$’ is the mark code.

2. YYWW is the last two digits of the year, and the week number that the part was assembled.

3. “G” after the two-letter package code denotes Pb free package.

4. “I” denotes industrial temperature range.

5. Bottom marking: country of origin if not USA.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

12

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Package Outline and Package Dimensions (PAG48, 48-pin TSSOP, 6.10 mm Body, 0.50 Pitch)

Package dimensions are kept current with JEDEC Publication No. 95

Millimeters

48

Symbol

E1

A

A1

A2

b

c

D

E

E1

e

L

aaa

E

INDEX

AREA

1 2

D

A

A2

Min

Max

-1.20

0.05

0.15

0.80

1.05

0.17

0.27

0.09

0.20

12.40

12.60

8.10 BASIC

6.00

6.20

0.50 Basic

0.45

0.75

0

8

-0.10

Inches*

Min

Max

-0.047

0.002

0.006

0.032

0.041

0.007

0.011

0.0035 0.008

0.488

0.496

0.319 BASIC

0.236

0.244

0.020 Basic

0.018

0.030

0

8

-0.004

*For reference only. Controlling dimensions in mm.

A1

c

- Ce

b

SEATING

PLANE

L

aaa C

Ordering Information

Part / Order Number

Marking

Shipping Packaging

Package

Temperature

6V49205APAGI

6V49205APAGI8

6V49205APAG

6V49205APAG8

see page 12

Tubes

Tape and Reel

Tubes

Tape and Reel

48-pin TSSOP

48-pin TSSOP

48-pin TSSOP

48-pin TSSOP

-40to +85C

-40to +85C

0to +70C

0to +70C

see page 12

“G” after the two-letter package code denotes Pb-Free configuration, RoHS compliant.

For an NLG I-temp device, see the 6V49205B.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

13

6V49205A

REV 20201021

�6V49205A

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

Revision History

Revision Date

Description

1. Extensive overhaul of Electrical tables to more closely align with Freescale

published specifications.

2. Updated electrical tables with characterization data.

December 12, 2013 3. Clarified SMBus registers for Slew Rate Controls

4. Moved electrical tables in front of SMBus for consistency with other data sheets.

5. Updated Thermal Data and added test loads for clarity.

6. Updated front page text

7. Minor updates to pin names (mainly power and ground) for consistency and clarity

January 9, 2014

Table 2: Sys_CCB and DDR Spread Table; 100~111 marked as Reserved.

February 12, 2014 Added 48-pin VFQFPN package, diagrams, and references

Updated ordering information to remove I-temp NLG package, and to add commercial

March 24, 2015

PAG and NLG packages

May 11, 2016

1. Correct PCIeT_LRn and PCIeC_LRn to be PCIeT_Ln and PCIeC_Ln to indicate that

the Rs for the PCIe outputs is outside the part and to correct the pin description

accordingly. The test loads for the device are correct.

2. Update block diagram PCIe pin names to be consistent.

1.

2.

November 22, 2016

3.

4.

October 21, 2020

Undo Revision P

PCIe outputs have integrated terminations for 100ohm differential Zo.

Update Test Loads

Update Features/Benefits

Updated Sys_CCB Frequency Select table.

FREESCALE P10XX AND P20XX SYSTEM CLOCK WITH 66.66M DDR CLOCK

14

6V49205A

REV 20201021

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

�