DATASHEET

ISL8105, ISL8105A

+5V or +12V Single-Phase Synchronous Buck Converter PWM Controller with

Integrated MOSFET Gate Drivers

The ISL8105, ISL8105A is a simple single-phase PWM

controller for a synchronous buck converter. It operates from

+5V or +12V bias supply voltage. With integrated linear

regulator, boot diode, and N-Channel MOSFET gate drivers,

the ISL8105, ISL8105A reduces external component count and

board space requirements. These make the IC suitable for a

wide range of applications.

Utilizing voltage-mode control, the output voltage can be

precisely regulated to as low as 0.6V. The 0.6V internal

reference features a maximum tolerance of ±1.0% over the

commercial temperature range, and ±1.5% over the

industrial temperature range. Two fixed oscillator frequency

versions are available; 300kHz (ISL8105 for high efficiency

applications) and 600kHz (ISL8105A for fast transient

applications).

The ISL8105, ISL8105A features the capability of safe

start-up with pre-biased load. It also provides overcurrent

protection by monitoring the ON-resistance of the

bottom-side MOSFET to inhibit PWM operation

appropriately. During start-up interval, the resistor connected

to BGATE/BSOC pin is employed to program overcurrent

protection condition. This approach simplifies the

implementation and does not deteriorate converter

efficiency.

Pinouts

ISL8105, ISL8105A

(10 LD 3X3 DFN)

TOP VIEW

FN6306

Rev 5.00

April 15, 2010

Features

• Operates from +5V or +12V Bias Supply Voltage

- 1.0V to 12V Input Voltage Range (up to 20V possible

with restrictions; see “Input Voltage Considerations” on

page 9)

- 0.6V to VIN Output Voltage Range

• 0.6V Internal Reference Voltage

- ±1.0% Tolerance Over the Commercial Temperature

Range (0°C to +70°C)

- ±1.5% Tolerance Over the Industrial Temperature

Range (-40°C to +85°C).

• Integrated MOSFET Gate Drivers that Operate from

VBIAS (+5V to +12V)

- Bootstrapped High-side Gate Driver with Integrated

Boot Diode

- Drives N-Channel MOSFETs

• Simple Voltage-Mode PWM Control

- Traditional Dual Edge Modulation

• Fast Transient Response

- High-Bandwidth Error Amplifier

- Full 0% to 100% Duty Cycle

• Fixed Operating Frequency

- 300kHz for ISL8105

- 600kHz for ISL8105A

• Fixed Internal Soft-Start with Pre-biased Load Capability

• Lossless, Programmable Overcurrent Protection

- Uses Bottom-side MOSFET’s rDS(ON)

BOOT

1

10 LX

TGATE

2

9

COMP/EN

N/C

3

8

FB

• Output Current Sourcing and Sinking Currents

GND

4

7

N/C

• Pb-Free (RoHS Compliant)

BGATE/BSOC

5

6

VBIAS

GND

• Enable/Disable Function Using COMP/EN Pin

Applications

• 5V or 12V DC/DC Regulators

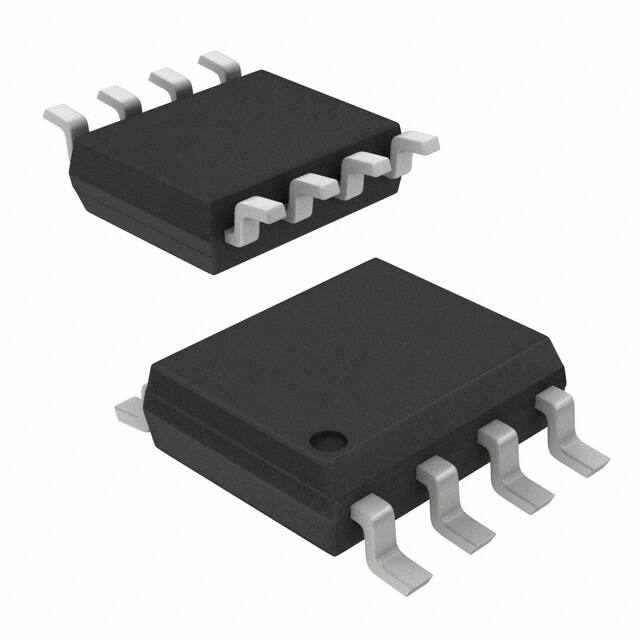

ISL8105, ISL8105A

(8 LD SOIC)

TOP VIEW

• Industrial Power Systems

• Telecom and Datacom Applications

BOOT 1

8

LX

• Test and Measurement Instruments

TGATE 2

7

COMP/EN

• Distributed DC/DC Power Architecture

3

6

FB

• Point of Load Modules

BGATE/BSOC 4

5

VBIAS

GND

FN6306 Rev 5.00

April 15, 2010

Page 1 of 16

�ISL8105, ISL8105A

Ordering Information

PART NUMBER

(Note)

PART

MARKING

SWITCHING

FREQUENCY

(kHz)

TEMPERATURE

RANGE

(°C)

PACKAGE

(Pb-Free)

PKG.

DWG. #

ISL8105CRZ*

5CRZ

300

0 to +70

10 Ld DFN

L10.3x3C

ISL8105IBZ*

8105 IBZ

300

-40 to +85

8 Ld SOIC

M8.15

ISL8105IRZ*

5IRZ

300

-40 to +85

10 Ld DFN

L10.3x3C

ISL8105ACRZ*

05AZ

600

0 to +70

10 Ld DFN

L10.3x3C

ISL8105AIBZ*

8105 AIBZ

600

-40 to +85

8 Ld SOIC

M8.15

ISL8105AIRZ*

5AIZ

600

-40 to +85

10 Ld DFN

L10.3x3C

ISL8105AEVAL1Z

Evaluation Board

*Add “-T” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations).

Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J

STD-020.

Typical Application Diagram

VIN

+1V TO +12V

VBIAS

+5V OR +12V

CHF

CBULK

CDCPL

VBIAS

BOOT

COMP/EN

CBOOT

TGATE

C1

C2

ISL8105

R2

Q1

LOUT

VOUT

LX

COUT

FB

Q2

BGATE/BSOC

GND

RBSOC

C3

R3

R1

R0

FN6306 Rev 5.00

April 15, 2010

Page 2 of 16

�ISL8105, ISL8105A

FN6306 Rev 5.00

April 15, 2010

Block Diagram

VBIAS

DBOOT

SAMPLE

AND

HOLD

INTERNAL

REGULATOR

POR AND

SOFT-START

+

BOOT

OC

TGATE

COMPARATOR

5V INT.

21.5A

LX

20k

PWM

TO

COMPARATOR

BGATE/BSOC

0.6V

INHIBIT

+

ERROR

+

-

PWM

GATE

CONTROL

LOGIC

VBIAS

AMP

FB

DIS

5V INT.

0.4V

20A

BGATE/BSOC

+

DIS

OSCILLATOR

COMP/EN

FIXED 300kHZ OR 600kHz

Page 3 of 16

GND

�ISL8105, ISL8105A

Absolute Maximum Ratings

Thermal Information

Bias Voltage, VBIAS . . . . . . . . . . . . . . . . . . . . GND - 0.3V to +15.0V

Boot Voltage, VBOOT . . . . . . . . . . . . . . . . . . . GND - 0.3V to +36.0V

TGATE Voltage, VTGATE . . . . . . . . . . . VLX - 0.3V to VBOOT + 0.3V

BGATE/BSOC Voltage, VBGATE/BSOC . .GND - 0.3 to VBIAS + 0.3V

LX Voltage, VLX . . . . . . . . . . . . . . . . . .GND - 0.3V to VBOOT + 0.3V

Upper Driver Supply Voltage, VBOOT - VLX . . . . . . . . . . . . . . . .15V

Clamp Voltage, VBOOT - VBIAS . . . . . . . . . . . . . . . . . . . . . . . . . .24V

FB, COMP/EN Voltage . . . . . . . . . . . . . . . . . . . . . GND - 0.3V to 6V

Thermal Resistance

JA (°C/W)

JC (°C/W)

SOIC Package (Note 1) . . . . . . . . . . . .

95

N/A

DFN Package (Notes 1, 2) . . . . . . . . . .

44

5.5

Maximum Junction Temperature

(Plastic Package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Maximum Storage Temperature Range . . . . . . . . . .-65°C to +150°C

Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

Recommended Operating Conditions

Bias Voltage, VBIAS . . . . . +5V ±10%, +12V ±20%, or 6.5V to 14.4V

Ambient Temperature Range

ISL8105C, ISL8105AC . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

ISL8105I, ISL8105AI. . . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C

Junction Temperature Range. . . . . . . . . . . . . . . . . .-40°C to +125°C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

1. JA is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. See

Tech Brief TB379.

2. For JC, the “case temp” location is the center of the exposed metal pad on the package underside.

Electrical Specifications

PARAMETER

Recommended Operating Conditions, Unless Otherwise Noted. Parameters with MIN and/or MAX limits are

100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are

not production tested.

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

4

5.2

7

mA

0.375

0.4

0.425

V

ISL8105C

270

300

330

kHz

ISL8105I

240

300

330

kHz

ISL8105AC

540

600

660

kHz

ISL8105AI

510

600

660

kHz

INPUT SUPPLY CURRENTS

Shutdown VBIAS Supply Current

IVBIAS_S

VBIAS = 12V; Disabled

DISABLE

Disable Threshold (COMP/EN pin)

VDISABLE

OSCILLATOR

Nominal Frequency Range

fOSC

fOSC

Ramp Amplitude (Note 3)

VOSC

1.5

VP-P

POWER-ON RESET

Rising VBIAS Threshold

VPOR_R

3.9

4.1

4.3

V

VBIAS POR Threshold Hysteresis

VPOR_H

0.30

0.35

0.40

V

REFERENCE

Nominal Reference Voltage

0.6

VREF

Reference Voltage Tolerance

V

ISL8105C (0°C to +70°C)

-1.0

+1.0

%

ISL8105I (-40°C to +85°C)

-1.5

+1.5

%

ERROR AMPLIFIER

DC Gain (Note 3)

Unity Gain-Bandwidth (Note 3)

Slew Rate (Note 3)

GAINDC

96

dB

UGBW

20

MHz

SR

9

V/µs

3.0

GATE DRIVERS

TGATE Source Resistance

FN6306 Rev 5.00

April 15, 2010

RTG-SRCh

VBIAS = 14.5V, 50mA Source Current

Page 4 of 16

�ISL8105, ISL8105A

Electrical Specifications

Recommended Operating Conditions, Unless Otherwise Noted. Parameters with MIN and/or MAX limits are

100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are

not production tested. (Continued)

PARAMETER

SYMBOL

TEST CONDITIONS

MIN

TYP

MAX

UNITS

TGATE Source Resistance

RTG-SRCl

VBIAS = 4.25V, 50mA Source Current

3.5

TGATE Sink Resistance

RTG-SNKh

VBIAS = 14.5V, 50mA Source Current

2.7

TGATE Sink Resistance

RTG-SNKl

VBIAS = 4.25V, 50mA Source Current

2.7

BGATE Source Resistance

RBG-SRCh

VBIAS = 14.5V, 50mA Source Current

2.4

BGATE Source Resistance

RBG-SRCl

VBIAS = 4.25V, 50mA Source Current

2.75

BGATE Sink Resistance

RBG-SNKh

VBIAS = 14.5V, 50mA Source Current

2.0

BGATE Sink Resistance

RBG-SNKl

VBIAS = 4.25V, 50mA Source Current

2.1

OVERCURRENT PROTECTION (OCP)

BSOC Current Source

IBSOC

ISL8105C; BGATE/BSOC Disabled

19.5

21.5

23.5

µA

ISL8105I; BGATE/BSOC Disabled

18.0

21.5

23.5

µA

NOTE:

3. Limits established by characterization and are not production tested.

Functional Pin Description (SOIC, DFN)

BOOT (SOIC Pin 1, DFN Pin 1)

This pin provides ground referenced bias voltage to the

top-side MOSFET driver. A bootstrap circuit is used to create

a voltage suitable to drive an N-Channel MOSFET (equal to

VBIAS minus the on-chip BOOT diode voltage drop), with

respect to LX.

TGATE (SOIC Pin 2, DFN Pin 2)

VBIAS (SOIC Pin 5, DFN Pin 6)

This pin provides the bias supply for the ISL8105, as well as

the bottom-side MOSFET's gate and the BOOT voltage for

the top-side MOSFET's gate. An internal 5V regulator will

supply bias if VBIAS rises above 6.5V (but the BGATE/BSOC

and BOOT will still be sourced by VBIAS). Connect a well

decoupled +5V or +12V supply to this pin.

FB (SOIC Pin 6, DFN Pin 8)

Connect this pin to the gate of top-side MOSFET; it provides

the PWM-controlled gate drive. It is also monitored by the

adaptive shoot-through protection circuitry to determine

when the top-side MOSFET has turned off.

This pin is the inverting input of the internal error amplifier.

Use FB, in combination with the COMP/EN pin, to

compensate the voltage-control feedback loop of the

converter. A resistor divider from the output to GND is used

to set the regulation voltage.

GND (SOIC Pin 3, DFN Pin 4)

COMP/EN (SOIC Pin 7, DFN Pin 9)

This pin represents the signal and power ground for the IC.

Tie this pin to the ground island/plane through the lowest

impedance connection available.

This is a multiplexed pin. During soft-start and normal converter

operation, this pin represents the output of the error amplifier.

Use COMP/EN, in combination with the FB pin, to compensate

the voltage-control feedback loop of the converter.

BGATE/BSOC (SOIC Pin 4, DFN Pin 5)

Connect this pin to the gate of the bottom-side MOSFET; it

provides the PWM-controlled gate drive (from VBIAS). This

pin is also monitored by the adaptive shoot-through

protection circuitry to determine when the lower MOSFET

has turned off.

During a short period of time following Power-On Reset

(POR) or shut-down release, this pin is also used to

determine the current limit threshold of the converter.

Connect a resistor (RBSOC) from this pin to GND. See

“Overcurrent Protection (OCP)” on page 7 for equations. An

overcurrent trip cycles the soft-start function, after two

dummy soft-start time-outs. Some of the text describing the

BGATE function may leave off the BSOC part of the name,

when it is not relevant to the discussion.

FN6306 Rev 5.00

April 15, 2010

Pulling COMP/EN low (VDISABLE = 0.4V nominal) will

disable (shut-down) the controller, which causes the

oscillator to stop, the BGATE and TGATE outputs to be held

low, and the soft-start circuitry to re-arm. The external

pull-down device will initially need to overcome maximum of

5mA of COMP/EN output current. However, once the IC is

disabled, the COMP output will also be disabled, so only a

20µA current source will continue to draw current.

When the pull-down device is released, the COMP/EN pin

will start to rise at a rate determined by the 20µA charging up

the capacitance on the COMP/EN pin. When the COMP/EN

pin rises above the VDISABLE trip point, the ISL8105 will

begin a new initialization and soft-start cycle.

Page 5 of 16

�ISL8105, ISL8105A

LX (SOIC Pin 8, DFN Pin 10)

Connect this pin to the source of the top-side MOSFET and

the drain of the bottom-side MOSFET. It is used as the sink

for the TGATE driver and to monitor the voltage drop across

the bottom-side MOSFET for overcurrent protection. This pin

is also monitored by the adaptive shoot-through protection

circuitry to determine when the top-side MOSFET has turned

off.

N/C (DFN Only; Pin3, Pin 7)

These two pins in the DFN package are No Connect.

Functional Description

time, the BGATE/BSOC pin is initialized by disabling the

BGATE driver and drawing BSOC (nominal 21.5µA) through

RBSOC. This sets up a voltage that will represent the BSOC

trip point. At t2, there is a variable time period for the OCP

sample and hold operation (0ms to 3.4ms nominal; the

longer time occurs with the higher overcurrent setting). The

sample and hold uses a digital counter and DAC to save the

voltage, so the stored value does not degrade, for as long as

the VBIAS is above VPOR. See “Overcurrent Protection

(OCP)” on page 7 for more details on the equations and

variables. Upon the completion of sample and hold at t3, the

soft-start operation is initiated, and the output voltage ramps

up between t4 and t5.

Initialization (POR and OCP Sampling)

BGATE

STARTS

SWITCHING

Figure 1 shows a start-up waveform of ISL8105. The

Power-ON-Reset (POR) function continually monitors the

bias voltage at the VBIAS pin. Once the rising POR

threshold is exceeded 4V (VPOR nominal), the POR function

initiates the Overcurrent Protection (OCP) sample and hold

operation (while COMP/EN is ~1V). When the sampling is

complete, VOUT begins the soft-start ramp.

COMP/EN

VOUT

BGATE/BSOC

VBIAS

3.4ms

t0 t1

3.4ms

0ms to 3.4ms

t2 t3 t4

t5

VOUT

~4V POR

VCOMP/EN

FIGURE 2. BGATE/BSOC AND SOFT-START OPERATION

Soft-Start and Pre-Biased Outputs

FIGURE 1. POR AND SOFT-START OPERATION

If the COMP/EN pin is held low during power-up, the

initialization will be delayed until the COMP/EN is released

and its voltage rises above the VDISABLE trip point.

Figure 2 shows a typical power-up sequence in more detail.

The initialization starts at t0, when either VBIAS rises above

VPOR, or the COMP/EN pin is released (after POR). The

COMP/EN will be pulled up by an internal 20µA current

source, but the timing will not begin until the COMP/EN

exceeds the VDISABLE trip point (at t1). The external

capacitance of the disabling device, as well as the

compensation capacitors, will determine how quickly the

20µA current source will charge the COMP/EN pin. With

typical values, it should add a small delay compared to the

soft-start times. The COMP/EN will continue to ramp to ~1V.

From t1, there is a nominal 6.8ms delay, which allows the

VBIAS pin to exceed 6.5V (if rising up towards 12V), so that

the internal bias regulator can turn on cleanly. At the same

FN6306 Rev 5.00

April 15, 2010

Functionally, the soft-start internally ramps the reference on

the non-inverting terminal of the error amp from 0V to 0.6V in

a nominal 6.8ms. The output voltage will thus follow the

ramp, from zero to final value, in the same 6.8ms (the actual

ramp seen on the VOUT will be less than the nominal time),

due to some initialization timing, between t3 and t4).

The ramp is created digitally, so there will be 64 small

discrete steps. There is no simple way to change this ramp

rate externally, and it is the same for either frequency

version of the IC (300kHz or 600kHz).

After an initialization period (t3 to t4), the error amplifier

(COMP/EN pin) is enabled, and begins to regulate the

converter's output voltage during soft-start. The oscillator's

triangular waveform is compared to the ramping error

amplifier voltage. This generates LX pulses of increasing

width that charge the output capacitors. When the internally

generated soft-start voltage exceeds the reference voltage

(0.6V), the soft-start is complete and the output should be in

regulation at the expected voltage. This method provides a

rapid and controlled output voltage rise; there is no large

inrush current charging the output capacitors. The entire

start-up sequence from POR typically takes up to 17ms; up

Page 6 of 16

�ISL8105, ISL8105A

Overcurrent Protection (OCP)

VOUT OVER-CHARGED

PRE-BIASED

VVOUT

OUTPRE-BIASED

NORMAL

VV

OUTNORMAL

OUT

t0

t1t1

t2

t2

FIGURE 3. SOFT-START WITH PRE-BIAS

to 10.2ms for the delay and OCP sample and 6.8ms for the

soft-start ramp.

Figure 3 shows the normal curve in blue; initialization begins

at t0, and the output ramps between t1 and t2. If the output is

pre-biased to a voltage less than the expected value, as

shown by the red curve, the ISL8105, ISL8105A will detect

that condition. Neither MOSFET will turn on until the

soft-start ramp voltage exceeds the output; VOUT starts

seamlessly ramping from there. If the output is pre-biased to

a voltage above the expected value, as in the gray curve,

neither MOSFET will turn on until the end of the soft-start, at

which time it will pull the output voltage down to the final

value. Any resistive load connected to the output will help

pull down the voltage (at the RC rate of the R of the load and

the C of the output capacitance).

If the VIN for the synchronous buck converter is from a

different supply that comes up after VBIAS, the soft-start

would go through its cycle, but with no output voltage ramp.

When VIN turns on, the output would follow the ramp of the

VIN from zero up to the final expected voltage (at close to

100% duty cycle, with COMP/EN pin >4V). If VIN is too fast,

there may be excessive inrush current charging the output

capacitors (only the beginning of the ramp, from zero to

VOUT matters here). If this is not acceptable, then consider

changing the sequencing of the power supplies, or sharing

the same supply, or adding sequencing logic to the

COMP/EN pin to delay the soft-start until the VIN supply is

ready (see “Input Voltage Considerations” on page 9).

If the IC is disabled after soft-start (by pulling COMP/EN pin

low), and then enabled (by releasing the COMP/EN pin),

then the full initialization (including OCP sample) will take

place. However, there is no new OCP sampling during

overcurrent retries. If the output is shorted to GND during

soft-start, the OCP will handle it, as described in the next

section.

The overcurrent function protects the converter from a

shorted output by using the bottom-side MOSFET's

on-resistance, rDS(ON), to monitor the current. A resistor

(RBSOC) programs the overcurrent trip level (see “Typical

Application Diagram” on page 2). This method enhances the

converter's efficiency and reduces cost by eliminating a

current sensing resistor. If overcurrent is detected, the output

immediately shuts off, it cycles the soft-start function in a

hiccup mode (2 dummy soft-start time-outs, then up to one

real one) to provide fault protection. If the shorted condition

is not removed, this cycle will continue indefinitely.

Following POR (and 6.8ms delay), the ISL8105, ISL8105A

initiates the Overcurrent Protection sample and hold

operation. The BGATE driver is disabled to allow an internal

21.5µA current source to develop a voltage across RBSOC.

The ISL8105, ISL8105A samples this voltage (which is

referenced to the GND pin) at the BGATE/BSOC pin, and

holds it in a counter and DAC combination. This sampled

voltage is held internally as the Overcurrent Set Point, for as

long as power is applied, or until a new sample is taken after

coming out of a shut-down.

The actual monitoring of the bottom-side MOSFET's

on-resistance starts 200ns (nominal) after the edge of the

internal PWM logic signal (that creates the rising external

BGATE signal). This is done to allow the gate transition

noise and ringing on the LX pin to settle out before

monitoring. The monitoring ends when the internal PWM

edge (and thus BGATE) goes low. The OCP can be detected

anywhere within the above window.

If the regulator is running at high TGATE duty cycles (around

75% for 600kHz or 87% for 300kHz operation), then the

BGATE pulse width may not be wide enough for the OCP to

properly sample the rDS(ON). For those cases, if the BGATE

is too narrow (or not there at all) for 3 consecutive pulses,

then the third pulse will be stretched and/or inserted to the

425ns minimum width. This allows for OCP monitoring every

third pulse under this condition. This can introduce a small

pulse-width error on the output voltage, which will be

corrected on the next pulse; and the output ripple voltage will

have an unusual 3-clock pattern, which may look like jitter. If

the OCP is disabled (by choosing a too-high value of

RBSOC, or no resistor at all), then the pulse stretching

feature is also disabled. Figure 4 illustrates the BGATE pulse

width stretching, as the width gets smaller.

If the output is shorted to GND during soft-start, the OCP will

handle it, as described in the next section.

FN6306 Rev 5.00

April 15, 2010

Page 7 of 16

�ISL8105, ISL8105A

MOSFETs is typically in the 20mV to 120mV ballpark

(500 to 3000). If the voltage drop across RBSOC is set

too low, that can cause almost continuous OCP tripping and

retry. It would also be very sensitive to system noise and

inrush current spikes, so it should be avoided. The maximum

usable setting is around 0.2V across RBSOC (0.4V across

the MOSFET); values above that might disable the

protection. Any voltage drop across RBSOC that is greater

than 0.3V (0.6V MOSFET trip point) will disable the OCP.

The preferred method to disable OCP is simply to remove

the resistor, which will be detected as no OCP.

BGATE > 425ns

BGATE = 425ns

Note that conditions during power-up or during a retry may

look different than normal operation. During power-up in a

12V system, the IC starts operation just above 4V; if the

supply ramp is slow, the soft-start ramp might be over well

before 12V is reached. So with bottom-side gate drive

voltages, the rDS(ON) of the MOSFETs will be higher during

power-up, effectively lowering the OCP trip. In addition, the

ripple current will likely be different at lower input voltage.

BGATE < 425ns

Another factor is the digital nature of the soft-start ramp. On

each discrete voltage step, there is in effect a small load

transient, and a current spike to charge the output

capacitors. The height of the current spike is not controlled; it

is affected by the step size of the output, the value of the

output capacitors, as well as the IC error amp compensation.

So it is possible to trip the overcurrent with inrush current, in

addition to the normal load and ripple considerations.

BGATE