LD56050

Datasheet

500 mA ultra-low dropout linear regulator with bias supply

Features

•

•

•

•

•

•

•

•

•

•

•

•

•

Input voltage from 0.8 to 5.5 V

Bias supply pin

Ultra low-dropout voltage (80 mV typ. at 500 mA load)

Low ground current (27 μA typ. at no-load)

Output voltage tolerance: ± 1.5% overtemperature, 0.5% at 25 °C

500 mA guaranteed output current

50 mV output voltage step available from 0.8 V to 3.6 V

Logic-controlled electronic shutdown

Internal current limit with foldback

Thermal shutdown

Output active discharge function

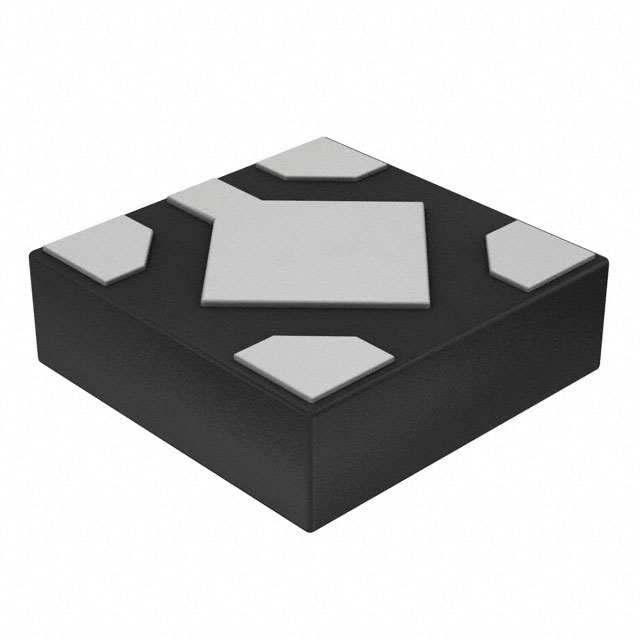

Available in DFN4 1.2 x 1.2 mm package

Temperature range: -40 °C to 85 °C

Applications

Maturity status link

LD56050

•

•

•

•

Mobile phones

Tablets

Battery-powered systems

Camera supply

Description

The LD56050 is a high accuracy voltage regulator, which provides 0.5 A of current. It

is equipped with an NMOS pass transistor, whose gate is biased by a dedicated pin,

thus allowing an ultra low-drop performance even at very low input voltages.

It is available in DFN4 1.2 x 1.2 package, allowing the maximum space saving.

The device is stabilized with a small ceramic capacitor on the output. The ultra lowdrop, low quiescent current and short circuit current foldback make the LD56050

suitable for low power battery-operated applications.

An enable logic control function puts the LD56050 in shutdown mode allowing a total

current consumption lower than 0.1 µA. Thermal protection is also included.

DS12441 - Rev 2 - April 2018

For further information contact your local STMicroelectronics sales office.

www.st.com

�LD56050

Diagram

1

Diagram

Figure 2. Block diagram

Thermal

Protection

V

BIAS

EN

VREF

V

IN

+

_

+

_

||

V

EN

OUT

*

GND

Note:

DS12441 - Rev 2

(*) Output discharge MOSFET.

page 2/21

�LD56050

Pin configuration

2

Pin configuration

Figure 3. Pin connection (top view)

4

3

5

1

2

Table 1. Pin description

Pin n° DFN8

Symbol

Function

1

VOUT

Output voltage

2

VBIAS

Bias supply input

3

EN

Enable pin logic input: low = shutdown, high = active.

Not internally pulled-up. Don't leave floating.

DS12441 - Rev 2

4

VIN

Input voltage (power element)

5

GND

Common ground

page 3/21

�LD56050

Typical application

3

Typical application

Figure 4. Typical application circuit

VIN

VOUT

VIN

CIN

VOUT

COUT

LD56050

VBIAS

VBIAS

CBIAS

VEN

EN

GND

Table 2. Typical bill of material

DS12441 - Rev 2

Symbol

Value

Description

CIN

1 µF

Output voltage

CBIAS

100 nF

Bias supply input

COUT

2.2 µF

Input voltage (power element)

Note

Ceramic type

page 4/21

�LD56050

Maximum ratings

4

Maximum ratings

Table 3. Absolute maximum ratings

Symbol

VIN

Input voltage

Value

Unit

- 0.3 to 7

V

- 0.3 to VIN + 0.3

V

- 0.3 to 7

V

VOUT

Output voltage

VEN

Enable input voltage

IOUT

Output current

Internally limited

mA

Power dissipation

Internally limited

mW

PD

Note:

Parameter

TSTG

Storage temperature range

- 40 to 150

°C

TOP

Operating junction temperature range

- 40 to 85

°C

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional

operation under these conditions is not implied. All values are referred to GND.

Table 4. Thermal data

Symbol

RthJA

Parameter

Thermal resistance junction-ambient

Value

Unit

170

°C/W

Table 5. ESD performance

Symbol

ESD

DS12441 - Rev 2

Parameter

ESD protection voltage

Test conditions

Value

Unit

HBM

2

kV

CDM

500

V

page 5/21

�LD56050

Electrical characteristics

5

Electrical characteristics

VBIAS = 2.7 V or VOUT + 1.6 V (whichever is greater); VIN = VOUT(NOM) + 0.3 V; IOUT = 1 mA; CIN = 1 µF, COUT =

2.2 µF; VEN = 1 V; typical values are at TJ = 25 °C; min./max. values are at -40 °C ≤ TJ ≤ 85 °C, unless otherwise

specified.

Table 6. Electrical characteristics

Symbol

Parameter

Test conditions

Min.

Typ. Max.

VIN

Operating input voltage

VBIAS

Operating bias voltage

VUVLO

BIAS undervoltage

lockout

VBIAS rising

1.6

Hysteresis

0.2

VOUT +

VDROP

5.5

V

VOUT ≤ 1 V

2.4

5.5

V

VOUT > 1 V

VOUT +

1.4

5.5

V

V

±0.5

VOUT(NOM) + 0.3 V ≤ VIN ≤ VOUT(NOM) + 1.0 V;

VOUT

Output voltage accuracy

Unit

-1.5

%

+1.5

%

2.7 V or VOUT(NOM) + 1.6 V (whichever is greater) ≤

VBIAS ≤ 5.5 V;

IOUT = 1 mA to 0.5 A; -40°C ≤ TJ ≤ 85°C

∆VOUT-IN

∆VOUT-BIAS

VIN static regulation(1)

VBIAS line

regulation(1)

∆VOUT

Static load regulation

VDROP

Dropout voltage

VDROP-BIAS

Dropout voltage

eN

Output noise voltage

SVRIN

VIN supply voltage

rejection

VOUT(NOM) + 0.3 V ≤ VIN ≤ 5.0 V, IOUT = 1 mA

0.02

0.1

%/V

2.7 V or VOUT(NOM) + 1.6 V (whichever is greater) ≤

VBIAS ≤ 5.5 V; IOUT = 1 mA

0.01

0.1

%/V

IOUT = 1 mA to 500 mA

1.5

IOUT = 0.15 A; VOUT = 97% of VOUT(NOM)

27

75

IOUT = 0.5 A; VOUT = 97% of VOUT(NOM)

80

250

VBIAS = VIN; IOUT = 0.5 A

0.9

1.5

VOUT(NOM) = 1.05 V; VIN = 1.5 V 10 Hz to 100 kHz,

IOUT = 1 mA

38

µVRMS

VIN = VOUT(NOM)+ 0.5 V +/- VRIPPLE

75

dB

76

dB

mV

mV

V

VRIPPLE = 0.2 V, freq=1 kHz, IOUT = 150 mA;

VBIAS = 2.7 V or VOUT + 1.6 V (whichever is

greater)

SVRBIAS

VBIAS supply voltage

rejection

VBIAS = 2.9 V or VOUT + 1.8 V (whichever is

greater) +/- VRIPPLE

VRIPPLE = 0.2 V freq = 1 kHz IOUT = 150 mA;

VIN = VOUT(NOM)+ 0.5 V

DS12441 - Rev 2

IBIAS

VBIAS operating current

IStandby-BIAS

VBIAS standby current

IStandby-IN

IOUT = 0 mA; VBIAS = 2.7 V

27

40

µA

VBIAS input current in OFF MODE: VEN = GND

0.03

1

µA

VIN standby current

VIN input current in OFF MODE: VEN = GND

0.03

1

µA

ILIM

Output current limit

VOUT= 0.9 x VOUT(NOM)

ISC

Short-circuit current

VOUT = 0 (foldback protection)

550

700 1000

mA

365

mA

500

page 6/21

�LD56050

Electrical characteristics

Symbol

Parameter

RON

Output voltage discharge

MOSFET

VEN

Typ. Max.

110

TON (2)

Turn on time

0.9

VEN = 5.5 V

400

VOUT(NOM) = 1.0 V

110

Thermal shutdown

160

Hysteresis

20

Output capacitor

1

2.2

Unit

Ω

0.4

Enable input logic high

Enable pin input current

COUT

Min.

Enable input logic low

IEN

TSHDN

Test conditions

V

nA

µs

°C

22

µF

1. Not applicable for VOUT(NOM) ≥ 5.0 V.

2. Turn-on time is time measured between the enable input just exceeding VEN high value and the output voltage just reaching

98% of its nominal value.

Note:

DS12441 - Rev 2

Values over the temperature range are guaranteed by design and correlation and not tested in production.

page 7/21

�LD56050

Application information

6

Application information

6.1

VBIAS pin voltage requirements

The bias input is the supply of the internal driving and control circuitry. In order to ensure proper biasing of the Nchannel power element, the bias pin must have a minimum voltage of 2.4 V and 1.6 V (typically) higher than the

output. If VIN supply voltage meets these requirements then the bias pin can be tied to VIN.

6.2

Output discharge function

The LD56050 integrates a MOSFET connected between VOUT and GND. This transistor is activated when the EN

pin goes to low logic level and has the function to quickly discharge the output capacitor when the device is

disabled by the user.

6.3

Short circuit and current limitation

The LD56050 is protected against short-circuit on the output. The load current is limited to the maximum value of

ILIM when VOUT is equal to 90% of its nominal value. If the VOUT decreases even more due to a lower output load

resistance then the foldback circuit starts operating limiting the current to ISC when VOUT = 0.

6.4

Thermal protection

Thermal protection acts when the junction temperature reaches 160 °C typical. At this point the output of the IC

shuts down. As soon as the junction temperature falls below the thermal hysteresis value the device starts

working again.

In order to calculate the maximum power that the device can dissipate, keeping the junction temperature below

the maximum operating value, the following formula is used:

PDMAX = (85 - TAMB) / RthJA

6.5

Input and output capacitors

The LD56050 requires external capacitors to assure the regulator control loop stability.

Any good quality ceramic capacitor can be used but, the X5R and the X7R are suggested since they guarantee a

very stable combination of capacitance and ESR across the temperature range.

Locating the input/output capacitors as close as possible to the relative pins is recommended. The LD56050

requires a VIN capacitor with a minimum value of 1 μF and a VBIAS capacitor of 100 nF minimum. These

capacitors must be located as close as possible to the input pins of the device and returned to a clean analog

ground.

The control loop is designed to be stable with any good quality output ceramic capacitor (such as X5R/X7R types)

with a minimum value of 1.0 μF and equivalent series resistance in the [3 – 300 mΩ] range. It is important to

highlight that the output capacitor must maintain its capacitance and ESR in the stable region over the full

operating temperature, load and input voltage ranges, to assure stability. Therefore, capacitance and ESR

variations must be taken into account in the design phase to ensure the device works in the expected stability

region.

DS12441 - Rev 2

page 8/21

�LD56050

Typical characteristics

7

Typical characteristics

(VOUT = 1.05 V ; CIN = 1 µF, COUT = 2.2 µF; VEN = 1 V; unless otherwise specified.)

Figure 5. VDROP vs. temperature (VBIAS = 2.7 V)

120

110

Io = 150 mA

100

Io = 500 mA

Figure 6. VDROP-BIAS vs. temperature (IOUT = 500 mA;

VBIAS = VIN)

1200

1150

1100

80

Dropout Voltage [mV]

Dropout Voltage [mV]

90

70

60

50

40

30

1050

1000

950

900

850

20

800

10

750

0

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

90

700

Junction Temperature [°C]

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

90

Junction Temperature [°C]

Figure 8. VDROP vs. IOUT (VBIAS = VIN)

1000

90

900

80

800

70

700

Dropout Voltage [mV]

Dropout Voltage [mV]

Figure 7. VDROP vs. IOUT (VBIAS = 2.7 V)

100

60

50

40

30

600

500

400

300

20

200

10

100

0

0

0

50

100

150

200

250

300

350

400

450

0

500

50

100

150

200

Figure 9. ISC vs. temperature (VIN = 1.4 V; VBIAS = 2.7 V)

300

350

400

450

500

Figure 10. ILIM vs. temperature (VIN = 1.4 V; VBIAS = 2.7 V)

800

400

780

395

760

390

740

385

Output Current Limit [mA]

Short Circuit Current [mA]

250

IOUT [mA]

IOUT [mA]

720

700

680

660

380

375

370

365

640

360

620

355

350

600

-40

-30

-20

-10

0

10

20

30

40

50

Junction Temperature [°C]

DS12441 - Rev 2

60

70

80

90

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

90

Junction Temperature [°C]

page 9/21

�LD56050

Typical characteristics

Figure 11. IBIAS vs. temperature (IOUT = 0 mA;

VBIAS = 2.7 V)

Figure 12. IBIAS vs. VIN (VBIAS = 2.7 V)

30

50

29.5

29

40

28.5

IBIAS Current [mA]

45

IBIAS [µA]

35

30

25

28

27.5

27

26.5

20

15

26

10

25.5

25

5

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

VIN [V]

0

-40

-30

-20

-10

0

10

20

30

40

50

60

70

80

90

Junction Temperature [°C]

Figure 13. SVRIN vs. frequency (VIN = 1.5 V; VBIAS = 2.7 V;

VOUT = 1.05 V)

Figure 14. SVRBIAS vs. frequency (VIN = 1.5 V;

VBIAS = 2.9 V; VOUT = 1.05 V)

120

120

110

Io=10 mA

Io=50 mA

110

Io=150 mA

100

100

90

90

Io=50 mA

Io=150 mA

80

SVR BIAS [dB]

80

SVR IN [dB]

Io=10 mA

70

60

50

40

70

60

50

40

30

30

20

20

10

10

0

10

0

10

100

1,000

10,000

100,000

1,000,000

100

1,000

10,000,000

10,000

100,000

1,000,000

10,000,000

Frequency [Hz]

Frequency [Hz]

Figure 15. Noise vs. frequency (VIN = 1.5 V; VBIAS = 2.7 V;

VOUT = 1.05 V)

Figure 16. Output voltage vs. junction temperature

1100

1090

10.00

Iout = 1 mA

1080

Io=10 mA

Output Voltage [mV]

Output Noise Density [µV/√(Hz)]

Io=1 mA

1.00

Iout = 0.5 A

1070

1060

1050

1040

1030

0.10

1020

1010

1000

-40

0.01

10

100

1,000

10,000

100,000

-30

-20

-10

0

10

20

30

40

50

60

70

80

90

Junction Temperature [°C]

Frequency [Hz]

DS12441 - Rev 2

page 10/21

�LD56050

Typical characteristics

Figure 17. Turn-on time (IOUT = 1 mA; VBIAS = 2.7 V)

Figure 18. Turn-on time at full load (IOUT = 500 mA;

VBIAS = 2.7 V)

Figure 19. Line transient (VBIAS = 2.7 V, VIN from 1.35 V to

2.35 V; tR = 5 µs)

Figure 20. Load transient (VBIAS = 2.7 V, VIN = 1.35 V; IOUT

1 to 500 mA)

DS12441 - Rev 2

page 11/21

�LD56050

Package information

8

Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK®

packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions

and product status are available at: www.st.com. ECOPACK® is an ST trademark.

DS12441 - Rev 2

page 12/21

�LD56050

DFN4 1.2 x 1.2 package information

8.1

DFN4 1.2 x 1.2 package information

Figure 21. DFN4 1.2 x 1.2 package outline

DS12441 - Rev 2

page 13/21

�LD56050

DFN4 1.2 x 1.2 package information

Table 7. DFN4 1.2 x 1.2 mechanical data

mm.

Dim.

Min.

Typ.

Max.

A

0.41

0.45

0.50

A1

0.00

0.02

0.05

A3

0.127 Ref.

b

0.25

0.30

D

1.20 BSC

E

1.20 BSC

e

0.80 BSC

0.35

D2

0.58

0.63

0.68

E2

0.58

0.63

0.68

K

0.20

--

--

L

0.25

0.30

0.35

N

4

aaa

0.05

bbb

0.10

ccc

0.10

ddd

0.05

eee

0.08

ND

2

Figure 22. DFN4 1.2 x 1.2 recommended footprint

Note:

DS12441 - Rev 2

All dimensions are in millimeters.

page 14/21

�LD56050

DFN4 1.2 x 1.2 package information

D0

1 .5 0

T

0.25 0.05

+ 0 .1

/ -0.

0

Y

P2 (I)

2.00 0.05

P0 (II)

4.00 0.1

E1

1.75 0.1

Figure 23. DFN4 1.2 x 1.2 tape and reel

D1

in

3°

Bo

R0.10

MAX

W

0m

F (III)

0 .8

Y

Ko

Ao

P1

SECTIO N Y-Y

SCALE 8 : 1

Ao

Bo

Ko

F

P1

W

Note:

DS12441 - Rev 2

1.40

1.40

0.64

3.50

4.00

8.00

+/- 0.05

+/- 0.05

+/- 0.05

+/- 0.05

+/- 0.10

+/- 0.10

(I)

(II)

(III)

(IV)

Measured from centreline of sprocket hole

to centreline of pocket.

Cumulative tolerance of 10 sprocket

holes is ± 0.20 .

Measured from centreline of sprocket

hole to centreline of pocket.

Other material available.

ALL DIMENSIONS IN MILLIMETRES UNLESS OTHERWISE STATED.

Pin 1 orientation: bottom-left.

page 15/21

�LD56050

Ordering information

9

Ordering information

Table 8. Order code

DS12441 - Rev 2

Order code

Discharge function

Output voltage (V)

Marking

LD56050DPU100R

Yes

1.00

UD

LD56050DPU105R

Yes

1.05

UA

LD56050DPU110R

Yes

1.10

UB

LD56050DPU115R

Yes

1.15

UE

LD56050DPU120R

Yes

1.20

UC

LD56050DPU150R

Yes

1.50

UF

page 16/21

�LD56050

Revision history

Table 9. Document revision history

Date

Revision

Changes

02-Feb-2018

1

Initial release.

09-Apr-2018

2

Updated: Figure 5. VDROP vs. temperature (VBIAS = 2.7 V) and Figure 6. VDROP-BIAS vs.

temperature (IOUT = 500 mA; VBIAS = VIN).

Added: Figure 16. Output voltage vs. junction temperature .

DS12441 - Rev 2

page 17/21

�LD56050

Contents

Contents

1

Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2

Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3

Typical application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

4

Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

5

Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

6

Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.1

VBIAS pin voltage requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.2

Output discharge function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.3

Short circuit and current limitation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.4

Thermal protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.5

Input and output capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

7

Typical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

8

Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

8.1

9

DFN4 1.2 x 1.2 package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

DS12441 - Rev 2

page 18/21

�LD56050

List of tables

List of tables

Table 1.

Table 2.

Table 3.

Table 4.

Table 5.

Table 6.

Table 7.

Table 8.

Table 9.

Pin description. . . . . . . . . . . . .

Typical bill of material . . . . . . . .

Absolute maximum ratings . . . .

Thermal data. . . . . . . . . . . . . .

ESD performance . . . . . . . . . .

Electrical characteristics . . . . . .

DFN4 1.2 x 1.2 mechanical data

Order code . . . . . . . . . . . . . . .

Document revision history . . . . .

DS12441 - Rev 2

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. 3

. 4

. 5

. 5

. 5

. 6

14

16

17

page 19/21

�LD56050

List of figures

List of figures

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Block diagram . . . . . . . . . . . . . . . . .

Pin connection (top view) . . . . . . . . . .

Typical application circuit . . . . . . . . . .

VDROP vs. temperature (VBIAS = 2.7 V)

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 15.

Figure 16.

Figure 17.

Figure 18.

Figure 19.

Figure 20.

Figure 21.

Figure 22.

Figure 23.

VDROP-BIAS vs. temperature (IOUT = 500 mA; VBIAS = VIN) . . . . . . .

VDROP vs. IOUT (VBIAS = 2.7 V) . . . . . . . . . . . . . . . . . . . . . . . . . .

VDROP vs. IOUT (VBIAS = VIN) . . . . . . . . . . . . . . . . . . . . . . . . . . .

ISC vs. temperature (VIN = 1.4 V; VBIAS = 2.7 V) . . . . . . . . . . . . . .

ILIM vs. temperature (VIN = 1.4 V; VBIAS = 2.7 V) . . . . . . . . . . . . . .

IBIAS vs. temperature (IOUT = 0 mA; VBIAS = 2.7 V) . . . . . . . . . . . .

IBIAS vs. VIN (VBIAS = 2.7 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SVRIN vs. frequency (VIN = 1.5 V; VBIAS = 2.7 V; VOUT = 1.05 V) . .

SVRBIAS vs. frequency (VIN = 1.5 V; VBIAS = 2.9 V; VOUT = 1.05 V) .

Noise vs. frequency (VIN = 1.5 V; VBIAS = 2.7 V; VOUT = 1.05 V) . . .

Output voltage vs. junction temperature . . . . . . . . . . . . . . . . . . .

Turn-on time (IOUT = 1 mA; VBIAS = 2.7 V) . . . . . . . . . . . . . . . . . .

Turn-on time at full load (IOUT = 500 mA; VBIAS = 2.7 V). . . . . . . . .

Line transient (VBIAS = 2.7 V, VIN from 1.35 V to 2.35 V; tR = 5 µs) .

Load transient (VBIAS = 2.7 V, VIN = 1.35 V; IOUT 1 to 500 mA) . . . .

DFN4 1.2 x 1.2 package outline . . . . . . . . . . . . . . . . . . . . . . . . .

DFN4 1.2 x 1.2 recommended footprint . . . . . . . . . . . . . . . . . . . .

DFN4 1.2 x 1.2 tape and reel . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. 9

. 9

. 9

. 9

. 9

10

10

10

10

10

10

11

11

11

11

13

14

15

DS12441 - Rev 2

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

2

3

4

9

page 20/21

�LD56050

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics – All rights reserved

DS12441 - Rev 2

page 21/21

�