TAR5S15U to TAR5S50U

TOSHIBA Bipolar Linear Integrated Circuit Silicon Monolithic

TAR5S15U to TAR5S50U

Point Regulators (Low-Dropout Regulators)

The TAR5SxxU Series consists of general-purpose bipolar LDO regulators

with an on/off control pin and features overtemperature and overcurrent

protection circuits.

Features

Low standby current

Overtemperature and overcurrent protections

Wide operating voltage range

High maximum output current

Low input-to-output voltage differential

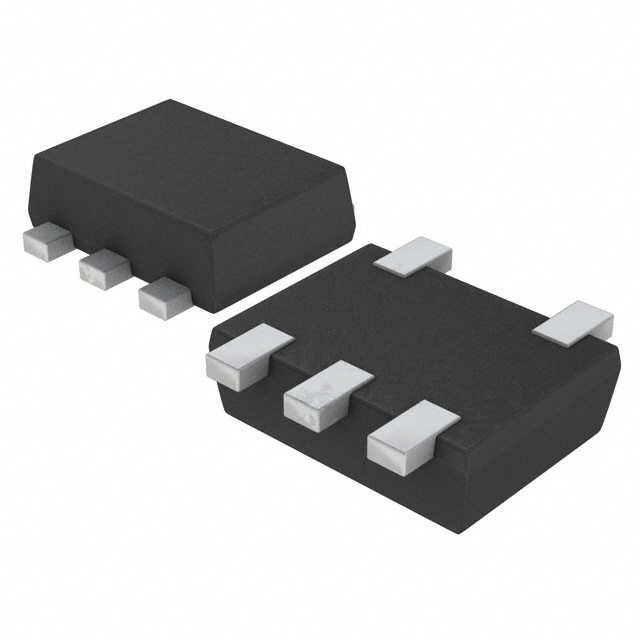

Small package (UFV package similar to SOT-353)

Allows use of ceramic capacitors as the input and output capacitors.

SON5-P-0202-0.65

(UFV)

Weight: 0.007 g (typ.)

Pin Assignment (Top View)

VIN

VOUT

5

4

1

2

CONTROL GND

3

NOISE

The overtemperature and overcurrent protection features are not intended to guarantee correct operation below the absolute

maximum ratings.

Do not use the TAR5SxxU under conditions where the absolute maximum ratings may be exceeded.

Start of commercial production

2001-08

© 2022

Toshiba Electronic Devices & Storage Corporation

1

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

List of Part Numbers and Markings

Part Marking

Part No.

Marking

Part No.

Marking

TAR5S15U

1V5

TAR5S33U

3V3

TAR5S16U

1V6

TAR5S34U

3V4

TAR5S17U

1V7

TAR5S35U

3V5

TAR5S18U

1V8

TAR5S36U

3V6

TAR5S19U

1V9

TAR5S37U

3V7

TAR5S20U

2V0

TAR5S38U

3V8

TAR5S21U

2V1

TAR5S39U

3V9

TAR5S22U

2V2

TAR5S40U

4V0

TAR5S23U

2V3

TAR5S41U

4V1

TAR5S24U

2V4

TAR5S42U

4V2

TAR5S25U

2V5

TAR5S43U

4V3

TAR5S26U

2V6

TAR5S44U

4V4

TAR5S27U

2V7

TAR5S45U

4V5

TAR5S28U

2V8

TAR5S46U

4V6

TAR5S29U

2V9

TAR5S47U

4V7

TAR5S30U

3V0

TAR5S48U

4V8

TAR5S31U

3V1

TAR5S49U

4V9

TAR5S32U

3V2

TAR5S50U

5V0

Example: TAR5S30U (3.0-V output)

3V0

Absolute Maximum Ratings (Ta 25°C)

Characteristics

Symbol

Rating

Unit

Supply Voltage

VIN

15

V

Output Current

IOUT

200

mA

Power Dissipation

PD

450

Operation Temp. Range

Topr

40 to 85

°C

Storage Temp. Range

Tstg

55 to 150

°C

(Note 1)

mW

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant

change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating

conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating

ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook (“Handling

Precautions”/“Derating Concept and Methods”) and individual reliability data (i.e. reliability test report and estimated

failure rate, etc).

Note 1: Mounted on a glass epoxy circuit board of 30 mm 30 mm; Pad dimension of 35 mm2

© 2022

Toshiba Electronic Devices & Storage Corporation

2

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

TAR5S15U to TAR5S22U

Electrical Characteristic (unless otherwise specified, VIN VOUT 1 V, IOUT 50 mA,

CIN 1 F, COUT 10 F, CNOISE 0.01 F, Tj 25°C)

Characteristics

Symbol

Test Condition

Min

Typ.

Max

Unit

Output voltage

VOUT

Line regulation

Reg・line

VOUT 1 V VIN 15 V,

IOUT 1 mA

3

15

mV

Load regulation

Reg・load

1 mA IOUT 150 mA

25

75

mV

IB1

IOUT 0 mA

170

IB2

IOUT 50 mA

550

850

VCT 0 V

0.1

A

Quiescent current

Standby current

IB (OFF)

Please refer to the Output Voltage Accuracy table.

A

Output noise voltage

VNO

VIN VOUT 1 V, IOUT 10 mA,

10 Hz f 100 kHz,

CNOISE 0.01 F, Ta 25°C

30

Vrms

Temperature coefficient

TCVO

40°C Topr 85°C

100

ppm/°C

2.4

15

V

70

dB

1.5

VIN

V

Input voltage

VIN

Ripple rejection

R.R.

Control voltage (ON)

VCT (ON)

Control voltage (OFF)

VCT (OFF)

VIN VOUT 1 V, IOUT 10 mA,

CNOISE 0.01 F, f 1 kHz,

VRipple 500 mVp-p, Ta 25°C

0.4

V

Control current (ON)

ICT (ON)

VCT 1.5 V

3

10

A

Control current (OFF)

ICT (OFF)

VCT 0 V

0

0.1

A

TAR5S23U to TAR5S50U

Electrical Characteristic (unless otherwise specified, VIN VOUT 1 V, IOUT 50 mA,

CIN 1 F, COUT 10 F, CNOISE 0.01 F, Tj 25°C)

Characteristics

Symbol

Test Condition

Min

Typ.

Max

Unit

Output voltage

VOUT

Line regulation

Reg・line

VOUT 1 V VIN 15 V,

IOUT 1 mA

3

15

mV

Load regulation

Reg・load

1 mA IOUT 150 mA

25

75

mV

IB1

IOUT 0 mA

170

IB2

IOUT 50 mA

550

850

VCT 0 V

0.1

A

VIN VOUT 1 V, IOUT 10 mA,

10 Hz f 100 kHz,

CNOISE 0.01 F, Ta 25°C

30

Vrms

130

200

mV

100

ppm/°C

VOUT

0.2 V

15

V

70

dB

Quiescent current

Standby current

IB (OFF)

Output noise voltage

Dropout volatge

VNO

Please refer to the Output Voltage Accuracy table.

VIN VOUT IOUT 50 mA

Temperature coefficient

TCVO

Input voltage

VIN

Ripple rejection

R.R.

40°C Topr 85°C

VIN VOUT 1 V, IOUT 10 mA,

CNOISE 0.01 F, f 1 kHz,

VRipple 500 mVp-p, Ta 25°C

A

Control voltage (ON)

VCT (ON)

1.5

VIN

V

Control voltage (OFF)

VCT (OFF)

0.4

V

Control current (ON)

ICT (ON)

VCT 1.5 V

3

10

A

Control current (OFF)

ICT (OFF)

VCT 0 V

0

0.1

A

© 2022

Toshiba Electronic Devices & Storage Corporation

3

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

Output Voltage Accuracy

(VIN VOUT 1 V, IOUT 50 mA, CIN 1 F, COUT 10 F, CNOISE 0.01 F, Tj 25°C)

Part No.

Symbol

Min

Typ.

Max

TAR5S15U

1.44

1.5

1.56

TAR5S16U

1.54

1.6

1.66

TAR5S17U

1.64

1.7

1.76

TAR5S18U

1.74

1.8

1.86

TAR5S19U

1.84

1.9

1.96

TAR5S20U

1.94

2.0

2.06

TAR5S21U

2.04

2.1

2.16

TAR5S22U

2.14

2.2

2.26

TAR5S23U

2.24

2.3

2.36

TAR5S24U

2.34

2.4

2.46

TAR5S25U

2.43

2.5

2.57

TAR5S26U

2.53

2.6

2.67

TAR5S27U

2.63

2.7

2.77

TAR5S28U

2.73

2.8

2.87

TAR5S29U

2.83

2.9

2.97

TAR5S30U

2.92

3.0

3.08

TAR5S31U

3.02

3.1

3.18

3.12

3.2

3.28

3.21

3.3

3.39

TAR5S34U

3.31

3.4

3.49

TAR5S35U

3.41

3.5

3.59

TAR5S36U

3.51

3.6

3.69

TAR5S37U

3.6

3.7

3.8

TAR5S38U

3.7

3.8

3.9

TAR5S39U

3.8

3.9

4.0

TAR5S40U

3.9

4.0

4.1

TAR5S41U

3.99

4.1

4.21

TAR5S42U

4.09

4.2

4.31

TAR5S43U

4.19

4.3

4.41

TAR5S44U

4.29

4.4

4.51

TAR5S45U

4.38

4.5

4.62

TAR5S46U

4.48

4.6

4.72

TAR5S47U

4.58

4.7

4.82

TAR5S48U

4.68

4.8

4.92

TAR5S49U

4.77

4.9

5.03

TAR5S50U

4.87

5.0

5.13

TAR5S32U

TAR5S33U

VOUT

© 2022

Toshiba Electronic Devices & Storage Corporation

Unit

V

4

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

Application Notes

1. Recommended Application Circuit

VOUT

1 F

10 F

VIN

5

2

CONTROL GND

CONTROL

Operation

HIGH

ON

LOW

OFF

3

0.01 F

1

4

NOISE

A noise-damping capacitor should be connected between the NOISE pin and GND

for stable operation. The recommended value is higher than 0.0047 F.

The above figure shows the recommended application circuit for the TAR5SxxU. Capacitors should be connected to VIN

and VOUT for input/output stabilization.

If on/off control is not required, it is recommended to connect the CONTROL pin (pin 1) to VCC.

2. Power Dissipation

The power dissipation rating (450 mW) is measured on a board shown below. More power can be safely dissipated by

reducing the input voltage, output current and/or ambient temperature. It is recommended to use the TAR5SxxU at 70% to

80% of the absolute maximum power dissipation.

Thermal Resistance Evaluation Board

VIN

CIN

VOUT

COUT

CNOISE

Material: Glass epoxy

CONTROL GND

NOISE

© 2022

Toshiba Electronic Devices & Storage Corporation

Dimensions: 30 mm 30 mm

Copper pad area: 35 mm2, t 0.8 mm

5

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

3. Ripple Rejection

The TAR5SxxU feature a good power supply ripple rejection and input transient response, making them an ideal solution

for the RF block of cell phones.

Ripple Rejection f

TAR5S28U Input Transient Response

80

Ripple rejection

(dB)

70

10 F

60

Input voltage

3.4 V

50

2.2 F

40

3.1 V

1 F

2.8 V

30

20

10

0

10

100

Output voltage

VIN 4.0 V, CNOISE 0.01 F,

Ta 25°C, CIN 1 F,

CIN 1 F, VRipple 500 mVpp,

COUT 10 F, CNOISE 0.01 F,

IOUT 10 mA, Ta 25°C

VIN: 3.4 V 3.1 V, IOUT 50 mA

1k

10 k

Frequency f

0

100 k 300 k

1

2

3

4

5

6

7

8

9

10

Time t (ms)

(Hz)

4. NOISE Pin

The TAR5SxxU have a pin named NOISE. To reduce the output noise and ensure stable operation, a capacitor should be

inserted between the NOISE pin and GND. The capacitance value should be at least 0.0047 F.

The output voltage rise time varies with the value of the capacitor connected to the NOISE pin.

CNOISE VN

Turn On Waveform

(V)

50

Output noise voltage VN

CIN 1 F, COUT 10 F,

40

IOUT 10 mA, Ta 25°C

Control voltage

VCT (ON) (V)

60

20

TAR5S50

TAR5S30

10

0

0.001

Output voltage

VOUT (V)

30

TAR5S15

0.01

0.1

NOISE capacitance

CNOISE

Control voltage waveform

1

0

CNOISE 0.01 F

3

Output voltage waveform

1 F

2

0.33 F

0.1 F

1

CIN 1 F, COUT 10 F,

0

10

1.0

IOUT 50 mA, Ta 25°C

0

10

20

30

40

50

60

70

80

90

Time t (ms)

(F)

© 2022

Toshiba Electronic Devices & Storage Corporation

2

6

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

5. Examples of Performance Curves When Ceramic Capacitors Are Used

The stable operating area (SOA) is an area where the output voltage does not go into oscillation. The following figures

represent the SOA obtained using an evaluation circuit shown below. The SOA is determined by the equivalent series

resistance (ESR) of the output capacitor and the output current. The TAR5SxxU provide stable operation even when a

ceramic capacitor is used as the output capacitor.

If the ripple frequency is 30 kHz or greater, the ripple rejection characteristics differ, depending on the type of the output

capacitor (ceramic or tantalum) as shown by the bottom figure on this page.

It is recommended to verify that TAR5SxxU operate properly under the intended conditions of use.

Examples of Safe Operating Area Characteristics

(TAR5S15U) Stable Operating Area

(TAR5S50U) Stable Operating Area

ESR

10

1

Stable Operating Area

@VIN 2.5 V, CNOISE 0.01 F,

0.1

CIN 1 F, COUT 1 F to 10 F,

Ta 25°C

0.02

0

20

40

60

80

100

Output current IOUT

120

Equivalent series resistance

ESR

Equivalent series resistance

()

100

()

100

10

Stable Operating Area

1

CIN 1 F, COUT 1 F to 10 F,

Ta 25°C

0.02

0

140 150

@VIN 6.0 V, CNOISE 0.01 F,

0.1

(mA)

20

40

60

80

Output current

100

IOUT

120

140 150

(mA)

(TAR5S28U) Stable Operating Area

Circuit for Stable Operating Area Evaluation

Equivalent series resistance

ESR

()

100

CONTROL

10

CNOISE 0.01 F

TAR5S**U

Stable Operating Area

VIN VOUT

1V

1

CIN

Ceramic

GND

COUT

Ceramic

ROUT

ESR

@VIN 3.8 V, CNOISE 0.01 F,

0.1

CIN 1 F, COUT 1 F to 10 F,

Ta 25°C

0.02

0

20

40

60

80

Output current

100

IOUT

120

140 150

Capacitors used for evaluation

CIN: Murata GRM40B105K

COUT: Murata GRM40B105K / GRM40B106K

(mA)

Ripple Rejection Characteristic (f 10 kHz to 300 kHz)

(TAR5S30U) Ripple Rejection – f

70

Ceramic 10 F

Tantalum10 F

(dB)

50

Ripple rejection

60

40

Ceramic

2.2 F

Ceramic

1 F

Tantalum 2.2 F

Tantalum 1 F

30

20

@VIN 4.0 V, CNOISE 0.01 F,

10

CIN 1 F, VRipple 500 mVp-p,

IOUT 10 mA, Ta 25°C

0

10 k

100 k

Frequency f

300 k

1000 k

(Hz)

© 2022

Toshiba Electronic Devices & Storage Corporation

7

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S15U)

IOUT – VOUT

(TAR5S18U)

1.6

IOUT – VOUT

1.9

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

VIN 2.8 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 2.5 V, CIN 1 F, COUT 10 F,

Ta 85°C

25

Output voltage

1.8

Output voltage

1.5

Ta 85°C

25

40

1.4

0

50

100

Output current

(TAR5S20U)

IOUT

1.7

0

150

(mA)

50

100

Output current

IOUT – VOUT

(TAR5S21U)

2.1

IOUT

150

(mA)

IOUT – VOUT

2.2

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

VIN 3.1 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 3.0 V, CIN 1 F, COUT 10 F,

Ta 85°C

Ta 85°C

Output voltage

2.1

Output voltage

2.0

25

40

1.9

0

50

100

Output current

(TAR5S22U)

IOUT

25

40

2.0

0

150

(mA)

50

100

Output current

(TAR5S23U)

IOUT – VOUT

2.3

IOUT

150

(mA)

IOUT – VOUT

2.4

VIN 3.3 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

(V)

VIN 3.2 V, CIN 1 F, COUT 10 F,

Ta 85°C

Output voltage

Output voltage

2.2

2.1

0

40

25

40

50

Output current

100

IOUT

2.3

25

40

2.2

0

150

50

Output current

(mA)

© 2022

Toshiba Electronic Devices & Storage Corporation

Ta 85°C

8

100

IOUT

150

(mA)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S25U)

(TAR5S27U)

IOUT – VOUT

2.6

IOUT – VOUT

2.8

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

VIN 3.7 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 2.6 V, CIN 1 F, COUT 10 F,

Ta 85°C

Output voltage

2.7

Output voltage

2.5

Ta 85°C

25

40

2.4

0

50

100

Output current

(TAR5S28U)

IOUT

25

40

2.6

0

150

(mA)

50

100

Output current

IOUT – VOUT

(TAR5S29U)

2.9

IOUT

150

(mA)

IOUT – VOUT

3

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

VIN 3.9 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 3.8 V, CIN 1 F, COUT 10 F,

Ta 85°C

Ta 85°C

Output voltage

2.9

Output voltage

2.8

25

40

2.7

0

50

100

Output current

(TAR5S30U)

IOUT

40

2.8

0

150

(mA)

50

100

Output current

IOUT – VOUT

(TAR5S31U)

3.1

IOUT

150

(mA)

IOUT – VOUT

3.2

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

VIN 4.1 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 4.0 V, CIN 1 F, COUT 10 F,

Ta 85°C

Ta 85°C

Output voltage

3.1

Output voltage

3.0

2.9

0

25

25

40

50

Output current

100

IOUT

3.0

0

150

(mA)

© 2022

Toshiba Electronic Devices & Storage Corporation

25

40

50

Output current

9

100

IOUT

150

(mA)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S32U)

IOUT – VOUT

(TAR5S33U)

3.3

VIN 4.3 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

VOUT

VOUT

(V)

(V)

VIN 4.2 V, CIN 1 F, COUT 10 F,

Ta 85°C

Output voltage

Output voltage

3.2

25

40

3.1

0

50

100

Output current

(TAR5S35U)

IOUT

3.3

25

40

(mA)

50

100

Output current

IOUT – VOUT

(TAR5S45U)

IOUT

150

(mA)

IOUT – VOUT

4.6

VIN 5.5 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

VOUT

(V)

(V)

VIN 4.5 V, CIN 1 F, COUT 10 F,

VOUT

Ta 85°C

3.5

Output voltage

Output voltage

Ta 85°C

3.2

0

150

3.6

25

40

3.4

0

50

100

Output current

(TAR5S48U)

IOUT

Ta 85°C

4.5

25

40

4.4

0

150

(mA)

50

100

Output current

IOUT – VOUT

(TAR5S50U)

4.9

IOUT

150

(mA)

IOUT – VOUT

5.1

VIN 6.0 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 5.8 V, CIN 1 F, COUT 10 F,

VOUT

(V)

VOUT

Ta 85°C

4.8

Output voltage

Output voltage

IOUT – VOUT

3.4

25

40

4.7

0

50

Output current

100

IOUT

5.0

25

40

4.9

0

150

50

Output current

(mA)

© 2022

Toshiba Electronic Devices & Storage Corporation

Ta 85°C

10

100

IOUT

150

(mA)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S15U)

IB – VIN

(TAR5S18U)

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

IB – VIN

10

5

IOUT 150 mA

IOUT 150 mA

100

100

1

50

0

0

5

10

Input voltage

(TAR5S20U)

VIN

10

Input voltage VIN

IB – VIN

(TAR5S21U)

15

(V)

IB – VIN

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

5

(V)

10

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

(TAR5S22U)

VIN

50

1

10

Input voltage

0

0

15

5

(V)

IB – VIN

(TAR5S23U)

1

10

Input voltage VIN

10

15

(V)

IB – VIN

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

1

50

0

0

15

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

Input voltage

10

VIN

50

1

0

0

15

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

5

10

Input voltage VIN

11

1

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S25U)

IB – VIN

(TAR5S27U)

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

IB – VIN

10

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

10

Input voltage

(TAR5S28U)

1

VIN

10

Input voltage VIN

IB – VIN

(TAR5S29U)

15

(V)

IB – VIN

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

5

(V)

10

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

(TAR5S30U)

50

1

10

Input voltage VIN

0

0

15

5

IB – VIN

(TAR5S31U)

1

10

Input voltage VIN

(V)

10

15

(V)

IB – VIN

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

1

50

0

0

15

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

Input voltage

10

VIN

50

1

0

0

15

10

Input voltage VIN

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

5

12

1

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S32U)

IB – VIN

(TAR5S33U)

10

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

Pulse width 1 ms

IB

(mA)

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

5

Bias current

Bias current

IB – VIN

10

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

10

Input voltage

(TAR5S35U)

VIN

0

0

15

(V)

(TAR5S45U)

IB – VIN

10

15

(V)

IB – VIN

10

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

Pulse width 1 ms

(mA)

CIN 1 F, COUT 10 F, CNOISE 0.01 F

IB

5

Bias current

Bias current

5

Input voltage VIN

10

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

(TAR5S48U)

1

10

Input voltage

VIN

50

0

0

15

5

(TAR5S50U)

IB – VIN

1

10

Input voltage VIN

(V)

10

15

(V)

IB – VIN

10

CNOISE 0.01 F

Pulse width 1 ms

Pulse width 1 ms

IB

(mA)

CIN 1 F, COUT 10 F,

CNOISE 0.01 F

(mA)

CIN 1 F, COUT 10 F,

IB

5

Bias current

Bias current

1

50

1

5

IOUT 150 mA

IOUT 150 mA

100

100

50

0

0

5

Input voltage

10

VIN

1

50

0

0

15

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

5

Input voltage VIN

13

10

1

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S15U)

6

VOUT – VIN

(TAR5S18U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

2

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

1

2

1

0

0

5

10

Input voltage

(TAR5S20U)

6

VIN

0

0

15

(V)

5

10

Input voltage VIN

VOUT – VIN

(TAR5S21U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

15

(V)

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

2

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

1

2

1

0

0

5

10

Input voltage

(TAR5S22U)

6

VIN

0

0

15

(V)

5

10

Input voltage VIN

VOUT – VIN

(TAR5S23U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

15

(V)

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

2

1

0

0

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

2

1

5

Input voltage

10

VIN

0

0

15

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

5

Input voltage VIN

14

10

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S25U)

6

VOUT – VIN

(TAR5S27U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

2

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

1

2

1

0

0

5

10

Input voltage

(TAR5S28U)

6

VIN

0

0

15

(V)

5

10

Input voltage

VOUT – VIN

(TAR5S29U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

VIN

15

(V)

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

2

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

1

2

1

0

0

5

10

Input voltage

(TAR5S30U)

6

VIN

0

0

15

(V)

5

10

Input voltage

VOUT – VIN

(TAR5S31U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

VIN

15

(V)

VOUT – VIN

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

2

1

0

0

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

5

(V)

5

3

2

1

5

Input voltage

10

VIN

0

0

15

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

5

Input voltage

15

10

VIN

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S32U)

6

VOUT – VIN

(TAR5S33U)

6

IOUT 1 mA, CIN 1 F, COUT 10 F,

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

5

3

2

1

VOUT

4

4

Output voltage

(V)

5

(V)

3

2

1

0

0

5

10

Input voltage

(TAR5S35U)

VIN

0

0

15

(V)

5

10

Input voltage VIN

VOUT – VIN

(TAR5S45U)

5

5

15

(V)

VOUT – VIN

3

2

1

VOUT

VOUT

4

Output voltage

(V)

6

(V)

6

4

Output voltage

VOUT

Output voltage

VOUT – VIN

3

2

1

IOUT 1 mA, CIN 1 F, COUT 10 F,

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

0

0

5

10

Input voltage

(TAR5S48U)

VIN

CNOISE 0.01 F, Pulse width 1 ms

0

0

15

(V)

5

10

Input voltage VIN

VOUT – VIN

(TAR5S50U)

5

5

VOUT – VIN

2

1

VOUT

3

4

Output voltage

VOUT

4

Output voltage

(V)

6

(V)

6

15

(V)

3

2

1

IOUT 1 mA, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

0

0

5

Input voltage

10

VIN

CNOISE 0.01 F, Pulse width 1 ms

0

0

15

(V)

© 2022

Toshiba Electronic Devices & Storage Corporation

IOUT 1 mA, CIN 1 F, COUT 10 F,

5

Input voltage VIN

16

10

15

(V)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S15U)

VOUT – Ta

(TAR5S18U)

1.6

VIN 2.5 V, CIN 1 F, COUT 10 F,

VIN 2.8 V, CIN 1 F, COUT 10 F,

(V)

100

150

1.45

1.4

50

25

0

25

Ambient temperature

(TAR5S20U)

1.85

VOUT

IOUT 50 mA

1.5

Output voltage

Output voltage

CNOISE 0.01 F, Pulse width 1 ms

1.55

VOUT

(V)

CNOISE 0.01 F, Pulse width 1 ms

50

75

IOUT 50 mA

1.8

100

150

1.75

1.7

50

100

Ta (°C)

25

0

VOUT – Ta

(TAR5S21U)

100

Ta (°C)

VOUT – Ta

(V)

CNOISE 0.01 F, Pulse width 1 ms

Output voltage

IOUT 50 mA

2.0

150

100

1.95

1.9

50

25

0

25

Ambient temperature

(TAR5S22U)

2.15

VOUT

2.05

VOUT

(V)

75

VIN 3.1 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

Output voltage

50

2.2

VIN 3.0 V, CIN 1 F, COUT 10 F,

50

75

IOUT 50 mA

2.1

Ta (°C)

25

0

VOUT – Ta

(TAR5S23U)

100

Ta (°C)

VOUT – Ta

(V)

CNOISE 0.01 F, Pulse width 1 ms

150

100

25

0

2.35

VOUT

IOUT 50 mA

Output voltage

VOUT

75

VIN 3.3 V, CIN 1 F, COUT 10 F,

2.25

2.1

50

50

2.4

CNOISE 0.01 F, Pulse width 1 ms

2.15

25

Ambient temperature

VIN 3.2 V, CIN 1 F, COUT 10 F,

2.2

150

100

2.05

2.0

50

100

2.3

(V)

25

Ambient temperature

2.1

Output voltage

VOUT – Ta

1.9

25

Ambient temperature

50

75

IOUT 50 mA

150

100

2.25

2.2

50

100

Ta (°C)

© 2022

Toshiba Electronic Devices & Storage Corporation

2.3

25

0

25

Ambient temperature

17

50

75

100

Ta (°C)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S25U)

VOUT – Ta

(TAR5S27U)

2.6

VIN 3.5 V, CIN 1 F, COUT 10 F,

VIN 3.7 V, CIN 1 F, COUT 10 F,

(V)

100

150

2.45

2.4

50

25

2.75

VOUT

IOUT 50 mA

2.5

Output voltage

Output voltage

CNOISE 0.01 F, Pulse width 1 ms

2.55

VOUT

(V)

CNOISE 0.01 F, Pulse width 1 ms

0

25

Ambient temperature

(TAR5S28U)

50

75

2.7

IOUT 50 mA

Ta (°C)

25

0

25

Ambient temperature

VOUT – Ta

(TAR5S29U)

50

75

100

Ta (°C)

VOUT – Ta

3.0

VIN 3.8 V, CIN 1 F, COUT 10 F,

VIN 3.9 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

CNOISE 0.01 F, Pulse width 1 ms

2.95

VOUT

2.85

VOUT

(V)

150

100

2.65

2.6

50

100

2.9

IOUT 50 mA

2.8

Output voltage

Output voltage

VOUT – Ta

2.8

150

100

2.75

2.7

50

25

0

25

Ambient temperature

(TAR5S30U)

50

75

Ta (°C)

25

0

(TAR5S31U)

VOUT – Ta

25

50

75

100

VOUT – Ta

3.2

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 4.1 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 4 V, CIN 1 F, COUT 10 F,

VOUT

3.15

VOUT

3.1

IOUT 50 mA

150

100

25

0

IOUT 50 mA

Output voltage

Output voltage

2.9

50

150

Ambient temperature Ta (°C)

3.05

2.95

100

2.85

2.8

50

100

3.1

3.0

IOUT 50 mA

2.9

3.05

25

Ambient temperature

50

75

3.0

50

100

Ta (°C)

© 2022

Toshiba Electronic Devices & Storage Corporation

150

100

25

0

25

Ambient temperature

18

50

75

100

Ta (°C)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

(TAR5S32U)

VOUT – Ta

(TAR5S33U)

3.3

VOUT – Ta

3.4

VIN 4.2 V, CIN 1 F, COUT 10 F,

VIN 4.3 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

(V)

CNOISE 0.01 F, Pulse width 1 ms

3.35

VOUT

VOUT

3.25

Output voltage

3.15

150

100

3.1

50

25

Output voltage

IOUT 50 mA

3.2

0

25

50

Ambient temperature

(TAR5S35U)

75

3.3

IOUT 50 mA

3.2

50

100

150

100

3.25

Ta (°C)

25

0

25

Ambient temperature

VOUT – Ta

(TAR5S45U)

3.6

50

75

100

Ta (°C)

VOUT – Ta

4.6

VIN 5.5 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 4.5 V, CIN 1 F, COUT 10 F,

4.55

VOUT

3.55

4.5

Output voltage

3.5

IOUT 50 mA

3.45

4.45

150

100

3.4

50

25

0

25

Ambient temperature

(TAR5S48U)

50

75

25

Ta (°C)

0

25

Ambient temperature

(TAR5S50U)

50

75

100

Ta (°C)

VOUT – Ta

5.1

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 6 V, CIN 1 F, COUT 10 F,

CNOISE 0.01 F, Pulse width 1 ms

(V)

VIN 5.8 V, CIN 1 F, COUT 10 F,

VOUT

5.05

VOUT

4.85

Output voltage

4.8

Output voltage

150

100

4.4

50

100

VOUT – Ta

4.9

IOUT 50 mA

IOUT 50 mA

4.75

5

IOUT 50 mA

4.95

150

150

100

4.7

50

25

100

0

25

Ambient temperature

50

75

4.9

50

100

Ta (°C)

© 2022

Toshiba Electronic Devices & Storage Corporation

25

0

25

Ambient temperature

19

50

75

100

Ta (°C)

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

IB – Ta

(TAR5S23U~TAR5S50U)

3

VIN VOUT 1 V, CIN 1 F,

(V)

IOUT 150 mA

0.5

Dropout voltage VIN - VOUT

Pulse width 1 ms

2

1.5

Bias current

CNOISE 0.01 F

Pulse width 1 ms

0.4

IB

(mA)

CIN 1 F, COUT 10 F,

COUT 10 F, CNOISE 0.01 F

2.5

IOUT 150 mA

0.3

100

1

100

0.2

50

0.5

50

0.1

10

10

1

0

50

25

0

25

50

Ambient temperature

75

1

0

50

100

25

0

25

85

Ta (°C)

VIN VOUT 1 V,

Ta 25°C

CNOISE 0.01 F

40

Pulse width 1 ms

(mA)

(V)

100

CIN 1 F, COUT 10 F,

2.0

Ta 25°C

1.5

Bias current

IB

0.3

40

0.2

85

1.0

0.1

0.5

0

0

50

100

Output current

IOUT

0

0

150

50

Output current

(mA)

Turn On Waveform

Control voltage

VCT (ON) (V)

3

2

Control voltage waveform

1

0

Output voltage

VOUT (V)

Ta 25°C

85

VIN VOUT 1 V,

VCT (ON) 0 1.5 V, CIN 1 F,

0

(mA)

VIN VOUT 1 V,

VCT (ON) 1.5 0 V, CIN 1 F,

2

COUT 10 F, CNOISE 0.01 F

1

Control voltage waveform

0

3

2

1

IOUT

150

Output voltage waveform

40

3

100

Turn Off Waveform

3

Control voltage

VCT (ON) (V)

75

IB – IOUT

2.5

CIN 1 F, COUT 10 F,

CNOISE 0.01F

Pulse width 1 ms

Dropout voltage VIN - VOUT

0.4

50

Ambient temperature

Ta (°C)

(TAR5S23U~TAR5S50U) VIN - VOUT – IOUT

0.5

Output voltage

VOUT (V)

VIN - VOUT – Ta

0.6

2

1

Output voltage waveform

0

COUT 10 F, CNOISE 0.01 F

0

1

Time

0

t (ms)

© 2022

Toshiba Electronic Devices & Storage Corporation

1

Time t (ms)

20

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

Ripple Rejection – f

VN – f

80

10

TAR5S25U (2.5 V)

VIN VOUT 1 V, IOUT 10 mA, CIN 1 F,

COUT 10 F, CNOISE 0.01 F,

)

TAR5S30U (3.0 V)

TAR5S15U (1.5 V)

70

1

(dB)

60

Ripple rejection

Output noise voltage VN

(V/

10 Hz f 100 kHz, Ta 25°C

0.1

0.01

TAR5S45U (4.5 V)

50

TAR5S50U (5.0 V)

40

TAR5S35U (3.5 V)

30

20

VIN VOUT 1 V, IOUT 10 mA, CIN 1 F,

10 COUT 10 F, CNOISE 0.01 F,

VRipple 500 mVp-p, Ta 25°C

0.001

10

100

1k

Frequency f

10 k

0

10

100 k

100

1k

Frequency f

(Hz)

10 k

100 k

1000 k

(Hz)

PD – Ta

400

Power dissipation

PD

(mW)

500

300

200

Circuit board material: glass epoxy, Circuit

board dimention:

30 mm 30 mm,

pad area: 35 mm2 (t 0.8 mm)

100

40

0

40

Ambient temperature

80

120

Ta (°C)

The above characteristics curves are presented for reference only and not guaranteed by production test,

unless otherwise noted.

© 2022

Toshiba Electronic Devices & Storage Corporation

21

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

Package Dimensions

2.0±0.1

SON5-P-0202-0.65

Weight: 0.007 g (typ.)

© 2022

Toshiba Electronic Devices & Storage Corporation

22

2022-08-01

Rev.1.0

�TAR5S15U to TAR5S50U

RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as “TOSHIBA”.

Hardware, software and systems described in this document are collectively referred to as “Product”.

TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's

written permission, reproduction is permissible only if reproduction is without alteration/omission.

Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for

complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which

minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to

property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the

Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information,

including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and

conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product

will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited

to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the

applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any

other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO

LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY

CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation,

equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment,

equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or

explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE,

TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our

website.

Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any

infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any

intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR

PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER,

INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING

WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2)

DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR

INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE,

ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for

the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass

destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations

including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export

and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and

regulations.

Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please

use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including

without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT

OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

https://toshiba.semicon-storage.com/

© 2022

Toshiba Electronic Devices & Storage Corporation

23

2022-08-01

Rev.1.0

�