ATSAMB11XR/ZR

Ultra-Low Power Bluetooth® Low Energy SiP/Module

Introduction

The ATSAMB11-XR2100A is an ultra-low power Bluetooth Low Energy (BLE) 5.0 System in a Package

(SiP) with Integrated MCU, transceiver, modem, MAC, PA, Transmit/Receive (T/R) switch, and Power

®

Management Unit (PMU). It is a standalone Cortex -M0 applications processor with embedded Flash

memory and BLE connectivity.

The Bluetooth SIG-qualified Bluetooth Low Energy protocol stack is stored in a dedicated ROM. The

firmware includes L2CAP service layer protocols, Security Manager, Attribute protocol (ATT), Generic

Attribute Profile (GATT), and the Generic Access Profile (GAP). Additionally, example applications are

available for application profiles such as proximity, thermometer, heart rate and blood pressure, and many

others.

The ATSAMB11-XR2100A provides a compact footprint and various embedded features, such as a 26

MHz crystal oscillator.

The ATSAMB11-ZR210CA is a fully certified module that contains the ATSAMB11-XR2100A and all

external RF circuitry required, including a ceramic high-gain antenna. The user simply places the module

into their PCB and provides power with a 32.768 kHz Real-Time Clock (RTC) or crystal, and an I/O path.

Microchip BluSDK Smart offers a comprehensive set of tools and reference applications for several

Bluetooth SIG defined profiles and a custom profile. The BluSDK Smart will help the user quickly

evaluate, design and develop BLE products with the ATSAMB11-XR2100A and ATSAMB11-ZR210CA.

The ATSAMB11-XR2100A and associated ATSAMB11-ZR210CA module have passed the Bluetooth SIG

certification for interoperability with the Bluetooth Low Energy 5.0 specification QDID: 117593.

Features

• 2.4 GHz Transceiver and Modem:

– -92.5 dBm receiver sensitivity

– -55 dBm to +3.5 dBm programmable TX output power

– Integrated T/R switch

– Single wire antenna connection (ATSAMB11-XR2100A)

– Incorporated chip antenna (ATSAMB11-ZR210CA)

• Processor Features:

®

®

– ARM Cortex -M0 32-bit processor

– Serial Wire Debug (SWD) interface

– Four-channel Direct Memory Access (DMA) controller

– Watchdog Timer

• Memory:

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 1

�ATSAMB11XR/ZR

•

•

•

•

•

•

•

– 128 KB embedded Random Access Memory (RAM)

– 128 KB embedded ROM

– 256 KB stacked Flash memory

Hardware Security Accelerators:

– Advanced Encryption Standard (AES)-128

– Secure Hash Algorithm (SHA)-256

Peripherals:

– 23 digital and 4 mixed-signal General Purpose Input Outputs (GPIOs) with 96 kOhm internal

programmable pull-up or down resistors and retention capability, and one wake-up GPIO with 96

kOhm internal pull-up resistor

– Two Serial Peripheral Interface (SPI) Master/Slave

– Two Inter-Integrated Circuit (I2C) Master/Slave

– Two UART

– One SPI Flash interface (used for accessing the internal stacked Flash)

– Three-axis quadrature decoder

– Four Pulse Width Modulation (PWM) channels

– Three General Purpose Timers and one Always-On (AON) sleep Timer

– 4-channel, 11-bit Analog-to-Digital Converter (ADC)

Clock:

– Integrated 26 MHz RC oscillator

– Integrated 2 MHz RC oscillator

– 26 MHz crystal oscillator (XO)

– 32.768 kHz Real Time Clock crystal oscillator (RTC XO)

Ultra-Low Power:

– 2.03 µA sleep current

– 4.18 mA peak TX current (1)

– 5.26 mA peak RX current

– 16.4 µA average advertisement current (three channels, 1s interval) (2)

Integrated Power Management:

– 2.3V to 4.3V battery voltage range

– 2.3V to 3.6V input range for I/O (limited by Flash memory)

– Fully integrated Buck DC/DC converter

Temperature Range:

– -40°C to 85°C

Package:

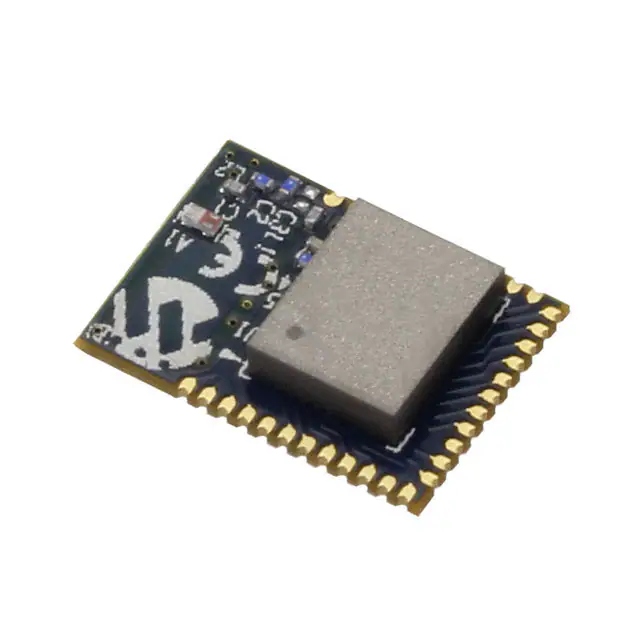

– 49-pin FLGA SiP package 5.50 mm x 4.50 mm

– 35-pin module package 10.541 mm x 7.503 mm

– BT SIG QDID: 117593

Note:

1. TX output power - 0 dBm.

2. Advertisement channels - 3 ; Advertising interval - 1 second ; Advertising event type - Connectable

undirected; Advertisement data payload size - 31 octets.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 2

�ATSAMB11XR/ZR

Table of Contents

Introduction......................................................................................................................1

Features.......................................................................................................................... 1

1. Ordering Information..................................................................................................9

2. Package Information................................................................................................10

3. Block Diagram..........................................................................................................11

4. Pinout Information................................................................................................... 12

5. Device States.......................................................................................................... 17

5.1.

5.2.

5.3.

Description of Device States...................................................................................................... 17

Power Sequences...................................................................................................................... 17

Digital and Mixed-Signal I/O Pin Behavior during Power-Up Sequences.................................. 18

6. Processor Architecture............................................................................................ 20

6.1.

6.2.

6.3.

ARM Subsystem.........................................................................................................................20

Cortex M0 Peripherals................................................................................................................21

Nested Vector Interrupt Controller..............................................................................................22

7. Memory Subsystem.................................................................................................25

7.1.

7.2.

7.3.

7.4.

7.5.

Shared Instruction and Data Memory.........................................................................................25

ROM........................................................................................................................................... 25

BLE Retention Memory.............................................................................................................. 25

Flash Memory.............................................................................................................................25

Non-Volatile Memory.................................................................................................................. 26

8. Bluetooth Low Energy Subsystem...........................................................................43

8.1.

8.2.

8.3.

8.4.

BLE Core....................................................................................................................................43

Features..................................................................................................................................... 43

BLE Radio.................................................................................................................................. 43

Microchip BluSDK Smart............................................................................................................44

9. Clocking...................................................................................................................45

9.1.

9.2.

9.3.

9.4.

9.5.

9.6.

9.7.

9.8.

9.9.

Overview.................................................................................................................................... 45

26 MHz Crystal Oscillator (XO).................................................................................................. 45

32.768 kHz RTC Crystal Oscillator (RTC XO)............................................................................46

2 MHz Integrated RC Oscillator..................................................................................................51

Clock Settings for Critical Sections............................................................................................ 52

Peripheral Clock Configuration...................................................................................................52

AON Sleep Timer Clock Configuration....................................................................................... 53

Clock Output...............................................................................................................................53

Register Summary......................................................................................................................56

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 3

�ATSAMB11XR/ZR

9.10. Register Description................................................................................................................... 57

10. I/O Peripheral Multiplexing and MEGAMUXing....................................................... 75

10.1.

10.2.

10.3.

10.4.

I/O Multiplexing...........................................................................................................................75

MEGAMUXing............................................................................................................................ 77

Register Summary .....................................................................................................................79

Register Description .................................................................................................................. 80

11. Muxable Interrupt.....................................................................................................95

11.1. Example..................................................................................................................................... 96

11.2. Register Summary......................................................................................................................96

11.3. Register Description................................................................................................................... 96

12. GPIO Pin Controller...............................................................................................103

12.1. Features................................................................................................................................... 103

12.2. Signal Description.................................................................................................................... 103

12.3. I/O Lines................................................................................................................................... 103

12.4. Clock Configuration.................................................................................................................. 104

12.5. Functional Description of LP_GPIO_x I/O Pins........................................................................104

12.6. Functional Description of GPIO_MSy I/O Pins.........................................................................106

12.7. Functional Description of AO_GPIO_z I/O Pins....................................................................... 108

12.8. External Interrupt...................................................................................................................... 111

12.9. Power Management................................................................................................................. 112

12.10. Register Summary....................................................................................................................112

12.11. Register Description................................................................................................................. 114

13. Always-On (AON) Sleep Timer..............................................................................132

13.1.

13.2.

13.3.

13.4.

13.5.

13.6.

13.7.

13.8.

Features................................................................................................................................... 132

Clock Configuration.................................................................................................................. 132

Functional Description..............................................................................................................132

Restart the Running AON Sleep Timer.................................................................................... 133

Wake-up Source.......................................................................................................................133

Power Management................................................................................................................. 133

Register Summary....................................................................................................................134

Register Description................................................................................................................. 134

14. Pulse Width Modulation.........................................................................................140

14.1.

14.2.

14.3.

14.4.

14.5.

14.6.

Features................................................................................................................................... 140

Clock Configuration.................................................................................................................. 140

Functional Description..............................................................................................................140

Power Management................................................................................................................. 147

Register Summary....................................................................................................................147

Register Description................................................................................................................. 148

15. I2C Interface.......................................................................................................... 152

15.1. Features................................................................................................................................... 152

15.2. Principal of Operation...............................................................................................................152

15.3. Clock Configuration.................................................................................................................. 153

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 4

�ATSAMB11XR/ZR

15.4.

15.5.

15.6.

15.7.

Functional Description..............................................................................................................154

Power Management................................................................................................................. 156

Register Summary....................................................................................................................156

Register Description................................................................................................................. 158

16. Dual Timer............................................................................................................. 173

16.1.

16.2.

16.3.

16.4.

16.5.

16.6.

16.7.

16.8.

Features................................................................................................................................... 173

Block Diagram.......................................................................................................................... 173

Clock Configuration.................................................................................................................. 174

Direct Memory Access............................................................................................................. 174

Functional Description..............................................................................................................174

Power Management................................................................................................................. 176

Register Summary....................................................................................................................176

Register Description................................................................................................................. 177

17. ARM Timer.............................................................................................................200

18. Serial Peripheral Interface..................................................................................... 201

18.1. Features................................................................................................................................... 201

18.2. Block Diagram.......................................................................................................................... 201

18.3. Signal Description.................................................................................................................... 201

18.4. Principle of Operation...............................................................................................................202

18.5. Clock Configuration.................................................................................................................. 202

18.6. Direct Memory Access............................................................................................................. 203

18.7. Functional Description..............................................................................................................203

18.8. Additional Features.................................................................................................................. 207

18.9. Power Management................................................................................................................. 209

18.10. Register Summary................................................................................................................... 209

18.11. Register Description................................................................................................................. 210

19. UART Interface......................................................................................................225

19.1.

19.2.

19.3.

19.4.

19.5.

19.6.

19.7.

19.8.

19.9.

Features................................................................................................................................... 225

Block Diagram.......................................................................................................................... 225

Principle of Operation...............................................................................................................226

Clock Configuration.................................................................................................................. 226

Direct Memory Access............................................................................................................. 226

Functional Description..............................................................................................................227

Power Management................................................................................................................. 230

Register Summary....................................................................................................................230

Register Description................................................................................................................. 232

20. SPI Flash Controller.............................................................................................. 244

20.1.

20.2.

20.3.

20.4.

20.5.

20.6.

Features................................................................................................................................... 244

Block Diagram.......................................................................................................................... 244

Clock Configuration.................................................................................................................. 245

Functional Description..............................................................................................................245

Endianness...............................................................................................................................249

Power Management................................................................................................................. 250

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 5

�ATSAMB11XR/ZR

20.7. Register Summary....................................................................................................................250

20.8. Register Description................................................................................................................. 251

21. Three-axis Quadrature Decoder............................................................................265

21.1.

21.2.

21.3.

21.4.

21.5.

21.6.

21.7.

Features................................................................................................................................... 265

Principle of Operation...............................................................................................................265

Clock Configuration.................................................................................................................. 266

Functional Description..............................................................................................................266

Power Management................................................................................................................. 269

Register Summary....................................................................................................................269

Register Description................................................................................................................. 270

22. Analog-to-Digital Converter................................................................................... 275

22.1.

22.2.

22.3.

22.4.

22.5.

22.6.

22.7.

Features................................................................................................................................... 275

Block Diagram.......................................................................................................................... 275

Clock Configuration.................................................................................................................. 276

Functional Description..............................................................................................................276

Power Management................................................................................................................. 279

Register Summary....................................................................................................................280

Register Description................................................................................................................. 280

23. Direct Memory Access Controller.......................................................................... 292

23.1.

23.2.

23.3.

23.4.

23.5.

23.6.

23.7.

Features................................................................................................................................... 292

Block Diagram.......................................................................................................................... 292

Operation Modes......................................................................................................................293

Functional Description..............................................................................................................296

Additional Features.................................................................................................................. 298

Register Summary....................................................................................................................301

Register Description................................................................................................................. 303

24. Watchdog Timer.................................................................................................... 335

24.1.

24.2.

24.3.

24.4.

24.5.

24.6.

24.7.

Features................................................................................................................................... 335

Flow Diagram........................................................................................................................... 335

Clock Configuration.................................................................................................................. 335

Functional Description..............................................................................................................336

Power Management................................................................................................................. 337

Register Summary....................................................................................................................337

Register Description................................................................................................................. 338

25. Electrical Characteristics....................................................................................... 360

25.1.

25.2.

25.3.

25.4.

25.5.

25.6.

25.7.

25.8.

Absolute Maximum Ratings......................................................................................................360

Recommended Operating Conditions...................................................................................... 360

DC Characteristics................................................................................................................... 361

Receiver Performance..............................................................................................................361

Transmitter Performance..........................................................................................................362

Current Consumption in Various Device States....................................................................... 363

ADC Characteristics................................................................................................................. 364

ADC Typical Characteristics.....................................................................................................365

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 6

�ATSAMB11XR/ZR

25.9. Timing Characteristics.............................................................................................................. 368

26. Package Outline Drawings.................................................................................... 374

26.1. Package Outline Drawing.........................................................................................................374

26.2. Module PCB Package Outline Drawing....................................................................................376

27. Module Reference Schematics..............................................................................378

27.1.

27.2.

27.3.

27.4.

Reference Schematic............................................................................................................... 378

Reference Schematic Bill of Materials (BOM).......................................................................... 378

Reference Schematic............................................................................................................... 380

Reference Bill of Materials(BOM).............................................................................................380

28. ATSAMB11-XR2100A Design Considerations.......................................................382

28.1. Layout Recommendation......................................................................................................... 382

28.2. SWD Interface.......................................................................................................................... 383

28.3. Unused or Unconnected Pins...................................................................................................385

29. ATSAMB11-ZR210CA Design Considerations...................................................... 386

29.1. Placement and Routing Guidelines.......................................................................................... 386

29.2. Interferers................................................................................................................................. 387

30. Reflow Profile Information..................................................................................... 388

30.1.

30.2.

30.3.

30.4.

Storage Condition.....................................................................................................................388

Soldering and Reflow Conditions............................................................................................. 388

Baking Conditions.................................................................................................................... 389

Module Assembly Considerations............................................................................................ 389

31. Regulatory Approval.............................................................................................. 390

31.1.

31.2.

31.3.

31.4.

31.5.

31.6.

31.7.

United States............................................................................................................................390

Canada.....................................................................................................................................392

Europe......................................................................................................................................393

Japan........................................................................................................................................395

Korea........................................................................................................................................395

Taiwan...................................................................................................................................... 396

Other Regulatory Information................................................................................................... 397

32. Reference Documents and Support...................................................................... 398

32.1. Reference Documents..............................................................................................................398

33. Document Revision History................................................................................... 399

The Microchip Web Site.............................................................................................. 401

Customer Change Notification Service........................................................................401

Customer Support....................................................................................................... 401

Microchip Devices Code Protection Feature............................................................... 401

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 7

�ATSAMB11XR/ZR

Legal Notice.................................................................................................................402

Trademarks................................................................................................................. 402

Quality Management System Certified by DNV...........................................................403

Worldwide Sales and Service......................................................................................404

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 8

�ATSAMB11XR/ZR

Ordering Information

1.

Ordering Information

Table 1-1. Ordering Details

Model Number

Ordering Code

Package

Description

ATSAMB11XR2100A

ATSAMB11XR2100A

5.5 mm x 4.5 mm

ATSAMB11 SiP

tray

ATSAMB11ZR210CA

ATSAMB11ZR210CA

Regulatory

Information

N/A

7.5 mm X 10.5 mm ATSAMB11 module FCC, ISED, CE,

with chip antenna MIC, KCC, NCC

Figure 1-1. Marking information

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 9

�ATSAMB11XR/ZR

Package Information

2.

Package Information

Table 2-1. ATSAMB11-XR2100A SiP 49 Package Information

Parameter

Value

Units

Tolerance

Package size

5.50 x 4.50

mm

±0.05 mm

Pad count

49

Total thickness

1.40

mm

Max

Tolerance (maximum pad pitch)

0.40

mm

±0.05 mm

Pad width

0.21

Exposed pad size

0.50 x 0.50

Note: For drawing details, see Figure 26-1.

Table 2-2. ATSAMB11-ZR210CA Module Information

Parameter

Value

Units

Tolerance

Package size

7.503 x 10.541

mm

Untoleranced dimension

Pad count

35

Total thickness

1.868

mm

Untoleranced dimensions

Pad pitch

0.61

Pad width

0.406

Exposed pad size

2.705 x 2.705

Note: For drawing details, see Figure 26-2.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 10

�ATSAMB11XR/ZR

Block Diagram

3.

Block Diagram

Figure 3-1. Block Diagram

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 11

�ATSAMB11XR/ZR

Pinout Information

4.

Pinout Information

The ATSAMB11-XR2100A is offered in an exposed pad 49-pin SiP package. This package has an

exposed paddle that must be connected to the system board ground. The SiP package pin assignment is

shown in the figure below. The colored shading is used to indicate the pin type as follows:

•

•

•

•

•

•

Red – analog

Green – digital I/O (switchable power domain)

Blue – digital I/O (always-on power domain)

Yellow – power

Purple – PMU

Shaded green/red – configurable mixed-signal GPIO (digital/analog)

The ATSAMB11-ZR210CA module is a castellated PCB with the ATSAMB11-XR2100A integrated with a

matched chip antenna. The pins are identified in the pin description table. The ATSAMB11-XR2100A also

contains a paddle pad on the bottom of the PCB, that must be soldered to the system ground.

Figure 4-1. ATSAMB11-XR2100A Pin Assignment

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 12

�ATSAMB11XR/ZR

Pinout Information

Figure 4-2. ATSAMB11-ZR210CA Pin Descriptions

The following table lists the pin assignments for both the ATSAMB11-XR2100A and the ATSAMB11ZR210CA.

Table 4-1. ATSAMB11-XR2100A and ATSAMB11-ZR210CA Pin Description

ATSAMB11XR2100A

Pin #

ATSAMB11ZR210CA

Pin #

Pin Name

Pin Type

Description / Default Function

1

-

LP_GPIO_23

Digital I/O

GPIO with Programmable Pull

Up/Down

2

17

LP_GPIO_5

Digital I/O

GPIO with Programmable Pull

Up/Down

3

18

LP_GPIO_6

Digital I/O

GPIO with Programmable Pull

Up/Down

4

19

LP_GPIO_7

Digital I/O

GPIO with Programmable Pull

Up/Down

5

20

LP_GPIO_8(1)

Digital I/O

GPIO with Programmable Pull

Up/Down

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 13

�ATSAMB11XR/ZR

Pinout Information

...........continued

ATSAMB11XR2100A

Pin #

ATSAMB11ZR210CA

Pin #

Pin Name

Pin Type

Description / Default Function

6

21

LP_GPIO_9(1)

Digital I/O

GPIO with Programmable Pull

Up/Down

7

22

LP_GPIO_10

Digital I/O

GPIO with Programmable Pull

Up/Down

8

23

LP_GPIO_11

Digital I/O

GPIO with Programmable Pull

Up/Down

9

24

LP_GPIO_12

Digital I/O

GPIO with Programmable Pull

Up/Down

10

25

LP_GPIO_13

Digital I/O

GPIO with Programmable Pull

Up/Down

11

27

VBAT

Power supply

Power supply pin for the DC/DC

convertor

12

28

GPIO_MS1

Mixed Signal I/O

Configurable to be a GPIO

digital and analog signal. Only

analog input for ADC interface.

13

29

GPIO_MS2

Mixed Signal I/O

Configurable to be a GPIO

digital and analog signal. Only

analog input for ADC interface.

14

30

C_EN

Digital Input

Can be used to control the state

of PMU. High level enables the

module; low-level places

module in Power-Down mode.

15

31

GPIO_MS3

Mixed Signal I/O

Configurable to be a GPIO

digital and analog signal. Only

analog input for ADC interface.

16

32

GPIO_MS4

Mixed Signal I/O

Configurable to be a GPIO

digital and analog signal. Only

analog input for ADC interface.

17

33

RTC_CLK_P

Analog

Crystal pin or External clock

supply, see 9.3 32.768 kHz

RTC Crystal Oscillator (RTC

XO)

18

34

RTC_CLK_N

Analog

Crystal pin or External clock

supply, see 9.3 32.768 kHz

RTC Crystal Oscillator (RTC

XO)

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 14

�ATSAMB11XR/ZR

Pinout Information

...........continued

ATSAMB11XR2100A

Pin #

ATSAMB11ZR210CA

Pin #

Pin Name

Pin Type

Description / Default Function

19

-

AO_TM

Digital Input

Always-On Test Mode. Connect

to GND

20

1

AO_GPIO_0

Always On Digital

I/O, Programmable

Pull-Up

To be held in logic '0' GND to

allow the device to enter

Ultra_Low_Power mode

Can be used to Wake-up the

device from Ultra_Low_Power

mode.

21

2

AO_GPIO_1

Always On. Digital

I/O, Programmable

Pull- Up

GPIO with Programmable Pull

Up

22

3

AO_GPIO_2

Always On. Digital

I/O, Programmable

Pull- Up

GPIO with Programmable Pull

Up

23

4

LP_GPIO_14

Digital I/O

GPIO with Programmable Pull

Up/Down

24

5

LP_GPIO_15

Digital I/O

GPIO with Programmable Pull

Up/Down

25

-

LP_GPIO_24

Digital I/O

GPIO with Programmable Pull

Up/Down

26

6

LP_GPIO_16

Digital I/O

GPIO with Programmable Pull

Up/Down

27

7

VDDIO

Power supply

Power supply pin for the I/O

pins. Can be less than or equal

to voltage supplied at VBAT

28

8

LP_GPIO_17

Digital I/O

GPIO with Programmable Pull

Up/Down

29

9

LP_GPIO_18

Digital I/O

GPIO with Programmable Pull

Up/Down

30

10

LP_GPIO_19

Digital I/O

GPIO with Programmable Pull

Up/Down

31

-

TPP

32

11, 26

GND

Ground

33

-

RFIO

Analog I/O

© 2019 Microchip Technology Inc.

Do not connect

Datasheet

RX input and TX output. Singleended RF I/O; To be connected

to antenna

DS70005342D-page 15

�ATSAMB11XR/ZR

Pinout Information

...........continued

ATSAMB11XR2100A

Pin #

ATSAMB11ZR210CA

Pin #

Pin Name

34

-

NC

35

12

LP_GPIO_0

Digital I/O

SWD clock

36

13

LP_GPIO_1

Digital I/O

SWD I/O

37

14

LP_GPIO_2

Digital I/O

GPIO with Programmable Pull

Up/Down

38

15

LP_GPIO_3

Digital I/O

GPIO with Programmable Pull

Up/Down

39

16

LP_GPIO_4

Digital I/O

GPIO with Programmable Pull

Up/Down

40

-

LP_GPIO_22

Digital I/O

GPIO with Programmable Pull

Up/Down

41 - 49

35

Paddle

Ground

Exposed paddle must be

soldered to system ground

Pin Type

Description / Default Function

Do not connect

Note:

1. These GPIO pads are high-drive pads. Refer Table 25-3.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 16

�ATSAMB11XR/ZR

Device States

5.

Device States

This section includes details on the description and controlling of the Device states.

5.1

Description of Device States

The ATSAMB11-XR2100A and the ATSAMB11-ZR210CA have multiple device states, depending on the

state of the ARM processor and BLE subsystem.

Note: The ARM is required to be powered on, if the BLE subsystem is active.

•

•

•

•

•

5.1.1

BLE_On_Transmit – Device is actively transmitting a BLE signal.

BLE_On_Receive – Device is in active receive state.

MCU_Only – Device has ARM processor powered-on and BLE subsystem powered-down.

Ultra_Low_Power – BLE subsystem and ARM processor are powered-down.

Power_Down – Device core supply off.

Controlling the Device States

The following pins are used to switch between the main device states:

• C_EN – used to enable PMU

• VDDIO – I/O supply voltage from an external power supply

• AO_GPIO_0 - can be used to control the device from entering/exiting Ultra_Low_Power mode

To be in the Power_Down state, the VDDIO supply must be turned on and the C_EN must be maintained

at logic low (at GND level). To switch between the Power_Down state and the MCU_Only state, C_EN is

to be maintained at logic high (VDDIO voltage level). Once the device is in the MCU_Only state, all other

state transitions are controlled entirely by software. When VDDIO supply is turned off and C_EN is in

logic low, the chip is powered off with no leakage.

When VDDIO supply is turned off, voltage cannot be applied to the ATSAMB11-XR2100A pins, as each

pin contains an ESD diode from the pin to supply. This diode turns on when a voltage higher than one

diode-drop is supplied to the pin.

If voltage is to be applied to the signal pads while the chip is in a low-power state, the VDDIO supply must

be on, so that the Power_Down state is used. Similarly, to prevent the pin-to-ground diode from turning

on, do not apply a voltage to any pin that is more than one diode-drop below ground.

The AO_GPIO_0 pin can be used to control the device from entering and exiting Ultra_Low_Power mode.

When AO_GPIO_0 is maintained in logic high state, the device will not enter Ultra_Low_Power mode.

When the AO_GPIO_0 is maintained in logic low, the device will enter Ultra_Low_Power mode provided

there are no BLE events to be handled.

For more details on how sleep and wake-up are handled, refer to the ATSAMB11 BluSDK Smart

Interrupts and ULP Architecture and Usage User guide.

5.2

Power Sequences

The power sequences and timing parameters for the ATSAMB11-XR2100A and ATSAMB11-ZR210CA,

are illustrated below.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 17

�ATSAMB11XR/ZR

Device States

Figure 5-1. Power-up/Power-down Sequence

The timing parameters are provided in following table.

Table 5-1. Power-up/Power-down Sequence Timing

Parameter Min. Max. Units

Description

Notes

VBAT rise to VDDIO rise

VBAT and VDDIO can rise

simultaneously or can be tied together

tA

0

tB

0

ms

VDDIO rise to C_EN rise

tC

10

µs

C_EN rise to 31.25 kHz (2

MHz/64) oscillator stabilizing

tB'

0

C_EN fall to VDDIO fall

ms

tA'

5.3

0

VDDIO fall to VBAT fall

C_EN must not rise before VDDIO. C_EN

must be driven high or low, not left

floating.

C_EN must fall before VDDIO. C_EN

must be driven high or low, not left

floating.

VBAT and VDDIO can fall simultaneously

or be tied together

Digital and Mixed-Signal I/O Pin Behavior during Power-Up Sequences

The following table represents I/O pin states corresponding to device power modes.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 18

�ATSAMB11XR/ZR

Device States

Table 5-2. I/O Pin Behavior in the Different Device States (1)

Device State

VDDIO CHIP_EN

Output Driver

Input Driver

Pull Up/Down

Resistor (2)

Power_Down: core supply

off

High

Low

Disabled (Hi-Z)

Disabled

Disabled

Power-on Reset: core

supply on, POR hard reset

pulse on

High

High

Disabled (Hi-Z)

Disabled

Disabled (3)

Power-on Default: core

supply on, device out of

reset but not programmed

yet

High

High

Disabled (Hi-Z)

Enabled(4)

Enabled Pull-Up (4)

MCU_Only, BLE_On: core

supply on, device

programmed by firmware

High

High

Programmed by

firmware for each

pin: Enabled or

Disabled (Hi-Z)

(5) ,when Enabled

driving 0 or 1

Opposite of

Output

Driver state:

Disabled or

Enabled (5)

Programmed by

firmware for each

pin: Enabled or

Disabled, Pull-Up

or Pull- Down(5)

Ultra_Low_Power:

High

High

Retains previous

Opposite of

state(6) for each pin:

Output

Enabled or Disabled Driver state:

(Hi-Z), when

Disabled or

Enabled driving 0 or Enabled(6)

1

Retains previous

state (6) for each

pin: Enabled or

Disabled, Pull-Up

or Pull-Down

core supply on for alwayson domain, core supply off

for switchable domains

Note:

1. This table applies to all three types of I/O pins (digital switchable domain GPIOs, digital always-on/

wake-up GPIO, and mixed-signal GPIOs) unless otherwise noted.

2. Pull-up/down resistor value is 96 kOhm ±10%.

3. In Power-on Reset state, the pull-up resistor is enabled in the always-on/wake-up GPIO only.

4. In Power-on Default state, the input drivers and pull-up/down resistors are disabled in the mixedsignal GPIOs only (mixed-signal GPIOs are defaulted to analog mode, see the note below).

5. Mixed-signal GPIOs can be programmed to be in analog or digital mode for each pin: when

programmed to analog mode (default), the output driver, input driver, and pull-up/down resistors are

all disabled.

6. In Ultra_Low_Power state, the always-on/wake-up GPIO does not have retention capability and

behaves same as in MCU_Only or BLE_On states, also for mixed-signal GPIOs programming

analog mode overrides retention functionality for each pin.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 19

�ATSAMB11XR/ZR

Processor Architecture

6.

Processor Architecture

6.1

ARM Subsystem

The ATSAMB11-XR2100A and ATSAMB11-ZR210CA have an ARM Cortex-M0 32-bit processor. It is

responsible for controlling the BLE Subsystem and handling all application features.

The Cortex-M0 Microcontroller consists of a full 32-bit processor capable of addressing 4GB of memory. It

has a RISC like load/store instruction set and internal 3-stage Pipeline Von Neumann architecture.

The Cortex-M0 processor provides a single system-level interface using AMBA technology to provide

high speed, low latency memory accesses.

The Cortex-M0 processor implements a complete hardware debug solution with four hardware breakpoint

and two watchpoint options. This provides high system visibility of the processor, memory, and

peripherals through a 2-pin Serial Wire Debug (SWD) port that is ideal for microcontrollers and other

small package devices.

ATSAMB11 is running a proprietary RTOS tightly coupled with FW in the ROM and the user can not

override it. SysTick timer is being used by the stack and will not be available for usage by the application.

Figure 6-1. ARM Cortex-M0 Subsystem

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 20

�ATSAMB11XR/ZR

Processor Architecture

6.1.1

Features

The processor features and benefits are:

•

•

•

•

Tight integration with the system peripherals to reduce area and development costs

Thumb instruction set combines high code density with 32-bit performance

Integrated sleep modes using a Wakeup Interrupt Controller for low power consumption

Deterministic and high-performance interrupt handling via Nested Vector Interrupt Controller for timecritical applications

• Serial Wire Debug reduces the number of pins required for debugging

• DMA engine for Peripheral-to-Memory, Memory-to-Memory, and Memory-to-Peripheral operation

6.1.2

Wakeup Sources

Ultra_Low_Power is the lowest possible power state for the system. In Ultra_Low_Power state, ARM

Cortex-M0, BLE core, GPIO's, and all other peripheral cores are powered-down. Only AON-GPIO_0 and

AON-Sleep timer are functional in this state.

ATSAMB11 contains the following wake-up sources that wake up the system from Ultra_Low_Power

mode:

• BLE events

• AON-GPIO_0

• AON-Sleep timer

6.2

Cortex M0 Peripherals

• System Control Space (SCS)

The processor provides debug through registers in the SCS. For more details, refer to the Cortex-M0

Devices Generic User Guide (http://www.arm.com).

• Nested Vectored Interrupt Controller (NVIC)

External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts. Software can

set the priority of each interrupt. The NVIC and the Cortex-M0 processor core are closely coupled,

providing low latency interrupt processing and efficient processing of late arriving interrupts. For more

details, refer to the Cortex-M0 Technical Reference Manual (http://www.arm.com).

• System Timer (SysTick)

The System Timer is a 24-bit timer clocked by CLK_CPU that extends the functionality of both the

processor and the NVIC. For more details, refer to the Cortex-M0 Technical Reference Manual

(http://www.arm.com).

• System Control Block (SCB)

The System Control Block provides system implementation information, and system control. This

includes configuration, control, and reporting of the system exceptions. For more details, refer to the

Cortex-M0 Devices Generic User Guide (http://www.arm.com).

6.2.1

Cortex M0 Peripheral Memory Map

•

•

•

•

0xE000E000 System Control Space (SCS)

0xE000E010 System Timer (SysTick)

0xE000E100 Nested Vectored Interrupt Controller (NVIC)

0xE000ED00 System Control Block (SCB)

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 21

�ATSAMB11XR/ZR

Processor Architecture

6.3

Nested Vector Interrupt Controller

External interrupt signals are connected to the NVIC, and the NVIC prioritizes the interrupts. Software can

set the priority of each interrupt. The NVIC and the Cortex-M0 processor core are closely coupled to

provide low-latency interrupt processing and efficient processing of late arriving interrupts.

All NVIC registers are accessible via word transfers and are little endian. Any attempt to read or write a

half-word or byte individually is unpredictable.

The NVIC allows the CPU to be able to individually enable or disable each interrupt source, and hold

each interrupt until it is serviced and cleared by the CPU.

Table 6-1. NVIC Register Summary

Name

Description

ISER

Interrupt Set-Enable Register

ICER

Interrupt Clear-Enable Register

ISPR

Interrupt Set-Pending Register

ICPR

Interrupt Clear-Pending Register

IPR0-IPR7

Interrupt Priority Registers

Note: For a description of each register, see the Cortex-M0 documentation from ARM (http://

www.arm.com).

6.3.1

Functional Description

The Cortex-M0 NVIC is connected to 32 IRQ sources. The following table lists the interrupts that are

available in ATSAMB11. Also, some of the interrupts are marked as RESERVED as they are used by the

BLE stack and are used for firmware in general. Applications must refrain from registering an ISR for

those interrupts as it affects the chip functionality.

Perform the following steps to enable an interrupt:

• Configure and enable peripheral interrupt using peripheral-specific registers. Refer to the intended

peripheral chapter for configuring interrupt.

• The ISRs are mapped in RAM memory called interrupt vector table. 0x10000000 is the start address

of first ISR index 0 and 4 bytes are allocated for each ISR index in incrementing order. The specific

peripheral ISR handler to be registered by assigning the handler address to this interrupt vector

table.

• Set the NVIC priority of the interrupt if required. IPR0-IPR7 ARM NVIC registers are used to set the

priority level for individual interrupt sources. IRQ number of the specific interrupt source as per the

following table is used. Only two bits are allocated for each interrupt source. Therefore, four priority

levels (0, 1, 2, and 3) are possible. The priority value is zero by default, and is also the highest

priority.

Note: The BLE interrupts are higher priority, and the Application peripherals must be set to lower

priority other than '0' either as 1, 2, 3. Therefore, the higher priority interrupts (BLE) can preempt the

lower priority interrupts like Application peripheral interrupts to meet the BLE timing requirements.

When the processor is executing an exception handler, an exception can preempt the exception

handler if its priority is higher than the priority of the exception being handled.

• Enable NVIC interrupt of specific IRQ numbers using ISER register.

© 2019 Microchip Technology Inc.

Datasheet

DS70005342D-page 22

�ATSAMB11XR/ZR

Processor Architecture

Table 6-2. ATSAMB11 Interrupt Vector Table

IRQ Number

ISR Index

Interrupt Source

Muxability

-15

1

Reset

Non-muxable

-14

2

NMI (Watchdog 0,

Watchdog 1)

Non-muxable

-13

3

Hard Fault

Non-muxable

-5

11

SVC

Non-muxable

-2

14

Pending SV

Non-muxable

-1

15

SysTick

Non-muxable

0

16

UART0 RX

Muxable

1

17

UART0 TX

Muxable

2

18

UART1 RX

Muxable

3

19

UART1 TX

Muxable

4

20

SPI0 RX

Muxable

5

21

SPI0 TX

Muxable

6

22

SPI1 RX

Muxable

7

23

SPI1 TX

Muxable

8

24

I2C0 RX

Muxable

9

25

I2C0 TX

Muxable

10

26

I2C1 RX

Muxable

11

27

I2C1 TX

Muxable

12

28

Watchdog 0

Muxable

13

29

Watchdog 1

Muxable

®

14

30

ARM Dual Timer

15

31

BLE Peripheral Register Muxable

16

32

EFuse Out of Reset

Muxable(1)

17

33

BLE Security

Muxable(1)

18

34

SPI Flash

Muxable

19

35

Calibration Done

Muxable(1)

20

36

Brown Out Detected(2)

Muxable

21

37

BLE specific

Non-Muxable(1)

22

38

BLE specific

Non-Muxable(1)

23

39

GPIO 0 Combined

Non-Muxable

© 2019 Microchip Technology Inc.

Datasheet

Muxable

DS70005342D-page 23

�ATSAMB11XR/ZR

Processor Architecture

...........continued

IRQ Number

ISR Index

Interrupt Source

Muxability

24

40

GPIO 1 Combined

Non-Muxable

25

41

GPIO 2 combined

Non-Muxable

26

42

ARM timer

Non-Muxable(1)

27

43

AON sleep timer

Non-Muxable

28

44

BLE specific

Non-Muxable(1)

29

45

BLE specific

Non-Muxable(1)

30

46

BLE specific

Non-Muxable(1)

31

47

BLE specific

Non-Muxable(1)

Note:

1. This ISR index is used by the BLE stack. Applications must refrain from registering an ISR as it

affects the chip functionality.

2. Brown out detection feature is not supported for ATSAMB11XR/ZR variant. By default the ISR is

mapped to brown-out detection interrupt. Since the feature is not supported in ATSAMB11XR/ZR

variant, this ISR can be used for any user-specific ISR using muxable interrupt configuration.

For more details on configuration options for muxable interrupts, see Muxable Interrupt.

6.3.2

Example

The following is the sample code to register and enable the AON Sleep Timer interrupt:

/* ISR Index for AON Sleep Timer from above table = 43 */

/* ISR Index base address 0x10000000 (start

address of first ISR index 0) */

/* Assign user define AON_Sleep_Timer_Handler function */

*((uint32_t *)(43 * 4 + 0x10000000))= AON_Sleep_Timer_Handler;

/* IRQ Number for AON Sleep Timer is 27 from above table. Enable AON Sleep Timer Interrupt */

NVIC->ISER[0] = (1 PINMUX_SEL_1.reg |= (0x7OUTENSET.reg |= (1 DATAOUT.reg &= ~(1 MS_GPIO_MODE.bit.ANALOG_EN GPIO_MS1 = 0;

/* Write '1' to OUTENCLR to enable input */

GPIO2->OUTENCLR.reg |= (1 INTTYPESET.reg |= (1 INTPOLSET.reg |= (1 INTENSET.reg |= (1 SINGLE_COUNT_DURATION.reg = 32768;

/* Enable Reload mode */

AON_SLEEP_TIMER0->CONTROL.reg = (1>

2

AGCDATA_I

N_POST_IN

VERT[1:0]

0

0

0xFF

0xFF

0xFF

0x3FF

0xFF

0xFF

3

AGCDATA_I

N_POST_IN

VERT[9:0]>>

1

AGCDATA_I

N_POST_IN

VERT[0:0]

0

0

0x1FF

0x1FF

0x1FF

0x3FF

0x1FF

0x1FF

4

AGCDATA_I

N_POST_IN

VERT[9:0]>>

0

0

0

0

0x3FF

0x3FF

0x3FF

0x3FF

0x3FF

0x3FF

5

AGCDATA_I

N_POST_IN

VERT[9:0]PINMUX_SEL_1.reg |= (0x1TRANSMIT_DATA.reg = (1TX_INTERRUPT_MASK.bit.TX_FIFO_EMPTY_MASK = 1;

/* As there is no default ISR mapping for DMA interrupt in Table 6-2. ATSAMB11 Interrupt

Vector Table, use muxable interrupt option as explained in 11.1 Example and register ISR

handler */

/* Static 0 register configuration for source (Memory)

RD_BURST_MAX_SIZE = 1, RD_TOKENS= 1, RD_INCR = 1 (For Memory transfer as the data is

available in RAM buffer) */

PROV_DMA_CTRL0->CH0_STATIC_REG0.reg = (1