Ultralow Distortion,

Ultralow Noise Op Amp

AD797

Data Sheet

FEATURES

GENERAL DESCRIPTION

Low noise

0.9 nV/√Hz typical (1.2 nV/√Hz maximum) input voltage

noise at 1 kHz

50 nV p-p input voltage noise, 0.1 Hz to 10 Hz

Low distortion

−120 dB total harmonic distortion at 20 kHz

Excellent ac characteristics

800 ns settling time to 16 bits (10 V step)

110 MHz gain bandwidth (G = 1000)

8 MHz bandwidth (G = 10)

280 kHz full power bandwidth at 20 V p-p

20 V/μs slew rate

Excellent dc precision

80 μV maximum input offset voltage

1.0 μV/°C VOS drift

Specified for ±5 V and ±15 V power supplies

High output drive current of 50 mA

The AD797 is a very low noise, low distortion operational amplifier

ideal for use as a preamplifier. The low noise of 0.9 nV/√Hz and

low total harmonic distortion of −120 dB in audio bandwidths

give the AD797 the wide dynamic range necessary for preamps

in microphones and mixing consoles.

APPLICATIONS

Furthermore, the AD797 has an excellent slew rate of 20 V/μs

and a 110 MHz gain bandwidth, which makes it highly suitable

for low frequency ultrasound applications.

The AD797 is also useful in infrared (IR) and sonar imaging

applications, where the widest dynamic range is necessary. The

low distortion and 16-bit settling time of the AD797 make it

ideal for buffering the inputs to Σ-Δ ADCs or the outputs of

high resolution DACs, especially when the device is used in

critical applications such as seismic detection or in spectrum

analyzers. Key features such as a 50 mA output current drive

and the specified power supply voltage range of ±5 V to ±15 V

make the AD797 an excellent general-purpose amplifier.

5

4

3

2

1

0

10

100

1k

10k

100k

10M

1M

FREQUENCY (Hz)

00846-002

INPUT VOLTAGE NOISE (nV/√Hz)

Professional audio preamplifiers

IR, CCD, and sonar imaging systems

Spectrum analyzers

Ultrasound preamplifiers

Seismic detectors

Σ-Δ ADC/DAC buffers

Figure 1. AD797 Voltage Noise Spectral Density

Table 1. Low Noise Op Amps

Voltage Noise

Single

Dual

Quad

Rev. K

0.9 nV

AD797

1.1 nV

AD8597

AD8599

1.8 nV

ADA4004-1

ADA4004-2

ADA4004-4

2.8 nV

AD8675/ADA4075-2

AD8676

3.2 nV

OP27

OP270

OP470

3.8 nV

AD8671

AD8672

AD8674

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©1992–2015 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�AD797

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Noise and Source Impedance Considerations ........................... 12

Applications ....................................................................................... 1

Low Frequency Noise ................................................................ 12

General Description ......................................................................... 1

Wideband Noise ......................................................................... 12

Revision History ............................................................................... 2

Bypassing Considerations ......................................................... 13

Specifications..................................................................................... 3

The Noninverting Configuration ............................................. 13

Absolute Maximum Ratings............................................................ 5

The Inverting Configuration .................................................... 14

Pin Configuration ............................................................................. 5

Driving Capacitive Loads .......................................................... 14

Thermal Resistance ...................................................................... 5

Settling Time ............................................................................... 14

ESD Caution .................................................................................. 5

Distortion Reduction ................................................................. 15

Typical Performance Characteristics ............................................. 6

Outline Dimensions ....................................................................... 18

Theory of Operation ...................................................................... 11

Ordering Guide .......................................................................... 19

REVISION HISTORY

3/15—Rev. J to Rev. K

Changes to Figure 35 ...................................................................... 12

Changes to Ordering Guide .......................................................... 19

2/14—Rev. I to Rev. J

Changes to Power Supply Rejection Parameter, Table 2 ............. 3

3/13—Rev. H to Rev. I

Added Figure 18................................................................................ 8

6/10—Rev. G to Rev. H

Added Table 1; Renumbered Sequentially .................................... 1

Moved Figure 1 to Absolute Maximum Ratings Section;

Renumbered Sequentially................................................................ 5

Changes to Table 3 ............................................................................ 5

Added Thermal Resistance Section and Table 4 .......................... 5

Moved Figure 3 to Typical Performance Characteristics

Section .............................................................................................. 10

Change to Noise and Source Impedance Considerations

Section .............................................................................................. 12

Changes to Ordering Guide .......................................................... 19

7/05—Rev. D to Rev. E

Updated Figure 1 Caption ................................................................1

Deleted Metallization Photo ............................................................6

Changes to Equation 1 ................................................................... 12

Updated Outline Dimensions ....................................................... 19

Changes to Ordering Guide .......................................................... 20

10/02—Rev. C to Rev. D

Deleted 8-Lead CERDIP Package (Q-8) ......................... Universal

Edits to Specifications .......................................................................2

Edits to Absolute Maximum Ratings ..............................................3

Edits to Ordering Guide ...................................................................3

Edits to Table I ...................................................................................9

Deleted Operational Amplifiers Graphic .................................... 15

Updated Outline Dimensions ....................................................... 15

9/08—Rev. F to Rev. G

Changes to Input Common-Mode Voltage Range Parameter,

Table 1 ................................................................................................ 3

1/08—Rev. E to Rev. F

Changes to Absolute Maximum Ratings ....................................... 5

Change to Equation 1 ..................................................................... 12

Changes to the Noninverting Configuration Section ................ 13

Updated Outline Dimensions ....................................................... 19

Changes to Ordering Guide .......................................................... 20

Rev. K | Page 2 of 19

�Data Sheet

AD797

SPECIFICATIONS

TA = 25°C and VS = ±15 V dc, unless otherwise noted.

Table 2.

AD797A

Parameter

INPUT OFFSET VOLTAGE

Conditions

Supply

Voltage (V)

±5 V, ±15 V

Min

TMIN to TMAX

Offset Voltage Drift

INPUT BIAS CURRENT

±5 V, ±15 V

±5 V, ±15 V

TMIN to TMAX

INPUT OFFSET CURRENT

OPEN-LOOP GAIN

DYNAMIC PERFORMANCE

Gain Bandwidth Product

–3 dB Bandwidth

Full Power Bandwidth1

Slew Rate

Settling Time to 0.0015%

COMMON-MODE REJECTION

POWER SUPPLY REJECTION

INPUT VOLTAGE NOISE

INPUT CURRENT NOISE

INPUT COMMON-MODE

VOLTAGE RANGE

OUTPUT VOLTAGE SWING

Short-Circuit Current

Output Current3

TOTAL HARMONIC

DISTORTION

±5 V, ±15 V

TMIN to TMAX

VOUT = ±10 V

RLOAD = 2 kΩ

TMIN to TMAX

RLOAD = 600 Ω

TMIN to TMAX

At 20 kHz1

G = 1000

G = 10002

G = 10

VOUT = 20 V p-p,

RLOAD = 1 kΩ

RLOAD = 1 kΩ

10 V step

VCM = CMVR

TMIN to TMAX

VS = ±5 V to ±18 V

TMIN to TMAX

f = 0.1 Hz to 10 Hz

f = 10 Hz

f = 1 kHz

f = 10 Hz to 1 MHz

f = 1 kHz

RLOAD = 2 kΩ

RLOAD = 600 Ω

RLOAD = 600 Ω

RLOAD = 1 kΩ, CN = 50 pF,

f = 250 kHz, 3 V rms

RLOAD = 1 kΩ,

f = 20 kHz, 3 V rms

±15 V

1

1

1

1

14,000

±15 V

15 V

±15 V

±15 V

±15 V

±15 V

±5 V, ±15 V

±15 V

±15 V

±15 V

±15 V

±15 V

±15 V

±5 V

±15 V

±15 V

±5 V

±5 V, ±15 V

±5 V, ±15 V

±15 V

12.5

114

110

114

110

±11

±2.5

±12

±11

±2.5

30

±15 V

Rev. K | Page 3 of 19

Typ

25

50

0.2

0.25

0.5

100

120

20

6

15

5

20,000

AD797B

Max

80

125/180

1.0

1.5

3.0

400

600/700

Min

2

2

2

2

14,000

110

450

8

280

110

450

8

20

800

130

120

130

120

50

1.7

0.9

1.0

2.0

±12

12.5

±3

±13

±13

±3

80

50

−98

−120

1200

120

114

120

114

1.2

1.3

±11

±2.5

±12

±11

±2.5

Typ

10

30

0.2

0.25

0.25

80

120

20

10

15

7

20,000

Max

40

60

0.6

0.9

2.0

200

300

Unit

μV

μV

μV/°C

μA

μA

nA

nA

V/μV

V/μV

V/μV

V/μV

V/V

280

MHz

MHz

MHz

kHz

20

800

130

120

130

120

50

1.7

0.9

1.0

2.0

±12

V/μs

ns

dB

dB

dB

dB

nV p-p

nV/√Hz

nV/√Hz

μV rms

pA/√Hz

V

1200

2.5

1.2

1.2

−90

±3

±13

±13

±3

80

50

−98

−90

V

V

V

V

mA

mA

dB

−110

−120

−110

dB

30

�AD797

Data Sheet

AD797A

Parameter

INPUT CHARACTERISTICS

Input Resistance

Differential

Common Mode

Input Capacitance

Differential4

Common Mode

OUTPUT RESISTANCE

POWER SUPPLY

Operating Range

Quiescent Current

Conditions

Supply

Voltage (V)

Min

AV = 1, f = 1 kHz

Typ

1

Max

3

Rev. K | Page 4 of 19

Typ

Max

Unit

7.5

100

kΩ

MΩ

20

5

3

20

5

3

pF

pF

mΩ

±18

10.5

V

mA

8.2

±18

10.5

Full power bandwidth = slew rate/2π VPEAK.

Specified using external decompensation capacitor.

Output current for |VS − VOUT| > 4 V, AOL > 200 kΩ.

4

Differential input capacitance consists of 1.5 pF package capacitance and 18.5 pF from the input differential pair.

2

Min

7.5

100

±5

±5 V, ±15 V

AD797B

±5

8.2

�Data Sheet

AD797

ABSOLUTE MAXIMUM RATINGS

PIN CONFIGURATION

Parameter

Supply Voltage

Input Voltage

Differential Input Voltage1

Output Short-Circuit Duration

Storage Temperature Range

(N, R Suffix)

Operating Temperature Range

Lead Temperature (Soldering 60 sec)

1

Ratings

±18 V

±VS

±0.7 V

Indefinite within

maximum internal

power dissipation

−65°C to +125°C

–IN 2

DECOMPENSATION

AND DISTORTION

NEUTRALIZATION

7 +VS

+IN 3

6

OUTPUT

–VS 4

5

OFFSET NULL

OFFSET NULL 1

AD797

TOP VIEW

8

00846-001

Table 3.

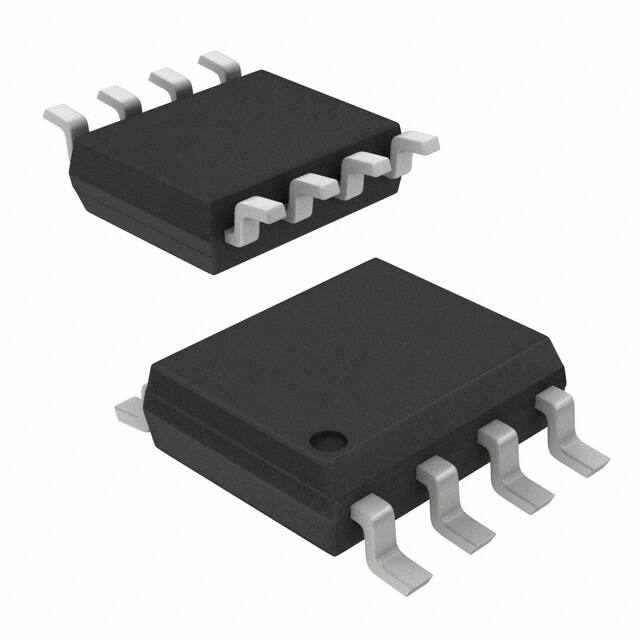

Figure 2. 8-Lead Plastic Dual In-Line Package [PDIP] and

8-Lead Standard Small Outline Package [SOIC]

THERMAL RESISTANCE

θJA is specified for the device soldered on a 4-layer JEDEC

standard printed circuit board (PCB) with zero airflow for the

SOIC package, and a 2-layer JEDEC standard printed circuit

board (PCB) with zero airflow for the PDIP package.

−40°C to +85°C

300°C

The AD797 inputs are protected by back-to-back diodes. To achieve low

noise, internal current-limiting resistors are not incorporated into the design

of this amplifier. If the differential input voltage exceeds ±0.7 V, the input

current should be limited to less than 25 mA by series protection resistors.

Note, however, that this degrades the low noise performance of the device.

Stresses at or above those listed under Absolute Maximum

Ratings may cause permanent damage to the product. This is a

stress rating only; functional operation of the product at these

or any other conditions above those indicated in the operational

section of this specification is not implied. Operation beyond

the maximum operating conditions for extended periods may

affect product reliability.

Table 4. Thermal Resistance

Package Type

8-Lead SOIC (R-8)

8-Lead PDIP (N-8)

ESD CAUTION

Rev. K | Page 5 of 19

θJA

120

103

θJC

43

50

Unit

°C/W

°C/W

�AD797

Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

10

5

0

5

10

15

20

SUPPLY VOLTAGE (±V)

HORIZONTAL SCALE (5sec/DIV)

Figure 3. Input Common-Mode Voltage Range vs. Supply Voltage

Figure 6. 0.1 Hz to 10 Hz Noise

0

INPUT BIAS CURRENT (µA)

15

10

+VOUT

–VOUT

5

0

0

5

10

15

20

SUPPLY VOLTAGE (±V)

–0.5

–1.0

–1.5

–2.0

–60

00846-005

–20

0

20

40

60

80

100

120

140

TEMPERATURE (°C)

Figure 4. Output Voltage Swing vs. Supply Voltage

Figure 7. Input Bias Current vs. Temperature

30

140

SHORT-CIRCUIT CURRENT (mA)

VS = ± 15V

20

10

VS = ±5

120

100

SOURCE CURRENT

SINK CURRENT

80

60

0

10

100

1k

LOAD RESISTANCE (Ω)

10k

40

–60

00846-006

OUTPUT VOLTAGE SWING (V p-p)

–40

–40

–20

0

20

40

60

80

100

120

TEMPERATURE (°C)

Figure 5. Output Voltage Swing vs. Load Resistance

Figure 8. Short-Circuit Current vs. Temperature

Rev. K | Page 6 of 19

140

00846-009

OUTPUT VOLTAGE SWING (±V)

20

00846-008

0

00846-007

VERTICAL SCALE (0.01µV/DIV)

15

00846-004

INPUT COMMON-MODE RANGE (±V)

20

�Data Sheet

AD797

+125°C

9

+25°C

8

7

5

15

10

20

SUPPLY VOLTAGE (±V)

Figure 9. Quiescent Supply Current vs. Supply Voltage

125

CMR

60

100

40

75

20

1

10

100

1k

10k

100k

FREQUENCY (Hz)

–60

f = 1kHz

RL = 600Ω

G = +10

RL = 600Ω

G = +10

f = 10kHz

NOISE BW = 100kHz

THD + NOISE (dB)

9

6

–80

VS = ±5V

–100

3

0

±5

±10

±15

±20

SUPPLY VOLTAGE (±V)

–120

0.01

0.1

1

10

OUTPUT LEVEL (V)

Figure 10. Output Voltage vs. Supply Voltage for 0.01% Distortion

00846-014

VS = ±15V

00846-011

0

50

1M

Figure 12. Power Supply and Common-Mode Rejection vs. Frequency

12

OUTPUT VOLTAGE (V rms)

150

80

00846-010

0

PSR

+SUPPLY

PSR

–SUPPLY

100

–55°C

6

175

120

00846-013

10

COMMON MODE REJECTION (dB)

200

140

POWER SUPPLY REJECTION (dB)

QUIESCENT SUPPLY CURRENT (mA)

11

Figure 13. Total Harmonic Distortion (THD) + Noise vs. Output Level

30

1.0

OUTPUT VOLTAGE (V p-p)

±15V SUPPLIES

0.0015%

0.6

0.01%

0.4

RL = 600Ω

20

10

±5V SUPPLIES

0

0

2

4

6

8

STEP SIZE (V)

10

0

10k

100k

1M

FREQUENCY (Hz)

Figure 14. Large-Signal Frequency Response

Figure 11. Settling Time vs. Step Size (±)

Rev. K | Page 7 of 19

10M

00846-015

0.2

00846-012

SETTLING TIME (µs)

0.8

�AD797

Data Sheet

100

3

2

1

0

1k

10k

100k

1M

10M

FREQUENCY (Hz)

1

1

10

100

1k

10k

FREQUENCY (Hz)

Figure 18. Current Noise Density VS = ±15 V

Figure 15. Input Voltage Noise Spectral Density

120

120

35

100

PHASE MARGIN

80

60

40

GAIN

20

40

*RS = 100

WITHOUT

RS*

20

*SEE FIGURE 26.

0

100

1k

SLEW RATE

RISING EDGE

25

100

SLEW RATE

FALLING EDGE

90

20

0

WITH RS*

10k

100k

1M

FREQUENCY (Hz)

10M

100M

15

–60

–40

–20

0

20

40

60

80

100

120

80

140

TEMPERATURE (°C)

Figure 16. Open-Loop Gain and Phase Margin vs. Frequency

Figure 19. Slew Rate and Gain/Bandwidth Product vs. Temperature

160

300

OVERCOMPENSATED

OPEN-LOOP GAIN (dB)

150

0

140

120

–150

–300

–60

100

–40

–20

0

20

40

60

80

100

TEMPERATURE (°C)

120

140

100

1k

LOAD RESISTANCE (Ω)

Figure 20. Open-Loop Gain vs. Load Resistance

Figure 17. Input Offset Current vs. Temperature

Rev. K | Page 8 of 19

10k

00846-020

UNDER COMPENSATED

00846-018

INPUT OFFSET CURRENT (nA)

110

30

SLEW RATE (V/µs)

80

60

GAIN/BANDWIDTH PRODUCT

PHASE MARGIN (Degrees)

WITHOUT

RS*

WITH RS*

00846-017

OPEN-LOOP GAIN (dB)

100

GAIN/BANDWIDTH PRODUCT (MHz (G = 1000))

100

00846-019

10

10

00846-055

CURRENT NOISE DENSITY (pA/√Hz)

4

00846-016

INPUT VOLTAGE NOISE (nV/√Hz)

5

�Data Sheet

AD797

50mV

100ns

100

90

10

1

WITHOUT CN*

0.1

10

100

1k

10k

100k

1M

FREQUENCY (Hz)

00846-024

0%

00846-021

0.01

10

WITH CN*

*SEE FIGURE 33.

Figure 21. Magnitude of Output Impedance vs. Frequency

Figure 24. Inverter Small-Signal Pulse Response

20pF

100Ω

+VS

1kΩ

1kΩ

2

7

AD797

3

VIN

VOUT

6

RS*

7

AD797

3

VOUT

6

600Ω

4

**

4

–VS

*

*VALUE OF SOURCE RESISTANCE

(SEE THE NOISE AND SOURCE IMPEDANCE

CONSIDERATIONS SECTION).

**SEE FIGURE 36.

–VS

*SEE FIGURE 36.

Figure 22. Inverter Connection

Figure 25. Follower Connection

1µs

5V

100

100

90

90

10

0%

5V

00846-023

10

0%

Figure 23. Inverter Large-Signal Pulse Response

1µs

00846-026

VIN

2

*

**

00846-025

+VS

00846-022

MAGNITUDE OF OUTPUT IMPEDANCE (Ω)

100

Figure 26. Follower Large-Signal Pulse Response

Rev. K | Page 9 of 19

�AD797

Data Sheet

50mV

100ns

100

100

90

90

10

0%

00846-027

10

0%

500ns

00846-029

50mV

Figure 29. 16-Bit Settling Time Negative Input Pulse

Figure 27. Follower Small-Signal Pulse Response

–90

500ns

100

THD (dB)

90

–100

0.001

–110

0.0003

–120

0.0001

THD (%)

50mV

00846-028

–130

100

300

1k

3k

10k

30k

FREQUENCY (Hz)

Figure 28. 16-Bit Settling Time Positive Input Pulse

Figure 30. THD vs. Frequency

Rev. K | Page 10 of 19

100k

300k

00846-003

MEASUREMENT

LIMIT

10

0%

�Data Sheet

AD797

THEORY OF OPERATION

The architecture of the AD797 was developed to overcome

inherent limitations in previous amplifier designs. Previous

precision amplifiers used three stages to ensure high open-loop

gain (see Figure 31) at the expense of additional frequency compensation components. Slew rate and settling performance are

usually compromised, and dynamic performance is not adequate

beyond audio frequencies. As can be seen in Figure 31, the first

stage gain is rolled off at high frequencies by the compensation

network. Second stage noise and distortion then appears at the

input and degrade performance. The AD797, on the other hand,

uses a single ultrahigh gain stage to achieve dc as well as dynamic

precision. As shown in the simplified schematic (Figure 32),

Node A, Node B, and Node C track the input voltage, forcing

the operating points of all pairs of devices in the signal path to

match. By exploiting the inherent matching of devices fabricated on

the same IC chip, high open-loop gain, CMRR, PSRR, and low

VOS are guaranteed by pairwise device matching (that is, NPN

to NPN and PNP to PNP), not by an absolute parameter such as

beta and the early voltage.

VOUT

BUFFER

gm

RL

C1

R1

GAIN = gm × R1 × 5 × 106

The elimination of second-stage noise effects has the additional

benefit of making the low noise of the AD797 (5 × 106 and VOS < 80 μV,

while at the same time providing a THD + noise of less than

−120 dB and true 16-bit settling in less than 800 ns.

Rev. K | Page 11 of 19

Figure 33. AD797 Block Diagram

00846-032

R1

gm

C

CN

j C N j C j

A

A

When CN is equal to CC, the ideal single-pole op amp response

is attained:

a.

gm

�AD797

Data Sheet

NOISE AND SOURCE IMPEDANCE CONSIDERATIONS

LOW FREQUENCY NOISE

The AD797 ultralow voltage noise of 0.9 nV/√Hz is achieved

with special input transistors running at nearly 1 mA of collector

current. Therefore, it is important to consider the total inputreferred noise (eNtotal), which includes contributions from voltage

noise (eN), current noise (iN), and resistor noise (√4 kTRS).

Analog Devices specifies low frequency noise as a peak-to-peak

quantity in a 0.1 Hz to 10 Hz bandwidth. Several techniques can

be used to make this measurement. The usual technique involves

amplifying, filtering, and measuring the amplifier noise for a

predetermined test time. The noise bandwidth of the filter is

corrected for, and the test time is carefully controlled because

the measurement time acts as an additional low frequency roll-off.

e N total [e N 2 4 kTR S (i N R S ) 2 ]1 / 2

(1)

where RS is the total input source resistance.

This equation is plotted for the AD797 in Figure 34. Because

optimum dc performance is obtained with matched source

resistances, this case is considered even though it is clear from

Equation 1 that eliminating the balancing source resistance

lowers the total noise by reducing the total RS by a factor of 2.

At very low source resistance (RS < 50 Ω), the voltage noise of the

amplifier dominates. As source resistance increases, the Johnson

noise of RS dominates until a higher resistance of RS > 2 kΩ is

achieved; the current noise component is larger than the

resistor noise.

100

The plot in Figure 6 uses a slightly different technique: an FFTbased instrument (Figure 35) is used to generate a 10 Hz brickwall

filter. A low frequency pole at 0.1 Hz is generated with an

external ac coupling capacitor, which is also the instrument being

dc coupled.

Several precautions are necessary to attain optimum low

frequency noise performance:

TOTAL NOISE

NOISE (nV/√Hz)

10

RESISTOR

NOISE

ONLY

1

Care must be used to account for the effects of RS. Even

a 10 Ω resistor has 0.4 nV/√Hz of noise (an error of 9%

when root sum squared with 0.9 nV/√Hz).

The test setup must be fully warmed up to prevent eOS drift

from erroneously contributing to input noise.

Circuitry must be shielded from air currents. Heat flow out

of the package through its leads creates the opportunity for

a thermoelectric potential at every junction of different metals.

Selective heating and cooling of these by random air currents

appears as 1/f noise and obscures the true device noise.

The results must be interpreted using valid statistical

techniques.

100kΩ

+VS

*

100

1000

10000

SOURCE RESISTANCE (Ω)

2

7

AD797

Figure 34. Noise vs. Source Resistance

3

1.5µF

6

4

VOUT

HP 3465

DYNAMIC SIGNAL

ANALYZER

(10Hz)

*

The AD797 is the optimum choice for low noise performance if

the source resistance is kept