9 kHz to 30 GHz,

Silicon SPDT Switch

ADRF5021

Data Sheet

FUNCTIONAL BLOCK DIAGRAM

RF2

ADRF5021

VSS

EN

50Ω

RFC

CTRL

50Ω

VDD

RF1

14580-001

Ultrawideband frequency range: 9 kHz to 30 GHz

Nonreflective 50 Ω design

Low insertion loss: 2.0 dB to 30 GHz

High isolation: 60 dB to 30 GHz

High input linearity

1 dB power compression (P1dB): 28 dBm typical

Third-order intercept (IP3): 52 dBm typical

High power handling

24 dBm through path

24 dBm terminated path

ESD sensitivity: Class 1, 1 kV human body model (HBM)

20-terminal, 3 mm × 3 mm land grid array package

No low frequency spurious

Radio frequency (RF) settling time (to 0.1 dB of final RF

output): 6.2 µs

DRIVER

FEATURES

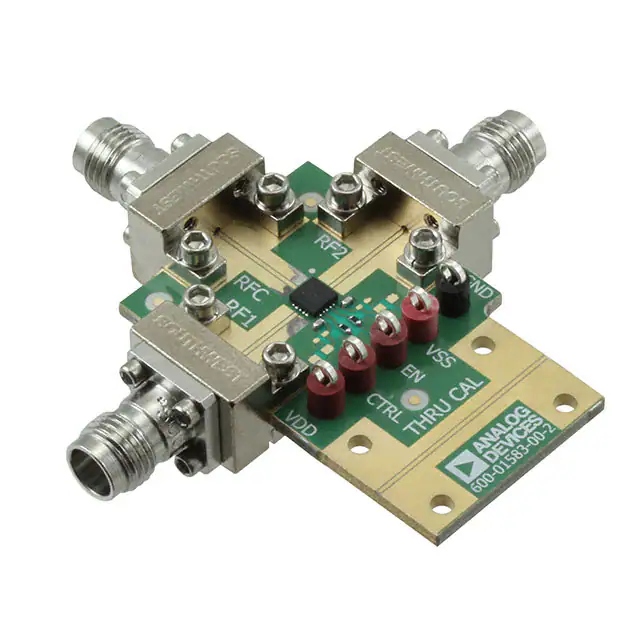

Figure 1.

APPLICATIONS

Test instrumentation

Microwave radios and very small aperture terminals (VSATs)

Military radios, radars, electronic counter measures (ECMs)

Broadband telecommunications systems

GENERAL DESCRIPTION

The ADRF5021 is a general-purpose single-pole, double-throw

(SPDT) switch manufactured using a silicon process. It comes

in a 3 mm × 3 mm, 20-terminal land grid array (LGA) package

and provides high isolation and low insertion loss from 9 kHz

to 30 GHz.

Rev. B

This broadband switch requires dual supply voltages, +3.3 V

and −2.5 V, and provides CMOS/LVTTL logic-compatible

control.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice.

No license is granted by implication or otherwise under any patent or patent rights of Analog

Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2016–2020 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

�ADRF5021

Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Interface Schematics .....................................................................6

Applications ...................................................................................... 1

Typical Performance Characterics..................................................7

Functional Block Diagram .............................................................. 1

Insertion Loss, Return Loss, and Isolation ................................7

General Description ......................................................................... 1

Input Power Compression and Third-Order Intercept (IP3) 8

Revision History ............................................................................... 2

Theory of Operation .........................................................................9

Specifications .................................................................................... 3

Applications Information ............................................................. 10

Absolute Maximum Ratings ........................................................... 5

Evaluation Board ........................................................................ 10

Power Derating Curves ............................................................... 5

Probe Matrix Board ................................................................... 11

ESD Caution.................................................................................. 5

Outline Dimensions ....................................................................... 12

Pin Configuration and Function Descriptions ............................ 6

Ordering Guide .......................................................................... 12

REVISION HISTORY

3/2020—Rev. A to Rev. B

Changes to Digital Control Inputs Parameter, Table 2 .............. 5

Added Endnote 1, Table 2; Renumbered Sequentially ............... 5

Changes to Theory of Operation Section.................................... 10

2/2017—Rev. 0 to Rev. A

Changed VEN = 3.3 V to 5 V to VEN = 0 V or 3.3 V to 5 V ...........3

7/2016—Revision 0: Initial Version

Rev. B | Page 2 of 12

�Data Sheet

ADRF5021

SPECIFICATIONS

VDD = 3.3 V to 5 V, VSS = −2.5 V, VCTRL = 0 V or 3.3 V to 5 V, VEN = 0 V or 3.3 V to 5 V, TCASE = 25°C, 50 Ω system, unless otherwise

noted.

Table 1.

Parameter

FREQUENCY RANGE

INSERTION LOSS

Between RFC and RF1/RF2

Symbol

ISOLATION

Between RFC and RF1/RF2

Between RF1 and RF2

RETURN LOSS

RFC and RF1/RF2 (On)

RF1/RF2 (Off)

SWITCHING

Rise and Fall Time

On and Off Time

RF Settling Time

0.1 dB

0.05 dB

INPUT LINEARITY 1

Power Compression

0.1 dB

1 dB

Third-Order Intercept

SUPPLY CURRENT

Positive

Negative

DIGITAL CONTROL INPUTS

Voltage

Low

High

Current

Low and High

tRISE, tFALL

tON, tOFF

P0.1dB

P1dB

IP3

IDD

ISS

VINL

VINH

Test Conditions/Comments

Min

0.009

Typ

Max

30,000

Unit

MHz

9 kHz to 10 GHz

10 GHz to 20 GHz

20 GHz to 30 GHz

1.1

1.4

2.0

dB

dB

dB

9 kHz to 10 GHz

10 GHz to 20 GHz

20 GHz to 30 GHz

9 kHz to 10 GHz

10 GHz to 20 GHz

20 GHz to 30 GHz

65

60

60

70

65

60

dB

dB

dB

dB

dB

dB

9 kHz to 10 GHz

10 GHz to 20 GHz

20 GHz to- 30 GHz

9 kHz to 10 GHz

10 GHz to 20 GHz

20 GHz to 30 GHz

23

17

13

30

18

8

dB

dB

dB

dB

dB

dB

10% to 90% of RF output

50% VCTL to 90% of RF output

1.0

1.1

µs

µs

50% VCTL to 0.1 dB of final RF output

50% VCTL to 0.05 dB of final RF output

1 MHz to 30 GHz

6.2

10

µs

µs

27

28

52

dBm

dBm

dBm

Two-tone input power = 14 dBm each tone,

Δf = 1 MHz

VDD, VSS pins

VDD = 3.3 V

VDD = 5 V

VSS = −2.5 V

CTRL, EN pins

VDD = 3.3 V

VDD = 5 V

VDD = 3.3 V

VDD = 5 V

IINL, IINH

80

100

很抱歉,暂时无法提供与“ADRF5021-EVALZ”相匹配的价格&库存,您可以联系我们找货

免费人工找货