LT5524

Low Distortion IF

Amplifier/ADC Driver with

Digitally Controlled Gain

U

FEATURES

DESCRIPTIO

■

The LT®5524 is a programmable gain amplifier (PGA) with

bandwidth extending from low frequency (LF) to 540MHz.

It consists of a digitally controlled variable attenuator,

followed by a high linearity amplifier. Four parallel digital

inputs control the gain over a 22.5dB range with 1.5dB

step resolution. An on-chip power supply regulator/filter

helps isolate the amplifier signal path from external noise

sources.

■

■

■

■

■

■

■

■

■

■

■

■

■

■

■

Output IP3 at 100MHz: 40dBm

Maximum Output Power: 16dBm

Bandwidth: LF to 540MHz

Propagation Delay: 0.8ns

Maximum Gain: 27dB

Gain Control Range: 22.5dB

Gain Control Step: 1.5dB

Gain Control Settling Time: 500ns

Noise Figure: 8.6dB at 100MHz (Max Gain)

Output Noise Floor: –138dBm/Hz (Max Gain)

Reverse Isolation: –92dB

Single Supply: 4.75V to 5.25V

Shutdown Mode

Enable/Disable Time: 1µs

Differential I/O Interface

20-Lead TSSOP Package

The LT5524’s open-loop architecture offers stable operation for any practical load conditions, including peakingfree AC response when driving capacitive loads, and

excellent reverse isolation.

The LT5524 may be operated broadband, where the output differential RC time constant sets the bandwidth, or it

may be used as a narrowband driver with the appropriate

output filter.

U

APPLICATIO S

■

■

■

■

High Linearity ADC Driver

IF Sampling Receivers

VGA IF Power Amplifier

50Ω Driver

Instrumentation Applications

U

■

, LTC and LT are registered trademarks of Linear Technology Corporation.

Patents Pending.

TYPICAL APPLICATIO

Output IP3 vs Frequency, ROUT = 200Ω

54

5V

CHOKE

RF

INPUT

IF

BPF

LO

IF

AMP

48

0.1µF

100Ω

LT5524

0.1µF

0.1µF

GAIN CONTROL

ADC

5524 TA01

OIP3 (dBm)

0.1µF

51

CHOKE

45

MAX GAIN

42

39

1.5dB

ATTENUATION

STEP

36

4 LINES

33

30

0

50

100

150

200

FREQUENCY (MHz)

5524 TA02

5524f

1

�LT5524

U

W

W W

U

U

W

ABSOLUTE MAXIMUM RATINGS

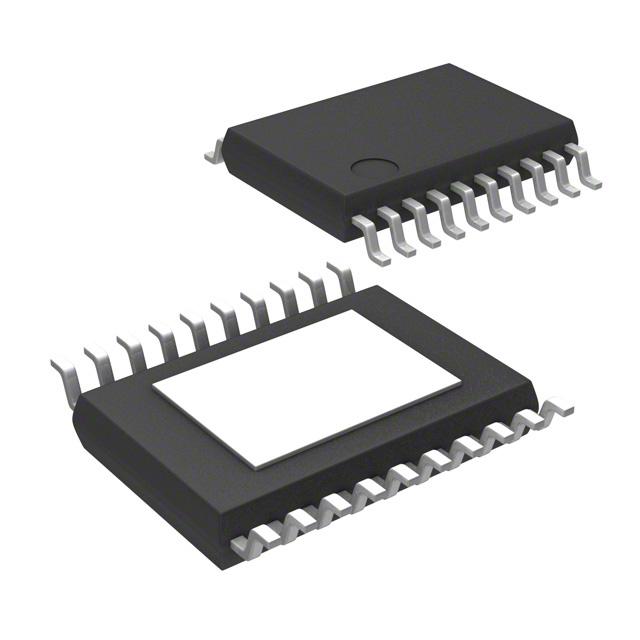

PACKAGE/ORDER INFORMATION

(Notes 1, 2)

Power Supply Voltage (VCC1, VCC2) .......................... 6V

Output DC Voltage (OUT+, OUT–) ............................. 7V

Control Input Voltage (EN, PGAx) ............. –0.5V to VCC

Signal Input Voltage (IN+, IN–) ................... –0.5V to 3V

Operating Ambient Temperature Range .. – 40°C to 85°C

Storage Temperature Range ................. – 65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

TOP VIEW

EN 1

20 NC

VCC1 2

19 VCC2

GND 3

18 GND

GND 4

17 GND

IN +

5

IN –

6

21

ORDER PART

NUMBER

LT5524EFE

16 OUT –

15 OUT +

GND 7

14 GND

GND 8

13 GND

PGA0 9

12 PGA3

PGA1 10

11 PGA2

FE PACKAGE

20-LEAD PLASTIC TSSOP

TJMAX = 150°C, θJA = 38°C/W

EXPOSED PAD (PIN 21) IS GND

MUST BE SOLDERED TO PCB

Consult LTC Marketing for parts specified with wider operating temperature ranges.

U

U

WW

PROGRA

ABLE GAI SETTI GS

ATTENUATION STEP

RELATIVE TO MAX GAIN

1

0dB

2

–1.5dB

3

–3.0dB

4

–4.5dB

5

–6.0dB

6

–7.5dB

7

–9.0dB

8

–10.5dB

9

–12.0dB

10

–13.5dB

11

–15.0dB

12

–16.5dB

13

–18.0dB

14

–19.5dB

15

–21.0dB

16

–22.5dB

*ROUT = 200Ω

PGA0

High

Low

High

Low

High

Low

High

Low

High

Low

High

Low

High

Low

High

Low

PGA1

High

High

Low

Low

High

High

Low

Low

High

High

Low

Low

High

High

Low

Low

PGA2

High

High

High

High

Low

Low

Low

Low

High

High

High

High

Low

Low

Low

Low

PGA3

High

High

High

High

High

High

High

High

Low

Low

Low

Low

Low

Low

Low

Low

POWER GAIN*

27.0dB

25.5dB

24.0dB

22.5dB

21.0dB

19.5dB

18.0dB

16.5dB

15.0dB

13.5dB

12.0dB

10.5dB

9.0dB

7.5dB

6.0dB

4.5dB (Note 3)

5524f

2

�LT5524

DC ELECTRICAL CHARACTERISTICS VCC = 5V, VCCO = 5V, EN = 3V, TA = 25°C, unless otherwise noted.

(Note 7) (Test circuits shown in Figures 9 and 10)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

4.75

5

5.25

V

3

5

5.5

V

1.15

1.3

Normal Operating Conditions

VCC

Supply Voltage (Pins 2, 19)

(Note 4)

VCCO

OUT+, OUT– Output Pin DC Common Mode Voltage

OUT+, OUT–

Connected to VOSUP via

Choke Inductors or Resistors (Note 5)

Shutdown DC Characteristics, EN = 0.6V

VIN(BIAS)

IN+, IN– Bias Voltage

Max Gain (Note 6)

1.5

V

IIL(PGA)

PGAO, PGA1, PGA2, PGA3 Input Current

VIN = 0.6V

20

µA

IIH(PGA)

PGAO, PGA1, PGA2, PGA3 Input Current

VIN = 5V

20

µA

IOUT

OUT+, OUT– Current

All Gain Settings

ICC

VCC Supply Current

All Gain Settings (Note 4)

44

20

µA

100

µA

0.6

V

Enable and PGA Inputs DC Characteristics

VIL

EN and PGAx Input Low Voltage

x = 0, 1, 2, 3

VIH

EN and PGAx Input High Voltage

x = 0, 1, 2, 3

IIL(PGA)

PGAO, PGA1, PGA2, PGA3 Input Current

VIN = 0.6V

IIH(PGA)

PGAO, PGA1, PGA2, PGA3 Input Current

VIN = 3V and 5V

IIL(EN)

EN Input Current

VIN = 0.6V

IIH(EN)

EN Input Current

VIN = 3V

VIN = 5V

3

V

20

µA

15

30

µA

4

20

µA

18

38

100

µA

µA

1.48

1.65

V

DC Characteristics, EN = 3V

VIN(BIAS)

IN+, IN– Bias Voltage

RIN

Input Differential Resistance

All Gain Settings (DC)

122

Ω

gm

Amplifier Transconductance

Max Gain

0.15

S

IOUT

OUT+, OUT– Quiescent Current

All Gain Settings, VOUT = 5V

Max Gain (Note 6)

1.34

17

20

24

mA

IOUT(OFFSET) Output Current Mismatch

All Gain Settings, IN+, IN–

ICC

VCC1 + VCC2 Supply Current

Max Gain (Note 4)

Min Gain (Note 4)

34

36

40

43

mA

mA

ICC(TOTAL)

Total Supply Current

ICC + 2 • IOUT (Max Gain)

75

91

mA

Open

100

µA

5524f

3

�LT5524

AC ELECTRICAL CHARACTERISTICS VCC = 5V, VCCO = 5V, EN = 3V, TA = 25°C, ROUT = 200Ω. Maximum gain

specifications are with respect to differential inputs and differential outputs, unless otherwise noted.

(Note 7) (Test circuits shown in Figures 9 and 10)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

Dynamic Performance

BW

Large-Signal –3dB Bandwidth

VOUT(CLIP) Output Voltage Clipping Levels

All Gain Settings (Note 8), ROUT = 100Ω

Each OUT+, OUT– with Respect to Ground

LF to 540

2

MHz

8

V

(Note 11)

POUT(MAX) Clipping Limited Maximum Sinusoidal

Output Power

All Gain Settings, Single Tone,

fIN = 100MHz (Note 10)

16

dBm

gm

Amplifier Transconductance

Max Gain, fIN = 100MHz

0.15

S

S12

Reverse Isolation

fIN = 100MHz (Note 9)

–92

dB

Output Third Order Intercept Point for

PGA0 = High (PGA1, PGA2, PGA3 Any State)

POUT = 4dBm (Each Tone), 200kHz Tone Spacing,

fIN = 100MHz

+40

dBm

Output Third Order Intercept Point for

PGA0 = Low (PGA1, PGA2, PGA3 Any State)

POUT = 4dBm (Each Tone), 200kHz Tone Spacing,

fIN = 100MHz

+36

dBm

Distortion and Noise

OIP3

HD2

Second Harmonic Distortion

POUT = 5dBm (Single Tone), fIN = 50MHz

–76

dBc

HD3

Third Harmonic Distortion

POUT = 5dBm (Single Tone), fIN = 50MHz

–72

dBc

NFLOOR

Output Noise Floor

(PGAO, PGA2, PGA3 Any State)

PGA1 = High, fIN = 100MHz

PGA1 = Low, fIN = 100MHz

–138

–140

dBm/Hz

dBm/Hz

NF

Noise Figure

Max Gain Setting, fIN = 100MHz

8.6

dB

PGA Settling Time

Output Settles within 10% of Final Value

500

ns

Enable/Disable Time

Output Settles within 10% of Final Value

600

ns

27

dB

Amplifier Power Gain and Gain Step

GMAX

Maximum Gain

fIN = 20MHz and 200MHz

GMIN

Minimum Gain

fIN = 20MHz and 200MHz

GSTEP

Gain Step Size

fIN = 20MHz and 200MHz

Gain Step Accuracy

fIN = 20MHz and 200MHz

4.5

0.8

1.5

dB

2.2

dB

±0.2

dB

Amplifier I/O Impedance (Parallel Values, Specified Differentially)

RIN

Input Resistance

fIN = 100MHz

122

Ω

CIN

Input Capacitance

fIN = 100MHz

2

pF

RO

Output Resistance

fIN = 100MHz

5

kΩ

CO

Output Capacitance

fIN = 100MHz

1.7

pF

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

Note 2: All voltage values are with respect to ground.

Note 3: Default state for open PGA inputs.

Note 4: VCC1 and VCC2 (Pins 2 and 19) are internally connected.

Note 5: External VOSUP is adjusted such that VCCO output pin common

mode voltage is as specified when resistors are used. For choke inductors

or transformer, VOSUP = VCCO = 5V typ.

Note 6: Internally generated common mode input bias voltage requires

capacitive or transformer coupling to the signal source.

Note 7: Specifications over the –40°C to 85°C operating temperature

range are assured by design, characterization and correlation with

statistical process controls. Gain always refers to power gain. Input

matching is assumed. PIN is the available input power. POUT is the power

into the external load, ROUT, as seen by the LT5524 differential outputs. All

dBm figures are with respect to 50Ω.

Note 8: High frequency operation is limited by the RC time constants at

the input and output ports. The low frequency (LF) roll-off is set by I/O

interface choice.

Note 9: Limited by package and board isolation.

Note 10: See “Clipping Free Operation” in the Applications Information

section. Refer to Figure 7.

Note 11: Although the instantaneous AC voltage on the OUT+ or OUT– pins

may in some situations safely exceed 8V (with respect to ground), in no

case should the DC voltage on these pins be allowed to exceed the

ABSMAX tested limit of 7V.

5524f

4

�LT5524

U W

TYPICAL PERFOR A CE CHARACTERISTICS

TA = 25°C, VCC = 5V, VCCO = 5V, EN = 3V, control

input levels VIL = 0.6V, VIH = 3V unless otherwise noted. (Test circuit shown in Figure 9)

Gain Error vs Attenuation Step at

25MHz, ROUT = 200Ω

Frequency Response for All Gain

Steps, ROUT = 200Ω

30

0.8

27

0.8

25°C

–40°C

85°C

0.6

24

15

12

9

0.4

GAIN ERROR (dB)

18

25°C

–40°C

85°C

0.6

0.4

21

GAIN ERROR (dB)

POWER GAIN (dB)

Gain Error vs Attenuation Step at

100MHz, ROUT = 200Ω

0.2

0

–0.2

0.2

0

–0.2

–0.4

–0.4

–0.6

–0.6

6

3

–0.8

0

100

FREQUENCY (MHz)

10

0

1000

3

12 15

6

9

18

ATTENUATION STEP (dB)

5524 G01

Maximum Gain vs VCC at

120MHz, ROUT = 200Ω

25

5.2

27.4

20

27.2

–40°C

85°C

27.0

25°C

26.8

4.4

26.6

4.2

26.4

4.9

5.1

4.7

4.9

5.1

5.5

5.3

VCC (V)

–5

–31 –28 –25 –22 –19 –16 –13 –10

PIN (dBm)

OIP3 vs Frequency at Pin = –23dBm,

Max Gain and 1.5dB Attenuation

Step, ROUT = 200Ω

–7

5524 G06

5524 G05

5524 G04

Harmonic Distortion vs POUT at

50MHz, Max Gain, ROUT = 200Ω

–40

54

–45

51

–50

–55

48

–60

HD(dBc)

45

MAX GAIN

42

39

–65

HD3

–70

HD2

–75

–80

1.5dB

ATTENUATION

STEP

36

–85

HD5

–90

33

30

ROUT = 200Ω

0

26.2

4.5

5.5

5.3

10

5

85°C

VCC (V)

OIP3 (dBm)

4.7

POUT (dBm)

GAIN (dB)

25°C

21

15

–40°C

4.8

4.0

4.5

12 15

6

9

18

ATTENUATION STEP (dB)

POUT vs PIN at 50MHz, Max Gain

27.6

4.6

3

5524 G03

5.4

5.0

0

5524 G02

Minimum Gain vs VCC at 120MHz,

ROUT = 200Ω

GAIN (dB)

–0.8

21

HD4

–95

–100

0

50

100

150

200

FREQUENCY (MHz)

5524 G07

–6

–3

0

6

3

POUT (dBm)

9

12

15

5524 G08

5524f

5

�LT5524

U W

TYPICAL PERFOR A CE CHARACTERISTICS

Two tones, 200kHz spacing, TA = 25°C, EN = 3V,

VCC = 5V, VCCO = 5V, control input levels VIL = 0.6V, VIH = 3V unless otherwise noted. (Test circuit shown in Figure 10)

NF vs Attenuation Step at

Freq = 100MHz

Noise Figure vs Frequency

Output Noise Floor vs Attenuation

Step, Freq = 100MHz, ROUT = 200Ω

–136

30

10.0

27

9.5

8.5

15

9

3dB ATTENUATION STEP

(PGA1 = LOW)

7.5

18

12

MAX GAIN

8.0

NOISE FLOOR (dBm/Hz)

21

NF (dB)

NF (dB)

9.0

–137

24

1.5dB ATTENUATION STEP

(PGA0 = LOW)

6

PGA1 = HIGH

–138

–139

PGA1 = LOW

–140

–141

3

7.0

0

50

0

100 150 200 250 300 350 400

FREQUENCY (MHz)

–142

0

3

6

9

12

18

15

ATTENUATION STEP (dB)

5524 G09

21

0

3

6

9

12 15 18

ATTENUATION STEP (dB)

5524 G11

5524 G10

Pulse Response vs Output Level at

Max Gain. Indicated Voltage Levels

are into 50Ω External Load

21

Single-Ended Output Current

vs Attenuation Step

VIN(BIAS) vs Attenuation Step

21.0

1.60

20.5

1.55

CURRENT (mA)

2VP-P

1.5VP-P

1VP-P

INPUTS

20.0

VIN(BIAS) (V)

COUT = 0.82pF

85°C

1.50

–40°C

1.45

85°C

25°C

25°C

19.5

–40°C

19.0

2ns/DIV

5524 G12

1.40

0

6

9

12 15 18

ATTENUATION STEP (dB)

3

21

0

6

9

12 15 18

ATTENUATION STEP (dB)

3

5524 G14

5524 G13

ICC Shutdown Current vs VCC,

EN = 0.6V

Total ICC vs Attenuation Step

70

78

85°C

75

25°C

60

85°C

50

CURRENT (µA)

CURRENT (mA)

80

73

–40°C

70

25°C

40

30

–40°C

20

68

65

21

10

0

3

6

9

12 15 18

ATTENUATION STEP (dB)

21

0

4.5

4.7

4.9

5.1

5.3

5.5

INPUT VCC (V)

5524 G15

5524 G16

5524f

6

�LT5524

U

U

U

PI FU CTIO S

EN (Pin 1): Enable Pin for Amplifier. When the input

voltage is higher than 3V, the amplifier is turned on. When

the input voltage is less than or equal to 0.6V, the amplifier

is turned off. This pin is internally pulled to ground if not

connected.

PGA2 (Pin 11): Amplifier PGA Control Input Pin for the 6dB

Attenuation Step (see Programmable Gain table). Input is

high when the input voltage is greater than 3V. Input is low

when the input voltage is less than or equal to 0.6V. This

pin is internally pulled to ground if not connected.

VCC1 (Pin 2): Power Supply. This pin is internally connected

to VCC2 (Pin 19). Decoupling capacitors (1000pF and 0.1µF

for example) may be required in some applications.

PGA3 (Pin 12): Amplifier PGA Control Input Pin for 12dB

Attenuation Step (see Programmable Gain table). Input is

high when the input voltage is greater than 3V. Input is low

when the input voltage is less than or equal to 0.6V. This

pin is internally pulled to ground if not connected.

GND (Pins 3, 4, 7, 8, 13, 14, 17, 18): Ground.

IN+ (Pin 5): Positive Signal Input Pin with Internal DC

Bias.

OUT+ (Pin 15): Positive Amplifier Output. A transformer

with center tap tied to VCC or a choke inductor is recommended to source the DC quiescent current.

IN– (Pin 6): Negative Signal Input Pin with Internal DC

Bias.

OUT– (Pin 16): Negative Amplifier Output. A transformer

with center tap tied to VCC or a choke inductor is recommended to source the DC quiescent current.

PGA0 (Pin 9): Amplifier PGA Control Input Pin for the 1.5dB

Attenuation Step (see Programmable Gain table). Input is

high when the input voltage is greater than 3V. Input is low

when the input voltage is less than or equal to 0.6V. This

pin is internally pulled to ground if not connected.

VCC2 (Pin 19): Power Supply. This pin is internally connected to VCC1 (Pin 2).

NC (Pin 20): Not Connected.

PGA1 (Pin 10): Amplifier PGA Control Input Pin for the 3dB

Attenuation Step (see Programmable Gain table). Input is

high when the input voltage is greater than 3V. Input is low

when the input voltage is less than or equal to 0.6V. This

pin is internally pulled to ground if not connected.

Exposed Pad (Pin 21): Ground. This pin must be soldered

to the printed circuit board ground plane for good heat

transfer.

W

BLOCK DIAGRA

LT5524

5

6

IN+

ATTENUATOR

IN–

RIN

100Ω

VOLTAGE REGULATOR

AND BIAS

GND (3, 4, 7, 8

13, 14, 17, 18)

VCC1

2

VCC2

19

OUT –

OUT+

GAIN CONTROL

LOGIC

PGA3

12

16

AMPLIFIER

ENABLE

CONTROL

PGA2 PGA1

11

10

15

PGA0

9

NC

20

EN

1

21

5524 F01

Figure 1. Functional Block Diagram

5524f

7

�LT5524

U

W

U U

APPLICATIO S I FOR ATIO

Circuit Operation

The LT5524 is a high linearity amplifier with high impedance output (Figure 1). It consists of the following

sections:

• An input variable attenuator “gain-control” block with

122Ω input impedance

• A differential transconductance amplifier, with enable

input

• An internal bias block with internal voltage regulator

• A gain control logic block

The LT5524 amplifier provides amplification with very low

distortion using a linearized open-loop architecture. In

contrast with high linearity amplifiers employing negative

feedback, the LT5524 offers:

where:

gm is the LT5524 transconductance = 0.15S.

RIN is the LT5524 differential input impedance ≅ 122Ω.

Input impedance matching is assumed.

ROUT is the external differential output impedance as

seen by the LT5524’s differential outputs. ROUT should

be distinguished from the actual load impedance, RLOAD,

which will typically be coupled to the LT5524 output by

an impedance transformation network.

The power gain as a function of ROUT is plotted in Figure 2.

The ideal relationship is linear. The curved line indicates

the roll-off due to the finite (noninfinite) output resistance

of the LT5524.

45

• Stable operation for any practical load

40

• A capacitive output reactance (not inductive) that provides peaking free AC response to capacitive loads

35

The LT5524 is a transconductance amplifier and its operation can be understood conceptually as consisting of two

steps: First, the input signal voltage is converted to an

output current. The intermodulation distortion (in dBc) of

the LT5524 output current is determined by the input

signal level, and is almost independent of the output load

conditions. Thus, the LT5524’s input IP3 is also nearly

independent of the output load.

Next, the external output load (ROUT) converts the output

current to output voltage (or power). The LT5524’s voltage and power gain both increase with increasing ROUT.

Accordingly, the output power and output IP3 also increase with increasing ROUT. The actual output linearity

performance in the application will thus be set by the

choice of output load, as well as by the output network.

Maximum Gain Calculation

The maximum power gain (with the 0dB attenuation step)

is:

GAIN (dB)

• Exceptional reverse isolation of –100dB at 50MHz and

–78dB at 300MHz (package and board leakage limited)

30

25

20

15

10

IDEAL

WITH RO

5

0

20

100

1000 2000

ROUT (Ω)

5524 F02

Figure 2. Power Gain as a Function of ROUT

The actual available output power (as well as power gain

and OIP3) will be reduced by losses in the output interface,

consisting of:

• The insertion loss of the output impedance transformation network (for example the transformer insertion

loss in Figure 6)

• About –3dB loss if a matching resistor (RMATCH in

Figure 6) is used to provide output load impedance

back-matching (for example when driving transmission lines)

GPWR(dB) = 10 • log(gm2 • RIN • ROUT)

5524f

8

�LT5524

U

W

U U

APPLICATIO S I FOR ATIO

VOSUP

Input Interface

C3

For the lowest noise and highest linearity, the LT5524

should be driven with a differential input signal. Singleended drive will severely degrade linearity and noise

performance.

• Match the source impedance to the LT5524, RIN ≅ 122Ω

• Provide well balanced differential input drive (capacitor

C2 in Figure 4)

• Minimize insertion loss to avoid degrading the noise

figure (NF)

RLOAD

50Ω

C2

RLOAD

50Ω

ROUT

+

LT5524 F05

Figure 5. Output Impedance-Matched

and Capacitively Coupled to a Differential Load

Input matching network design criteria are:

• DC block the LT5524 internal bias voltage (see Input

Bias Voltage section for DC coupling information)

R2

51Ω C1

–

RIN

122Ω

IN–

Example input matching networks are shown in Figures 3

and 4.

R1

51Ω

LT5524

IN+

Note: In Figure 5, (choke) inductors may be placed in

parallel with or used to replace resistors R1 and R2, thus

eliminating the DC voltage drop across these resistors.

VOSUP

IN+

IN–

LT5524

–

RIN

122Ω

C1

RMATCH

255Ω

(OPTIONAL)

ROUT

+

RLOAD

50Ω

T2

4:1

•

•

•

LT5524 F06

R1

50Ω

C1

VSRC R2

50Ω

C2

LT5524

IN+

Figure 6. Output Impedance-Matched and

Transformer-Coupled to a Single-Ended Load

–

RIN

122Ω

IN–

+

LT5524 F03

Figure 3. Input Capacitively-Coupled to a Differential Source

RSRC

50Ω

T1

1:2

•

VSRC

IN+

•

•

IN–

C2

0.33µF

• Provide DC isolation between the LT5524 DC output

voltage and RLOAD.

• Provide a path for the output DC current from the output

voltage source VOSUP.

LT5524

–

RIN

122Ω

+

Output network design criteria are:

LT5524 F04

Figure 4. Input Transformer-Coupled to a Single-Ended Source

Output Interface

The output interface network provides an impedance

transformation between the actual load impedance, RLOAD,

and the LT5524 output loading, ROUT, chosen to maximize

power or linearity, or to minimize output noise, or for some

other criteria as explained in the following sections.

Two examples of output matching networks are shown in

Figures 5 and 6 (as implemented in the LT5524 demo

boards).

• Provide an impedance transformation, if required, between the load impedance, RLOAD, and the optimum

ROUT loading.

• Set the bandwidth of the output network.

• Optional: Provide board output impedance matching

using resistor RMATCH (when driving a transmission

line).

• Use high linearity passive parts to avoid introducing

noninearity.

Note that there is a noise penalty of up to 6dB when using

power delivered by only one output in Figure 5.

5524f

9

�LT5524

U

W

U U

APPLICATIO S I FOR ATIO

Clipping Free Operation

To avoid current clipping, the output signal current should

not exceed the DC quiescent current, IOUT = 20mA (typical). Correspondingly, the maximum input voltage,

VIN(MAX), is IOUT/gm = 133mV (peak). In power terms,

PIN(MAX) = –11.5dBm (assuming RIN = 122Ω).

To avoid output voltage clipping (due to LT5524 output

stage saturation or breakdown), the single-ended output

voltage swing should stay within the specified limits; i.e.,

2V ≤ VOUT ≤ 8V. For a DC output bias of 5V, the maximum

single ended swing will be 3Vpeak and the maximum

differential swing will be 6Vpeak. The simultaneous onset

of both current and voltage limiting occurs when ROUT =

6Vpeak/20mA = 300Ω (typ) for a maximum POUT =

17.8dBm. This calculation applies for a sinusoidal signal.

For nonsinusoidal signals, use the appropriate crest factor to calculate the actual maximum power that avoids

output clipping.

Although the instantaneous AC voltage on the OUT+ or

OUT– pins may in some situations safely exceed 8V (with

respect to ground), in no case should the DC voltage on

these pins be allowed to exceed the ABSMAX tested limit

of 7V.

For nonoptimal ROUT values, the maximum available output power will be lower and can be calculated (considering

current limiting for ROUT < 300Ω, and voltage limiting for

ROUT > 300Ω). The result of this calculation is shown in

Figure 7.

The LT5524 input should not be overdriven (PIN >

–11.5dBm at maximum gain). The consequences of overdrive are reduced bandwidth and, when the frequency is

greater than 50MHz, reduced output power. At reduced

gain settings, the maximum PIN is increased by an amount

equal to the gain reduction.

Input Bias Voltage

The LT5524 IN+, IN– signal inputs are internally biased to

1.48V common mode when enabled, and to 1.26V in

VCC = VCCO = 5V

CURRENT

LIMIT

20

POUT(MAX) (dBm)

The LT5524 is a class A amplifier. To avoid signal distortion, the user must ensure that the LT5524 outputs do not

enter into current or voltage limiting. The following discussion applies to maximum gain operation.

25

VOLTAGE

LIMIT

15

10

5

0

20

100

1000 2000

ROUT (Ω)

5524 F07

Figure 7. Maximum Output Power as a Function of ROUT

shutdown mode. These inputs are typically coupled by

means of a capacitor or a transformer to a signal source,

and impedance matching is assumed. In shutdown mode,

the internal bias can handle up to 1µA leakage on the input

coupling capacitors. This reduces the turn-on delay due to

the input coupling RC time constant when exiting shutdown mode.

If DC coupling to the input is required, the external

common mode bias should track the LT5524’s internal

common mode level. The DC current from the LT5524

inputs should not exceed IIN(SINK) = –200µA and IIN(SOURCE)

= 400µA.

Stability Considerations

The LT5524’s open-loop architecture allows it to drive any

practical load. Note that LT5524 gain is proportional to the

load impedance, and may exceed the reverse isolation at

frequencies above 1GHz if the LT5524’s outputs are left

unloaded, with instability as the undesirable consequence.

In such cases, placing a resistive differential load (e.g., 4k)

or a small capacitor at the LT5524 outputs can be used to

limit the maximum gain.

The LT5524 has about 20GHz gain-bandwidth product.

Hence, attention must be paid to the printed circuit board

layout to avoid output pin to input pin signal coupling (the

evaluation board layout is a good example). Due to the

LT5524’s internal power supply regulator, external supply

decoupling capacitors typically are not required. Likewise,

decoupling capacitors on the LT5524 control inputs typically are not needed. Note, however, that the Exposed Pad

5524f

10

�LT5524

U

W

U U

APPLICATIO S I FOR ATIO

on the LT5524 package must be soldered to a good ground

plane on the PCB.

PGA Function, Linearity and NF

As described in the Circuit Operation section, the LT5524

consists of a variable (step) attenuator followed by a high

gain output amplifier. The overall gain of the LT5524 is

digitally controlled by means of four gain control pins with

internal pull-down. Minimum gain is programmed when

the gain control pins are set low or left floating. In

shutdown mode, these PGA inputs draw