National Semiconductor is now part of

Texas Instruments.

Search http://www.ti.com/ for the latest technical

information and details on our current products and services.

�LMC8101

Rail-to-Rail Input and Output, 2.7V Op Amp in

micro SMD package with Shutdown

General Description

Features

The LMC8101 is a Rail-to-Rail Input and Output high performance CMOS operational amplifier. The LMC8101 is ideal

for low voltage (2.7V to 10V) applications requiring Rail-toRail inputs and output. The LMC8101 is supplied in the die

sized micro SMD as well as the 8 pin MSOP packages. The

micro SMD package requires 75% less board space as

compared to the SOT23-5 package. The LMC8101 is an

upgrade to the industry standard LMC7101.

The LMC8101 incorporates a simple user controlled methodology for shutdown. This allows ease of use while reducing the total supply current to 1nA typical. This extends

battery life where power saving is mandated. The shutdown

input threshold can be set relative to either V+ or V− using

the SL pin (see Application Note section for details).

Other enhancements include improved offset voltage limit,

three times the output current drive and lower 1/f noise when

compared to the industry standard LMC7101 Op Amp. This

makes the LMC8101 ideal for use in many battery powered,

wireless communication and Industrial applications.

VS = 2.7V, TA = 25˚C, RL to V+/2, Typical values unless

specified.

n Rail-to-Rail Inputs

n Rail-to-Rail Output

Swing

Within 35mV of Supplies (RL =2kΩ)

n Packages Offered:

n

micro SMD package

1.39mm x 1.41mm

n

MSOP package

3.0mm x 4.9mm

< 1mA (max)

n Low Supply Current

n Shutdown Current

1µA (max)

n Versatile Shutdown feature

10µs turn-on

n Output Short Circuit Current

10mA

± 5 mV (max)

n Offset Voltage

n Gain-Bandwidth

1MHz

n Supply Voltage Range

2.7V-10V

n THD

0.18%

n Voltage Noise

36

Applications

n

n

n

n

n

n

Portable Communication (voice, data)

Cellular Phone Power Amp Control Loop

Buffer AMP

Active Filters

Battery Sense

VCO Loop

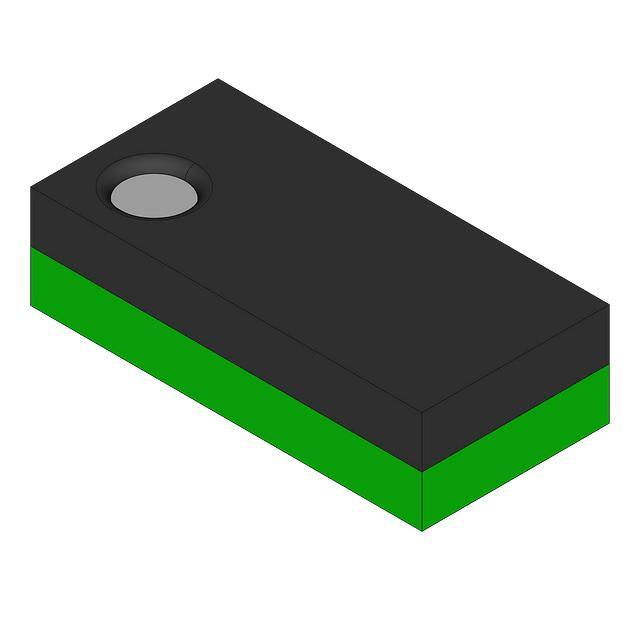

Connection Diagrams

8-Pin MSOP

micro SMD

10124079

Top View

10124080

Top View

© 2004 National Semiconductor Corporation

DS101240

www.national.com

LMC8101 Rail-to-Rail Input and Output, 2.7V Op Amp in micro SMD package with Shutdown

May 2004

�LMC8101

Absolute Maximum Ratings (Note 1)

Junction Temperature(Note 4)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Soldering Information

ESD Tolerance

2KV (Note 2)

200V (Note 13)

VIN differential

± Supply Voltage

Output Short Circuit Duration

+

Supply Voltage (V − V )

Voltage at Input/Output pins

235˚C

Wave Soldering (10 sec.)

260˚C

(Note 1)

Supply Voltage (V+ - V−)

2.7V to 10V

Junction Temperature Range

(Note 4)

12V

V+ +0.8V, V− −0.8V

−40˚C to +85˚C

Package Thermal Resistance (θJA) (Note 4)

± 10mA

Current at Input Pin

Infrared or Convection (20 sec.)

Operating Ratings

(Notes 3, 11)

−

+150˚C

micro SMD

Current at Output Pin

(Notes 3, 12)

± 80mA

± 80mA

Current at Power Supply pins

Storage Temperature Range

220˚C/W

MSOP pkg. 8 pin Surface

Mount

230˚C/W

−65˚C to +150˚C

2.7V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for TJ = 25˚C, V+ = 2.7V, V− = 0V, VCM = VO = V+/2 and RL > 1 MΩ to V+/2.

Boldface limits apply at the temperature extremes.

Symbol

Parameter

VOS

Input Offset Voltage

TCVOS

Input Offset Voltage Average Drift

IB

Input Bias Current

IOS

Conditions

Typ

(Note 5)

Limit

(Note 6)

Units

± 0.70

±5

±7

mV

max

4

µV/˚C

±1

± 64

pA

max

Input Offset Current

0.5

32

pA

max

(Note 7)

Rin CM

Input Common Mode Resistance

10

Cin CM

Input Common Mode Capacitance

10

CMRR

Common Mode Rejection Ratio

GΩ

pF

0V < = VCM < = 2.7V

78

60

VS = 3V

0V < = VCM < = 3V

78

64

60

dB

min

PSRR

Power Supply Rejection Ratio

VS = 2.7V to 3V

57

50

48

dB

min

CMVR

Input Common-Mode Voltage Range

VS = 2.7V

CMRR > = 50dB

0.0

0.0

V

max

3.0

2.7

V

min

−0.2

−0.1

V

max

3.2

3.1

V

min

VS = 3V

CMRR > = 50dB

www.national.com

2

�(Continued)

Unless otherwise specified, all limits guaranteed for TJ = 25˚C, V+ = 2.7V, V− = 0V, VCM = VO = V+/2 and RL > 1 MΩ to V+/2.

Boldface limits apply at the temperature extremes.

Symbol

AVOL

VO

Parameter

Large Signal Voltage Gain

Output Swing

High

Output Swing

Low

ISC

IS

Output Short Circuit Current

Supply Current

Conditions

Typ

(Note 5)

Limit

(Note 6)

Sourcing

RL = 2kΩ to V+/2

VO = 1.35V to 2.45V

3162

1000

562

Sinking

RL = 2kΩ to V+/2

VO = 1.35V to 0.25V

3162

804

562

Sourcing

RL = 10kΩ to V+/2

VO = 1.35V to 2.65V

4000

1778

1000

Sinking

RL = 10kΩ to V+/2

VO = 1.35V to 0.05V

4000

1778

1000

Units

V/V

min

V/V

min

RL = 2kΩ to V+/2

VID = 100mV

2.67

2.64

2.62

V

min

RL = 10kΩ to V+/2

VID = 100mV

2.69

2.68

2.67

V

min

RL = 2kΩ to V+/2

VID = −100mV

32

100

150

mV

max

RL = 10kΩ to V+/2

VID = −100mV

10

30

70

mV

max

Sourcing to V+/2

VID = 100mV (Note 11)

20

14

6

mA

min

Sinking to V+/2

VID = −100mV (Note 11)

10

5

4

mA

min

No load, normal operation

0.70

1.0

1.2

mA

max

Shutdown mode

0.001

1

µA

max

15

µs

±1

± 64

pA

max

1

0.8

V/µs

min

Ton

Shutdown Turn-on time

(Note 9)

10

Toff

Shutdown Turn-off time

(Note 9)

1

Iin

"SL" and "SD" Input Current

SR

Slew Rate (Note 8)

AV = +1, RL = 10kΩ to V+/2

VI = 1VPP

fu

Unity Gain-Bandwidth

VI = 10mV, RL = 2kΩ to V+/2

750

KHz

GBW

Gain Bandwidth Product

f = 100KHz

1

MHz

en

Input-Referred Voltage Noise

f = 10KHz, RS = 50Ω

36

in

Input-Referred Current Noise

f = 10KHz

1.5

THD

Total Harmonic Distortion

f = 1KHz, AV = +1,

VO = 2.2Vpp,

RL = 600Ω to V+/2

0.18

3

µs

%

www.national.com

LMC8101

2.7V Electrical Characteristics

�LMC8101

± 5V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for TJ = 25˚C, V+ =5V, V− = −5V, VCM = VO = 0V, and RL > 1 MΩ to gnd.

Boldface limits apply at the temperature extremes.

Symbol

Parameter

VOS

Input Offset Voltage

TCVos

Input Offset Voltage Average Drift

IB

Input Bias Current

IOS

Conditions

Typ

(Note 5)

Limit

(Note 6)

Units

± 0.7

±5

±7

mV

max

4

µV/˚C

±1

± 64

pA

max

Input Offset Current

0.5

32

pA

max

Rin CM

Input Common Mode Resistance

10

GΩ

Cin CM

Input Common Mode Capacitance

10

pF

(Note 7)

CMRR

Common-Mode Rejection Ratio

−5V < = VCM < = 5V

PSRR

Power Supply Rejection Ratio

VS = 5V to 10V

80

76

72

dB

min

CMVR

Input Common-Mode Voltage Range

CMRR ≥ 50 dB

−5.3

−5.2

−5.0

V

max

5.3

5.2

5.0

V

min

AVOL

VO

Large Signal Voltage Gain

Output Swing

High

Output Swing

Low

ISC

Output Short Circuit Current

87

70

67

dB

min

Sourcing

RL = 600Ω

VO = 0V to 4V

34.5

Sinking

RL = 600Ω

VO = 0V to −4V

34.5

17.8

3.16

Sourcing

RL = 2kΩ

VO = 0V to 4.6V

138

31.6

17.8

Sinking

RL = 2kΩ

VO = 0V to −4.6V

138

17.8

10

31.6

10

V/mV

min

V/mV

min

RL = 600Ω

VID = 100mV

4.73

4.60

4.54

V

min

RL = 2kΩ

VID = 100mV

4.90

4.85

4.83

V

min

RL = 600Ω

VID = −100mV

−4.85

−4.75

−4.65

V

max

RL = 2kΩ

VID = −100mV

−4.95

4.90

−4.84

V

max

Sourcing, VID = 100mV

(Note 3),(Note 11)

49

30

25

mA

min

Sinking, VID = −100mV

(Note 3),(Note 11)

90

60

52

mA

min

1.1

1.7

1.9

mA

max

IS

Supply Current

No load, normal operation

0.001

1

µA

Ton

Shutdown Turn-on time

(Note 9)

10

15

µs

Toff

Shutdown Turn-off time

(Note 9)

1

Iin

"SL" and "SD" Input Current

Shutdown mode

www.national.com

±1

4

µs

± 64

pA

max

�(Continued)

Unless otherwise specified, all limits guaranteed for TJ = 25˚C, V+ =5V, V− = −5V, VCM = VO = 0V, and RL > 1 MΩ to gnd.

Boldface limits apply at the temperature extremes.

Symbol

Parameter

Conditions

Typ

(Note 5)

Limit

(Note 6)

Units

SR

Slew Rate

(Note 8)

AV = +10, RL = 10kΩ,

VO = 10Vpp, CL = 1000pF

1.2

V/µs

fu

Unity Gain-Bandwidth

VI = 10mV

RL = 2kΩ

840

KHz

GBW

Gain Bandwidth Product

f = 10KHz

1.3

MHz

en

Input-Referred Voltage Noise

f = 10KHz, Rs = 50Ω

33

in

Input-Referred Current Noise

f = 10KHz

1.5

THD

Total Harmonic Distortion

f = 10KHz, AV = +1,

VO =8Vpp, RL = 600Ω

0.2

%

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human body model, 1.5kΩ in series with 100pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the

maximum allowed junction temperature at 150˚C. Output currents in excess of 40mA over long term may adversely affect reliability.

Note 4: The maximum power dissipation is a function of TJ(MAX), θJA and TA. The maximum allowable power dissipation at any ambient temperature is

PD = (TJ(MAX) − TA)/θJA. All numbers apply for packages soldered directly onto a PC board.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Positive current corresponds to current flowing into the device.

Note 8: Slew rate is the slower of the rising and falling slew rates.

Note 9: Shutdown Turn-on and Turn-off times are defined as the time required for the output to reach 90% and 10%, respectively, of its final peak to peak swing

when set for Rail to Rail output swing with a 100KHz sine wave, 2KΩ load, and AV = +10.

Note 10: Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.

Note 11: Short circuit test is a momentary test. See Note 12.

Note 12: Output short circuit duration is infinite for VS < 6V. Otherwise, extended period output short circuit may damage the device.

Note 13: machine Model, 0Ω in series with 200pF.

5

www.national.com

LMC8101

± 5V Electrical Characteristics

�LMC8101

Typical Performance Characteristics

VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

specified

Gain/Phase vs. Frequency (RL = 2k, VS = ± 1.35V)

Gain/Phase vs. Frequency (RL = 2k, VS = ± 5V)

10124001

10124002

Gain vs. Phase for various CL

VS = ± 1.35V

Gain/Phase vs. Frequency (RL = Open)

10124004

10124003

Unity Gain Frequency vs. Supply Voltage

Phase Margin vs. Supply Voltage

10124005

www.national.com

10124006

6

�specified (Continued)

Unity Gain Frequency and Phase Margin vs. Load

Unity Gain Frequency and Phase Margin vs. Load

10124007

10124008

PSRR vs. Frequency

PSRR vs. Frequency

10124010

10124009

Input Bias Current vs. Common Mode Voltage @ 85˚C

CMRR vs. Frequency

10124013

10124011

7

www.national.com

LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

�LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

specified (Continued)

Input Current vs. Temperature

VS = 10V

VIN vs. VOUT

10124023

10124091

VIN vs. VOUT

VIN vs. VOUT

10124083

10124028

VIN vs. VOUT

Supply Current vs. Supply Voltage

10124029

10124024

www.national.com

8

�specified (Continued)

Delta VOS vs. VCM

(Ref VCM = 1.35V)

Delta VOS vs. VCM

(Ref VCM = 5V)

10124092

10124093

Output Positive Swing vs. Supply Voltage

RL = 600Ω to V+/2

Offset Voltage vs. VSUPPLY

10124037

10124025

Output Negative Swing vs. Supply Voltage

RL = 600Ω to V+/2

Output Positive Swing vs. Supply Voltage

RL = 2k to V+/2

10124035

10124027

9

www.national.com

LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

�LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

specified (Continued)

Output Negative Swing vs.

Supply Voltage, RL = 2k to V+/2

Short Circuit Sinking Current vs. Supply Voltage

10124026

10124036

Undistorted Output Voltage Swing

vs. Output Load Resistance

Short Circuit Sourcing Current vs. Supply Voltage

10124030

10124046

Step Response 1% settling time and % overshoot vs.

Cap Load

Large Signal Step Response

10124015

10124014

www.national.com

10

�specified (Continued)

Small Signal Step Response

Large Signal Step Response

10124016

10124017

Small Signal Step Response

Small Signal Step Response

10124018

10124019

Large Signal Step Response

Large Signal Step Response

10124020

10124021

11

www.national.com

LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

�LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

specified (Continued)

Small Signal Step Response

Slew Rate vs. Supply Voltage

10124022

10124038

Slew Rate vs. Capacitive Load

Slew Rate vs. Capacitive Load

10124039

10124041

Slew Rate vs. Capacitive Load

Slew Rate vs. Capacitive Load

10124042

www.national.com

10124043

12

�specified (Continued)

Voltage Noise vs. VCM @ Various Frequencies

Voltage Noise vs. Frequency

10124012

10124040

THD+N vs. Amplitude

THD+N vs. Frequency

10124045

10124044

Sourcing Current vs. Output Voltage (VS = 2.7V)

Sinking Current vs. Output Voltage (VS = 2.7V)

10124087

10124085

13

www.national.com

LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

�LMC8101

Typical Performance Characteristics VS = 2.7V, Single Supply, VCM = V+/2, TA = 25˚C unless

specified (Continued)

Sourcing Current vs. Output Voltage (VS = 10V)

Sinking Current vs. Output Voltage (VS = 10V)

10124086

10124084

Cap Load vs. IOUT

Cap Load vs. Isolation Resistance

10124088

www.national.com

10124090

14

�SHUTDOWN FEATURES

The LMC8101 is capable of being turned off in order to

conserve power. Once in shutdown, the device supply current is drastically reduced (1µA maximum) and the output will

be "Tri-stated".

TINY PACKAGE

The LMC8101 is available in the micro SMD package as well

the 8 pin MSOP package. The micro SMD package requires

approximately 1/4 the board area of a SOT23. This package

is less than 1mm in height allowing it to be placed in absolute

minimum height clearance areas such as cellular handsets,

LCD panels, PCMCIA cards, etc. More information about the

micro SMD package can be found at: http://

www.national.com/appinfo/microsmd.

The shutdown feature of the LMC8101 is designed for flexibility. The threshold level of the SD input can be referenced

to either V- or V+ by setting the level on the SL input. When

the SL input is connected to V-, the SD threshold level is

referenced to V- and vice versa. This threshold will be about

1.5V from the supply tied to the SL pin. So, for this example,

the device will be in shutdown as long as the SD pin voltage

is within 1V of V-. In order to ensure that the device would not

"chatter" between active and shutdown states, hysteresis is

built into the SD pin transition (see Figure 1 for an illustration

of this feature). The shutdown threshold and hysteresis level

are independent of the supply voltage. Figure 1 illustration

applies equally well to the case when SL is tied to V+ and the

horizontal axis is referenced to V+ instead. The SD pin

should not be set within the voltage range from 1.1V to 1.9V

of the selected supply voltage since this is a transition region

and the device status will be undetermined.

CONVERSION BOARDS

In order to ease the evaluation of tiny packages such as the

micro SMD, there is a conversion board (LMC8101CONV)

available to board designers. This board converts a micro

SMD device into an 8 pin DIP package (see Figure 2,

Conversion Board Pin out diagram) for easier handling and

evaluation. This board can be ordered from National Semiconductor by contacting http://www.national.com .

10124089

FIGURE 2. micro SMD Conversion Board pin-out

INCREASED OUTPUT CURRENT

Compared to the LMC7101, the LMC8101 has an improved

output stage capable of up to three times larger output

sourcing and sinking current. This improvement would allow

a larger output voltage swing range compared to the

LMC7101 when connected to relatively heavy loads. For

lower supply voltages this is an added benefit since it increases the output swing range. For example, the LMC8101

can typically swing 2.5Vpp with 2mA sourcing and sinking

output current (Vs = 2.7V) whereas the LMC7101 output

swing would be limited to 1.9Vpp under the same conditions.

Also, compared to the LMC7101 in the SOT23 package, the

LMC8101 can dissipate more power because both the

MSOP and the micro SMD packages have 40% better heat

dissipation capability.

10124082

FIGURE 1. Supply Current vs. "SD" Voltage

Table 1, below, summarizes the status of the device when

the SL and SD pins are connected directly to V- or V+:

TABLE 1. LMC8101 Status Summary

SL

SD

LMC8101 Status

V−

V−

Shutdown

V−

V+

Active

V+

V+

Shutdown

V+

V−

Active

LOWER 1/f NOISE

The dominant input referred noise term for the LMC8101 is

the input noise voltage. Input noise current for this device is

of no practical significance unless the equivalent resistance

it looks into is 5MΩ or higher.

The LMC8101’s low frequency noise is significantly lower

than that of the LMC7101. For example, at 10Hz, the input

as comreferred spot noise voltage density is 85 nV

for the LMC7101. Over a frepared to about 200nV

quency range of 0.1Hz to 100Hz, the total noise of the

LMC8101 will be approximately 60% less than that of the

LMC7101.

In case shutdown operation is not needed, as can be seen in

Table 1, the two pins SL and SD can simply be connected to

opposite supply nodes to achieve "Active" operation. The SL

and SD should always be tied to a node; if left unconnected,

these high impedance inputs will float to an undetermined

state and the device status will be undetermined as well.

With the device in shutdown, once "Active" operation is

initiated, there will be a finite amount of time required before

the device output is settled to its final value. This time is less

than 15µs. In addition, there may be some output spike

during this time while the device is transitioning into a fully

15

www.national.com

LMC8101

operational state. Some applications may be sensitive to this

output spike and proper precautions should be taken in order

to ensure proper operation at all times.

Application Notes

�LMC8101

Application Notes

Isolation resistor between output and cap load:

•

This resistor will isolate the feedback path (where excessive

phase shift due to output capacitance can cause instability)

from the capacitive load. With a 10V supply, a 100Ω isolation

resistor allows unlimited capacitive load without oscillation

compared to only 300pF without this resistor (AV = +1).

Higher supply voltage:

•

Operating the LMC8101 at higher supply voltages allows

higher cap load tolerance. At 10V, the LMC8101’s low supply

voltage cap load limit of 300pF improves to about 600pF (AV

= +1).

Closed loop gain increase:

•

As with all Op Amps, the capacitive load tolerance of the

LMC8101 increases with increasing closed loop gain. In

applications where the load is mostly capacitive and the

resistive loading is light, stability increases when the

LMC8101 is operated at a closed loop gain larger than +1.

(Continued)

LOWER THD

When connected to heavier loads, the LMC8101 has lower

THD compared to the LMC7101. For example, with 5V supply at 10KHz and 2Vpp swing (Av = −2), the LMC8101 THD

(0.2%) is 60% less than the LMC7101’s. The LMC8101 THD

can be kept below 0.1% with 3Vpp at the output for up to

10KHz (refer to the Typical Characteristics Plots).

IMPROVING THE CAP LOAD DRIVE CAPABILITY

This can be accomplished in several ways:

Output resistive loading increase:

•

The Phase Margin increases with increasing load (refer to

the Typical Characteristics Plots). When driving capacitive

loads, stability can generally be improved by allowing some

output current to flow through a load. For example, the cap

load drive capability can be increased from 8200pF to

16000pF if the output load is increased from 5kΩ to 600Ω

(AV = +10, 25% overshoot limit, 10V supply).

Ordering Information

Package

Part Number

Package Marking

Transport Media

8-Bump micro SMD

Leaded

LMC8101BP

250 Units Tape and Reel

LMC8101BPX

A

2

8-Bump micro SMD

Lead Free

A

08

250 Units Tape and Reel

LMC8101TPX

8-Pin MSOP

www.national.com

LMC8101TP

LMC8101MM

LMC8101MMX

3k Units Tape and Reel

3k Units Tape and Reel

1k Units Tape and Reel

A11

3.5k Units Tape and Reel

16

NSC Drawing

BPA08FFB

TPA08FFA

MUA08A

�LMC8101

Physical Dimensions

inches (millimeters) unless otherwise noted

NOTES: UNLESS OTHERWISE SPECIFIED

1. EPOXY COATING

2. 63Sn/37Pb EUTECTIC BUMP

3. RECOMMENDED NON-SOLDER MASK DEFINED LANDING PAD.

4. PIN A1 IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION. REMAINING PINS ARE NUMBERED

COUNTERCLOCKWISE.

5. XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1 IS PACKAGE WIDTH, X2 IS PACKAGE LENGTH AND X3 IS

PACKAGE HEIGHT.

6. REFERENCE JEDEC REGISTRATION MO-211, VARIATION BC.

8-Bump micro SMD Package

Order Package Number LMC8101BP, LMC8101BPCONV or LMC8101BPX

NS Package Number BPA08FFB

X1 = 1.412 X2 = 1.412 X3 = 0.850

17

www.national.com

�LMC8101

Physical Dimensions

inches (millimeters) unless otherwise noted (Continued)

NOTES: UNLESS OTHERWISE SPECIFIED

1. EPOXY COATING

2. FOR SOLDER BUMP COMPOSITION, SEE “SOLDER INFORMATION”. IN THE PACKAGING SECTION OF THE NATIONAL SEMICONDUCTOR WEB

PAGE (www.national.com)

3. RECOMMENDED NON-SOLDER MASK DEFINED LANDING PAD.

4. PIN A1 IS ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION.

5. XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1 IS PACKAGE WIDTH, X2 IS PACKAGE LENGTH AND X3 IS

PACKAGE HEIGHT.

6. REFERENCE JEDEC REGISTRATION MO-211, VARIATION BC.

8-Bump micro SMD (Lead Free) Package

Order Package Number LMC8101TP, or LMC8101TPX

NS Package Number TPA08FFA

X1 = 1.412 mm X2 = 1.412 mm X3 = 0.5 mm

www.national.com

18

�inches (millimeters) unless otherwise noted (Continued)

8-Pin MSOP Package

Order Package Number LMC8101MM or LMC8101MMX

NS Package Number MUA08A

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a

significant injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products

Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification

(CSP-9-111S2) and contain no ‘‘Banned Substances’’ as defined in CSP-9-111S2.

National Semiconductor

Americas Customer

Support Center

Email: new.feedback@nsc.com

Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor

Asia Pacific Customer

Support Center

Email: ap.support@nsc.com

National Semiconductor

Japan Customer Support Center

Fax: 81-3-5639-7507

Email: jpn.feedback@nsc.com

Tel: 81-3-5639-7560

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

LMC8101 Rail-to-Rail Input and Output, 2.7V Op Amp in micro SMD package with Shutdown

Physical Dimensions

�