Product

Folder

Order

Now

Support &

Community

Tools &

Software

Technical

Documents

TPS84620

SLVSA43F – OCTOBER 2010 – REVISED APRIL 2018

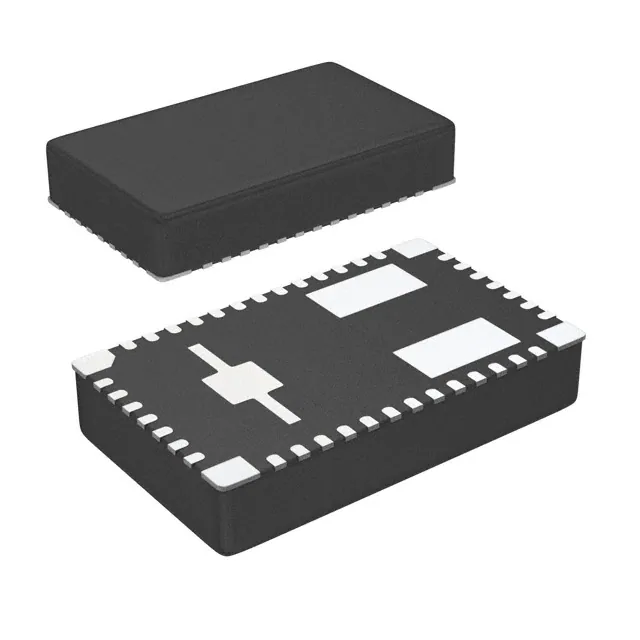

TPS84620 4.5-V to 14.5-V Input, 6-A Synchronous Buck, Integrated Power Solution

1 FEATURES

3 DESCRIPTION

•

The TPS84620RUQ is an easy-to-use integrated

power solution that combines a 6-A DC/DC converter

with power MOSFETs, an inductor, and passives into

a low profile, BQFN package. This total power

solution allows as few as 3 external components and

eliminates the loop compensation and magnetics part

selection process.

1

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Complete Integrated Power Solution Allows

Small Footprint, Low-Profile Design

Efficiencies Up To 96%

Wide-Output Voltage Adjust

1.2 V to 5.5 V, with 1% Reference Accuracy

Optional Split Power Rail allows

Input Voltage Down to 1.7 V

Adjustable Switching Frequency

(480 kHz to 780 kHz)

Synchronizes to an External Clock

Adjustable Slow Start

Output Voltage Sequencing / Tracking

Power Good Output

Programmable Undervoltage Lockout (UVLO)

Output Overcurrent Protection

Over Temperature Protection

Pre-bias Output Start-up

Operating Temperature Range: –40°C to +85°C

Enhanced Thermal Performance: 13°C/W

Meets EN55022 Class B Emissions

For Design Help Including SwitcherPro™ visit

http://www.ti.com/tps84620

2 APPLICATIONS

•

•

•

•

•

The 9×15×2.8 mm BQFN package is easy to solder

onto a printed circuit board and allows a compact

point-of-load design with greater than 90% efficiency

and excellent power dissipation with a thermal

impedance of 13°C/W junction to ambient. The

device delivers the full 6-A rated output current at

85°C ambient temperature without airflow.

The TPS84620 offers the flexibility and the featureset of a discrete point-of-load design and is ideal for

powering performance DSPs and FPGAs. Advanced

packaging technology afford a robust and reliable

power solution compatible with standard QFN

mounting and testing techniques.

SIMPLIFIED APPLICATION

PVIN

PWRGD

VIN

VIN

CIN

Broadband and Communications Infrastructure

Automated Test and Medical Equipment

Compact PCI / PCI Express / PXI Express

DSP and FPGA Point of Load Applications

High Density Distributed Power Systems

TPS84620

RT/CLK

SENSE+

INH/UVLO

SS/TR

COUT

VADJ

RSET

STSEL

100

VOUT

VOUT

AGND

95

PGND

90

Efficiency (%)

85

80

UDG-10021

75

70

VOUT = 3.3 V

fSW = 630 kHz

65

60

PVIN = VIN = 5 V

PVIN = VIN = 12 V

55

50

0

1

2

3

4

Output Current (A)

5

6

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS84620

SLVSA43F – OCTOBER 2010 – REVISED APRIL 2018

www.ti.com

Table 1. ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see

the TI website at www.ti.com.

4 Specifications

4.1

ABSOLUTE MAXIMUM RATINGS (1)

over operating temperature range (unless otherwise noted)

Input Voltage

Output Voltage

VALUE

UNIT

VIN

–0.3 to 16

V

PVIN

–0.3 to 16

V

INH/UVLO

–0.3 to 6

V

VADJ

–0.3 to 3

V

PWRGD

–0.3 to 6

V

SS/TR

–0.3 to 3

V

STSEL

–0.3 to 3

V

RT/CLK

–0.3 to 6

V

PH

–1 to 20

V

PH 10-ns Transient

–3 to 20

V

VDIFF (GND to exposed thermal pad)

–0.2 to 0.2

V

±100

µA

PH

Current Limit

A

PH

Current Limit

A

PVIN

Current Limit

A

–0.1 to 5

mA

–40 to 125 (2)

°C

–65 to 150

°C

245

°C

RT/CLK

Source Current

Sink Current

PWRGD

Operating Junction Temperature

Storage Temperature

Peak Reflow Case Temperature (3) (4)

Maximum Number of Reflows Allowed (3) (4)

3

Mechanical Shock

Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted

Mechanical Vibration

Mil-STD-883D, Method 2007.2, 20-2000Hz

(1)

(2)

(3)

(4)

2

1500

G

20

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

See the temperature derating curves in the Typical Characteristics section for thermal information.

For soldering specifications, refer to the Soldering Requirements for BQFN Packages application note.

Devices with a date code prior to week 14 2018 (1814) have a peak reflow case temperature of 240°C with a maximum of one reflow.

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

Product Folder Links: TPS84620

�TPS84620

www.ti.com

SLVSA43F – OCTOBER 2010 – REVISED APRIL 2018

4.2 THERMAL INFORMATION

LMZ31506H

THERMAL METRIC (1)

RUQ47

UNITS

47 PINS

Junction-to-ambient thermal resistance (2)

θJA

(3)

13

θJCtop

Junction-to-case (top) thermal resistance

θJB

Junction-to-board thermal resistance (4)

ψJT

Junction-to-top characterization parameter (5)

ψJB

Junction-to-board characterization parameter (6)

5

θJCbot

Junction-to-case (bottom) thermal resistance (7)

3.8

(1)

(2)

(3)

(4)

(5)

(6)

(7)

9

6

°C/W

2.5

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report (SPRA953).

The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

The junction-to-top characterization parameter, ψJT, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining RθJA, using a procedure described in JESD51-2a (sections 6 and 7).

The junction-to-board characterization parameter, ψJB, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining RθJA, using a procedure described in JESD51-2a (sections 6 and 7).

The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Spacer

4.3 PACKAGE SPECIFICATIONS

TPS84620

Weight

Flammability

MTBF Calculated reliability

UNIT

1.26 grams

Meets UL 94 V-O

Per Bellcore TR-332, 50% stress, TA = 40°C, ground benign

33.9 MHrs

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

Product Folder Links: TPS84620

3

�TPS84620

SLVSA43F – OCTOBER 2010 – REVISED APRIL 2018

4.4

www.ti.com

ELECTRICAL CHARACTERISTICS

over -40°C to 85°C free-air temperature, PVIN = VIN = 12 V, VOUT = 1.8 V, IOUT = 6A,

CIN1 = 2x 22 µF ceramic, CIN2 = 68 µF poly-tantalum, COUT1 = 4x 47 µF ceramic (unless otherwise noted)

PARAMETER

TEST CONDITIONS

IOUT

Output current

TA = 85°C, natural convection

VIN

Input bias voltage range

PVIN

Input switching voltage range

UVLO

VIN Undervoltage lockout

VOUT(adj)

VOUT

A

4.5

14.5

V

Over IOUT range

1.7 (1)

14.5

V

VIN = increasing

4.0

3.5

Output voltage adjust range

Over IOUT range

1.2

Set-point voltage tolerance

TA = 25°C, IOUT = 0A

Temperature variation

-40°C ≤ TA ≤ +85°C, IOUT = 0A

±0.3%

Line regulation

Over PVIN range, TA = 25°C, IOUT = 0A

±0.1%

Load regulation

Over IOUT range, TA = 25°C

±0.1%

Total output voltage variation

Includes set-point, line, load, and temperature variation

PVIN = VIN = 5 V

IO = 3 A

VINH-H

VINH-L

II(stby)

Inhibit Control

VOUT = 3.3V, fSW = 630kHz

90 %

VOUT = 2.5V, fSW = 530kHz

89 %

VOUT = 1.8V, fSW = 480kHz

87 %

VOUT = 1.5V, fSW = 480kHz

85 %

VOUT = 1.2V, fSW = 480kHz

83 %

VOUT = 3.3V, fSW = 630kHz

94 %

VOUT = 2.5V, fSW = 530kHz

92 %

VOUT = 1.8V, fSW = 480kHz

90 %

VOUT = 1.5V, fSW = 480kHz

88 %

VOUT = 1.2V, fSW = 480kHz

86 %

1.0 A/µs load step from 50 to 100% IOUT(max)

A

VOUT

over/undershoot

60

–0.3

-1.15

INH > 1.26 V

-3.4

Input standby current

INH pin to AGND

2

VOUT falling

Over VIN and IOUT ranges, RT/CLK pin OPEN

fCLK

Synchronization frequency

VCLK-H

CLK High-Level Threshold

VCLK-L

CLK Low-Level Threshold

DCLK

CLK Duty cycle

CLK Control

Good

94%

Fault

109%

Fault

91%

Good

106%

Thermal shutdown hysteresis

V

μA

μA

4

µA

0.3

V

560

kHz

480

780

kHz

2.0

5.5

V

0.8

V

400

480

20%

Thermal shutdown

(3)

1.05

INH < 1.1 V

PWRGD Thresholds

mV

Open

INH Hysteresis current

I(PWRGD) = 2 mA

mVPP

µs

1.30

Switching frequency

4

(2)

80

Inhibit Low Voltage

PWRGD Low Voltage

(3)

±1.5%

V

Recovery time

Inhibit High Voltage

fSW

(1)

(2)

(2)

V

11

INH Input current

Thermal Shutdown

±1.0%

30

VOUT rising

Power

Good

5.5

93 %

20 MHz bandwith

4.5

3.85

VOUT = 5V, fSW = 780kHz

Overcurrent threshold

Transient response

UNIT

Over IOUT range

VIN = decreasing

Output voltage ripple

MAX

6

Efficiency

ILIM

TYP

0

PVIN = VIN = 12 V

IO = 3 A

η

MIN

160

80%

175

°C

10

°C

The minimum PVIN voltage is 1.7V or (VOUT+ 0.5V) , whichever is greater. VIN must be greater than 4.5V.

The stated limit of the set-point voltage tolerance includes the tolerance of both the internal voltage reference and the internal

adjustment resistor. The overall output voltage tolerance will be affected by the tolerance of the external RSET resistor.

This control pin has an internal pullup. If this pin is left open circuit, the device operates when input power is applied. A small lowleakage (