Product

Folder

Order

Now

Support &

Community

Tools &

Software

Technical

Documents

TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

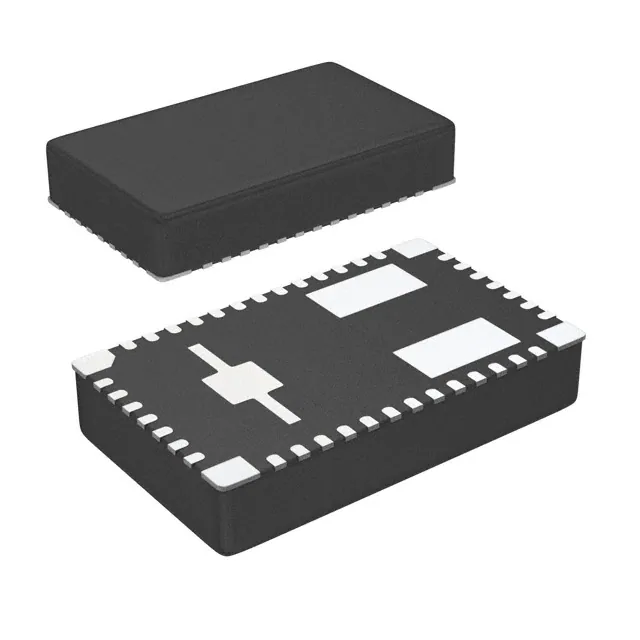

TPS84621 2.95-V to 14.5-V Input, 6-A Synchronous Buck, Integrated Power Solution

1 FEATURES

3 DESCRIPTION

•

The TPS84621 is an easy-to-use integrated power

solution that combines a 6-A DC-to-DC converter with

power MOSFETs, an inductor, and passives into a

low profile, BQFN package. This total power solution

allows as few as three external components and

eliminates the loop compensation and magnetics part

selection process.

1

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Complete Integrated Power Solution Allows

Small Footprint, Low-Profile Design

Efficiencies Up To 96%

Wide-Output Voltage Adjust

0.6 V to 5.5 V, with 1% Reference Accuracy

Supports Parallel Operation for Higher Current

Optional Split Power Rail allows

input voltage down to 1.6 V

Adjustable Switching Frequency

(250 kHz to 780 kHz)

Synchronizes to an External Clock

Adjustable Slow Start

Output Voltage Sequencing and Tracking

Power Good Output

Programmable Undervoltage Lockout (UVLO)

Output Overcurrent Protection (Hiccup Mode)

Overtemperature Protection

Prebias Output Start-up

Operating Temperature Range: –40°C to +85°C

Enhanced Thermal Performance: 13°C/W

Meets EN55022 Class B Emissions

Design Help visit http://www.ti.com/TPS84621

2 APPLICATIONS

•

•

•

•

•

The 9×15×2.8 mm BQFN package is easy to solder

onto a printed circuit board and allows a compact

point-of-load design with greater than 90% efficiency

and excellent power dissipation with a thermal

impedance of 13°C/W junction to ambient. The

device delivers the full 6-A rated output current at

85°C ambient temperature without airflow.

The TPS84621 offers the flexibility and the featureset of a discrete point-of-load design and is ideal for

powering performance DSPs and FPGAs. Advanced

packaging technology afford a robust and reliable

power solution compatible with standard QFN

mounting and testing techniques.

SIMPLIFIED APPLICATION

VIN

VIN

ISHARE

PVIN

PWRGD

TPS84621

CIN

Broadband and Communications Infrastructure

Automated Test and Medical Equipment

Compact PCI, PCI Express and PXI Express

DSP and FPGA Point of Load Applications

High Density Distributed Power Systems

100

RT/CLK

SENSE+

INH/UVLO

SS/TR

COUT

VADJ

RSET

STSEL

95

AGND

90

Efficiency (%)

VOUT

VOUT

PGND

85

80

75

VOUT = 3.3 V

fSW = 630 kHz

70

65

60

PVIN = VIN = 5 V

PVIN = VIN = 12 V

55

50

0

1

2

3

4

Output Current (A)

5

6

G000

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

Table 1. ORDERING INFORMATION

For the most current package and ordering information, see

the Package Option Addendum at the end of this datasheet,

or see the TI website at www.ti.com.

4 Specifications

4.1

ABSOLUTE MAXIMUM RATINGS (1)

over operating temperature range (unless otherwise noted)

Input Voltage

Output Voltage

MAX

VIN, PVIN, INH/UVLO

–0.3

16

V

PWRGD, RT/CLK

–0.3

6

V

VADJ, SS/TR, STSEL, ISHARE

–0.3

3

V

PH

–1

20

V

PH 10-ns Transient

–3

20

V

–0.2

0.2

V

RT/CLK

Sink Current

UNIT

MIN

VDIFF (GND to exposed

thermal pad)

Source Current

VALUE

100

µA

PH

–100

Current Limit

A

PH

Current Limit

A

PVIN

Current Limit

PWRGD

A

–0.1

5

mA

Operating Junction Temperature

–40

125 (2)

°C

Storage Temperature

–65

150

°C

245

°C

Peak Reflow Case Temperature (3) (4)

Maximum Number of Reflows Allowed (3) (4)

3

Mechanical Shock

Mil-STD-883D, Method 2002.3, 1 msec, 1/2 sine, mounted

Mechanical Vibration

Mil-STD-883D, Method 2007.2, 20-2000Hz

(1)

(2)

(3)

(4)

2

1500

G

20

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

See the temperature derating curves in the Typical Characteristics section for thermal information.

For soldering specifications, refer to the Soldering Requirements for BQFN Packages application note.

Devices with a date code prior to week 14 2018 (1814) have a peak reflow case temperature of 240°C with a maximum of one reflow.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

4.2 THERMAL INFORMATION

TPS84621

THERMAL METRIC (1)

RUQ47

UNIT

47 PINS

Junction-to-ambient thermal resistance (2)

θJA

13

(3)

θJCtop

Junction-to-case (top) thermal resistance

θJCbot

Junction-to-case (bottom) thermal resistance

θJB

Junction-to-board thermal resistance

ψJT

Junction-to-top characterization parameter (6)

ψJB

Junction-to-board characterization parameter (7)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

9

(4)

(5)

3.8

°C/W

6

2.5

5

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

The junction-to-ambient thermal resistance, θJA, applies to devices soldered directly to a 100 mm x 100 mm double-sided PCB with 1 oz.

copper and natural convection cooling. Additional airflow reduces θJA.

The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard

test exists, but a close description can be found in the ANSI SEMI standard G30-88.

The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

The junction-to-top characterization parameter, ψJT, estimates the junction temperature, TJ, of a device in a real system, using a

procedure described in JESD51-2A (sections 6 and 7). TJ = ψJT * Pdis + TT; where Pdis is the power dissipated in the device and TT is

the temperature of the top of the device.

The junction-to-board characterization parameter, ψJB, estimates the junction temperature, TJ, of a device in a real system, using a

procedure described in JESD51-2A (sections 6 and 7). TJ = ψJB * Pdis + TB; where Pdis is the power dissipated in the device and TB is

the temperature of the board 1mm from the device.

4.3 PACKAGE SPECIFICATIONS

TPS84621

Weight

Flammability

MTBF Calculated reliability

UNIT

1.26 grams

Meets UL 94 V-O

Per Bellcore TR-332, 50% stress, TA = 40°C, ground benign

33.9 MHrs

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

3

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

4.4

www.ti.com

ELECTRICAL CHARACTERISTICS

Over –40°C to 85°C free-air temperature, PVIN = VIN = 12 V, VOUT = 1.8 V, IOUT = 6 A,

CIN1 = 2 x 22 µF ceramic, CIN2 = 68 µF poly-tantalum, COUT1 = 4 x 47 µF ceramic (unless otherwise noted)

PARAMETER

TEST CONDITIONS

IOUT

Output current

TA = 85°C, natural convection

VIN

Input bias voltage range

PVIN

Input switching voltage range

MIN

TYP

A

Over IOUT range

4.5

14.5

V

Over IOUT range

1.6 (1)

14.5 (2)

V

VIN = increasing

4.0

VIN Undervoltage lockout

VOUT(adj)

Output voltage adjust range

Over IOUT range

Set-point voltage tolerance

TA = 25°C, IOUT = 0A

Temperature variation

-40°C ≤ TA ≤ +85°C, IOUT = 0A

±0.3%

Line regulation

Over PVIN range, TA = 25°C, IOUT = 0A

±0.1%

Load regulation

Over IOUT range, TA = 25°C

±0.1%

Total output voltage variation

Includes set-point, line, load, and temperature variation

VIN = decreasing

3.5

Efficiency

Output voltage ripple

ILIM

PVIN = VIN = 5 V

IO = 2 A

92 %

VOUT = 3.3 V, fSW = 630 kHz

91 %

VOUT = 2.5 V, fSW = 530 kHz

89 %

VOUT = 1.8 V, fSW = 480 kHz

88 %

VOUT = 1.2 V, fSW = 480 kHz

85 %

VOUT = 0.8 V, fSW = 480 kHz

80 %

VOUT = 3.3V, fSW = 630 kHz

95 %

VOUT = 2.5V, fSW = 530 kHz

93 %

VOUT = 1.8V, fSW = 480 kHz

91 %

VOUT = 1.2V, fSW = 480 kHz

89 %

VOUT = 0.8V, fSW = 480 kHz

85 %

VOUT = 0.6V, fSW = 250 kHz

83 %

Transient response

VINH-H

VINH-L

II(stby)

Inhibit Control

1.0 A/µs load step

from 50 to 100% IOUT(max)

Recovery time

VOUT over/undershoot

1.30

Inhibit Low Voltage

–0.3

Input standby current

INH pin to AGND

2

Switching frequency

Over VIN and IOUT ranges, RT/CLK pin OPEN

fCLK

Synchronization frequency

VCLK-H

CLK High-Level

VCLK-L

CLK Low-Level

DCLK

CLK Duty cycle

CLK Control

Good

94%

Fault

109%

Fault

91%

Good

106%

Thermal shutdown hysteresis

V

μA

μA

4

µA

0.3

V

300

kHz

250

780

kHz

2.0

5.5

V

0.8

V

200

250

20%

Thermal shutdown

(4)

1.05

-3.4

VOUT falling

mV

Open

-1.15

fSW

4

A

INH > 1.26 V

PWRGD Thresholds

mVPP

µs

INH < 1.1 V

I(PWRGD) = 2 mA

(4)

(3)

80

INH Hysteresis current

PWRGD Low Voltage

(1)

(2)

(3)

±1.5%

V

11

INH Input current

Thermal Shutdown

(3)

60

Inhibit High Voltage

VOUT rising

Power

Good

±1.0%

30

Overcurrent threshold

V

5.5

VOUT = 5 V, fSW = 780 kHz

20 MHz bandwith

4.5

3.85

0.6 (2)

PVIN = VIN = 12 V

IO = 2 A

η

UNIT

6

UVLO

VOUT

MAX

0

160

80%

175

°C

10

°C

The minimum PVIN voltage is 1.6V or (VOUT+ 0.9V), whichever is greater. VIN must be greater than 4.5V.

The maximum PVIN voltage is 14.5V or (15 x VOUT), whichever is less.

The stated limit of the set-point voltage tolerance includes the tolerance of both the internal voltage reference and the internal

adjustment resistor. The overall output voltage tolerance will be affected by the tolerance of the external RSET resistor.

This control pin has an internal pullup. If this pin is left open circuit, the device operates when input power is applied. A small lowleakage MOSFET is recommended for control. See the application section for further guidance.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

ELECTRICAL CHARACTERISTICS (continued)

Over –40°C to 85°C free-air temperature, PVIN = VIN = 12 V, VOUT = 1.8 V, IOUT = 6 A,

CIN1 = 2 x 22 µF ceramic, CIN2 = 68 µF poly-tantalum, COUT1 = 4 x 47 µF ceramic (unless otherwise noted)

PARAMETER

CIN

TEST CONDITIONS

External input capacitance

Non-ceramic

Ceramic

COUT

External output capacitance

(6)

44

Non-ceramic

TYP

MAX

UNIT

(5)

µF

68 (5)

47

Equivalent series resistance (ESR)

(5)

MIN

Ceramic

(6)

200

1500

220 (6)

5000

35

µF

mΩ

A minimum of 100µF of polymer tantalum and/or ceramic external capacitance is required across the input (VIN and PVIN connected)

for proper operation. Locate the capacitor close to the device. See Table 5 for more details. When operating with split VIN and PVIN

rails, place 4.7µF of ceramic capacitance directly at the VIN pin.

The amount of required output capacitance varies depending on the output voltage (see Table 4 ). The amount of required capacitance

must include at least 1x 47µF ceramic capacitor. Locate the capacitance close to the device. Adding additional capacitance close to the

load improves the response of the regulator to load transients. See Table 4 and Table 5 more details.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

5

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

5 DEVICE INFORMATION

FUNCTIONAL BLOCK DIAGRAM

Thermal Shutdown

PWRGD

INH/UVLO

PWRGD

Logic

VSENSE+

Shutdown

Logic

OCP

VIN

VIN

UVLO

PVIN

VADJ

+

+

SS/TR

VREF

PH

Comp

STSEL

Current

Share

ISHARE

RT/CLK

Power

Stage

and

Control

Logic

VOUT

OSC

w/PLL

PGND

AGND

TPS84621

6

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

PIN DESCRIPTIONS

TERMINAL

NAME

DESCRIPTION

NO.

1

AGND

2

34

Zero VDC reference for the analog control circuitry. Connect AGND to PGND at a single point. Connect near

the output capacitors. See Figure 43 for a recommended layout.

45

8

INH/UVLO

ISHARE

9

5

Inhibit and UVLO adjust pin. Use an open drain or open collector output logic to control the INH function. A

resistor divider between this pin, AGND and VIN adjusts the UVLO voltage. Tie both pins together when

using this control.

Current share pin. Connect this pin to other TPS84621 device's ISHARE pin when paralleling multple

TPS84621 devices. When unused, treat this pin as a Do Not Connect (DNC) and leave it isolated from all

other signals or ground.

3

4

15

16

18

DNC

19

20

Do Not Connect. Do not connect these pins to AGND, to another DNC pin, or to any other voltage. These

pins are connected to internal circuitry. Each pin must be soldered to an isolated pad.

22

23

30

31

32

36

PGND

37

Common ground connection for the PVIN, VIN, and VOUT power connections. See Figure 43 for a

recommended layout.

38

10

11

12

PH

13

Phase switch node. These pins should be connected to a small copper island under the device for thermal

relief. Do not connect any external component to this pin or tie it to a pin of another function.

14

17

46

PWRGD

33

Power good fault pin. Asserts low if the output voltage is out of range. A pull-up resistor is required.

39

PVIN

40

Input switching voltage. This pin supplies voltage to the power switches of the converter. See Figure 43 for a

recommended layout.

41

RT/CLK

35

This pin automatically selects between RT mode and CLK mode. A timing resistor adjusts the switching

frequency of the device. In CLK mode, the device synchronizes to an external clock.

SENSE+

44

Remote sense connection. Connect this pin to VOUT at the load for improved regulation. This pin must be

connected to VOUT at the load, or at the module pins.

SS/TR

6

Slow-start and tracking pin. Connecting an external capacitor to this pin adjusts the output voltage rise time.

A voltage applied to this pin allows for tracking and sequencing control.

STSEL

7

Slow-start or track feature select. Connect this pin to AGND to enable the internal SS capacitor with a SS

interval of approximately 1.1 ms. Leave this pin open to enable the TR feature.

VADJ

43

Connecting a resistor between this pin and AGND sets the output voltage.

VIN

42

Input bias voltage pin. Supplies the control circuitry of the power converter. See Figure 43 for a

recommended layout.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

7

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

PIN DESCRIPTIONS (continued)

TERMINAL

NAME

DESCRIPTION

NO.

21

24

25

VOUT

26

27

Output voltage. Connect output capacitors between these pins and PGND.

28

29

47

38 PGND

39 PVIN

40 PVIN

41 PVIN

42 VIN

43 VADJ

44 SENSE+

RUQ PACKAGE

47 PIN

TOP VIEW

AGND 1

37

PGND

AGND 2

36

PGND

DNC 3

35

RT/CLK

34

AGND

ISHARE 5

33

PWRGD

SS/TR 6

32

DNC

STSEL 7

31

DNC

INH/UVLO 8

30

DNC

INH/UVLO 9

29

VO

28

VO

27

VO

26

VO

PH 13

25

VO

PH 14

24

VO

DNC 15

23

DNC

DNC 4

45

AGND

PH 10

PH 11

8

DNC 22

VO 21

DNC 20

DNC 19

DNC 18

47

VO

PH 17

DNC 16

PH 12

46

PH

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

100

95

90

85

80

75

70

65

60

55

50

45

40

(1) (2)

90

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

80

Output Voltage Ripple (mV)

Efficiency (%)

6 TYPICAL CHARACTERISTICS (PVIN = VIN = 12 V)

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2V, fSW = 480 kHz

VOUT = 0.8V, fSW = 330 kHz

0

1

2

3

4

Output Current (A)

5

70

60

50

40

30

20

10

6

0

0

1

Figure 1. Efficiency vs. Output Current

3

4

Output Current (A)

5

6

G000

Figure 2. Voltage Ripple vs. Output Current

90

3

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

2

80

Ambient Temperature (°C)

2.5

Power Dissipation (W)

2

G000

1.5

70

60

50

40

30

1

All Output Voltages

20

0

1

2

0.5

Natural Convection

3

4

Output Current (A)

5

6

G000

Figure 4. Safe Operating Area

0

0

1

2

3

4

Output Current (A)

5

6

G000

40

120

30

90

20

60

10

30

0

0

−30

−10

−60

−20

−30

−40

1000

Phase (°)

Gain (dB)

Figure 3. Power Dissipation vs. Output Current

Gain

Phase

−90

10000

Frequency (Hz)

100000

−120

400000

G000

Figure 5. VOUT= 1.8 V, IOUT= 6 A, COUT1= 200 µF ceramic, fSW= 480 kHz

(1)

(2)

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the

converter. Applies to Figure 1, Figure 2, and Figure 3.

The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum

operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper.

Applies to Figure 4.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

9

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

100

95

90

85

80

75

70

65

60

55

50

45

40

(1) (2)

60

Output Voltage Ripple (mV)

Efficiency (%)

7 TYPICAL CHARACTERISTICS (PVIN = VIN = 5 V)

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

VOUT = 0.6V, fSW = 250 kHz

0

1

2

3

4

Output Current (A)

5

50

40

30

20

10

0

6

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

VOUT = 0.6 V, fSW = 250 kHz

0

Figure 6. Efficiency vs. Output Current

2

3

4

Output Current (A)

6

G000

90

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

VOUT = 0.6 V, fSW = 250 kHz

1.5

80

Ambient Temperature (°C)

2

1

0.5

70

60

50

40

30

All Output Voltages

20

0

1

2

3

4

Output Current (A)

5

6

0

2

120

30

90

20

60

10

30

0

0

−30

−10

6

G000

−60

−20

−40

1000

5

Figure 9. Safe Operating Area

40

−30

Natural Convection

3

4

Output Current (A)

G000

Figure 8. Power Dissipation vs. Output Current

Gain (dB)

1

Phase (°)

0

5

Figure 7. Voltage Ripple vs. Output Current

2.5

Power Dissipation (W)

1

G000

Gain

Phase

−90

10000

Frequency (Hz)

100000

−120

400000

G000

Figure 10. VOUT= 1.8 V, IOUT= 6 A, COUT1= 200 µF ceramic, fSW=480 kHz

(1)

(2)

10

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the

converter. Applies to Figure 6, Figure 7, and Figure 8.

The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum

operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper.

Applies to Figure 9.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

100

95

90

85

80

75

70

65

60

55

50

45

40

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

80

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2V, fSW = 480 kHz

VOUT = 0.8V, fSW = 330 kHz

0

1

2

3

4

Output Current (A)

5

70

60

50

40

30

20

10

0

6

0

1

G000

Figure 11. Efficiency vs. Output Current

2

3

4

Output Current (A)

1.5

1

70

60

50

40

0.5

30

0

20

0

1

2

3

4

Output Current (A)

5

6

0

1

Natural Convection

2

3

4

Output Current (A)

5

6

G000

G000

Figure 14. Safe Operating Area

90

40

120

80

30

90

20

60

10

30

0

0

Gain (dB)

70

60

50

40

−60

−20

30

0

1

−30

100 LFM

Natural Convection

VOUT = 5.0 V

20

−30

−10

2

3

4

Output Current (A)

5

6

G000

Figure 15. Safe Operating Area

−40

1000

Phase (°)

2

Ambient Temperature (°C)

2.5

Figure 13. Power Dissipation vs. Output Current

Ambient Temperature (°C)

G000

80

VOUT< 5.0 V

(2)

6

90

VOUT = 5.0 V, fSW = 780 kHz

VOUT = 3.3 V, fSW = 630 kHz

VOUT = 2.5 V, fSW = 480 kHz

VOUT = 1.8 V, fSW = 480 kHz

VOUT = 1.2 V, fSW = 480 kHz

VOUT = 0.8 V, fSW = 480 kHz

3

(1)

5

Figure 12. Voltage Ripple vs. Output Current

3.5

Power Dissipation (W)

(1) (2)

90

Output Voltage Ripple (mV)

Efficiency (%)

8 TYPICAL CHARACTERISTICS (PVIN = 12 V, VIN = 5 V)

Gain

Phase

−90

10000

Frequency (Hz)

100000

−120

400000

G000

Figure 16. VOUT= 2.5 V, IOUT= 6 A, COUT1= 200 µF ceramic,

fSW= 480 kHz

The electrical characteristic data has been developed from actual products tested at 25°C. This data is considered typical for the

converter. Applies to Figure 11, Figure 12, and Figure 13.

The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum

operating temperatures. Derating limits apply to devices soldered directly to a 100 mm × 100 mm double-sided PCB with 1 oz. copper.

Applies to Figure 14 and Figure 15.

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

11

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9 APPLICATION INFORMATION

9.1 ADJUSTING THE OUTPUT VOLTAGE

The VADJ control sets the output voltage of the TPS84621. The output voltage adjustment range is from 0.6V to

5.5V. The adjustment method requires the addition of RSET, which sets the output voltage, the connection of

SENSE+ to VOUT, and in some cases RRT which sets the switching frequency. The RSET resistor must be

connected directly between the VADJ (pin 43) and AGND (pin 45). The SENSE+ pin (pin 44) must be connected

to VOUT either at the load for improved regulation or at VOUT of the device. The RRT resistor must be connected

directly between the RT/CLK (pin 35) and AGND (pin 34). Table 2 gives the standard external RSET resistor for a

number of common bus voltages, along with the required RRT resistor for that output voltage.

Table 2. Standard RSET Resistor Values for Common Output Voltages

RESISTORS

OUTPUT VOLTAGE VOUT (V)

0.9

1.0

1.2

1.8

2.5

3.3

5.0

RSET (kΩ)

2.87

2.15

1.43

0.715

0.453

0.316

0.196

RRT (kΩ)

261

261

200

200

165

121

86.6

For other output voltages, the value of the required resistor can either be calculated using the following formula,

or simply selected from the range of values given in Table 3.

1.43

RSET =

(kW )

æ æ VOUT ö ö

çç

÷ - 1÷

è è 0.6 ø ø

(1)

Table 3. Standard RSET Resistor Values

12

VOUT (V)

RSET (kΩ)

RRT(kΩ)

fSW(kHz)

VOUT (V)

RSET (kΩ)

RRT(kΩ)

fSW(kHz)

0.6

open

open

250

3.1

0.348

140

580

0.7

8.66

590

330

3.2

0.332

140

580

0.8

4.32

590

330

3.3

0.316

121

630

0.9

2.87

261

430

3.4

0.309

121

630

1.0

2.15

261

430

3.5

0.294

121

630

1.1

1.74

261

430

3.6

0.287

121

630

1.2

1.43

200

480

3.7

0.280

121

630

1.3

1.24

200

480

3.8

0.267

107

680

1.4

1.07

200

480

3.9

0.261

107

680

1.5

0.953

200

480

4.0

0.255

107

680

1.6

0.866

200

480

4.1

0.243

107

680

1.7

0.787

200

480

4.2

0.237

95.3

730

1.8

0.715

200

480

4.3

0.232

95.3

730

1.9

0.665

200

480

4.4

0.226

95.3

730

2.0

0.619

200

480

4.5

0.221

95.3

730

2.1

0.576

200

480

4.6

0.215

95.3

730

2.2

0.536

200

480

4.7

0.210

95.3

730

2.3

0.511

200

480

4.8

0.205

86.6

780

2.4

0.475

200

480

4.9

0.200

86.6

780

2.5

0.453

200

480

5.0

0.196

86.6

780

2.6

0.432

165

530

5.1

0.191

86.6

780

2.7

0.412

165

530

5.2

0.187

86.6

780

2.8

0.392

165

530

5.3

0.182

86.6

780

2.9

0.374

165

530

5.4

0.178

86.6

780

3.0

0.357

140

580

5.5

0.174

86.6

780

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.2 CAPACITOR RECOMMENDATIONS FOR THE TPS84621 POWER SUPPLY

9.2.1 Capacitor Technologies

9.2.1.1 Electrolytic, Polymer-Electrolytic Capacitors

When using electrolytic capacitors, high-quality, computer-grade electrolytic capacitors are recommended.

Polymer-electrolytic type capacitors are recommended for applications where the ambient operating temperature

is less than 0°C. The Sanyo OS-CON capacitor series is suggested due to the lower ESR, higher rated surge,

power dissipation, ripple current capability, and small package size. Aluminum electrolytic capacitors provide

adequate decoupling over the frequency range of 2 kHz to 150 kHz, and are suitable when ambient temperatures

are above 0°C.

9.2.1.2 Ceramic Capacitors

The performance of aluminum electrolytic capacitors is less effective than ceramic capacitors above 150 kHz.

Multilayer ceramic capacitors have a low ESR and a resonant frequency higher than the bandwidth of the

regulator. They can be used to reduce the reflected ripple current at the input as well as improve the transient

response of the output.

9.2.1.3 Tantalum, Polymer-Tantalum Capacitors

Polymer-tantalum type capacitors are recommended for applications where the ambient operating temperature is

less than 0°C. The Sanyo POSCAP series and Kemet T530 capacitor series are recommended rather than many

other tantalum types due to their lower ESR, higher rated surge, power dissipation, ripple current capability, and

small package size. Tantalum capacitors that have no stated ESR or surge current rating are not recommended

for power applications.

9.2.2 Input Capacitor

The TPS84621 requires a minimum input capacitance of 100 μF of ceramic and/or polymer-tantalum capacitors.

The ripple current rating of the capacitor must be at least 450 mArms. Table 5 includes a preferred list of

capacitors by vendor.

9.2.3 Output Capacitor

The required output capacitance is determined by the output voltage of the TPS84621. See Table 4 for the

amount of required capacitance. The required output capacitance must be comprised of all ceramic capacitors.

When adding additional non-ceramic bulk capacitors, low-ESR devices like the ones recommended in Table 5

are required. The required capacitance above the minimum is determined by actual transient deviation

requirements. See Table 6 for typical transient response values for several output voltage, input voltage and

capacitance combinations. Table 5 includes a preferred list of capacitors by vendor.

Table 4. Required Output Capacitance

VOUT RANGE (V)

MINIMUM REQUIRED COUT (µF)

MIN

MAX

0.6

< 0.8

400 µF ceramic

0.8

< 1.2

300 µF ceramic

1.2

< 3.0

200 µF ceramic

3.0

< 4.0

100 µF ceramic

4.0

5.5

47 µF ceramic

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

13

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

Table 5. Recommended Input/Output Capacitors (1)

CAPACITOR CHARACTERISTICS

VENDOR

SERIES

PART NUMBER

WORKING

VOLTAGE

(V)

CAPACITANCE

(µF)

ESR (2)

(mΩ)

Murata

X5R

GRM32ER61E226K

16

22

2

TDK

X5R

C3225X5R0J476K

6.3

47

2

Murata

X5R

GRM32ER60J476M

6.3

47

2

Sanyo

POSCAP

16TQC68M

16

68

50

Kemet

T520

T520V107M010ASE025

10

100

25

Sanyo

POSCAP

6TPE100MI

6.3

100

25

Sanyo

POSCAP

2R5TPE220M7

2.5

220

7

Kemet

T530

T530D227M006ATE006

6.3

220

6

Kemet

T530

T530D337M006ATE010

6.3

330

10

Sanyo

POSCAP

2TPF330M6

2.0

330

6

Sanyo

POSCAP

6TPE330MFL

6.3

330

15

(1)

(2)

Capacitor Supplier Verification

Please verify availability of capacitors identified in this table.

RoHS, Lead-free and Material Details

Please consult capacitor suppliers regarding material composition, RoHS status, lead-free status, and manufacturing process

requirements.

Maximum ESR @ 100kHz, 25°C.

9.3 Transient Response

Table 6. Output Voltage Transient Response

CIN1 = 47 µF CERAMIC, CIN2 = 220 µF POLYMER-TANTALUM

VOLTAGE DEVIATION (mV)

VIN (V)

COUT1 Ceramic

COUT2 BULK

2 A LOAD STEP,

(1 A/µs)

3 A LOAD STEP,

(1 A/µs)

0.6

5

400 µF

330 µF

20

30

120

300 µF

220 µF

25

35

140

300 µF

330 µF

20

30

140

300 µF

220 µF

30

35

140

300 µF

330 µF

25

30

140

200 µF

100 µF

40

50

150

200 µF

220 µF

35

45

150

200 µF

100 µF

35

45

150

200 µF

220 µF

30

40

150

200 µF

-

65

85

160

200 µF

100 µF

55

96

160

200 µF

-

55

80

160

200 µF

100 µF

50

75

160

5

100 µF

100 µF

90

140

180

12

100 µF

100 µF

85

125

180

5

0.8

12

5

1.2

12

5

1.8

12

3.3

14

RECOVERY TIME

(µs)

VOUT (V)

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.4 Transient Waveforms

Figure 17. PVIN = 5V, VOUT = 0.6V, 2A Load Step

Figure 18. PVIN = 5V, VOUT = 0.8V, 2A Load Step

Figure 19. PVIN = 12V, VOUT = 1.2V, 2A Load Step

Figure 20. PVIN = 5V, VOUT = 1.2V, 2A Load Step

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

15

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

Transient Waveforms (continued)

Figure 21. PVIN = 12V, VOUT = 1.8V, 2A Load Step

Figure 22. PVIN = 5V, VOUT = 1.8V, 2A Load Step

9.5 Application Schematics

TPS84621

VIN

VIN / PVIN

4.5 V to 14.5 V

PWRGD

PVIN

+

CIN2

68 F

CIN1

47 F

VOUT

1.8 V

SENSE+

INH/UVLO

VOUT

SS/TR

+

COUT1

4x 47 F

COUT2

220 F

RT/CLK

RRT

200 k

VADJ

RSET

715

STSEL AGND PGND

Figure 23. Typical Schematic

PVIN = VIN = 4.5 V to 14.5 V, VOUT = 1.8 V

16

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

Application Schematics (continued)

TPS84621

VIN

VIN / PVIN

4.5 V to 14.5 V

PWRGD

PVIN

+

CIN2

68 F

CIN1

47 F

VOUT

3.3 V

SENSE+

INH/UVLO

VOUT

COUT1 +

2x 47 F

SS/TR

COUT2

100 F

RT/CLK

VADJ

RRT

121 k

RSET

316

STSEL AGND PGND

Figure 24. Typical Schematic

PVIN = VIN = 4.5 V to 14.5 V, VOUT = 3.3 V

VIN

4.5 V to 14.5 V

CIN3

4.7 F

VIN

TPS84621

PVIN

3.3 V

+

PWRGD

PVIN

CIN2

68 F

CIN1

47 F

VOUT

1.2 V

SENSE+

INH/UVLO

VOUT

SS/TR

COUT1 +

4x 47 F

COUT2

330 F

RT/CLK

RRT

200 k

VADJ

RSET

1.43 k

STSEL AGND PGND

Figure 25. Typical Schematic

PVIN = 3.3 V, VIN = 4.5 V to 14.5 V, VOUT = 1.2 V

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

17

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.6 VIN and PVIN Input Voltage

The TPS84621 allows for a variety of applications by using the VIN and PVIN pins together or separately. The

VIN voltage supplies the internal control circuits of the device. The PVIN voltage provides the input voltage to the

power converter system.

If tied together, the input voltage for the VIN pin and the PVIN pin can range from 4.5 V to 14.5 V. If using the

VIN pin separately from the PVIN pin, the VIN pin must be between 4.5 V and 14.5 V, and the PVIN pin can

range from as low as 1.6 V to 14.5 V. A voltage divider connected to the INH/UVLO pin can adjust the either

input voltage UVLO appropriately. See the Programmable Undervoltage Lockout (UVLO) section of this

datasheet for more information.

9.7 3.3-V Input Operation

Applications operating from 3.3 V must provide at least 4.5 V for VIN. See application note, SLVA561 for help

creating 5 V from 3.3 V using a small, simple charge pump device.

9.8 Power Good (PWRGD)

The PWRGD pin is an open drain output. Once the voltage on the SENSE+ pin is between 94% and 106% of the

set voltage, the PWRGD pin pull-down is released and the pin floats. The recommended pull-up resistor value is

between 10 kΩ and 100 kΩ to a voltage source that is 5.5 V or less. The PWRGD pin is in a defined state once

VIN is greater than 1.0 V, but with reduced current sinking capability. The PWRGD pin achieves full current

sinking capability once the VIN pin is above 4.5V. The PWRGD pin is pulled low when the voltage on SENSE+ is

lower than 91% or greater than 109% of the nominal set voltage. Also, the PWRGD pin is pulled low if the input

UVLO or thermal shutdown is asserted, the INH pin is pulled low, or the SS/TR pin is below 1.4 V.

18

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.9 Parallel Operation

Up to six TPS84621 devices can be paralleled for increased output current. Multiple connections must be made

between the paralleled devices and the component selection is slightly different than for a stand-alone TPS84621

device. A typical TPS84621 parallel schematic is shown in Figure 26. Refer to application note, SLVA574 for

information and design help when paralleling multiple TPS84621 devices.

47 µF

100 µF

100 µF

100 µF

330 µF

PGND

AGND

STSEL

VADJ

SS/TR

100 µF

RSET

715

PWRGD

SENSE+

VOUT

TPS84621

STSEL

RT/CLK

RRT

200 k

PGND

VIN

PVIN

CSS

VADJ

Voltage

Supervisor

CSH

INH

Control

SS/TR

5V

INH/UVLO

ISHARE

RRT

200 k

VO = 1.8V

VOUT

TPS84621

RT/CLK

Sync Freq

480 kHz

SENSE+

47 µF

INH/UVLO

ISHARE

220 µF

PWRGD

VIN

PVIN

AGND

VIN = 12 V

Figure 26. Typical TPS84621 Parallel Schematic

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

19

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.10 Power-Up Characteristics

When configured as shown in the front page schematic, the TPS84621 produces a regulated output voltage

following the application of a valid input voltage. During the power-up, internal soft-start circuitry slows the rate

that the output voltage rises, thereby limiting the amount of in-rush current that can be drawn from the input

source. The soft-start circuitry introduces a short time delay from the point that a valid input voltage is

recognized. Figure 27 shows the start-up waveforms for a TPS84621, operating from a 5-V input (PVIN=VIN)

and with the output voltage adjusted to 1.8 V. Figure 28 shows the start-up waveforms for a TPS84621 starting

up into a pre-biased output voltage. The waveforms were measured with a 3-A constant current load.

Figure 27. Start-Up Waveforms

Figure 28. Start-up into Pre-bias

9.11 Pre-Biased Start-Up

The TPS84621 has been designed to prevent discharging a pre-biased output. During monotonic pre-biased

startup, the TPS84621 does not allow current to sink until the SS/TR pin voltage is higher than 1.4 V.

9.12 Remote Sense

The SENSE+ pin must be connected to VOUT at the load, or at the device pins.

Connecting the SENSE+ pin to VOUT at the load improves the load regulation performance of the device by

allowing it to compensate for any I-R voltage drop between its output pins and the load. An I-R drop is caused by

the high output current flowing through the small amount of pin and trace resistance. This should be limited to a

maximum of 300 mV.

NOTE

The remote sense feature is not designed to compensate for the forward drop of nonlinear

or frequency dependent components that may be placed in series with the converter

output. Examples include OR-ing diodes, filter inductors, ferrite beads, and fuses. When

these components are enclosed by the SENSE+ connection, they are effectively placed

inside the regulation control loop, which can adversely affect the stability of the regulator.

9.13 Thermal Shutdown

The internal thermal shutdown circuitry forces the device to stop switching if the junction temperature exceeds

175°C typically. The device reinitiates the power up sequence when the junction temperature drops below 165°C

typically.

20

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.14 Output On/Off Inhibit (INH)

The INH pin provides electrical on/off control of the device. Once the INH pin voltage exceeds the threshold

voltage, the device starts operation. If the INH pin voltage is pulled below the threshold voltage, the regulator

stops switching and enters low quiescent current state.

The INH pin has an internal pull-up current source, allowing the user to float the INH pin for enabling the device.

If an application requires controlling the INH pin, use an open drain/collector device, or a suitable logic gate to

interface with the pin.

Figure 29 shows the typical application of the inhibit function. The Inhibit control has its own internal pull-up to

VIN potential. An open-collector or open-drain device is recommended to control this input.

Turning Q1 on applies a low voltage to the inhibit control (INH) pin and disables the output of the supply, shown

in Figure 30. If Q1 is turned off, the supply executes a soft-start power-up sequence, as shown in Figure 31. A

regulated output voltage is produced within 3 ms. The waveforms were measured with a 3-A constant current

load.

INH/UVLO

Q1

INH

Control

AGND

STSEL

Figure 29. Typical Inhibit Control

Figure 31. Inhibit Turn-On

Figure 30. Inhibit Turn-Off

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

21

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.15 Slow Start (SS/TR)

Connecting the STSEL pin to AGND and leaving SS/TR pin open enables the internal SS capacitor with a slow

start interval of approximately 1.1 ms. Adding additional capacitance between the SS pin and AGND increases

the slow start time. Table 7 shows an additional SS capacitor connected to the SS/TR pin and the STSEL pin

connected to AGND. See Table 7 below for SS capacitor values and timing interval.

SS/TR

CSS

(Optional)

AGND

STSEL

Figure 32. Slow-Start Capacitor (CSS) and STSEL Connection

Table 7. Slow-Start Capacitor Values and Slow-Start Time

CSS (pF)

open

2200

4700

10000

15000

22000

25000

SS Time (msec)

1.1

1.9

2.8

4.6

6.4

8.8

9.8

9.16 Overcurrent Protection

For protection against load faults, the TPS84621 incorporates output overcurrent protection. Applying a load that

exceeds the regulator's overcurrent threshold causes the regulated output to shut down. Following shutdown, the

module periodically attempts to recover by initiating a soft-start power-up as shown in Figure 33. This is

described as a hiccup mode of operation, whereby the module continues in a cycle of successive shutdown and

power up until the load fault is removed. During this period, the average current flowing into the fault is

significantly reduced. Once the fault is removed, the module automatically recovers and returns to normal

operation as shown in Figure 34.

Figure 33. Overcurrent Limiting

22

Figure 34. Removal of Overcurrent Condition

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.17 Synchronization (CLK)

An internal phase locked loop (PLL) has been implemented to allow synchronization between 250 kHz and

780 kHz, and to easily switch from RT mode to CLK mode. To implement the synchronization feature, connect a

square wave clock signal to the RT/CLK pin with a duty cycle between 20% to 80%. The clock signal amplitude

must transition lower than 0.8 V and higher than 2.0 V. The start of the switching cycle is synchronized to the

falling edge of RT/CLK pin. In applications where both RT mode and CLK mode are needed, the device can be

configured as shown in .

Before the external clock is present, the device works in RT mode and the switching frequency is set by RT

resistor. When the external clock is present, the CLK mode overrides the RT mode. The first time the CLK pin is

pulled above the RT/CLK high threshold (2.0 V), the device switches from RT mode to th CLK mode and the

RT/CLK pin becomes high impedance as the PLL starts to lock onto the frequency of the external clock. It is not

recommended to switch from CLK mode back to RT mode because the internal switching frequency drops to

100 kHz first before returning to the switching frequency set by the RT resistor (RRT).

External Clock

250 kHz to 780 kHz

RT/CLK

RRT

AGND

Figure 35. CLK/RT Configuration

The synchronization frequency must be selected based on the output voltages of the devices being

synchronized. Table 8 shows the allowable frequencies for a given range of output voltages. For the most

efficient solution, always synchronize to the lowest allowable frequency. For example, an application requires

synchronizing three TPS84621 devices with output voltages of 1.2 V, 1.8 V and 3.3 V, all powered from

PVIN = 12 V. Table 8 shows that all three output voltages should be synchronized to 630 kHz.

Table 8. Synchronization Frequency vs Output Voltage

PVIN = 12 V

PVIN = 5 V

VOUT RANGE (V)

VOUT RANGE (V)

SYNCHRONIZATION

FREQUENCY (kHz)

RRT (kΩ)

MIN

MAX

MIN

MAX

250

open

0.6

1.0

0.6

1.3

280

1100

0.6

1.2

0.6

1.6

330

590

0.6

1.5

0.6

4.5

380

357

0.7

1.7

0.6

4.5

430

261

0.8

2.1

0.6

4.5

480

200

0.9

2.5

0.6

4.5

530

165

1.0

2.9

0.6

4.5

580

140

1.1

3.2

0.6

4.5

630

121

1.2

3.7

0.6

4.5

680

107

1.3

4.1

0.6

4.5

730

95.3

1.4

4.7

0.6

4.5

780

86.6

1.5

5.5

0.6

4.5

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

23

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.18 Sequencing (SS/TR)

Many of the common power supply sequencing methods can be implemented using the SS/TR, INH and

PWRGD pins. The sequential method is illustrated in Figure 36 using two TPS84621 devices. The PWRGD pin

of the first device is coupled to the INH pin of the second device which enables the second power supply once

the primary supply reaches regulation. Figure 37 shows sequential turn-on waveforms of two TPS84621 devices.

INH/UVLO

VOUT1

VOUT

STSEL

PWRGD

INH/UVLO

VOUT2

VOUT

STSEL

PWRGD

Figure 36. Sequencing Schematic

Figure 37. Sequencing Waveforms

Simultaneous power supply sequencing can be implemented by connecting the resistor network of R1 and R2

shown in Figure 38 to the output of the power supply that needs to be tracked or to another voltage reference

source. Figure 39 shows simultaneous turn-on waveforms of two TPS84621 devices. Use Equation 2 and

Equation 3 to calculate the values of R1 and R2.

R1 =

24

(VOUT2 ´ 12.6 )

0.6

(kW )

R2 =

(2)

0.6 ´ R1

(kW )

V

( OUT2 - 0.6 )

Submit Documentation Feedback

(3)

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

VOUT1

VOUT

INH/UVLO

STSEL

SS/TR

VOUT2

VOUT

INH/UVLO

R1

STSEL

SS/TR

R2

Figure 38. Simultaneous Tracking Schematic

Figure 39. Simultaneous Tracking Waveforms

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

25

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.19 Programmable Undervoltage Lockout (UVLO)

The TPS84621 implements internal UVLO circuitry on the VIN pin. The device is disabled when the VIN pin

voltage falls below the internal VIN UVLO threshold. The internal VIN UVLO rising threshold is 4.5 V(max) with a

typical hysteresis of 150 mV.

If an application requires either a higher UVLO threshold on the VIN pin or a higher UVLO threshold for a

combined VIN and PVIN, then the UVLO pin can be configured as shown in Figure 40 or Figure 41. Table 9 lists

standard values for RUVLO1 and RUVLO2 to adjust the VIN UVLO voltage up.

PVIN

PVIN

VIN

VIN

RUVLO1

RUVLO1

INH/UVLO

INH/UVLO

RUVLO2

RUVLO2

Figure 40. Adjustable VIN UVLO

Figure 41. Adjustable VIN and PVIN Undervoltage Lockout

Table 9. Standard Resistor values for Adjusting VIN UVLO

VIN UVLO (V)

5.0

5.5

6.0

6.5

7.0

7.5

8.0

8.5

9.0

9.5

10.0

RUVLO1 (kΩ)

68.1

68.1

68.1

68.1

68.1

68.1

68.1

68.1

68.1

68.1

68.1

RUVLO2 (kΩ)

21.5

18.7

16.9

15.4

14.0

13.0

12.1

11.3

10.5

9.76

9.31

Hysteresis (mV)

400

415

430

450

465

480

500

515

530

550

565

For a split rail application, if a secondary UVLO on PVIN is required, VIN must be ≥ 4.5V. Figure 42 shows the

PVIN UVLO configuration. Use Table 10 to select RUVLO1 and RUVLO2 for PVIN. If PVIN UVLO is set for less than

3.0 V, a 5.1-V zener diode should be added to clamp the voltage on the UVLO pin below 6 V.

> 4.5 V

VIN

PVIN

RUVLO1

INH/UVLO

RUVLO2

Figure 42. Adjustable PVIN Undervoltage Lockout, (VIN ≥4.5 V)

Table 10. Standard Resistor Values for Adjusting PVIN UVLO, (VIN ≥4.5 V)

PVIN UVLO (V)

26

2.0

2.5

3.0

3.5

4.0

4.5

RUVLO1 (kΩ)

68.1

68.1

68.1

68.1

68.1

68.1

RUVLO2 (kΩ)

95.3

60.4

44.2

34.8

28.7

24.3

Hysteresis (mV)

300

315

335

350

365

385

Submit Documentation Feedback

For higher PVIN UVLO voltages see

Table UV for resistor values

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

9.20 Layout Considerations

To achieve optimal electrical and thermal performance, an optimized PCB layout is required. Figure 43, shows a

typical PCB layout. Some considerations for an optimized layout are:

• Use large copper areas for power planes (PVIN, VOUT, and PGND) to minimize conduction loss and thermal

stress.

• Place ceramic input and output capacitors close to the device pins to minimize high frequency noise.

• Locate additional output capacitors between the ceramic capacitor and the load.

• Place a dedicated AGND copper area beneath the TPS84621.

• Isolate the PH copper area from the VOUT copper area using the AGND copper area.

• Connect the AGND and PGND copper area at one point; see AGND to PGND connection point in Figure 43.

• Place RSET, RRT, and CSS as close as possible to their respective pins.

• Use multiple vias to connect the power planes to internal layers.

SENSE+

Via

SENSE+

Via

VOUT

COUT3

PGND

Plane

COUT2

COUT1

Vias to

Topside

PGND

Copper

RRT

PGND

AGND to PGND

connection

CIN1

CIN2

Vias to

Topside

AGND

Copper

AGND

AGND

Plane

PH

SENSE+

Via

RSET

VIN/PVIN

SENSE+

Via

CSS

Figure 43. Typical Top-Layer Recommended Layout

Figure 44. Typical GND-Layer Recommended Layout

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

27

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

9.21 EMI

The TPS84621 is compliant with EN55022 Class B radiated emissions. Figure 46 and Figure 45 show typical

examples of radiated emissions plots for the TPS84621 operating from 5V and 12V respectively. Both graphs

include the plots of the antenna in the horizontal and vertical positions.

Figure 45. Radiated Emissions 5-V Input, 1.8-V Output, 6-A

Load (EN55022 Class B)

28

Figure 46. Radiated Emissions 12-V Input, 1.8-V Output, 6A Load (EN55022 Class B)

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

10 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision D (June 2017) to Revision E

•

Page

Increased the peak reflow temperature and maximum number of reflows to JEDEC specification for improved

manufacturability..................................................................................................................................................................... 2

Changes from Revision C (February 2013) to Revision D

•

Page

Added peak reflow and maximum number of reflows information ........................................................................................ 2

Changes from Revision B (OCTOBER 2012) to Revision C

Page

•

Changed the minimum input voltage to 2.95V from 4.5V....................................................................................................... 1

•

Added ISHARE parameter to Absolute Maximum Ratings table............................................................................................ 2

•

Added ISHARE to the Pin Description table........................................................................................................................... 7

•

Added Parallel Operation section. ........................................................................................................................................ 19

Changes from Revision A (MAY 2012) to Revision B

•

Page

Added Thermal Information table ........................................................................................................................................... 3

Changes from Original (DECEMBER 2011) to Revision A

•

Page

Changed – updated pin names in package drawing. ............................................................................................................ 8

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

29

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

11 Device and Documentation Support

11.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper

right corner, click on Alert me to register and receive a weekly digest of any product information that has

changed. For change details, review the revision history included in any revised document.

11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective

contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of

Use.

TI E2E™ Online Community TI's Engineer-to-Engineer (E2E) Community. Created to foster collaboration

among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help

solve problems with fellow engineers.

Design Support TI's Design Support Quickly find helpful E2E forums along with design support tools and

contact information for technical support.

11.3 Trademarks

E2E is a trademark of Texas Instruments.

11.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most

current data available for the designated devices. This data is subject to change without notice and revision of

this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

30

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�TPS84621

www.ti.com

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

12.1 Package Option Addendum

REEL DIMENSIONS

TAPE DIMENSIONS

K0

P1

B0 W

Reel

Diameter

Cavity

A0

B0

K0

W

P1

A0

Dimension designed to accommodate the component width

Dimension designed to accommodate the component length

Dimension designed to accommodate the component thickness

Overall width of the carrier tape

Pitch between successive cavity centers

Reel Width (W1)

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Sprocket Holes

Q1

Q2

Q1

Q2

Q3

Q4

Q3

Q4

User Direction of Feed

Pocket Quadrants

Device

Package

Type

Package

Drawing

Pins

SPQ

Reel

Diameter

(mm)

Reel

Width W1

(mm)

A0

(mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

(mm)

Pin1

Quadrant

TPS84621RUQR

B1QFN

RUQ

47

500

330.0

24.4

9.35

15.35

3.1

16.0

24.0

Q1

TPS84621RUQT

B1QFN

RUQ

47

250

330.0

24.4

9.35

15.35

3.1

16.0

24.0

Q1

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

31

�TPS84621

SLVSAW7E – DECEMBER 2011 – REVISED APRIL 2018

www.ti.com

TAPE AND REEL BOX DIMENSIONS

Width (mm)

L

W

32

H

Device

Package Type

Package Drawing

Pins

SPQ

Length (mm)

Width (mm)

Height (mm)

TPS84621RUQR

B1QFN

RUQ

47

500

383.0

353.0

58.0

TPS84621RUQT

B1QFN

RUQ

47

250

383.0

353.0

58.0

Submit Documentation Feedback

Copyright © 2011–2018, Texas Instruments Incorporated

Product Folder Links: TPS84621

�PACKAGE OPTION ADDENDUM

www.ti.com

4-Jun-2020

PACKAGING INFORMATION

Orderable Device

Status

(1)

Package Type Package Pins Package

Drawing

Qty

Eco Plan

Lead/Ball Finish

MSL Peak Temp

(2)

(6)

(3)

Op Temp (°C)

Device Marking

(4/5)

TPS84621RUQR

ACTIVE

B1QFN

RUQ

47

500

RoHS Exempt

& Green

NIPDAU

Level-3-245C-168 HR

-40 to 85

TPS84621

TPS84621RUQT

ACTIVE

B1QFN

RUQ

47

250

RoHS Exempt

& Green

NIPDAU

Level-3-245C-168 HR

-40 to 85

TPS84621

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance

do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may

reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of