TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

1.8V/3V SIM Card Power Supply With Level Translator

Check for Samples: TXS4555

FEATURES

1

•

3

NC

4

11

SIMCLK

10

GND

9

SIMRST

NC

I/O

RST

CLK

16

15

14

13

Note: The Exposed center thermal pad must be

connected to Ground

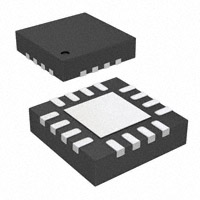

RUT Package

(Top View)

EN

I/O

RST

CLK

SIMCLK

10

9

8

7

2

3

4

5

VBATT

VSIM

SIMI/O

SIMRST

6

1

12

VCC

SEL

11

DESCRIPTION

The TXS4555 is a complete Smart Identity Module

(SIM) card solution for interfacing wireless baseband

processors with a SIM card to store I/O for mobile

handset applications. The device complies with

ISO/IEC Smart-Card Interface requirements as well

as GSM and 3G mobile standards. It includes a highspeed level translator capable of supporting Class-B

(2.95 V) and Class-C (1.8 V) interfaces, a lowdropout (LDO) voltage regulator that has output

voltages that are selectable between 2.95-V Class-B

and 1.8-V Class-C interfaces.

NC

8

VCC

Exposed

Thermal Pad

12

SIMI/O

2

7

SEL

VSIM

1

6

•

EN

NC

•

RGT Package

(Top View)

5

•

Level Translator

– VCC Range of 1.65 V to 3.3 V

– VBATT Range from 2.3 to 5.5V

Low-Dropout (LDO) Regulator

– 50-mA LDO Regulator With Enable

– 1.8-V or 2.95-V Selectable Output Voltage

– 2.3-V to 5.5-V Input Voltage Range

– Very Low Dropout: 100mV (Max) at 50mA

Incorporates Shutdown Feature for the SIM

Card Signals According to ISO-7816-3

ESD Protection Exceeds JESD 22

– 2000-V Human-Body Model (A114-B)

– 500-V Charged-Device Model (C101)

– 8kV HBM for SIM Pins

Package

– 16-Pin QFN (3 mm x 3 mm)

– 12-Pin QFN (2mm x 1.7mm)

VBATT

•

GND

The device has two supply voltage pins. VCC can be operated over the full range of 1.65 V to 3.3 V and VBATT

from 2.3 to 5.5 V. VPWR is set to either 1.8 V or 2.95 V and is supplied by an internal LDO. The integrated LDO

accepts input voltages as high as 5.5 V and outputs either 1.8 V or 2.95 V at 50 mA to the B-side circuitry and to

the external SIM card. The TXS4555 enables system designers to easily interface low-voltage microprocessors

to SIM cards operating at 1.8 V or 2.95 V.

The TXS4555 also incorporates shutdown sequence for the SIM card pins based on the ISO 7816-3 specification

for SIM cards. Proper shutdown of the SIM card signals helps in prevention of corruption of data during

accidental shutdown of the phone. The device also has 8kV HBM protection for the SIM pins and standard 2kV

HBM protection for all the other pins.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2011–2013, Texas Instruments Incorporated

�TXS4555

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

VBATT

(2.3 to 5.5 V)

Core Supply

VCC (1.65 to 3.3 V)

LDO

Baseband

2.95 V or 1.8 V,

50 mA

Reset

CLK

Translator

I/O

Vcc

GND

RST

Vpp

CLK

I/O

NC

NC

Figure 1. Interfacing with SIM Card

PIN FUNCTIONS

PIN NAME

PIN NO.

RGT

RUT

EN

1

11

SEL

2

Vcc

3

VBATT

TYPE (1)

DESCRIPTION

I

Enable/disable control input. Pull EN low to place all outputs in Hi-Z state and to disable the

LDO. Referenced to VCC.

12

I

Pin to program VSIM value (Low = 1.8V, High = 2.95V)

1

P

Power supply voltage which powers all A-port I/Os and control inputs

5

2

P

Battery power supply

VSIM

7

3

O

SIM card Power-Supply pin (1.8V or 2.95V)

SIM_I/O

8

4

I/O

Bidirectional SIM I/O pin which connected to I/O pin of the SIM card connector

SIM_RST

9

5

O

SIM Reset pin which connects to RESET pin of the SIM card connector

GND

10

6

G

Ground

SIM_CLK

11

7

O

Clock signal pin which connects to CLK pin of the SIM card connector

CLK

13

8

I

Clock signal pin connected from baseband processor

RST

14

9

I

SIM Reset pin connected from baseband processor

I/O

15

10

I/O

Bidirectional SIM I/O pin which connected from baseband processor

NC

4, 6, 12,

16

–

NC

No Connects

(1)

2

G = Ground, I = Input, O = Output, P = Power

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

�TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

Figure 2. Block Diagram

VBATT

Cin = 1 mF

VSIM

Vref

R

1

Cout = 1 mF

R

2

GND

Figure 3. Block Diagram of the LDO

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

3

�TXS4555

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

www.ti.com

EN

SIM_RST

SIM_CLK

Active Data

SIM_I/O

VSIM

Figure 4. Shutdown Sequence for SIM_RST, SIM_CLK, SIM_IO and VSIM

The shutdown sequence for the SIM signals is based on the ISO 7816-3 specification. The shutdown sequence

of these signals helps to properly disable these channels and not have any corruption of data accidently. Also,

this is also helpful when the SIM card is present in a hot swap slot and when pulling out the SIM card, the orderly

shutdown of these signals help avoid any improper write/corruption of data.

When EN is taken low, the shutdown sequence happens by powering of the SIM_RST channel. Once that is

achieved, SIM_CLK, SIM_I/O and VSIM are powered sequentially one by one. There is an internal 2K pull-down

value on the SIM pins and helps to pull these channels low. The shutdown time sequence is in the order of a few

microseconds. It is important that EN is taken low before VBAT and VCC supplies go low so that the shutdown

sequence can be initiated properly.

4

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

�TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

ABSOLUTE MAXIMUM RATINGS (1)

over operating free-air temperature range (unless otherwise noted)

VALUE

MIN

MAX

UNIT

LEVEL TRANSLATOR

VCC

Supply voltage range

VI

Input voltage range

Voltage range applied to any output in the

high-impedance or power-off state

VO

Voltage range applied to any output in the

high or low state

VO

–0.3

4.0

VCC-port

–0.5

4.6

SIM-port

–0.5

4.6

Control inputs

–0.5

4.6

VCC -port

–0.5

4.6

VSIM-port

–0.5

4.6

Control inputs

–0.5

4.6

VCC-port

–0.5

4.6

SIM-port

–0.5

4.6

Control inputs

–0.5

4.6

V

V

V

V

IIK

Input clamp current

VI < 0

–50

mA

IOK

Output clamp current

VO < 0

–50

mA

IO

Continuous output current

Continuous current through VCCA or GND

Tstg

±50

mA

±100

mA

Storage temperature range

–65

150

°C

VBAT

Input voltage range

–0.3

6

V

VOUT

Output voltage range

–0.3

6

V

Peak output current

TBD

LDO

Continuous total power dissipation

mA

TBD

TJ

Junction temperature range

–55

150

°C

Tstg

Storage temperature range

–55

150

°C

2

kV

Human-Body Model (HBM)

ESD rating (host side)

Charged-Device Model (CDM)

ESD rating (SIM side)

(1)

Human-Body Model (HBM)

500

V

8

kV

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating

conditions” is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

THERMAL INFORMATION

TXS4555

THERMAL METRIC (1)

RGT

RUT

16 PINS

12 PINS

47

87.2

25.12

N/A

θJA

Junction-to-ambient thermal resistance

θJB

Junction-to-board thermal resistance

ψJT

Junction-to-top characterization parameter

1.3

1.7

θJCbot

Junction-to-case (bottom) thermal resistance

3.6

n/A

(1)

UNITS

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

5

�TXS4555

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

www.ti.com

RECOMMENDED OPERATING CONDITIONS (1)

MIN

MAX UNIT

LEVEL TRANSLATOR

VCC

Supply voltage

1.65

3.3

EN, SEL, RST, CLK, I/O

VCC × 0.7

VCC

Vsim × 0.7

Vsim

VIH

High-level input

voltage

VCC - port

SIM - port

SIM_I/O

VIL

Low-level input

voltage

VCC - port

EN, SEL, RST, CLK, I/O

0

VCC × 0.3

SIM - port

SIM_I/O

0

Vsim × 0.3

–40

85

Δt/Δv Input transition rise or fall rate

TA

(1)

V

V

V

5 ns/V

Operating free-air temperature

°C

All unused data inputs of the device must be held at VCCI or GND to ensure proper device operation. Refer to the TI application report,

Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

ELECTRICAL CHARACTERISTICS – LEVEL TRANSLATOR

over recommended operating free-air temperature range (unless otherwise noted)

PARAMETER

VOH

VOL

TEST CONDITIONS

VCC

(2)

IOH = –1mA

SIM_CLK

IOH = –1mA

VSIM × 0.8

SIM_I/O

IOH = –20 µA

VSIM × 0.8

I/O

IOH = –20 µA

IOL = 1 mA

SIM_CLK

IOL = 1mA

SIM_I/O

IOL = 1 mA

I/O

IOL = 1 mA

1.8 V / 2.95 V

MIN

SIM_RST

SIM_RST

1.65 V to 3.3 V

VSIM

1.65 V to 3.3 V

1.8 V / 2.95 V

VSIM × 0.2

V

0.3

0.3

(2)

VI = EN, 1.8V/3V

1.65 V to 3.3 V

1.8 V / 2.95 V

I/O

VI = VCCI, IO = 0

1.65 V to 3.3 V

1.8 V / 2.95 V (2)

(1)

(2)

V

VSIM × 0.2

Control inputs

I/O port

±1

µA

±5

µA

8

SIM ports

Control inputs

UNIT

VCC × 0.8

ICC

Ci

MAX

VSIM × 0.8

(2)

II

Cio

TYP (1)

pF

4

VI = VCC or GND

4

pF

All typical values are at TA = 25°C.

(Supplied by LDO)

LDO ELECTRICAL CHARACTERISTICS

PARAMETER

VBAT

Input voltage

VSIM

Output voltage

TEST CONDITIONS

MIN

TYP (1) MAX UNIT

2.3

Class-B Mode (SEL = VCC)

Class-C Mode (SEL = 0)

5.5

V

2.85

2.95

3.05

V

1.7

1.8

1.9

VDO

Dropout voltage

IOUT = 50 mA

100

mV

IGND

Ground-pin current

IOUT = 0 mA

35

µA

ISHDN

Shutdown current

(IGND)

VENx ≤ 0.4 V, (VSIM + VDO) ≤ VBAT ≤ 5.5 V, TJ = 85°C

3.5

µA

IOUT(SC)

Short-circuit current

RL = 0 Ω

COUT

Output Capacitor

f = 1 kHz

50

f = 10 kHz

40

PSRR

Power-supply rejection

ratio

VBAT = 3.25 V, VSIM = 1.8 V or 2.95 V,

COUT = 1 µF, IOUT = 50 mA

TSTR

Start-up time

VSIM = 1.8 V or 2.95 V, IOUT = 50 mA, COUT = 1 µF

TJ

Operating junction

temperature

(1)

6

–40

145

mA

1

µF

dB

400

µS

125

°C

All typical values are at TA = 25°C.

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

�TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

GENERAL ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP MAX UNIT

RI/OPU

I/O pull-up

16

20

24

kΩ

RSIMPU

SIM_I/O pull-up

10

14

18

kΩ

3

kΩ

RSIMPD

SIM_I/O pull-down

Active pull-downs are connected to the VSIM regulator output to the

SIM_CLK, SIM_RST, SIM_I/O when EN = 0

SWITCHING CHARACTERISTICS

over recommended operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

VCC = 1.8 V ± 0.15 V

MIN

UNIT

MAX

VSIM = 1.8 V or 2.95 V SUPPLIED BY INTERNAL LDO

trA

trB

SIM_I/O

1

µs

SIM_RST

1

µs

SIM_CLK

18

ns

1

us

SIM_I/O

fmax

SIM_CLK

Duty Cycle

SIM_CLK

CL

= 50 pF

25 MHz

40%

60%

OPERATING CHARACTERISTICS

TA = 25°C, VSIM = 1.8 V

PARAMETER

CpdA (1)

(1)

Class B

Class C

TEST CONDITIONS

CL = 0, f = 5 MHz, tr = tf = 1 ns

Vcc TYP

UNIT

1.8 V

13

11

pF

Power dissipation capacitance per transceiver.

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

7

�TXS4555

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

www.ti.com

TYPICAL CHARACTERISTICS

110

VBAT = 3.25 V,

ILOAD = 50 mA

-80

1.8 V Vsim

90

-70

-60

2.95 V Vsim

-50

VBAT = 5.5 V

100

VDO - Dropout Voltage - mV

PSRR - Power Supply Rejection Ratio - dB

-90

-40

-30

-20

85°C Vsim

80

70

25°C Vsim

60

50

40

30

-40°C Vsim

20

-10

10

0

100

1k

10k

f - Frequency - Hz

100k

0

1M

0

1

0

0.8

0.6

-0.2

0.4

0.2

-2

-2.2

-2.4

-40 -30 -20 -10

-50 mA, Vism

50

-40°C Vsim

-0.6

-0.8

-1

85°C Vsim

-1.2

-1.4

25°C Vsim

-1.6

-1.8

-2

0 10 20 30 40 50 60 70 80

TA - Temperature - °C

Figure 7. Output Voltage vs Temperature, Class-B/C

8

15 20

25 30 35 40 45

IOUT Output Current - mA

Figure 6. Dropout Voltage vs Output Current

-0.4

-100 mA, Vism

0

-0.2

-0.4

-0.6

-0.8

-1

-1.2

-1.4

-1.6

-1.8

10

IO = 50 mA

DVOUT - Output Voltage - %

DVOUT - Output Voltage - %

Figure 5. PSRR

5

0

15 20

25 30 35 40 45 50

IOUT Output Current - mA

Figure 8. Load Regulation, Iout = 50 mA, Class-C

Submit Documentation Feedback

5

10

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

�TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

APPLICATION INFORMATION

The LDO’s included on the TXS4555 achieve ultra-wide bandwidth and high loop gain, resulting in extremely

high PSRR at very low headroom (VBAT – VSIM). The TXS4555 provides fixed regulation at 1.8V or 2.95V. Low

noise, enable, low ground pin current make it ideal for portable applications. The device offers sub-bandgap

output voltages, current limit and thermal protection, and is fully specified from –40°C to 125°C.

VSIM

VCC

TXS4555

VBAT

GND

1 mF

1 mF

0.1 mF

Figure 9. Typical Application Circuit for TXS4555

INPUT AND OUTPUT CAPACITOR REQUIREMENTS

It is good analog design practice to connect a 1.0 µF low equivalent series resistance (ESR) capacitor across the

input supply (VBAT) near the regulator. Also, a 0.1µF is required for the logic core supply (VDDIO).

This capacitor will counteract reactive input sources and improve transient response, noise rejection, and ripple

rejection. A higher-value capacitor may be necessary if large, fast rise-time load transients are anticipated or if

the device is located several inches from the power source. The LDO’s are designed to be stable with standard

ceramic capacitors of values 1.0 µF or larger. X5R- and X7R-type capacitors are best because they have

minimal variation in value and ESR over temperature. Maximum ESR should be < 1.0 Ω.

OUTPUT NOISE

In most LDO’s, the bandgap is the dominant noise source. To improve ac performance such as PSRR, output

noise, and transient response, it is recommended that the board be designed with separate ground planes for VIN

and VOUT, with each ground plane connected only at the GND pin of the device. In addition, the ground

connection for the bypass capacitor should connect directly to the GND pin of the device.

INTERNAL CURRENT LIMIT

The TXS4555 internal current limit helps protect the regulator during fault conditions. During current limit, the

output sources a fixed amount of current that is largely independent of output voltage. For reliable operation, the

device should not be operated in a current limit state for extended periods of time.

The PMOS pass element in the TXS4555 has a built-in body diode that conducts current when the voltage at

VSIM exceeds the voltage at VBAT. This current is not limited, so if extended reverse voltage operation is

anticipated, external limiting may be appropriate.

DROPOUT VOLTAGE

The TXS4555 uses a PMOS pass transistor to achieve low dropout. When (VBAT – VSIM) is less than the dropout

voltage (VDO), the PMOS pass device is in its linear region of operation and the input-to-output resistance is the

RDS(ON) of the PMOS pass element. VDO will approximately scale with output current because the PMOS device

behaves like a resistor in dropout.

STARTUP

The TXS4555 uses a quick-start circuit which allows the combination of very low output noise and fast start-up

times.

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

9

�TXS4555

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

www.ti.com

TRANSIENT RESPONSE

As with any regulator, increasing the size of the output capacitor reduces over/undershoot magnitude but

increases duration of the transient response.

MINIMUM LOAD

The TXS4555 is stable and well-behaved with no output load. Traditional PMOS LDO regulators suffer from

lower loop gain at very light output loads. The TXS4555 employs an innovative low-current mode circuit to

increase loop gain under very light or no-load conditions, resulting in improved output voltage regulation

performance down to zero output current.

THERMAL INFORMATION

Thermal Protection

Thermal protection disables the output when the junction temperature rises to approximately +160°C, allowing

the device to cool. When the junction temperature cools to approximately +140°C the output circuitry is again

enabled. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection

circuit may cycle on and off. This cycling limits the dissipation of the regulator, protecting it from damage

because of overheating.

Any tendency to activate the thermal protection circuit indicates excessive power dissipation or an inadequate

heat sink. For reliable operation, junction temperature should be limited to +125°C maximum. To estimate the

margin of safety in a complete design (including heat sink), increase the ambient temperature until the thermal

protection is triggered; use worst-case loads and signal conditions. For good reliability, thermal protection should

trigger at least +35°C above the maximum expected ambient condition of your particular application. This

configuration produces a worst-case junction temperature of +125°C at the highest expected ambient

temperature and worst-case load.

The internal protection circuitry of the TXS4555 has been designed to protect against overload conditions. It was

not intended to replace proper heat sinking. Continuously running the TXS4555 into thermal shutdown will

degrade device reliability.

10

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

�TXS4555

www.ti.com

SBOS550B – FEBRUARY 2011 – REVISED AUGUST 2013

REVISION HISTORY

Changes from Revision A (March 2011) to Revision B

Page

•

Removed Ordering Information table. ................................................................................................................................... 2

•

Updated VIH and VIL to specify additional information. ......................................................................................................... 6

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: TXS4555

11

�PACKAGE OPTION ADDENDUM

www.ti.com

10-Dec-2020

PACKAGING INFORMATION

Orderable Device

Status

(1)

Package Type Package Pins Package

Drawing

Qty

Eco Plan

(2)

Lead finish/

Ball material

MSL Peak Temp

Op Temp (°C)

Device Marking

(3)

(4/5)

(6)

TXS4555RGTR

ACTIVE

VQFN

RGT

16

3000

RoHS & Green

NIPDAU

Level-2-260C-1 YEAR

-40 to 85

ZUT

TXS4555RUTR

ACTIVE

UQFN

RUT

12

3000

RoHS & Green

NIPDAUAG

Level-1-260C-UNLIM

-40 to 85

69R

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance

do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may

reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of