32-Bit

Microcontroller

TC37x

32-Bit Single-Chip Microcontroller

AA-Step

32-Bit Single-Chip Microcontroller

Data Sheet

V 1.1, 2021-03

Microcontroller

OPEN MARKET VERSION

�Edition 2021-03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2021 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com)

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

OPEN MARKET VERSION

�TC37x AA-Step

Revision History

Page or Item

Subjects (major changes since previous revision)

V 0.4, 2018-01

Version 0.4 is the first version of this document

V 0.6, 2018-10

The history is documented in the last chapter

V 0.61, 2019-01

The history is documented in the last chapter

V 0.7, 2019-05

The history is documented in the last chapter

V 1.0, 2020-01

The history is documented in the last chapter

V 1.1, 2021-03

The history is documented in the last chapter

Data Sheet

3

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Trademarks of Infineon Technologies AG

AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, EconoPACK™, CoolMOS™, CoolSET™,

CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™, EasyPIM™, EconoBRIDGE™, EconoDUAL™,

EconoPIM™, EconoPACK™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, I²RF™,

ISOFACE™, IsoPACK™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OptiMOS™, ORIGA™,

POWERCODE™; PRIMARION™, PrimePACK™, PrimeSTACK™, PRO-SIL™, PROFET™, RASIC™,

ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™, SmartLEWIS™, SOLID FLASH™, TEMPFET™,

thinQ!™, TRENCHSTOP™, TriCore™.

Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™,

PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR

development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™,

FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG.

FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of

Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data

Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of

MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics

Corporation. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA

MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of

OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF

Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™

of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co.

TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™

of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas

Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes

Zetex Limited.

Last Trademarks Update 2011-11-11

Data Sheet

4

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Table of Contents

1

Summary of Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2

2.1

2.2

2.3

2.4

TC37x Pin Definition and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

LFBGA-292 Package Pinning of TC37x TP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

LQFP-176 Package Pinning of TC37x T and TP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Sequence of Pads in Pad Frame . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Legend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

3

3.1

3.2

3.3

3.4

3.5

3.6

3.7

3.8

3.9

3.10

3.11

3.12

3.12.1

3.13

3.13.1

3.13.1.1

3.13.1.2

3.13.1.3

3.13.1.4

3.14

3.15

3.16

3.17

3.18

3.19

3.20

3.21

3.22

3.23

3.24

3.24.1

3.24.2

3.24.3

3.24.4

3.24.5

3.25

3.26

3.27

3.28

3.29

3.30

Electrical Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parameter Interpretation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Pin Reliability in Overload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 V / 3.3 V switchable Pads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

High performance LVDS Pads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VADC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DSADC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MHz Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Back-up Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Calculating the 1.25 V Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Supply Infrastructure and Supply Start-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply Ramp-up and Ramp-down Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Single Supply mode (a) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Single Supply mode (e) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Supply mode (d) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Supply mode (h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Phase Locked Loop (SYS_PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peripheral Phase Locked Loop (PER_PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

JTAG Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DAP Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ASCLIN SPI Master Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

QSPI Timings, Master and Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MSC Timing 5 V Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Ethernet Interface (ETH) Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ETH Measurement Reference Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ETH Management Signal Parameters (ETH_MDC, ETH_MDIO) . . . . . . . . . . . . . . . . . . . . . . . . .

ETH MII Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ETH RMII Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

ETH RGMII Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

E-Ray Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

HSCT Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Inter-IC (I2C) Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Target Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Quality Declarations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Sheet

5

OPEN MARKET VERSION

212

212

213

214

217

221

241

244

248

251

253

254

255

262

263

263

263

266

268

270

272

275

285

286

287

288

290

292

294

298

300

300

301

302

303

304

305

307

308

312

317

318

V 1.1, 2021-03

�TC37x AA-Step

3.30.1

4

4.1

4.2

4.3

4.4

4.5

4.6

Package Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 0.4 to Version 0.6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 0.6 to Version 0.61 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 0.61 to Version 0.7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 0.7 to Version 0.71 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 0.71 to Version 1.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Changes from Version 1.0 to Version 1.1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data Sheet

6

OPEN MARKET VERSION

321

321

330

333

335

337

338

V 1.1, 2021-03

�TC37x AA-Step

Summary of Features

1

Summary of Features

The TC37x product family has the following features:

•

High Performance Microcontroller with three CPU cores

•

Three 32-bit super-scalar TriCore CPUs (TC1.6.2P), each having the following features:

–

Superior real-time performance

–

Strong bit handling

–

Fully integrated DSP capabilities

–

Multiply-accumulate unit able to sustain 2 MAC operations per cycle

–

Fully pipelined Floating point unit (FPU)

–

up to 300 MHz operation at full temperature range

–

up to 240/96 Kbyte Data Scratch-Pad RAM (DSPR)

–

up to 64 Kbyte Instruction Scratch-Pad RAM (PSPR)

–

32 Kbyte Instruction Cache (ICACHE)

–

16 Kbyte Data Cache (DCACHE)

•

Lockstepped shadow cores for up to two TC1.6.2P

•

Multiple on-chip memories

–

All embedded NVM and SRAM are ECC protected

–

up to 6 Mbyte Program Flash Memory (PFLASH)

–

up to 256 Kbyte Data Flash Memory (DFLASH 0) usable for EEPROM emulation

–

BootROM (BROM)

•

128-Channel DMA Controller with safe data transfer

•

Sophisticated interrupt system (ECC protected)

•

High performance on-chip bus structure

–

64-bit Cross Bar Interconnect (SRI) giving fast parallel access between bus masters, CPUs and memories

–

32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

–

SRI to SPB bus bridges (SFI Bridge)

•

Optional Hardware Security Module (HSM) on some variants

•

Safety Management Unit (SMU) handling safety monitor alarms

•

Memory Test Unit with ECC, Memory Initialization and MBIST functions (MTU)

•

Hardware I/O Monitor (IOM) for checking of digital I/O

•

Versatile On-chip Peripheral Units

–

12 Asynchronous/Synchronous Serial Channels (ASCLIN) with hardware LIN support (V1.3, V2.0, V2.1

and J2602) up to 50 MBaud

–

5 Queued SPI Interface Channels (QSPI) with master and slave capability up to 50 Mbit/s

–

1 High Speed Serial Link (HSSL) for serial inter-processor communication up to 320 Mbit/s

–

2 serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

–

2 MCMCAN Modules with 4 CAN nodes for high efficiency data handling via FIFO buffering

–

15 Single Edge Nibble Transmission (SENT) channels for connection to sensors

–

1 FlexRayTM module with 2 channels (E-Ray) supporting V2.1

–

One Generic Timer Module (GTM) providing a powerful set of digital signal filtering and timer functionality

to realize autonomous and complex Input/Output management

–

One Capture / Compare 6 module (Two kernels CCU60 and CCU61)

Data Sheet

7

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Summary of Features

•

•

–

One General Purpose 12 Timer Unit (GPT120)

–

2 channel Peripheral Sensor Interface conforming to V1.3 (PSI5)

–

1 Peripheral Sensor Interface with Serial PHY (PSI5-S)

–

1 Inter-Integrated Circuit Bus Interface (I2C) conforming to V2.1

–

1 IEEE802.3 Ethernet MAC with RMII and MII interfaces (ETH)

Versatile Successive Approximation ADC (VADC)

–

Cluster of 12 independent ADC kernels

–

Input voltage range from 0 V to 5.5V (ADC supply)

Delta-Sigma ADC (DSADC)

–

6 channels

•

Digital programmable I/O ports

•

On-chip debug support for OCDS Level 1 (CPUs, DMA, On Chip Buses)

•

multi-core debugging, real time tracing, and calibration

•

four/five wire JTAG (IEEE 1149.1) or DAP (Device Access Port) interface

•

Power Management System and on-chip regulators

•

Clock Generation Unit with System PLL and Peripheral PLL

•

Embedded Voltage Regulator

•

Qualified for automotive application according to AEC-Q100 (only applicable after delivery release of the

corresponding sales codes)

•

ISO 26262 Safety Element out of Context for safety requirements up to ASIL D (only applicable for sales codes

listed within a released Safety Package Release Note from IFX)

Data Sheet

8

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Summary of Features

Ordering Information

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering

code identifies:

•

The derivative itself, i.e. its function set, the temperature range, and the supply voltage

•

The package and the type of delivery

Table 1-1

Platform Feature Overview

Feature

CPUs

TC37x

Type

TC1.6.2

Cores / Checker Cores

3/2

Max. Freq.

300 MHz

Program

32 KB

Data

16 KB

PSPR

64 KB

DSPR

240 KB for CPU0,1/ 96 KB else

DLMU

64 KB

SRAM global

DAM

32 KB

Extension Memory

TCM

-

XCM

-

XTM

-

Size

6 MB

Banks

2 x 3 MB

Data Flash

Size (single-ended)

256 KB (DF0) + 128 KB (DF1)

DMA

Channels

128

CONVCTRL

Modules

1

EVADC

Primary Groups/Channels

4 / 32

Secondary Groups/Channels

4 / 64

Fast Compare Channels

4

Channels

6

Cache per CPU

SRAM per CPU

Program Flash

EDSADC

Data Sheet

9

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Summary of Features

Table 1-1

Platform Feature Overview (cont’d)

Feature

GTM

TC37x

Clusters

6 (5 @ 200 MHz + 1 @ 100 MHz)

TIM (8 ch)

6

TOM (16 ch)

3

ATOM (8 ch)

6

MCS (8 ch)

5

CMU / ICM

1/1

PSM

1

TBU channels

1)

4 (TBU0-3)

SPE

2

CMP / MON

1/1

BRC / DPLL

1/1

CDTM modules

5

DTM modules

16 (6 on TOM, 10 on ATOM)

GPT12

1

CCU6

1

STM

Modules

3

FlexRay

Modules

1

Channels

2

Modules

2

Nodes

2x4

of which support TT-CAN

1

Modules

5

HSCI Channels

0

ASCLIN

Modules

12

I2C

Interfaces

1

SENT

Channels

15

PSI5

Modules

2

PSI5-S

Modules

1

HSSL

Channels

1

MSC

Channels

2

SDMMC

eMMC/SD Interface

-

CIF

Camera Interface

-

Ethernet (10/100Mbit/1Gbit)

Modules

1

FCE

Modules

1

Safety Support

SMU

yes

IOM

yes

HSM+

1

Timer

CAN

QSPI

Security

Data Sheet

10

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

Summary of Features

Table 1-1

Platform Feature Overview (cont’d)

Feature

Debug

TC37x

OCDS

yes

MCDS

no

miniMCDS

yes

miniMCDS TRAM

8 KB

AGBT

no

Standby RAM

2

SCR

yes

Packages

Type

Pad Position Configuration /

LFBGA-292 / LQFP-176 /

I/O

Type

5 V CMOS / 3.3 V CMOS / LVDS

Tambient

Range

Low Power Features

−40 … +150°C

1) TBU3 has special purpose as angle clock.

Data Sheet

11

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions

2

TC37x Pin Definition and Functions

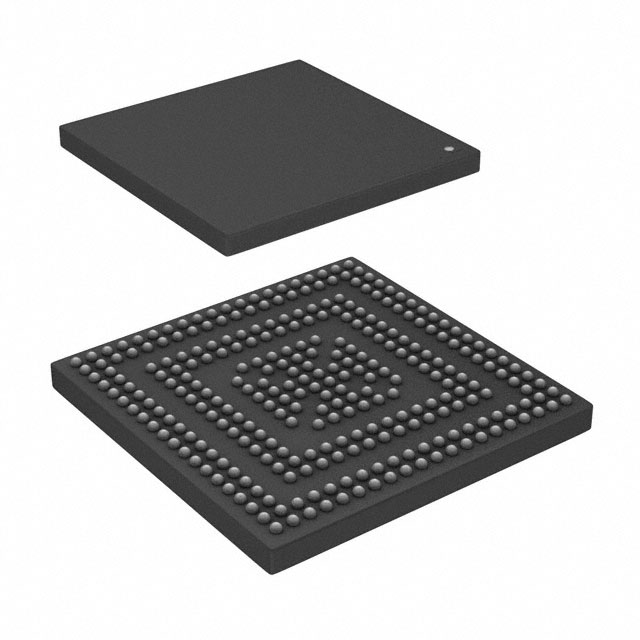

The following figures show the TC37x package variants:

•

LFBGA-292 for feature package TP (Figure 2-1)

•

LQFP-176 for feature package T and TP (Figure 2-2)

•

Sequence of Pads in Pad Frame (Chapter 2.3)

Data Sheet

12

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

2.1

LFBGA-292 Package Pinning of TC37x TP

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

A

NC1

VEXT

P10.7

P10.6

P10.2

P10.3

P10.0

P11.11

P11.9

P11.2

P13.3

P13.1

P14.8

P14.5

P14.1

P15.6

P15.4

P15.1

VDDP3

VSS

A

B

P02.0

VSS

VEXT

P10.8

P10.5

P10.4

P10.1

P11.12

P11.10

P11.3

P13.2

P13.0

P14.6

P14.3

P14.4

P14.0

P15.3

VDDP3

VSS

P15.0

B

C

P02.2

P02.1

P15.2

P20.14

C

D

P02.4

P02.3

VSS

VFLEX

P11.15

P11.14

P11.5

P11.6

P11.4

P14.10

P14.9

P14.7

P15.8

P15.7

VDD

VSS

P20.12

P20.13

D

E

P02.6

P02.5

P02.9

VSS

P11.13

P11.8

P11.7

P11.1

P11.0

P12.1

P12.0

P14.2

P15.5

VDD

VSS

P20.9

P20.10

P20.11

E

F

P02.8

P02.7

P02.11

P02.10

ESR0

P20.6

P20.7

P20.8

F

G

P00.0

P00.1

P01.4

P01.3

ESR1

PORST

P20.1

P20.3

G

H

P00.2

P00.3

P01.6

P01.5

VDD

VDD

P21.7 /

TDO

P21.6 /

TDI

P20.2

P20.0

H

J

P00.4

P00.5

P00.6

P01.7

VSS

VSS

VSS

VSS

TCK

P21.1

P21.3

P21.5

J

K

P00.7

P00.9

P00.8

P00.10

VSS

VSS

L

P00.11

P00.12

AN43

AN42

VSS

VSS

M

AN46

AN47

AN41

AN40

VSS

VSS

N

AN44

AN45

AN36 /

P40.6

AN38 /

P40.8

VDD

P

AN39 /

P40.9

AN37 /

P40.7

AN32 /

P40.4

AN34

R

AN33 /

P40.5

AN35

AN31

AN23

T

VAREF

2

VAGND

2

AN30

AN22

AN15

AN12

AN6

AN4

AN0

VEVRS

B

P34.2

P34.4

P33.14

U

AN29 /

P40.14

AN28 /

P40.13

NC1

AN17 /

P40.10

AN14

AN9

AN7

AN3

AN1

P34.1

P34.3

P34.5

P33.15

V

AN27 /

P40.3

AN26 /

P40.2

W

AN25 /

P40.1

AN24 /

P40.0

AN19 /

P40.12

AN18 /

P40.11

AN16

AN13

AN11

AN8

AN2

P33.0

P33.2

P33.4

P33.6

P33.8

P33.10

P33.12

P32.1 /

VGATE

1P

Y

NC1

AN21

AN20

VSSM

VDDM

VAREF

1

VAGND

1

AN10

AN5

P33.1

P33.3

P33.5

P33.7

P33.9

P33.11

P33.13

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

VDD

VDD

VSS

VSS

VSS

VSS

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC

TMS

P21.0

P21.2

P21.4

K

VSS

VSS

VSS

VSS

VSS

VSS

P22.10

P22.11

TRST

VSS

L

VSS

VSS

VSS

VSS

P22.8

P22.9

XTAL2

XTAL1

M

VSS

VSS

VSS

VSS

VDD

P22.6

P22.7

VDD

VEXT

N

VSS

VSS

VSS

VSS

P22.4

P22.5

P22.1

P22.0

P

P23.7

P23.6

P22.3

P22.2

R

P32.5

VSS

P23.5

P23.3

P23.4

T

P32.6

P32.7

VSS

P23.1

P23.2

U

VEXT

P23.0

V

P32.4

VSS

VEXT

W

P32.0 /

VGATE

1N

P32.2

P32.3

VSS

Y

17

18

19

20

VDD

TC37xpd - (top view)

Figure 2-1 TC37x TP package variant LFBGA-292

Data Sheet

13

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions

Ball

Symbol

Ctrl.

Buffer

Type

Function

G1

P00.0

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM5_IN4_10

GTM_TIM3_IN0_1

GTM_TIM2_IN0_1

Mux input channel 4 of TIM module 5

Mux input channel 0 of TIM module 3

Mux input channel 0 of TIM module 2

CCU61_CTRAPA

Trap input capture

CCU60_T12HRE

External timer start 12

MSC0_INJ0

Injection signal from port

GETH_MDIOA

MDIO Input

P00.0

O0

General-purpose output

GTM_TOUT9

O1

GTM muxed output

IOM_REF0_9

Reference input 0

ASCLIN3_ASCLK

O2

Shift clock output

ASCLIN3_ATX

O3

Transmit output

IOM_MON2_15

Monitor input 2

IOM_REF2_15

Reference input 2

—

O4

Reserved

CAN10_TXD

O5

CAN transmit output node 0

—

O6

Reserved

CCU60_COUT63

O7

T13 PWM channel 63

IOM_MON1_6

Monitor input 1

IOM_REF1_0

Reference input 1

GETH_MDIO

Data Sheet

O

MDIO Output

14

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

G2

P00.1

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM5_IN5_11

GTM_TIM3_IN1_1

GTM_TIM2_IN1_1

Mux input channel 5 of TIM module 5

Mux input channel 1 of TIM module 3

Mux input channel 1 of TIM module 2

CCU60_CC60INB

T12 capture input 60

ASCLIN3_ARXE

Receive input

EDSADC_DSCIN5A

Modulator clock input, channel 5

CAN10_RXDA

CAN receive input node 0

PSI5_RX0A

RXD inputs (receive data) channel 0

CCU61_CC60INA

T12 capture input 60

SENT_SENT0B

Receive input channel 0

EVADC_G9CH11

AI

EDSADC_EDS5NA

Analog input channel 11, group 9

Negative analog input channel 5, pin A

P00.1

O0

General-purpose output

GTM_TOUT10

O1

GTM muxed output

IOM_REF0_10

ASCLIN3_ATX

Reference input 0

O2

Transmit output

IOM_MON2_15

Monitor input 2

IOM_REF2_15

Reference input 2

—

O3

Reserved

EDSADC_DSCOUT5

O4

Modulator clock output

—

O5

Reserved

SENT_SPC0

O6

Transmit output

CCU61_CC60

O7

T12 PWM channel 60

IOM_MON1_8

Monitor input 1

IOM_REF1_13

Reference input 1

Data Sheet

15

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

H1

P00.2

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM5_IN6_11

GTM_TIM3_IN1_2

GTM_TIM2_IN1_2

Mux input channel 6 of TIM module 5

Mux input channel 1 of TIM module 3

Mux input channel 1 of TIM module 2

EDSADC_DSDIN5A

Digital datastream input, channel 5

SENT_SENT1B

Receive input channel 1

EVADC_G9CH10

AI

EDSADC_EDS5PA

Analog input channel 10, group 9

Positive analog input channel 5, pin A

P00.2

O0

General-purpose output

GTM_TOUT11

O1

GTM muxed output

IOM_REF0_11

Reference input 0

ASCLIN3_ASCLK

O2

Shift clock output

—

O3

Reserved

PSI5_TX0

O4

TXD outputs (send data)

IOM_MON1_14

Monitor input 1

IOM_REF1_14

Reference input 1

CAN03_TXD

O5

CAN transmit output node 3

IOM_MON2_8

Monitor input 2

IOM_REF2_8

Reference input 2

QSPI3_SLSO4

O6

Master slave select output

CCU61_COUT60

O7

T12 PWM channel 60

IOM_MON1_11

Monitor input 1

IOM_REF1_10

Reference input 1

Data Sheet

16

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

H2

P00.3

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM5_IN7_10

GTM_TIM3_IN2_1

GTM_TIM2_IN2_1

Mux input channel 7 of TIM module 5

Mux input channel 2 of TIM module 3

Mux input channel 2 of TIM module 2

CCU60_CC61INB

T12 capture input 61

EDSADC_DSCIN3A

Modulator clock input, channel 3

EDSADC_ITR5F

Trigger/Gate input, channel 5

PSI5_RX1A

RXD inputs (receive data) channel 1

CAN03_RXDA

CAN receive input node 3

PSI5S_RXA

RX data input

SENT_SENT2B

Receive input channel 2

CCU61_CC61INA

T12 capture input 61

EVADC_G9CH9

AI

EDSADC_EDS5NB

Analog input channel 9, group 9

Negative analog input channel 5, pin B

P00.3

O0

General-purpose output

GTM_TOUT12

O1

GTM muxed output

IOM_REF0_12

Reference input 0

ASCLIN3_ASLSO

O2

Slave select signal output

—

O3

Reserved

EDSADC_DSCOUT3

O4

Modulator clock output

—

O5

Reserved

SENT_SPC2

O6

Transmit output

CCU61_CC61

O7

T12 PWM channel 61

IOM_MON1_9

Monitor input 1

IOM_REF1_12

Reference input 1

Data Sheet

17

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

J1

P00.4

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM3_IN3_1

GTM_TIM2_IN3_1

SCU_E_REQ2_2

Mux input channel 3 of TIM module 3

Mux input channel 3 of TIM module 2

ERU Channel 2 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

SENT_SENT3B

Receive input channel 3

EDSADC_DSDIN3A

Digital datastream input, channel 3

EDSADC_SGNA

Carrier sign signal input

ASCLIN10_ARXA

Receive input

EVADC_G9CH8

AI

EDSADC_EDS5PB

Analog input channel 8, group 9

Positive analog input channel 5, pin B

P00.4

O0

General-purpose output

GTM_TOUT13

O1

GTM muxed output

IOM_REF0_13

Reference input 0

PSI5S_TX

O2

TX data output

CAN11_TXD

O3

CAN transmit output node 1

PSI5_TX1

O4

TXD outputs (send data)

IOM_MON1_15

Monitor input 1

—

O5

Reserved

SENT_SPC3

O6

Transmit output

CCU61_COUT61

O7

T12 PWM channel 61

IOM_MON1_12

Monitor input 1

IOM_REF1_9

Reference input 1

Data Sheet

18

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

J2

P00.5

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM3_IN4_1

GTM_TIM3_IN0_11

GTM_TIM2_IN4_1

Mux input channel 4 of TIM module 3

Mux input channel 0 of TIM module 3

Mux input channel 4 of TIM module 2

CCU60_CC62INB

T12 capture input 62

EDSADC_DSCIN2A

Modulator clock input, channel 2

CCU61_CC62INA

T12 capture input 62

SENT_SENT4B

Receive input channel 4

CAN11_RXDB

CAN receive input node 1

GTM_DTMT1_1

CDTM1_DTM0

EVADC_G9CH7

AI

Analog input channel 7, group 9

P00.5

O0

General-purpose output

GTM_TOUT14

O1

GTM muxed output

IOM_REF0_14

Reference input 0

EDSADC_CGPWMN

O2

Negative carrier generator output

QSPI3_SLSO3

O3

Master slave select output

EDSADC_DSCOUT2

O4

Modulator clock output

EVADC_FC0BFLOUT

O5

Boundary flag output, FC channel 0

SENT_SPC4

O6

Transmit output

CCU61_CC62

O7

T12 PWM channel 62

IOM_MON1_10

Monitor input 1

IOM_REF1_11

Reference input 1

Data Sheet

19

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

J4

P00.6

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM3_IN5_1

GTM_TIM3_IN1_14

GTM_TIM2_IN5_1

Mux input channel 5 of TIM module 3

Mux input channel 1 of TIM module 3

Mux input channel 5 of TIM module 2

EDSADC_ITR4F

Trigger/Gate input, channel 4

EDSADC_DSDIN2A

Digital datastream input, channel 2

SENT_SENT5B

Receive input channel 5

ASCLIN5_ARXA

Receive input

EVADC_G9CH6

AI

Analog input channel 6, group 9

P00.6

O0

General-purpose output

GTM_TOUT15

O1

GTM muxed output

IOM_REF0_15

Reference input 0

EDSADC_CGPWMP

O2

Positive carrier generator output

—

O3

Reserved

—

O4

Reserved

EVADC_EMUX10

O5

Control of external analog multiplexer interface 1

SENT_SPC5

O6

Transmit output

CCU61_COUT62

O7

T12 PWM channel 62

IOM_MON1_13

Monitor input 1

IOM_REF1_8

Reference input 1

Data Sheet

20

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

K1

P00.7

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM3_IN6_1

GTM_TIM3_IN2_11

GTM_TIM2_IN6_1

Mux input channel 6 of TIM module 3

Mux input channel 2 of TIM module 3

Mux input channel 6 of TIM module 2

CCU61_CC60INC

T12 capture input 60

SENT_SENT6B

Receive input channel 6

EDSADC_DSCIN4A

Modulator clock input, channel 4

GPT120_T2INA

Trigger/gate input of timer T2

CCU61_CCPOS0A

Hall capture input 0

CCU60_T12HRB

External timer start 12

GTM_DTMT0_2

CDTM0_DTM0

EVADC_G9CH5

AI

EDSADC_EDS4NA

Analog input channel 5, group 9

Negative analog input channel 4, pin A

P00.7

O0

General-purpose output

GTM_TOUT16

O1

GTM muxed output

ASCLIN5_ATX

O2

Transmit output

EVADC_FC2BFLOUT

O3

Boundary flag output, FC channel 2

EDSADC_DSCOUT4

O4

Modulator clock output

EVADC_EMUX11

O5

Control of external analog multiplexer interface 1

SENT_SPC6

O6

Transmit output

CCU61_CC60

O7

T12 PWM channel 60

IOM_MON1_8

Monitor input 1

IOM_REF1_13

Reference input 1

Data Sheet

21

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

K4

P00.8

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM3_IN7_1

GTM_TIM3_IN3_11

GTM_TIM2_IN7_1

Mux input channel 7 of TIM module 3

Mux input channel 3 of TIM module 3

Mux input channel 7 of TIM module 2

CCU61_CC61INC

T12 capture input 61

SENT_SENT7B

Receive input channel 7

EDSADC_DSDIN4A

Digital datastream input, channel 4

GPT120_T2EUDA

Count direction control input of timer T2

CCU61_CCPOS1A

Hall capture input 1

CCU60_T13HRB

External timer start 13

ASCLIN10_ARXB

Receive input

EVADC_G9CH4

AI

EDSADC_EDS4PA

Analog input channel 4, group 9

Positive analog input channel 4, pin A

P00.8

O0

General-purpose output

GTM_TOUT17

O1

GTM muxed output

QSPI3_SLSO6

O2

Master slave select output

ASCLIN10_ATX

O3

Transmit output

—

O4

Reserved

EVADC_EMUX12

O5

Control of external analog multiplexer interface 1

SENT_SPC7

O6

Transmit output

CCU61_CC61

O7

T12 PWM channel 61

IOM_MON1_9

Monitor input 1

IOM_REF1_12

Reference input 1

Data Sheet

22

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

K2

P00.9

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM4_IN0_7

GTM_TIM1_IN0_1

GTM_TIM0_IN0_1

Mux input channel 0 of TIM module 4

Mux input channel 0 of TIM module 1

Mux input channel 0 of TIM module 0

CCU61_CC62INC

T12 capture input 62

SENT_SENT8B

Receive input channel 8

CCU61_CCPOS2A

Hall capture input 2

EDSADC_DSCIN1A

Modulator clock input, channel 1

EDSADC_ITR3F

Trigger/Gate input, channel 3

GPT120_T4EUDA

Count direction control input of timer T4

CCU60_T13HRC

External timer start 13

CCU60_T12HRC

External timer start 12

EVADC_G9CH3

AI

EDSADC_EDS4NB

Analog input channel 3, group 9

Negative analog input channel 4, pin B

P00.9

O0

General-purpose output

GTM_TOUT18

O1

GTM muxed output

QSPI3_SLSO7

O2

Master slave select output

ASCLIN3_ARTS

O3

Ready to send output

EDSADC_DSCOUT1

O4

Modulator clock output

ASCLIN4_ATX

O5

Transmit output

SENT_SPC8

O6

Transmit output

CCU61_CC62

O7

T12 PWM channel 62

IOM_MON1_10

Monitor input 1

IOM_REF1_11

Reference input 1

Data Sheet

23

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

K5

P00.10

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM4_IN1_11

GTM_TIM1_IN1_1

GTM_TIM0_IN1_1

Mux input channel 1 of TIM module 1

Mux input channel 1 of TIM module 0

SENT_SENT9B

Receive input channel 9

EDSADC_DSDIN1A

Digital datastream input, channel 1

EVADC_G9CH2

AI

Analog input channel 2, group 9

EDSADC_EDS4PB

L1

Mux input channel 1 of TIM module 4

Positive analog input channel 4, pin B

P00.10

O0

General-purpose output

GTM_TOUT19

O1

GTM muxed output

ASCLIN4_ASCLK

O2

Shift clock output

—

O3

Reserved

—

O4

Reserved

—

O5

Reserved

SENT_SPC9

O6

Transmit output

CCU61_COUT63

O7

T13 PWM channel 63

IOM_MON1_7

Monitor input 1

IOM_REF1_7

Reference input 1

P00.11

I

GTM_TIM4_IN2_11

GTM_TIM1_IN2_1

GTM_TIM0_IN2_1

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

Mux input channel 2 of TIM module 4

Mux input channel 2 of TIM module 1

Mux input channel 2 of TIM module 0

CCU60_CTRAPA

Trap input capture

EDSADC_DSCIN0A

Modulator clock input, channel 0

CCU61_T12HRE

External timer start 12

SENT_SENT10B

Receive input channel 10

EVADC_G9CH1

AI

EVADC_FC3CH0

Analog input channel 1, group 9

Analog input FC channel 3

P00.11

O0

General-purpose output

GTM_TOUT20

O1

GTM muxed output

ASCLIN4_ASLSO

O2

Slave select signal output

—

O3

Reserved

EDSADC_DSCOUT0

O4

Modulator clock output

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

24

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-1

Port 00 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

L2

P00.12

I

SLOW /

PU1 /

VEXT /

ES1

General-purpose input

GTM_TIM4_IN3_11

GTM_TIM1_IN3_1

GTM_TIM0_IN3_1

Mux input channel 3 of TIM module 4

Mux input channel 3 of TIM module 1

Mux input channel 3 of TIM module 0

ASCLIN3_ACTSA

Clear to send input

EDSADC_DSDIN0A

Digital datastream input, channel 0

ASCLIN4_ARXA

Receive input

SENT_SENT11B

Receive input channel 11

EVADC_G9CH0

AI

EVADC_FC2CH0

Analog input channel 0, group 9

Analog input FC channel 2

P00.12

O0

General-purpose output

GTM_TOUT21

O1

GTM muxed output

—

O2

Reserved

—

O3

Reserved

—

O4

Reserved

—

O5

Reserved

—

O6

Reserved

CCU61_COUT63

O7

T13 PWM channel 63

IOM_MON1_7

Monitor input 1

IOM_REF1_7

Reference input 1

Data Sheet

25

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-2

Port 01 Functions

Ball

Symbol

Ctrl.

Buffer

Type

Function

G5

P01.3

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN5_2

GTM_TIM2_IN0_14

GTM_TIM0_IN5_8

QSPI3_SLSIB

G4

Mux input channel 5 of TIM module 4

Mux input channel 0 of TIM module 2

Mux input channel 5 of TIM module 0

Slave select input

EVADC_G9CH14

AI

Analog input channel 14, group 9

P01.3

O0

General-purpose output

GTM_TOUT111

O1

GTM muxed output

—

O2

Reserved

—

O3

Reserved

QSPI3_SLSO9

O4

Master slave select output

CAN01_TXD

O5

CAN transmit output node 1

IOM_MON2_6

Monitor input 2

IOM_REF2_6

Reference input 2

—

O6

Reserved

—

O7

Reserved

P01.4

I

GTM_TIM4_IN6_2

GTM_TIM2_IN1_14

GTM_TIM0_IN6_8

CAN01_RXDC

SLOW /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 6 of TIM module 4

Mux input channel 1 of TIM module 2

Mux input channel 6 of TIM module 0

CAN receive input node 1

EVADC_G9CH13

AI

Analog input channel 13, group 9

P01.4

O0

General-purpose output

GTM_TOUT112

O1

GTM muxed output

—

O2

Reserved

ASCLIN9_ASLSO

O3

Slave select signal output

QSPI3_SLSO10

O4

Master slave select output

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

26

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-2

Port 01 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

H5

P01.5

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM5_IN3_2

GTM_TIM2_IN3_7

GTM_TIM2_IN2_7

H4

Mux input channel 3 of TIM module 5

Mux input channel 3 of TIM module 2

Mux input channel 2 of TIM module 2

QSPI3_MRSTC

Master SPI data input

ASCLIN9_ARXA

Receive input

EVADC_G9CH12

AI

Analog input channel 12, group 9

P01.5

O0

General-purpose output

GTM_TOUT113

O1

GTM muxed output

—

O2

Reserved

—

O3

Reserved

QSPI3_MRST

O4

Slave SPI data output

IOM_MON2_3

Monitor input 2

IOM_REF2_3

Reference input 2

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

P01.6

I

GTM_TIM5_IN6_2

GTM_TIM5_IN5_3

GTM_TIM2_IN5_7

QSPI3_MTSRC

FAST /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 6 of TIM module 5

Mux input channel 5 of TIM module 5

Mux input channel 5 of TIM module 2

Slave SPI data input

P01.6

O0

General-purpose output

GTM_TOUT114

O1

GTM muxed output

—

O2

Reserved

ASCLIN9_ASCLK

O3

Shift clock output

QSPI3_MTSR

O4

Master SPI data output

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

27

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-2

Port 01 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

J5

P01.7

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM5_IN7_2

GTM_TIM2_IN7_7

QSPI3_SCLKC

ASCLIN9_ARXB

Mux input channel 7 of TIM module 5

Mux input channel 7 of TIM module 2

Slave SPI clock inputs

Receive input

P01.7

O0

General-purpose output

GTM_TOUT115

O1

GTM muxed output

—

O2

Reserved

ASCLIN9_ATX

O3

Transmit output

QSPI3_SCLK

O4

Master SPI clock output

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

28

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions

Ball

Symbol

Ctrl.

Buffer

Type

Function

B1

P02.0

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN0_2

GTM_TIM0_IN0_2

CCU61_CC60INB

Mux input channel 0 of TIM module 1

Mux input channel 0 of TIM module 0

T12 capture input 60

ASCLIN2_ARXG

Receive input

CCU60_CC60INA

T12 capture input 60

SCU_E_REQ3_2

ERU Channel 3 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

GTM_DTMA0_0

CDTM0_DTM4

P02.0

O0

General-purpose output

GTM_TOUT0

O1

GTM muxed output

IOM_REF0_0

ASCLIN2_ATX

Reference input 0

O2

Transmit output

IOM_MON2_14

Monitor input 2

IOM_REF2_14

Reference input 2

QSPI3_SLSO1

O3

Master slave select output

EDSADC_CGPWMN

O4

Negative carrier generator output

CAN00_TXD

O5

CAN transmit output node 0

IOM_MON2_5

Monitor input 2

IOM_REF2_5

Reference input 2

ERAY0_TXDA

O6

Transmit Channel A

CCU60_CC60

O7

T12 PWM channel 60

IOM_MON1_2

Monitor input 1

IOM_REF1_6

Reference input 1

Data Sheet

29

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

C2

P02.1

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN1_2

GTM_TIM0_IN1_2

ERAY0_RXDA2

Mux input channel 1 of TIM module 1

Mux input channel 1 of TIM module 0

Receive Channel A2

ASCLIN2_ARXB

Receive input

CAN00_RXDA

CAN receive input node 0

SCU_E_REQ2_1

ERU Channel 2 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

P02.1

O0

General-purpose output

GTM_TOUT1

O1

GTM muxed output

IOM_REF0_1

Reference input 0

QSPI4_SLSO7

O2

Master slave select output

QSPI3_SLSO2

O3

Master slave select output

EDSADC_CGPWMP

O4

Positive carrier generator output

—

O5

Reserved

—

O6

Reserved

CCU60_COUT60

O7

T12 PWM channel 60

IOM_MON1_3

Monitor input 1

IOM_REF1_3

Reference input 1

Data Sheet

30

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

C1

P02.2

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN2_2

GTM_TIM0_IN2_2

CCU61_CC61INB

Mux input channel 2 of TIM module 1

Mux input channel 2 of TIM module 0

T12 capture input 61

CCU60_CC61INA

T12 capture input 61

SENT_SENT14B

Receive input channel 14

P02.2

O0

General-purpose output

GTM_TOUT2

O1

GTM muxed output

IOM_REF0_2

ASCLIN1_ATX

Reference input 0

O2

Transmit output

IOM_MON2_13

Monitor input 2

IOM_REF2_13

Reference input 2

QSPI3_SLSO3

O3

Master slave select output

PSI5_TX0

O4

TXD outputs (send data)

IOM_MON1_14

Monitor input 1

IOM_REF1_14

Reference input 1

CAN02_TXD

O5

CAN transmit output node 2

IOM_MON2_7

Monitor input 2

IOM_REF2_7

Reference input 2

ERAY0_TXDB

O6

Transmit Channel B

CCU60_CC61

O7

T12 PWM channel 61

IOM_MON1_1

Monitor input 1

IOM_REF1_5

Reference input 1

Data Sheet

31

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

D2

P02.3

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN3_2

GTM_TIM0_IN3_2

EDSADC_DSCIN5B

Mux input channel 3 of TIM module 1

Mux input channel 3 of TIM module 0

Modulator clock input, channel 5

ERAY0_RXDB2

Receive Channel B2

CAN02_RXDB

CAN receive input node 2

ASCLIN1_ARXG

Receive input

MSC1_SDI1

Upstream assynchronous input signal

PSI5_RX0B

RXD inputs (receive data) channel 0

SENT_SENT13B

Receive input channel 13

P02.3

O0

General-purpose output

GTM_TOUT3

O1

GTM muxed output

IOM_REF0_3

Reference input 0

ASCLIN2_ASLSO

O2

Slave select signal output

QSPI3_SLSO4

O3

Master slave select output

EDSADC_DSCOUT5

O4

Modulator clock output

—

O5

Reserved

—

O6

Reserved

CCU60_COUT61

O7

T12 PWM channel 61

IOM_MON1_4

Monitor input 1

IOM_REF1_2

Reference input 1

Data Sheet

32

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

D1

P02.4

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN4_1

GTM_TIM0_IN4_1

CCU61_CC62INB

Mux input channel 4 of TIM module 1

Mux input channel 4 of TIM module 0

T12 capture input 62

EDSADC_DSDIN5B

Digital datastream input, channel 5

QSPI3_SLSIA

Slave select input

CCU60_CC62INA

T12 capture input 62

I2C0_SDAA

Serial Data Input 0

CAN11_RXDA

CAN receive input node 1

CAN0_ECTT1

External CAN time trigger input

SENT_SENT12B

Receive input channel 12

P02.4

O0

General-purpose output

GTM_TOUT4

O1

GTM muxed output

IOM_REF0_4

Reference input 0

ASCLIN2_ASCLK

O2

Shift clock output

QSPI3_SLSO0

O3

Master slave select output

PSI5S_CLK

O4

PSI5S CLK is a clock that can be used on a pin to drive

the external PHY.

I2C0_SDA

O5

Serial Data Output

ERAY0_TXENA

O6

Transmit Enable Channel A

CCU60_CC62

O7

T12 PWM channel 62

IOM_MON1_0

Monitor input 1

IOM_REF1_4

Reference input 1

Data Sheet

33

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

E2

P02.5

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN5_1

GTM_TIM0_IN5_1

EDSADC_DSCIN4B

Mux input channel 5 of TIM module 1

Mux input channel 5 of TIM module 0

Modulator clock input, channel 4

I2C0_SCLA

Serial Clock Input 0

PSI5_RX1B

RXD inputs (receive data) channel 1

PSI5S_RXB

RX data input

QSPI3_MRSTA

Master SPI data input

SENT_SENT3C

Receive input channel 3

CAN0_ECTT2

External CAN time trigger input

P02.5

O0

General-purpose output

GTM_TOUT5

O1

GTM muxed output

IOM_REF0_5

Reference input 0

CAN11_TXD

O2

CAN transmit output node 1

QSPI3_MRST

O3

Slave SPI data output

IOM_MON2_3

Monitor input 2

IOM_REF2_3

Reference input 2

EDSADC_DSCOUT4

O4

Modulator clock output

I2C0_SCL

O5

Serial Clock Output

ERAY0_TXENB

O6

Transmit Enable Channel B

CCU60_COUT62

O7

T12 PWM channel 62

IOM_MON1_5

Monitor input 1

IOM_REF1_1

Reference input 1

Data Sheet

34

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

E1

P02.6

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM3_IN0_10

GTM_TIM1_IN6_1

GTM_TIM0_IN6_1

Mux input channel 0 of TIM module 3

Mux input channel 6 of TIM module 1

Mux input channel 6 of TIM module 0

CCU60_CC60INC

T12 capture input 60

SENT_SENT2C

Receive input channel 2

EDSADC_DSDIN4B

Digital datastream input, channel 4

EDSADC_ITR5E

Trigger/Gate input, channel 5

GPT120_T3INA

Trigger/gate input of core timer T3

CCU60_CCPOS0A

Hall capture input 0

CCU61_T12HRB

External timer start 12

QSPI3_MTSRA

Slave SPI data input

P02.6

O0

General-purpose output

GTM_TOUT6

O1

GTM muxed output

IOM_REF0_6

Reference input 0

PSI5S_TX

O2

TX data output

QSPI3_MTSR

O3

Master SPI data output

PSI5_TX1

O4

TXD outputs (send data)

IOM_MON1_15

Monitor input 1

EVADC_EMUX00

O5

Control of external analog multiplexer interface 0

—

O6

Reserved

CCU60_CC60

O7

T12 PWM channel 60

IOM_MON1_2

Monitor input 1

IOM_REF1_6

Reference input 1

Data Sheet

35

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

F2

P02.7

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM3_IN1_10

GTM_TIM1_IN7_1

GTM_TIM0_IN7_1

Mux input channel 1 of TIM module 3

Mux input channel 7 of TIM module 1

Mux input channel 7 of TIM module 0

CCU60_CC61INC

T12 capture input 61

SENT_SENT1C

Receive input channel 1

EDSADC_DSCIN3B

Modulator clock input, channel 3

EDSADC_ITR4E

Trigger/Gate input, channel 4

GPT120_T3EUDA

Count direction control input of core timer T3

CCU60_CCPOS1A

Hall capture input 1

QSPI3_SCLKA

Slave SPI clock inputs

CCU61_T13HRB

External timer start 13

P02.7

O0

General-purpose output

GTM_TOUT7

O1

GTM muxed output

IOM_REF0_7

Reference input 0

—

O2

Reserved

QSPI3_SCLK

O3

Master SPI clock output

EDSADC_DSCOUT3

O4

Modulator clock output

EVADC_EMUX01

O5

Control of external analog multiplexer interface 0

SENT_SPC1

O6

Transmit output

CCU60_CC61

O7

T12 PWM channel 61

IOM_MON1_1

Monitor input 1

IOM_REF1_5

Reference input 1

Data Sheet

36

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

F1

P02.8

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM3_IN2_10

GTM_TIM3_IN0_2

GTM_TIM2_IN0_2

Mux input channel 2 of TIM module 3

Mux input channel 0 of TIM module 3

Mux input channel 0 of TIM module 2

CCU60_CC62INC

T12 capture input 62

SENT_SENT0C

Receive input channel 0

CCU60_CCPOS2A

Hall capture input 2

EDSADC_DSDIN3B

Digital datastream input, channel 3

EDSADC_ITR3E

Trigger/Gate input, channel 3

GPT120_T4INA

Trigger/gate input of timer T4

CCU61_T12HRC

External timer start 12

CCU61_T13HRC

External timer start 13

GTM_DTMA0_1

CDTM0_DTM4

P02.8

O0

General-purpose output

GTM_TOUT8

O1

GTM muxed output

IOM_REF0_8

Reference input 0

QSPI3_SLSO5

O2

Master slave select output

ASCLIN8_ASCLK

O3

Shift clock output

—

O4

Reserved

EVADC_EMUX02

O5

Control of external analog multiplexer interface 0

GETH_MDC

O6

MDIO clock

CCU60_CC62

O7

T12 PWM channel 62

IOM_MON1_0

Monitor input 1

IOM_REF1_4

Reference input 1

Data Sheet

37

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

E4

P02.9

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN2_2

GTM_TIM3_IN3_10

GTM_TIM0_IN2_10

ASCLIN8_ARXA

F5

Mux input channel 2 of TIM module 4

Mux input channel 3 of TIM module 3

Mux input channel 2 of TIM module 0

Receive input

P02.9

O0

General-purpose output

GTM_TOUT116

O1

GTM muxed output

ASCLIN2_ATX

O2

Transmit output

IOM_MON2_14

Monitor input 2

IOM_REF2_14

Reference input 2

ASCLIN8_ATX

O3

Transmit output

—

O4

Reserved

CAN01_TXD

O5

CAN transmit output node 1

IOM_MON2_6

Monitor input 2

IOM_REF2_6

Reference input 2

—

O6

Reserved

—

O7

Reserved

P02.10

I

GTM_TIM4_IN3_2

GTM_TIM3_IN4_11

GTM_TIM0_IN3_10

SLOW /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 3 of TIM module 4

Mux input channel 4 of TIM module 3

Mux input channel 3 of TIM module 0

ASCLIN2_ARXC

Receive input

CAN01_RXDE

CAN receive input node 1

ASCLIN8_ARXB

Receive input

P02.10

O0

General-purpose output

GTM_TOUT117

O1

GTM muxed output

—

O2

Reserved

—

O3

Reserved

—

O4

Reserved

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

38

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-3

Port 02 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

F4

P02.11

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN4_3

GTM_TIM3_IN5_12

GTM_TIM0_IN7_7

Mux input channel 4 of TIM module 4

Mux input channel 5 of TIM module 3

Mux input channel 7 of TIM module 0

EVADC_G9CH15

AI

Analog input channel 15, group 9

P02.11

O0

General-purpose output

GTM_TOUT118

O1

GTM muxed output

—

O2

Reserved

ASCLIN8_ASLSO

O3

Slave select signal output

—

O4

Reserved

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Table 2-4

Port 10 Functions

Ball

Symbol

Ctrl.

Buffer

Type

Function

A7

P10.0

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN0_12

GTM_TIM1_IN4_2

GTM_TIM0_IN4_2

Mux input channel 0 of TIM module 4

Mux input channel 4 of TIM module 1

Mux input channel 4 of TIM module 0

GPT120_T6EUDB

Count direction control input of core timer T6

ASCLIN11_ARXA

Receive input

GETH_RXERC

Receive Error MII

P10.0

O0

General-purpose output

GTM_TOUT102

O1

GTM muxed output

ASCLIN11_ATX

O2

Transmit output

QSPI1_SLSO10

O3

Master slave select output

—

O4

Reserved

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

39

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-4

Port 10 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

B7

P10.1

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN4_12

GTM_TIM1_IN1_3

GTM_TIM0_IN1_3

A5

Mux input channel 4 of TIM module 4

Mux input channel 1 of TIM module 1

Mux input channel 1 of TIM module 0

GPT120_T5EUDB

Count direction control input of timer T5

QSPI1_MRSTA

Master SPI data input

GTM_DTMT0_1

CDTM0_DTM0

P10.1

O0

General-purpose output

GTM_TOUT103

O1

GTM muxed output

QSPI1_MTSR

O2

Master SPI data output

QSPI1_MRST

O3

Slave SPI data output

IOM_MON2_1

Monitor input 2

IOM_REF2_1

Reference input 2

MSC0_EN1

O4

Chip Select

EVADC_FC1BFLOUT

O5

Boundary flag output, FC channel 1

—

O6

Reserved

—

O7

Reserved

P10.2

I

GTM_TIM4_IN5_12

GTM_TIM1_IN2_3

GTM_TIM0_IN2_3

FAST /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 5 of TIM module 4

Mux input channel 2 of TIM module 1

Mux input channel 2 of TIM module 0

CAN02_RXDE

CAN receive input node 2

MSC0_SDI1

Upstream assynchronous input signal

QSPI1_SCLKA

Slave SPI clock inputs

GPT120_T6INB

Trigger/gate input of core timer T6

SCU_E_REQ2_0

ERU Channel 2 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

GTM_DTMT2_2

CDTM2_DTM0

P10.2

O0

General-purpose output

GTM_TOUT104

O1

GTM muxed output

IOM_MON2_9

Monitor input 2

—

O2

Reserved

QSPI1_SCLK

O3

Master SPI clock output

MSC0_EN0

O4

Chip Select

EVADC_FC3BFLOUT

O5

Boundary flag output, FC channel 3

—

O6

Reserved

—

O7

Reserved

Data Sheet

40

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-4

Port 10 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

A6

P10.3

I

FAST /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN6_10

GTM_TIM1_IN3_3

GTM_TIM0_IN3_3

Mux input channel 3 of TIM module 1

Mux input channel 3 of TIM module 0

QSPI1_MTSRA

Slave SPI data input

SCU_E_REQ3_0

ERU Channel 3 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

GPT120_T5INB

Trigger/gate input of timer T5

P10.3

O0

General-purpose output

GTM_TOUT105

O1

GTM muxed output

IOM_MON2_10

B6

Mux input channel 6 of TIM module 4

Monitor input 2

—

O2

Reserved

QSPI1_MTSR

O3

Master SPI data output

MSC0_EN0

O4

Chip Select

—

O5

Reserved

CAN02_TXD

O6

CAN transmit output node 2

IOM_MON2_7

Monitor input 2

IOM_REF2_7

Reference input 2

—

O7

P10.4

I

GTM_TIM4_IN7_3

GTM_TIM1_IN6_2

GTM_TIM0_IN6_2

Reserved

FAST /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 7 of TIM module 4

Mux input channel 6 of TIM module 1

Mux input channel 6 of TIM module 0

QSPI1_MTSRC

Slave SPI data input

CCU60_CCPOS0C

Hall capture input 0

GPT120_T3INB

Trigger/gate input of core timer T3

ASCLIN11_ARXB

Receive input

P10.4

O0

General-purpose output

GTM_TOUT106

O1

GTM muxed output

IOM_MON2_11

Monitor input 2

—

O2

Reserved

QSPI1_SLSO8

O3

Master slave select output

QSPI1_MTSR

O4

Master SPI data output

MSC0_EN0

O5

Chip Select

—

O6

Reserved

—

O7

Reserved

Data Sheet

41

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-4

Port 10 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

B5

P10.5

I

SLOW /

PU2 /

VEXT /

ES

General-purpose input

GTM_TIM4_IN3_13

GTM_TIM1_IN2_4

GTM_TIM0_IN2_4

Mux input channel 2 of TIM module 1

Mux input channel 2 of TIM module 0

PMS_HWCFG4IN

HWCFG4 pin input

MSC0_INJ1

Injection signal from port

P10.5

O0

General-purpose output

GTM_TOUT107

O1

GTM muxed output

IOM_REF2_9

ASCLIN2_ATX

A4

Mux input channel 3 of TIM module 4

Reference input 2

O2

Transmit output

IOM_MON2_14

Monitor input 2

IOM_REF2_14

Reference input 2

QSPI3_SLSO8

O3

Master slave select output

QSPI1_SLSO9

O4

Master slave select output

GPT120_T6OUT

O5

External output for overflow/underflow detection of

core timer T6

ASCLIN2_ASLSO

O6

Slave select signal output

—

O7

Reserved

P10.6

I

GTM_TIM4_IN2_13

GTM_TIM1_IN3_4

GTM_TIM0_IN3_4

SLOW /

PU2 /

VEXT /

ES

General-purpose input

Mux input channel 2 of TIM module 4

Mux input channel 3 of TIM module 1

Mux input channel 3 of TIM module 0

ASCLIN2_ARXD

Receive input

QSPI3_MTSRB

Slave SPI data input

PMS_HWCFG5IN

HWCFG5 pin input

P10.6

O0

General-purpose output

GTM_TOUT108

O1

GTM muxed output

IOM_REF2_10

Reference input 2

ASCLIN2_ASCLK

O2

Shift clock output

QSPI3_MTSR

O3

Master SPI data output

GPT120_T3OUT

O4

External output for overflow/underflow detection of

core timer T3

—

O5

Reserved

QSPI1_MRST

O6

Slave SPI data output

IOM_MON2_1

Monitor input 2

IOM_REF2_1

Reference input 2

—

Data Sheet

O7

Reserved

42

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-4

Port 10 Functions (cont’d)

Ball

Symbol

Ctrl.

Buffer

Type

Function

A3

P10.7

I

SLOW /

PU1 /

VEXT /

ES

General-purpose input

GTM_TIM1_IN0_3

GTM_TIM0_IN0_3

GPT120_T3EUDB

Mux input channel 0 of TIM module 0

Count direction control input of core timer T3

ASCLIN2_ACTSA

Clear to send input

QSPI3_MRSTB

Master SPI data input

SCU_E_REQ0_2

ERU Channel 0 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

CCU60_CCPOS1C

Hall capture input 1

P10.7

O0

General-purpose output

GTM_TOUT109

O1

GTM muxed output

IOM_REF2_11

B4

Mux input channel 0 of TIM module 1

Reference input 2

—

O2

Reserved

QSPI3_MRST

O3

Slave SPI data output

IOM_MON2_3

Monitor input 2

IOM_REF2_3

Reference input 2

—

O4

Reserved

—

O5

Reserved

CAN12_TXD

O6

CAN transmit output node 2

—

O7

Reserved

P10.8

I

GTM_TIM4_IN0_13

GTM_TIM1_IN5_2

GTM_TIM0_IN5_2

SLOW /

PU1 /

VEXT /

ES

General-purpose input

Mux input channel 0 of TIM module 4

Mux input channel 5 of TIM module 1

Mux input channel 5 of TIM module 0

CAN12_RXDB

CAN receive input node 2

GPT120_T4INB

Trigger/gate input of timer T4

QSPI3_SCLKB

Slave SPI clock inputs

SCU_E_REQ1_2

ERU Channel 1 inputs 0 to 5 (0 is the LSB and 5 is the

MSB)

CCU60_CCPOS2C

Hall capture input 2

P10.8

O0

General-purpose output

GTM_TOUT110

O1

GTM muxed output

ASCLIN2_ARTS

O2

Ready to send output

QSPI3_SCLK

O3

Master SPI clock output

—

O4

Reserved

—

O5

Reserved

—

O6

Reserved

—

O7

Reserved

Data Sheet

43

OPEN MARKET VERSION

V 1.1, 2021-03

�TC37x AA-Step

TC37x Pin Definition and Functions LFBGA-292 Package Pinning of TC37x TP

Table 2-5

Port 11 Functions

Ball

Symbol

Ctrl.

Buffer

Type

Function

E10

P11.0

I

RFAST /

PU1 /

VFLEX /

ES

General-purpose input

GTM_TIM4_IN0_4

GTM_TIM2_IN0_7

ASCLIN3_ARXB

GTM_DTMA2_1

E9

Mux input channel 0 of TIM module 4

Mux input channel 0 of TIM module 2

Receive input

CDTM2_DTM4

P11.0

O0

General-purpose output

GTM_TOUT119

O1

GTM muxed output

ASCLIN3_ATX

O2

Transmit output

IOM_MON2_15

Monitor input 2

IOM_REF2_15

Reference input 2

—