2:1 1.8V PCIe Gen1-2-3 Clock Mux with

Zo=100ohms

9DMV0141

DATASHEET

Description

Features

The 9DMV0141 is a member of IDT's SOC-Friendly 1.8V

Very-Low-Power (VLP) PCIe Gen1-2-3 family. It has

integrated output terminations providing Zo=100 for direct

connection to 100 transmission lines. The output has an

OE# pin for optimal system control and power management.

The part provides asynchronous or glitch-free switching

modes.

• LP-HCSL output w/integrated terminations; saves 4

•

•

•

•

•

Typical Application

2:1 PCIe Gen1-2-3 Clock Multiplexer

•

•

Output Features

• 1 -Low-Power (LP) HCSL DIF pair w/ZO=100

•

Key Specifications

resistors compared to standard HCSL output

1.8V operation; 12mW typical power consumption

Selectable asynchronous or glitch-free switching; allows

the mux to be selected at power up even if both inputs are

not running, then transition to glitch-free switching mode

Spread Spectrum Compatible; supports EMI reduction

OE# pins; support DIF power management

HCSL differential inputs; can be driven by common clock

sources

1MHz to 200MHz operating frequency

Configuration can be accomplished with strapping pins;

SMBus interface not required for device control

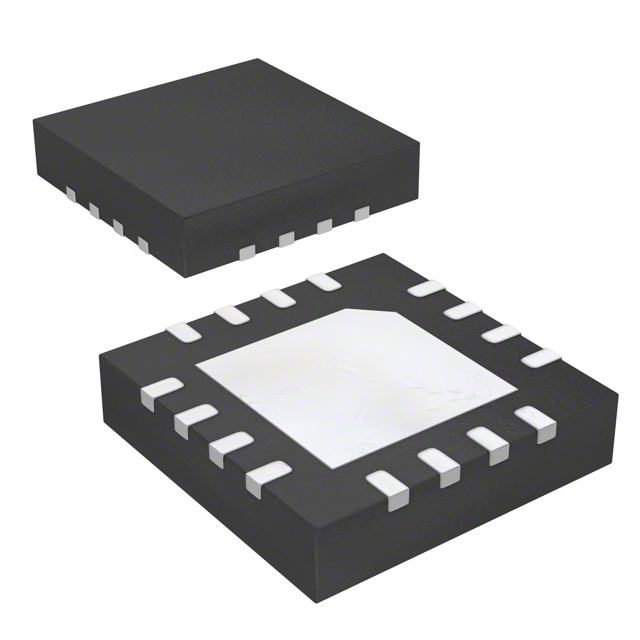

Space saving 16-pin 3x3mm VFQFPN; minimal board

space

• DIF additive cycle-to-cycle jitter 200 mV

DIF_IN input

4

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

4

AUGUST 15, 2017

�9DMV0141 DATASHEET

Electrical Characteristics–Clock Input Parameters

TA = TAMB, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

Input High Voltage - DIF_IN

VIHDIF

Input Low Voltage - DIF_IN

VILDIF

Input Common Mode

Voltage - DIF_IN

Input Amplitude - DIF_IN

Input Slew Rate - DIF_IN

Input Leakage Current

Input Duty Cycle

Input Jitter - Cycle to Cycle

1

CONDITIONS

Differential inputs

(single-ended measurement)

Differential inputs

(single-ended measurement)

MIN

TYP

MAX

UNITS NOTES

300

750

1150

mV

1

VSS - 300

0

300

mV

1

VCOM

Common Mode Input Voltage

200

725

mV

1

VSWING

dv/dt

IIN

dtin

J DIFIn

Peak to Peak value (VIHDIF - VILDIF)

Measured differentially

VIN = VDD , VIN = GND

Measurement from differential waveform

Differential Measurement

300

0.35

-5

45

0

1450

8

5

55

150

mV

V/ns

uA

%

ps

1

1,2

50

1

1

Guaranteed by design and characterization, not 100% tested in production.

Slew rate measured through +/-75mV window centered around differential zero

2

Electrical Characteristics–DIF Low-Power HCSL Outputs

TA = TAMB, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX UNITS NOTES

Slew rate

Slew rate matching

Trf

ΔTrf

Scope averaging on

Slew rate matching, Scope averaging on

1.8

3.0

3

4.2

20

Voltage High

VHIGH

660

783

850

Voltage Low

VLOW

Statistical measurement on single-ended signal

using oscilloscope math function. (Scope

averaging on)

-150

26

150

Max Voltage

Min Voltage

Vswing

Crossing Voltage (abs)

Crossing Voltage (var)

Vmax

Vmin

Vswing

Vcross_abs

Δ-Vcross

Measurement on single ended signal using

absolute value. (Scope averaging off)

Scope averaging off

Scope averaging off

Scope averaging off

790

9

1514

393

12

1150

-300

300

250

V/ns

%

1,2,3

1,2,4

mV

550

140

mV

mV

mV

mV

1,2

1,5

1,6

1

Guaranteed by design and characterization, not 100% tested in production.

Measured from differential waveform

2

3

Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around

differential 0V.

4

Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on

the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the

oscilloscope is to use for the edge rate calculations.

5

Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising

edge (i.e. Clock rising and Clock# falling).

6

The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross_min/max (Vcross

absolute) allowed. The intent is to limit Vcross induced modulation by setting ∆-Vcross to be smaller than Vcross absolute.

Electrical Characteristics–Current Consumption

TA = TAMB, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Operating Supply Current

IDDOP

VDD rails, All outputs active @100MHz

7.9

12

mA

Disable Current

IDDDIS

VDD rails, All outputs disabled Low/Low

1.5

2.5

mA

NOTES

2

1

Guaranteed by design and characterization, not 100% tested in production.

2

Input clock stopped after outputs have parked Low/Low.

AUGUST 15, 2017

5

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

�9DMV0141 DATASHEET

Electrical Characteristics–Output Duty Cycle, Jitter, Skew and PLL Characteristics

TA = TAMB, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

NOTES

Duty Cycle Distortion

Skew, Input to Output

Jitter, Cycle to cycle

tDCD

Measured differentially, @100MHz

VT = 50%

Additive Jitter

-1

1853

-0.12

2409

0.1

1

3132

5

%

ps

ps

1,3

1

1,2

tpdBYP

tjcyc-cyc

1

Guaranteed by design and characterization, not 100% tested in production.

Measured from differential waveform

3

Duty cycle distortion is the difference in duty cycle between the output and the input clock.

2

Electrical Characteristics–Phase Jitter Parameters

TA = TAMB, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

PARAMETER

SYMBOL

CONDITIONS

tjphPCIeG1

PCIe Gen 1

tjphPCIeG2

Additive Phase Jitter,

Bypass Mode

tjphPCIeG3

tjph125M0

tjph125M1

MIN

PCIe Gen 2 Lo Band

10kHz < f < 1.5MHz

PCIe Gen 2 High Band

1.5MHz < f < Nyquist (50MHz)

PCIe Gen 3

(PLL BW of 2-4 or 2-5MHz, CDR = 10MHz)

125MHz, 1.5MHz to 10MHz, -20dB/decade

rollover < 1.5MHz, -40db/decade rolloff > 10MHz

125MHz, 12KHz to 20MHz, -20dB/decade

rollover < 12kHz, -40db/decade rolloff > 20MHz

INDUSTRY

LIMIT

UNITS

TYP

MAX

1.3

5

N/A

0.1

0.3

N/A

0.1

0.2

N/A

0.065

0.1

N/A

284

350

N/A

420

500

N/A

Notes

ps (p-p) 1,2,3,5

ps

(rms)

ps

(rms)

ps

(rms)

fs

(rms)

fs

(rms)

1,2,3,4

,5

1,2,3,4

1,2,3,4

1,6

1,6

1

Guaranteed by design and characterization, not 100% tested in production.

See http://www.pcisig.com for complete specs

2

3

Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

4

For RMS figures, additive jitter is calculated by solving the following equation: Additive jitter = SQRT[(total jitter)^2 - (input jitter)^2]

Driven by 9FGV0831 or equivalent

Driven by Rohde & Schwartz SMA100

5

6

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

6

AUGUST 15, 2017

�9DMV0141 DATASHEET

Marking Diagram

XXX

YYWW

41AIL

Notes:

1. “XXX” is the last 3 characters of the lot number.

2. “YYWW” is the last two digits of the year and week that the part was assembled.

3. Line 3: truncated part number

4. “L” denotes RoHS compliant package.

5. “I” denotes industrial temperature grade.

Thermal Characteristics

PARAMETER

SYMBOL

Thermal Resistance

θJC

θJb

θJA0

θJA1

θJA3

θJA5

TYP

VALUE

Junction to Case

66

Junction to Base

5

Junction to Air, still air

63

NLG16

Junction to Air, 1 m/s air flow

56

Junction to Air, 3 m/s air flow

51

Junction to Air, 5 m/s air flow

49

CONDITIONS

PKG

UNITS NOTES

°C/W

°C/W

°C/W

°C/W

°C/W

°C/W

1

1

1

1

1

1

1

ePad soldered to board

AUGUST 15, 2017

7

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

�9DMV0141 DATASHEET

Package Outline and Dimensions (NLG16P2)

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

8

AUGUST 15, 2017

�9DMV0141 DATASHEET

Package Outline and Dimensions (NLG16P2), cont.

AUGUST 15, 2017

9

2:1 1.8V PCIE GEN1-2-3 CLOCK MUX WITH ZO=100OHMS

�Ordering Information

Part / Order Number Shipping Packaging

9DMV0141AKILF

Trays

9DMV0141AKILFT

Tape and Reel

Package

16-pin VFQFPN

16-pin VFQFPN

Temperature

-40 to +85° C

-40 to +85° C

“LF” to the suffix denotes Pb-Free configuration, RoHS compliant.

“A” is the device revision designator (will not correlate with the datasheet revision).

Revision History

Rev.

A

B

C

D

Initiator Issue Date Description

1. Update front page text and electrical tables with char data.

RDW

9/29/2014 2. Update pinout diagram with note about package paddle.

3. Move to final.

RDW

1/26/2015 Updated package drawing to the latest NLG16 document.

RDW

5/11/2007 Updated package drawing to the latest NLG16 document.

RDW

8/15/2017 Updated package drawing to NLG16P2 document.

Page #

Various

8

8,9

8,9

Corporate Headquarters

Sales

Tech Support

6024 Silver Creek Valley Road

San Jose, CA 95138 USA

www.IDT.com

1-800-345-7015 or 408-284-8200

Fax: 408-284-2775

www.IDT.com/go/sales

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as “IDT”) reserve the right to modify the products and/or specifications described herein at any time, without

notice, at IDT’s sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when

installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products

for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under

intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably

expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of

IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc.. All rights reserved.

9DMV0141 AUGUST 15, 2017

10

©2017 Integrated Device Technology, Inc.

�16-VFQFPN Package Outline Drawing

3.0 x 3.0 x 0.9 mm, 0.5mm Pitch, 1.70 x 1.70 mm Epad

NL/NLG16P2, PSC-4169-02, Rev 05, Page 1

�16-VFQFPN Package Outline Drawing

3.0 x 3.0 x 0.9 mm, 0.5mm Pitch, 1.70 x 1.70 mm Epad

NL/NLG16P2, PSC-4169-02, Rev 05, Page 2

Package Revision History

Description

Date Created

Rev No.

Oct 25, 2017

Rev 04 Remove Bookmak at Pdf Format & Update Thickness Tolerance

Jan 18, 2018

Rev 05

Change QFN to VFQFPN

�IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES (“RENESAS”) PROVIDES TECHNICAL

SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING

REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND

OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED,

INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A

PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible

for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3)

ensuring your application meets applicable standards, and any other safety, security, or other requirements. These

resources are subject to change without notice. Renesas grants you permission to use these resources only for

development of an application that uses Renesas products. Other reproduction or use of these resources is strictly

prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property.

Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims,

damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject

to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources

expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

Corporate Headquarters

Contact Information

TOYOSU FORESIA, 3-2-24 Toyosu,

Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

For further information on a product, technology, the most

up-to-date version of a document, or your nearest sales

office, please visit:

www.renesas.com/contact/

Trademarks

Renesas and the Renesas logo are trademarks of Renesas

Electronics Corporation. All trademarks and registered

trademarks are the property of their respective owners.

© 2020 Renesas Electronics Corporation. All rights reserved.

�