RT1731

Cable ID for USB Type-C Cables

Features

General Description

The RT1731 is Electronically-Marked ID cables IC for

both passive and active full-featured USB Type-C cable

controller complies with USB type-C and Power

Delivery application, the Electronically-Marked ID

cables support USB Power Delivery Structured VDM

Discover Identity command directed to SOP’. With

Electrically-Marked Cable ID, the DFP host can

determine the characteristics of the cable, e.g. its

current carrying capability, its performance, and vendor

identification, the RT1731 features VBUS short

protection on VCONN and CCIN to avoid pin short

when VBUS voltage rises above 20V after PD

communication is complete.

The RT1731 is available in WDFN-8L 2x2 and

WL-CSP-8B 0.96x1.64 (BSC) packages.

Support I2C Bus for Programming VDM Data

Power

Support 3V to 5.5V Operation on

VCON1/VCON2 Pin

Protection

HV Protection of VCON1/VCON2/CCIN

Package

WDFN-8L 2x2

RT1731

Lead Plating System

G : Green (Halogen Free and Pb Free)

(WDFN Only)

Write Protect on Multi One-Time Programmable

(OTP) Memory

Ordering Information

Package Type

QW : WDFN-8L 2x2 (W-Type)

WSC : WL-CSP-8B 0.96x1.64 (BSC)

Type-C Support/PD Support

Support SOP’ and SOP’’ Communication

Support Host Authentication

Support Additional Modal Operation

Advantage

Embedded Both Side RA Resistor

Embedded Both Side ISO Diode

Support Multi-Time Writable Memory to Store

VDM Data

Support Custom Structured VDM Writing Over

CC Pin

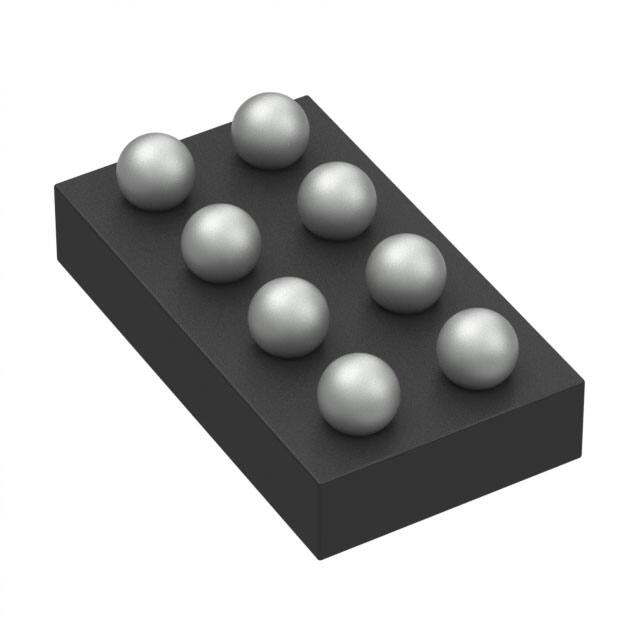

WL-CSP-8B 0.96x1.64 (BSC)

Applications

Note :

USB Full-Featured Type-C Cables

Type-C Active Cable

Richtek products are :

Type-C Passive Cable

RoHS compliant and compatible with the current

requirements of IPC/JEDEC J-STD-020.

Suitable for use in SnPb or Pb-free soldering

processes.

Simplified Application Circuit

CC

VCONN1

VCONN2

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

RT1731

VCON1

VCON2

CCIN

GND

NC

SCL

NC

SDA

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

1

�RT1731

Marking Information

RT1731GQW

4TW

RT1731WSC

4T : Product Code

W : Date Code

72W

72 : Product Code

W : Date Code

Pin Configuration

(TOP VIEW)

VCON1

A1

A2

VCON2

CCIN

B1

B2

SCL

NC

NC

C1

C2

SDA

NC

NC

D1

D2

GND

1

8

VCON1

GND

2

7

CCIN

SCL

3

6

SDA

4

5

NC

VCON2

9

WL-CSP-8B 0.96x1.64 (BSC)

WDFN-8L 2x2

Functional Pin Description

Pin No.

Pin Name

Pin Function

WDFN-8L 2x2

WL-CSP-8B

0.96x1.64 (BSC)

1

A2

VCON2

The power is input pin supplied from VCONN with resistor RA

termination and has high voltage protection at 22V.

2

D2

GND

Ground pin.

3

B2

SCL

This pin is only used for debug. No internal connection.

(Recommend to connect to GND)

4

C2

SDA

This pin is only used for debug. No internal connection.

(Recommend to connect to GND)

5, 6

C1, D1

NC

No internal connection. (Recommend to connect to GND)

7

B1

CCIN

The configuration channel pin used in the discovery,

configuration and management of connections, includes high

voltage protection at 22V.

8

A1

VCON1

The power is input pin supplied from VCONN with resistor RA

termination and has high voltage protection at 22V.

9

(Exposed Pad)

--

NC

No internal connection. The exposed pad must be soldered to a

large PCB and connected to GND for maximum power

dissipation.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

2

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Functional Block Diagram

SCL

SDA

2

M-OTP

I C Controller

Internal Bus

Cable Policy

Engine

MUX Control

Register Block

Protocol Layer

Detection

Voltage

Regulator

USB PD Physical

Layer

VCON1

CCIN

RA

RA

GND

VCON2

Operation

SOP’ and SOP’’ Communication

A Cable Plug capable of SOP’ Communication shall

only detect and communicate with packets starting with

SOP’. The eMarker in a Passive Cable shall be capable

of SOP’ Communication only after VCONN is on. Or

the eMarker in an Active Cable shall be capable of

SOP’ Communication only after VCONN is on and

SOP’’ Controller is not present.

40Gbps Model operation. There are several

SVID/MODE configuration setting to supports up to 3

kinds of Modal operation (40Gbps Modal Operation

included). Flexibility is retained for new applications in

the feature.

PD 3.0 Compliance

A Cable Plug capable of SOP’’ Communication shall

have a SOP’ Communication capability in the other

The RT1731 supports PD3.0 Get_Status capability.

Customized response above will be returned. The

RT1731 also support Active Cable VDO and Active

Cable VDO2 response when product is configured as

Cable Plug. No cable shall only support SOP’’

Communication. A Cable Plug to which SOP’’

PD3.0, Active Cable VDO version = 1.2 and act as

Active Cable.

Communication is assigned shall only detect and

communicate with packets starting with SOP’’. The

eMarker in an Active Cable with SOP’’ Controller

present will support SOP’ communication in one Cable

Plug and SOP’’ communication in the other Cable Plug.

The term Cable Plug in the SOP’ Communication and

SOP’’ Communication case is used to represent a

logical entity (RT1731) in the cable which is capable of

PD Communication.

PD Modal Operation

The RT1731 supports PD Model operation when the

feature of Mode Enter/Exit process is specified, e.g.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

Proprietary Authentication

Proprietary

Authentication

is

supported

with

cooperating Device, TA, etc., that need certain

authentication before enabling proprietary charging or

customized function to ensure Cable Plug’s reliability

and quality.

Inter-Frame Gap Timings

The transmitter (Host command) shall drive the bus for

no longer than tEndDriveBMC after transmitting the final

bit of the Frame.

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

3

�RT1731

Cable Response (GoodCRC)

Host Command

Bus driven after

end of Frame

End of Frame

Bus driven before

Preamble

Preamble

tInterFrameGap

tEndDriveBFSK or

tStartDrive

tEndDriveBMC

Figure1. Inter-Frame Gap Timings

The GoodCRC Message shall be sent by the receiver to acknowledge that the previous Message was correctly

received (i.e. had a good CRC). The GoodCRC Message shall return the Message’s MessageID so the transmitter

can determine that the correct Message is being acknowledged. The first bit of the GoodCRC Message shall be

returned within tTransmit after receipt of the last bit of the previous Message.

BMC Encoded Start of Preamble

The transmitter may vary the start of the Preamble by tStartDrive min. When sending the Preamble, the transmitter

shall start by transmitting a low level. The receiver shall tolerate the loss of the first edge.

0

1

0

1

1UI

1UI

1UI

0

etc

1

High Impedance

(level set by Rp/Rd)

1UI

1UI

1UI

tStartDrive

Figure 2. BMC Encoded Start of Preamble

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

4

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Transmitting or Receiving BMC Encoded Frame Terminated

The end of a BMC encoded Frame with an encoded zero for which the final bit of the Frame is terminated by a high

to low transition.

Final bit

of frame

0

Preamble for

next frame

Trailing edge

of final bit

0

High Impedance

(level set by Rp/Rd)

1UI

min tHoldLowBMC

max tEndDriveBMC

tInterFrameGap

Figure 3. tInterFrameGap

Biphase Mark Coding (BMC) Signaling Scheme

Biphase Mark Coding is the physical layer Signaling Scheme for carrying USB Power Delivery Messages. This

encoding assumes a dedicated DC connection, identified as the CC wire, which is used for sending PD Messages.

Preamble

0

1

0

1

0

1

Sync-1

0

1

0

0

0

Sync-1

1

1

0

0

0

1

1

Data In

BMC

Figure 4. BMC Example

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

5

�RT1731

1UI

Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

X1 X2

X3

X4

X12

0.5UI

X14

X13

Figure 5. BMC Tx ‘ZERO’ Mask

1UI

Y9

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

X1 X2 X3

X4

X5

X6X7 X8 X9

X10

0.5UI

X11

X12

X14

X13

Figure 6. BMC Tx ‘ONE’ Mask

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

6

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Table 1. BMC Tx Mask Definition and X Values

BMC TC Mask Definition, X Values

Parameter

Symbol

Value

Unit

Left Edge of Mask

X1Tx

0.015

UI

X2Tx point

X2Tx

0.07

UI

X3Tx point

X3Tx

0.15

UI

X4Tx point

X4Tx

0.25

UI

X5Tx point

X5Tx

0.35

UI

X6Tx point

X6Tx

0.43

UI

X7Tx point

X7Tx

0.485

UI

X8Tx point

X8Tx

0.515

UI

X9Tx point

X9Tx

0.57

UI

X10Tx point

X10Tx

0.65

UI

X11Tx point

X11Tx

0.75

UI

X12Tx point

X12Tx

0.85

UI

X13Tx point

X13Tx

0.93

UI

Right Edge of Mask

X14Tx

0.985

UI

Table 2. BMC Tx Mask Definition and Y Values

BMC TC Mask Definition, Y Values

Parameter

Symbol

Typ

Unit

Lower Bound of Outer Mask

Y1Tx

0.075

V

Lower Bound of Inner Mask

Y2Tx

0.075

V

Y3Tx Point

Y3Tx

0.15

V

Y4Tx Point

Y4Tx

0.325

V

Inner Mask Vertical Midpoint

Y5Tx

0.5625

V

Y6Tx Point

Y6Tx

0.8

V

Y7Tx Point

Y7Tx

0.975

V

Y8Tx Point

Y8Tx

1.04

V

Upper Bound of Outer Mask

Y9Tx

1.2

V

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

7

�RT1731

Absolute Maximum Ratings

(Note1)

VCON1/VCON2/CCIN ----------------------------------------------------------------------------------------------- 0.3V to 22V

SCL/SDA ---------------------------------------------------------------------------------------------------------------- 0.3V to 6V

Power Dissipation, PD @ TA = 25C

WDFN-8L 2x2 ---------------------------------------------------------------------------------------------------------- 2.19W

WL-CSP-8B 0.96x1.64 (BSC) -------------------------------------------------------------------------------------- 0.93W

Package Thermal Resistance

(Note 2)

WDFN-8L 2x2, JA ---------------------------------------------------------------------------------------------------- 45.5°C/W

WDFN-8L 2x2, JC ---------------------------------------------------------------------------------------------------- 11.5°C/W

WL-CSP-8B 0.96x1.64 (BSC), JA -------------------------------------------------------------------------------- 106.5°C/W

Lead Temperature (Soldering, 10 sec.) -------------------------------------------------------------------------- 260C

Junction Temperature ------------------------------------------------------------------------------------------------ 150C

Storage Temperature Range --------------------------------------------------------------------------------------- 65C to 150C

ESD Susceptibility

(Note 3)

HBM (Human Body Model)

VCON1/VCON2/CCIN ----------------------------------------------------------------------------------------------- 8kV

Others -------------------------------------------------------------------------------------------------------------------- 2kV

Recommended Operating Conditions

(Note 4)

Supply Input Voltage ------------------------------------------------------------------------------------------------- 3V to 5.5V

Ambient Temperature Range--------------------------------------------------------------------------------------- 40C to 85C

Junction Temperature Range -------------------------------------------------------------------------------------- 40C to 125C

Electrical Characteristics

(VDD = 5V, TA = 25C, unless otherwise specified)

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

BMC Signaling

Bit rate

Maximum difference between the

bit-rate during the part of the

packet following the Preamble and

the reference bit-rate.

Time from the end of last bit of a

Frame until the start of the first bit

of the next Preamble.

Time before the start of the first bit

of the Preamble when the

transmitter shall start driving the

line.

f BitRate

VCONN = 3V to 5.5V

270

300

330

Kbps

pBitRate

VCONN = 3V to 5.5V

--

--

0.25

%

tInterFrameGap

VCONN = 3V to 5.5V

25

--

--

s

tStartDrive

VCONN = 3V to 5.5V

1

--

1

s

VCONN = 3V to 5.5V

--

--

23

s

BMC Common Normative

Time to cease driving the line after

t

the end of the last bit of the Frame. EndDriveBMC

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

8

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Parameter

Symbol

Test Conditions

Min

Typ

Max

Unit

Fall Time

tFall

VCONN = 3V to 5.5V

300

--

--

ns

Time to cease driving the line after

the final high-to-low transition

tHoldLowBMC

VCONN = 3V to 5.5V

1

--

--

s

Rise Time

tRise

VCONN = 3V to 5.5V

300

--

--

ns

Voltage Swing

vSwing

VCONN = 3V to 5.5V

1.05

1.125

1.2

V

Transmitter Output Impedance

zDriver

VCONN = 3V to 5.5V

33

--

75

Cable Termination

RA

VCONN = 3V to 5.5V

800

--

1200

Receiver Input Impedance

zBmcRx

VCONN = 3V to 5.5V

1

--

--

M

Isupply

Typical values measured

at VCONN1 or VCONN2 = 5V

--

9.5

--

mA

Isupply-by

Typical values measured

at VCONN1 or VCONN2 = 5V

--

1.6

--

mA

BMC Receiver Normative

BIST Mode

Supply Current

Stand-by Mode

Supply Current

Note 1. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These

are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in

the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect

device reliability.

Note 2. JA is measured under natural convection (still air) at TA = 25°C with the component mounted on a high

effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard. JC is measured

at the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

9

�RT1731

Typical Application Circuit

Electronically Marked Cable with VCONN connected through the cable (Passive cable application)

VBUS

VBUS

CC

VCONN

CC

VCONN

Type-C Plug

RT1731

VCON2 VCON1

CCIN

GND

SCL

SDA

Type-C Plug

NC

NC

(Exposed Pad)

GND

GND

Electronically Marked Cable with SOP’ at both ends (Passive cable application)

VBUS

VBUS

CC

CC

VCONN

Type-C Plug

VCONN

RT1731

VCON2 VCON1

CCIN

GND

SCL

NC

SDA

NC

(Exposed Pad)

RT1731

VCON2 VCON1

CCIN

GND

SCL

NC

SDA

NC

Type-C Plug

(Exposed Pad)

GND

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

10

GND

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Application Information

Start of Packet Sequence Prime (SOP’)

The SOP’ ordered set is defined as : two Sync-1

K-codes followed by two Sync-3 K-codes

K-code Number

K-code in Code Table

1

Sync-1

2

Sync-1

3

Sync-3

4

Sync-3

Communication is assigned shall only detect and

communicate with packets starting with SOP’’ and shall

Discard any other packets.

A Port needing to communicate with such a Cable Plug,

Attached between a Port Pair will be able to

communicate using packets starting with SOP’ and

SOP’’ to communicate with the Cable Plugs and

packets starting with SOP to communicate with its Port

Partner.

A Cable Plug capable of SOP’ Communications shall

only detect and communicate with packets starting with

Structured VDM

SOP’.

defines the use of bits Bit[14:0] in the Structured VDM

Header. The fields in the Structured VDM Header are

defined in Table.

A DFP or Source needing to communicate with a Cable

Plug capable of SOP’ Communications, attached

between a Port Pair will be able to communicate using

both packets starting with SOP’ to communicate with

the Cable Plug and starting with SOP to communicate

with its Port Partner. The DFP or Source shall

co-ordinate SOP and SOP’ Communication so as to

avoid collisions.

Setting the VDM Type field to 1 (Structured VDM)

The following rules apply to the use of Structured VDM

messages :

Start of Packet Sequence Double Prime (SOP’’)

The SOP’’ ordered set is defined as the following

sequence of K-codes : Sync-1, Sync-3, Sync-1, Sync-3

K-code Number

K-code in Code Table

1

Sync-1

2

Sync-3

3

Sync-1

4

Sync-3

A Cable Plug capable of SOP’’ Communication, shall

have a SOP’ Communication capability in the other

Cable Plug. No cable shall only support SOP’’

Communication. A Cable Plug to which SOP’’

Bit(s)

Structured VDMs shall only be used when an

Explicit Contract is in place with the following

exception :

Prior to establishing an Explicit Contract a Source

may issue Discover Identity messages, to a Cable

Plug using SOP’ Packets, as an Initiator.

Only the DFP shall be an Initiator of Structured

VDMs except for the Attention Command that shall

only be initiated by the UFP.

Only the UFP or a Cable Plug shall be a Responder

to Structured VDMs.

Structured VDMs shall not be initiated or responded

to under any other circumstances.

A DFP or UFP which does not support Structured

VDMs shall ignore any Structured VDMs received.

A Command sequence shall be interruptible e.g.

due to the need for a message sequence using SOP

Packets.

Field

Description

Bit[31:16]

Standard or Vendor ID (SVID) Unique 16-bit unsigned integer, assigned by the USB-IF

Bit[15]

VDM Type

1 = Structured VDM

Structured VDM Version

Version number of the structured VDM (not this specification

Version)

00b = Version 1.0 (shall not be used)

01b = Version 2.0

Values = 10, 11 are Reserved and shall not be used

Bit[14:13]

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

11

�RT1731

Bit(s)

Field

Description

Reserved

For Commands 0…15 shall be set to 0 and shall be ignored

SVID specific commands (16…31) defined by the SVID.

Object Position

For the enter mode, exit mode and attention commands

(requests/responses) :

000b = Reserved and shall not be used.

001b…110b = Index into the list of VDOs to identify the desired

Mode VDO

111b = Exit all Active Modes (equivalent of a power on reset).

Shall only be used with the exit mode command.

Commands 0…3, 7…15 :

000b

001b…111b = Reserved and shall not be used.

SVID specific commands (16…31) defined by the SVID.

Bit[7:6]

Command Type

00b = REQ (Request from initiator port)

01b = ACK (Acknowledge response from responder port)

10b = NAK (Negative acknowledge response from responder port)

11b = BUSY (Busy response from responder port)

Bit[5]

Reserved

0 : Reserved, shall not be used

Command (Note 5)

0 = Reserved, shall not be used

1 = Discover identity

2 = Discover SVIDs

3 = Discover modes

4 = Enter mode

5 = Exit mode

6 = Attention

7-15 = Reserved, shall not be used

16..31 = SVID specific commands

Bit[12:11]

Bit[10:8]

Bit[4:0]

Note 5 : In the case where a SID is used the modes are defined by a standard. When a VID is used the modes are

defined by the Vendor.

Discover Identity

The Discover Identity Command is provided to enable an Initiator (DFP) to identify its Port Partner and for an

Initiator (Source or DFP) to identify the attached Cable Plug (Responder).

The SVID in the Discover SVIDs Command shall be set to the PD SID by both the Initiator and the Responder for

this Command.

The Discover Identity Command sent back by the Responder contains an ID Header, a Cert Stat VDO and some

Type specific VDOs which depend on the Product Type. This specification defines the following Type specific

VDOs :

Header

No. of Data Objects = 4-71

VDM

Header

ID

Header

Cert Stat VDO

Product VDO

0..32 Product

Type VDO(s)

1. Only Data objects defined in this specification can be sent as part of the Discover Identity Command.

2. The following sections define the number and content of the VDOs for each Product Type.

The Number of Data Objects field in the Message Header in the Discover Identity Command NAK and BUSY

responses shall be set to 1 since they shall not contain any VDOs.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

12

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

ID Header

The ID Header contains the vendor ID corresponding to the Power Delivery Product.

Bit(s)

Description

Bit[31]

USB communications capable as USB host :

0b : Otherwise

1b : The product is capable of enumerating USB devices.

Bit[30]

USB communications capable as a USB device :

0b : Otherwise

1b : The product is capable of being enumerated as a USB device.

Bit[29:27]

Product type (cable plug) :

000b : Undefined

001b…010b : Reserved, shall not be used.

011b : Passive cable

100b : Active cable

101b…111b : Reserved, shall not be used.

Bit[26]

Modal operation supported :

0 : Otherwise

1 : The product supports modal operation.

Bit[25:16]

0 : Reserved, shall not be used

Bit[15:0]

16-bit unsigned integer. USB vendor ID

Cert Stat VDO

The Cert Stat VDO contains the Test ID (TID) allocated by USB-IF during certification.

Bit(s)

Bit[31: 0]

Description

32-bit unsigned integer, XID

Product VDO

The Product VDO contains identity information relating to the product.

Bit(s)

Description

Bit[31:16]

16-bit unsigned integer. USB Product ID

Bit[15:0]

16-bit unsigned integer. bcdDevice

PD2 Cable VDO

The Cable VDO defined in this section shall be sent when the Product Type is given as Passive or Active Cable.

Bit(s)

Field

Description

Bit[31:28]

Cable HW Version

0000b..1111b assigned by the VID owner

Bit[27:24]

Cable Firmware Version

0000b..1111b assigned by the VID owner

Bit[23:21]

VDO Version

Version number of the VDO

Values 000b, 001b, … 111b are Reserved

Reserved

0 = Reserved, shall not be used

Type-C to Type-A/B/C

00b = Type-A

01b = Type-B

10b = Type-C

11b = Captive

Bit[20]

Bit[19:18]

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

13

�RT1731

Bit(s)

Field

Description

Type-C to Plug/Receptacle

0 = Plug

1 = Receptacle (not valid when B19..18 set to

Type-C or Captive)

Cable Latency

0000b : Reserved

0001b : < 10ns (~1m)

0010b : 10ns to 20ns (~2m)

0011b : 20ns to 30ns (~3m)

0100b : 30ns to 40ns (~4m)

0101b : 40ns to 50ns (~5m)

0110b : 50ns to 60ns (~6m)

0111b : 60ns to 70ns (~7m)

1000b : 1000ns (~100m)

1001b : 2000ns (~200m)

1010b : 3000ns (~300m)

1011b ….1111b : Reserved

Includes latency of electronics in active cable

Cable Termination Type

00b = Both ends Passive, VCONN not required

01b = Both ends Passive, VCONN required

10b = One end Active, one end passive,

VCONN required

11b = Both ends Active, VCONN required

Bit[10]

SSTX1 Directionality Support

0 = Fixed

1 = Configurable

Bit[9]

SSTX2 Directionality Support

0 = Fixed

1 = Configurable

Bit[8]

SSRX1 Directionality Support

0 = Fixed

1 = Configurable

Bit[7]

SSRX2 Directionality Support

0 = Fixed

1 = Configurable

VBUS Current Handling Capability

00b = VBUS not through cable

01b = 3A

10b = 5A

11b = Reserved

Bit[4]

VBUS through cable

0 = No

1 = Yes

Bit[3]

SOP” controller present

1 = SOP” controller present

0 = No SOP” controller present

USB Super speed Signaling Support

000b = USB 2.0 only

001b = USB3.1 Gen1

010b = USB3.1 Gen1 and Gen2

011b.. 111b = Reserved

Bit[17]

Bit[16:13]

Bit[12:11]

Bit[6:5]

Bit[2:0]

PD3 Passive Cable VDO

The Cable VDO defined in this section shall be sent when the Product Type is given as Passive or Active Cable.

Bit(s)

Field

Description

Bit[31:28]

HW Version

0000b..1111b assigned by the VID owner

Bit[27:24]

Firmware Version

0000b..1111b assigned by the VID owner

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

14

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Bit(s)

Field

Description

VDO Version

Version number of the VDO (not this

specification version) :

Version 1.0 = 000b

Values 001b…111b are Reserved and shall not

be used

Reserved

0= Reserved, shall not be used

USB Type-C plug to USB

Type-C/Captive

00b = Reserved, shall not be used

01b = Reserved, shall not be used

10b = USB Type-C

11b = Captive

Reserved

0= Reserved, shall not be used

Cable Latency

0000b : Reserved, shall not be used

0001b : < 10ns (~1m)

0010b : 10ns to 20ns (~2m)

0011b : 20ns to 30ns (~3m)

0100b : 30ns to 40ns (~4m)

0101b : 40ns to 50ns (~5m)

0110b : 50ns to 60ns (~6m)

0111b : 60ns to 70ns (~7m)

1000b : 70ns (> ~7m)

1001b ….1111b : Reserved, shall not be used

Includes latency of electronics in active cable

Cable Termination Type

00b = VCONN not required. Cable plugs that

only support discover identity commands shall

set these bits to 00b.

01b = VCONN required

10b…11b = Reserved, shall not be used

Bit[10:9]

Maximum VBUS Voltage

Maximum Cable VBUS voltage :

00b = 20V

01b = 30V

10b = 40V

11b = 50V

Bit[8:7]

Reserved

00b = Reserved, shall not be used

Bit[6:5]

VBUS Current Handling Capability

00b = Reserved, shall not be used

01b = 3A

10b = 5A

11b = Reserved, shall not be used

Bit[4:3]

Reserved

00b = Reserved, shall not be used

USB Super speed Signaling Support

000b = USB 2.0 only, no Super-Speed support

001b = USB 3.1 Gen1

010b = USB 3.1 Gen1 and Gen2

011b…111b = Reserved, shall not be used

See USB Type-C 1.2 for definitions

Bit[23:21]

Bit[20]

Bit[19:18]

Bit[17]

Bit[16:13]

Bit[12:11]

Bit[2:0]

PD3 Active Cable VDO

Bit(s)

Field

Description

Bit[31:28]

HW Version

0000b..1111b assigned by the VID owner

Bit[27:24]

Firmware Version

0000b..1111b assigned by the VID owner

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

15

�RT1731

Bit(s)

Field

Description

VDO Version

Version number of the VDO (not this

specification version) :

Version 1.0 = 000b

Version 1.1 = 001b

Values 010b…111b are Reserved and shall not

be used

Reserved

0 = Reserved, shall not be used

USB Type-C plug to USB

Type-C/Captive

00b = Reserved, shall not be used

01b = Reserved, shall not be used

10b = USB Type-C

11b = Captive

Reserved

0 = Reserved, shall not be used

Cable Latency

0000b : Reserved, shall not be used

0001b : < 10ns (~1m)

0010b : 10ns to 20ns (~2m)

0011b : 20ns to 30ns (~3m)

0100b : 30ns to 40ns (~4m)

0101b : 40ns to 50ns (~5m)

0110b : 50ns to 60ns (~6m)

0111b : 60ns to 70ns (~7m)

1000b : 70ns (> ~7m)

1001b ….1111b : Reserved, shall not be used

Includes latency of electronics in active cable

Cable Termination Type

00b…01b = Reserved, shall not be used

10b = One end Active, one end passive,

VCONN required

11b = Both ends Active, VCONN required

Bit[10:9]

Maximum VBUS Voltage

Maximum Cable VBUS voltage :

00b = 20V

01b = 30V

10b = 40V

11b = 50V

Bit[8]

SBU Supported 0 = SBUs

connections supported

0 = SBUs connections supported

1 = SBU connections are not supported

1 = SBU connections are not

supported

When SBU supported = 1 this bit shall be

Ignored.

When SBU supported = 0 :

0 = SBU is passive

1 = SBU is active

VBUS Current Handling Capability

When VBUS through cable is “No”, Reserved,

shall not be used.

When VBUS though Cable is “Yes” :

00b = Reserved, shall not be used

01b = 3A

10b = 5A

11b = Reserved, shall not be used

Bit[4]

VBUS Through Cable

0 = No

1 = Yes

Bit[3]

SOP” Controller Present

0 = No SOP” controller present

1 = SOP” controller present

Bit[23:21]

Bit[20]

Bit[19:18]

Bit[17]

Bit[16:13]

Bit[12:11]

Bit[7]

Bit[6:5]

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

16

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Bit(s)

Bit[2:0]

Field

Description

Reserved

00b = Reserved, shall not be used

PD3 Active Cable VDO2 with VDO Version = 1.2

The Cable VDO defined in this section shall be sent when the Product Type is given as Active Cable and VDO

version = 1.2.

Bit(s)

Field

Description

Bit[31:24]

Maximum Operating Temperature

The maximum internal operating temperature. It

may or may not reflect the plug’s skin

temperature.

Bit[23:16]

Shutdown Temperature

The temperature at which the cable will go into

thermal shutdown so as not to exceed the

allowable plug skin temperature.

Bit[15:6]

Reserved

0…0b = Reserved, shall not be used

Bit[5]

USB 2.0 Supported

0 = USB2.0 supported

1 = USB2.0 not supported

Bit[4]

SuperSpeed Supported

0 = USB3.1 Super-Speed supported

1 = USB3.1 Super-Speed not supported

Bit[3]

SuperSpeed Lanes Supported

0 = One Lane

1 = Two Lanes

Bit[2]

Reserved

0 = Reserved, shall not be used

SuperSpeed Signaling

00b = USB 3.1 Gen1

01b = USB 3.1 Gen2

10 to 11b = Reserved, shall not be used.

Bit[1:0]

Discover SVIDs Responder VDO

The Discover SVIDs Command is used by an Initiator to determine the SVIDs for which a Responder has Modes.

The Discover SVIDs Command is used in conjunction with the Discover Modes Command in the Discovery Process

to determine which Modes a device supports.

Bit(s)

Field

Description

Bit[31:16]

SVID n

16-bit unsigned integer, assigned by the USB-IF

or 0x0000 if this is the last VDO and the

Responder supports an even number of SVIDs.

Bit[15:0]

SVID n+1

16-bit unsigned integer, assigned by the USB-IF

or 0x0000 if this is the last VDO and the

Responder supports an odd number of SVIDs.

Discover MODES

The Discover Modes Command is used by an Initiator to determine the Modes a Responder supports for a given

SVID. The SVID in the Discover Modes Command shall be set to the SVID for which Modes are being requested by

both the Initiator and the Responder for this Command.

Header

No. of Data Objects = 4

VDM Header

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

Mode 1

Mode 2

Mode 3

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

17

�RT1731

PD3.0 Get Status

The Get_Status Message is sent by a Port to request Port Partner’s present state. The Get_Status Message may

also be sent to an Active Cable to get its present status using SOP’/SOP’’.The Active Cable shall respond by

returning a Status Message.

The Status Message shall be sent in response to a Get_Status Message. The Contents of the Status Message

depends on the target of the Get_Status Message. When sent to SOP the Status Message returns the status of the

Port’s Port Partner. When sent to SOP’ or SOP’’ the Status Message returns the status of the Active Cable’s Plug.

Extended Header

Data Size = 2

SDB

(2-byte block)

SOP’ Status Data Block

Offset

Field

Value

0

Internal Temp

Unsigned

Int

1

Flags

Bit field

Description

Active Cable Plug’s internal temperature in celcious degree.

0 = Feature not supported

1 = Temperature is less than 2 celcious degree.

2 to 255 = Temperature in celcious degree.

Bit0 = Thermal shutdown

Bit1..Bit7 = Reserved and shall be set to zero

Thermal Considerations

The junction temperature should never exceed the

absolute maximum junction temperature TJ(MAX), listed

under Absolute Maximum Ratings, to avoid permanent

damage to the device. The maximum allowable power

dissipation depends on the thermal resistance of the IC

package, the PCB layout, the rate of surrounding

airflow, and the difference between the junction and

ambient temperatures. The maximum power

dissipation can be calculated using the following

formula :

PD(MAX) = (TJ(MAX) - TA) / JA

where TJ(MAX) is the maximum junction temperature,

TA is the ambient temperature, and JA is the

junction-to-ambient thermal resistance.

effective-thermal-conductivity four-layer test board.The

maximum power dissipation at TA = 25°C can be

calculated as below :

PD(MAX) = (125°C - 25°C) / (45.5°C/W) = 2.19W for a

WDFN-8L 2x2 package.

PD(MAX) = (125°C - 25°C) / (106.5°C/W) = 0.93W for a

WL-CSP-8B 0.96x1.64 (BSC) package.

The maximum power dissipation depends on the

operating ambient temperature for the fixed TJ(MAX)

and the thermal resistance, JA. The derating curves in

Figure 7 allows the designer to see the effect of rising

ambient temperature on the maximum power

dissipation.

For continuous operation, the maximum operating

junction temperature indicated under Recommended

Operating

Conditions

is

125°C.

The

junction-to-ambient thermal resistance, JA, is highly

package dependent. For a WDFN-8L 2x2 package, the

thermal resistance, JA, is 45.5°C/W on a standard

JEDEC 51-7 high effective-thermal-conductivity

four-layer test board. For a WL-CSP-8B 0.96x1.64

(BSC) package, the thermal resistance, JA, is

106.5°C/W on a standard JEDEC 51-7 high

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

18

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Layout Considerations

Maximum Power Dissipation (W)1

2.5

Four-Layer PCB

2.0

PCB layout is very important for designing e-marked

IC (RT1731) circuits.

WDFN-8L 2x2

Connect VCON1/VCON2 pins with bypass capacitor,

1.5

and as near the pins as possible.

1.0

The exposed pad of the chip should be connected to

a large ground plane for thermal consideration.

0.5

WL-CSP-8B 0.96x1.64 (BSC)

Keep the CCIN traces away from those sensing pins

(D+, D-, SSTX+, SSTX-, SSRX+, SSRX-, SBU).

0.0

0

25

50

75

100

125

Ambient Temperature (°C)

Figure 7. Derating Curve of Maximum Power

Dissipation

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

19

�RT1731

Outline Dimension

Symbol

Dimensions In Millimeters

Dimensions In Inches

Min

Max

Min

Max

A

0.700

0.800

0.028

0.031

A1

0.000

0.050

0.000

0.002

A3

0.175

0.250

0.007

0.010

b

0.200

0.300

0.008

0.012

D

1.950

2.050

0.077

0.081

D2

1.000

1.250

0.039

0.049

E

1.950

2.050

0.077

0.081

E2

0.400

0.650

0.016

0.026

e

L

0.500

0.300

0.020

0.400

0.012

0.016

W-Type 8L DFN 2x2 Package

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

20

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Dimensions In Millimeters

Symbol

Dimensions In Inches

Min

Max

Min

Max

A

0.500

0.600

0.020

0.024

A1

0.170

0.230

0.007

0.009

b

0.240

0.300

0.009

0.012

D

1.600

1.680

0.063

0.066

D1

E

1.200

0.920

0.047

1.000

0.036

0.039

E1

0.400

0.016

e

0.400

0.016

8B WL-CSP 0 96x1 64 Package (BSC)

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

21

�RT1731

Footprint Information

Package

V/W/U/XDFN2*2-8

Footprint Dimension (mm)

Number of

Pin

P

A

B

C

D

Sx

Sy

M

8

0.50

2.80

1.20

0.80

0.30

1.30

0.70

1.80

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

www.richtek.com

22

Tolerance

±0.05

is a registered trademark of Richtek Technology Corporation.

DS1731-02

April 2021

�RT1731

Package

Number of

WL-CSP0.96x1.64-8(BSC)

Pin

8

Footprint Dimension (mm)

Type

NSMD

SMD

e

0.400

A

B

0.240

0.340

0.270

0.240

Tolerance

±0.025

Richtek Technology Corporation

14F, No. 8, Tai Yuen 1st Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should

obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume

responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and

reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may

result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

DS1731-02

April 2021

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

23

�