TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

USB Charging Port Controller and Power Switch with Load Detection

Check for Samples: TPS2543

FEATURES

DESCRIPTION

•

The TPS2543 is a USB charging port controller and

power switch with an integrated USB 2.0 high-speed

data line (D+/D–) switch. The TPS2543 provides the

electrical signatures on D+/D– to support the

following charging schemes:

• USB Battery Charging Specification 1.2;

• Chinese Telecom Standard YD/T 1591-2009;

• Divider Mode, Compliant with Apple iPod, iPhone

(1A), and iPad (2A) Mobile Digital Devices. (1)

1

•

•

•

•

•

•

•

•

•

•

•

•

D+/D– CDP/DCP Modes per USB Battery

Charging Specification 1.2

D+/D– Shorted Mode per Chinese

Telecommunication Industry Standard YD/T

1591-2009

D+/D– Divider Modes 2.0V/2.7V and 2.7/2.0V

Compliant with 1A and 2A Apple Mobile Digital

Devices

Automatic Selection of D+/D– Mode for an

Attached Device

Supports Sleep-Mode Charging and

Mouse/Keyboard (Low-Speed Only) Wake Up

Load Detection for Both Power Supply Control

in S4/S5 Charging and Port Power

Management in all Charge Modes

Compatible with USB 2.0 and 3.0 Power Switch

Requirements

73-mΩ (typ) High-Side MOSFET

Adjustable Current-Limit up to 3.0 A (typ)

Operating Range: 4.5 V to 5.5 V

Drop-In Compatible with TPS2540/40A

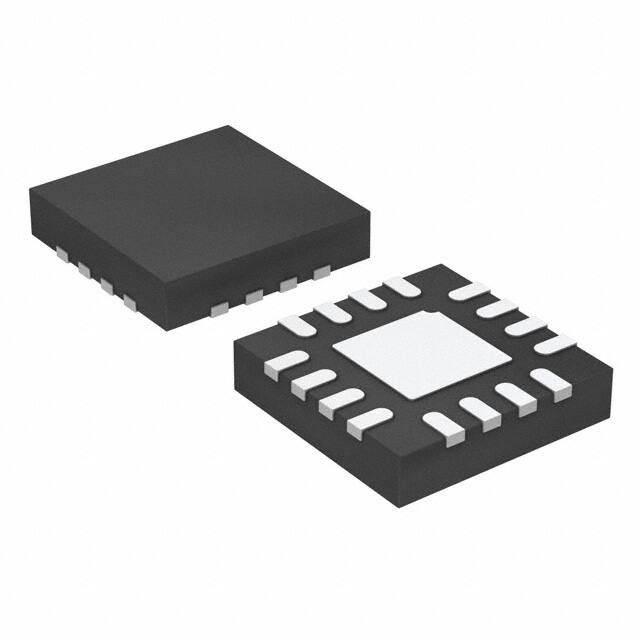

Available in 16-Pin QFN (3x3) Package

UL Listed and CB File No. E169910

The TPS2543 can be configured to automatically

select the D+/D– mode needed to charge an attached

device. The TPS2543 provides load detection via the

STATUS pin that allows for both power supply control

in S4/S5 charging and the ability to manage port

power in a multi-port application. Additionally, system

wake up (from S3) with a mouse/keyboard (low

speed only) is fully supported in the TPS2343.

The TPS2543 73-mΩ power-distribution switch is

intended for applications where heavy capacitive

loads and short-circuits are likely to be encountered.

Two programmable current thresholds provide

flexibility for setting current limits and load detect

thresholds.

APPLICATIONS

•

•

•

USB Ports (Host and Hubs)

Notebook Desktop PCs

Universal Wall Charging Adapters

(1)

Apple, iPod, iPhone, and iPad are trademarks of Apple Inc.,

registered in the U.S. and other countries.

15

14

To Portable Device à

FAULT

GND

ILIM_HI

16

ILIM_LO

TPS2543 RTE PACKAGE AND TYPICAL APPLICATION DIAGRAM

Power Bus

RSTATUS

(10 kW)

13

IN

1

12

OUT

DM_OUT

2

11

DM_IN

DP_OUT

3

10

DP_IN

ILIM_SEL

4

9

STATUS Signal

Fault Signal

6

7

8

EN

CLT1

CLT2

CLT3

Thermal Pad

5

4.5V – 5.5V

STATUS

ILIM Select

Power Switch EN

Mode Select I/O

0.1 uF

IN

OUT

TPS2543

RFAULT

(10 kW)

CUSB

ILIM_LO

ILIM_HI

STATUS

RILIM_HI

FAULT

ILIM_SEL

EN

CTL1

CTL2

CTL3

VBUS

DD+

GND

RILIM_LO

GND

DM_IN

DP_IN

DM_OUT

DP_OUT

USB

Connector

To Host Controller à

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2012, Texas Instruments Incorporated

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

ORDERING INFORMATION (1)

(1)

TA

PACKAGE

DEVICE

TOP-SIDE MARKING

–40°C to 125°C

QFN16

TPS2543

2543

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

ABSOLUTE MAXIMUM RATINGS (1)

over operating free-air temperature range, voltages are referenced to GND (unless otherwise noted)

Voltage range

IN, EN, ILIM_LO, ILIM_HI, FAULT, STATUS, ILIM_SEL,

CTL1, CTL2, CTL3, OUT

IN to OUT

LIMIT

UNIT

–0.3 to 7

V

–7 to 7

DP_IN, DM_IN, DP_OUT, DM_OUT

–0.3 to (IN + 0.3) or 5.7

Input clamp current

DP_IN, DM_IN, DP_OUT, DM_OUT

±20

mA

Continuous current in SDP or CDP

mode

DP_IN to DP_OUT or DM_IN to DM_OUT

±100

mA

Continuous current in BC1.2 DCP

mode

DP_IN to DM_IN

±50

mA

Continuous output current

OUT

Continuous output sink current

FAULT, STATUS

25

mA

Continuous output source current

ILIM_LO, ILIM_HI

Internally limited

mA

ESD rating

HBM

2

kV

HBM wrt GND and each other, DP_IN, DM_IN

8

Internally limited

CDM

Operating junction temperature, TJ

(1)

500

V

–40 to Internally limited

°C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating

Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

THERMAL INFORMATION

THERMAL METRIC (1)

TPS2543

RTE (16 PIN)

θJA

Junction-to-ambient thermal resistance

53.4

θJCtop

Junction-to-case (top) thermal resistance

51.4

θJB

Junction-to-board thermal resistance

17.2

ψJT

Junction-to-top characterization parameter

3.7

ψJB

Junction-to-board characterization parameter

20.7

θJCbot

Junction-to-case (bottom) thermal resistance

3.9

(1)

2

UNITS

°C/W

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

RECOMMENDED OPERATING CONDITIONS

voltages are referenced to GND (unless otherwise noted)

MIN

VIN

Input voltage, IN

NOM

MAX

UNIT

4.5

5.5

V

Input voltage, logic-level inputs, EN, CTL1, CTL2, CTL3, ILIM_SEL

0

5.5

V

Input voltage, data line inputs, DP_IN, DM_IN, DP_OUT, DM_OUT

0

VIN

V

VIH

High-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL

1.8

V

VIL

Low-level input voltage, EN, CTL1, CTL2, CTL3, ILIM_SEL

0.8

V

Continuous current, data line inputs, SDP or CDP mode, DP_IN to DP_OUT, DM_IN to

DM_OUT

±30

mA

±15

mA

Continuous current, data line inputs, BC1.2 DCP mode, DP_IN to DM_IN

IOUT

Continuous output current, OUT

0

2.5

A

Continuous output sink current, FAULT, STATUS

0

10

mA

RILIM_XX

Current-limit set resistors

16.9

750

kΩ

TJ

Operating virtual junction temperature

–40

125

°C

ELECTRICAL CHARACTERISTICS

Unless otherwise noted: –40 ≤ TJ ≤ 125°C, 4.5 V ≤ VIN ≤ 5.5 V, VEN = VIN, VILIM_SEL = VIN, VCTL1 = VCTL2 = VCTL3 = VIN. RFAULT =

RSTATUS = 10 kΩ, RILIM_HI = 20 kΩ, RILIM_LO = 80.6 kΩ. Positive currents are into pins. Typical values are at 25°C. All voltages

are with respect to GND.

PARAMETER

TEST CONDITIONS

MIN

TYP MAX

UNIT

POWER SWITCH

RDS(on)

On resistance

(1)

tr

OUT voltage rise time

tf

OUT voltage fall time

ton

OUT voltage turn-on time

toff

OUT voltage turn-off time

IREV

Reverse leakage current

TJ = 25°C, IOUT = 2 A

73

84

–40°C ≤ TJ ≤ 85°C, IOUT = 2 A

73

105

–40°C ≤ TJ ≤ 125°C, IOUT = 2 A

73

120

0.7

1.0

1.60

0.2

0.35

0.5

2.7

4

1.7

3

VIN = 5 V, CL = 1 µF, RL = 100 Ω (see Figure 23 and

Figure 24)

VIN = 5V, CL = 1 µF, RL = 100 Ω (see Figure 23 and

Figure 25)

VOUT = 5.5 V, VIN = VEN = 0 V, –40 ≤ TJ ≤ 85°C,

Measure IOUT

2

mΩ

ms

ms

µA

DISCHARGE

RDCHG

OUT discharge resistance

VOUT = 4 V, VEN = 0 V

400

500

630

Ω

tDCHG

OUT discharge hold time

Time VOUT < 0.7 V (see Figure 26)

205

310

450

ms

(1)

Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account

separately.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

3

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise noted: –40 ≤ TJ ≤ 125°C, 4.5 V ≤ VIN ≤ 5.5 V, VEN = VIN, VILIM_SEL = VIN, VCTL1 = VCTL2 = VCTL3 = VIN. RFAULT =

RSTATUS = 10 kΩ, RILIM_HI = 20 kΩ, RILIM_LO = 80.6 kΩ. Positive currents are into pins. Typical values are at 25°C. All voltages

are with respect to GND.

PARAMETER

TEST CONDITIONS

MIN

TYP MAX

UNIT

EN, ILIMSEL, CTL1, CTL2, CTL3 INPUTS

Input pin rising logic threshold

voltage

1

1.35

1.70

Input pin falling logic threshold

voltage

0.85

1.15

1.45

Hysteresis (2)

Input current

200

Pin voltage = 0 V or 5.5 V

–0.5

VILIM_SEL = 0 V, RILIM_LO = 210 kΩ

205

V

mV

0.5

µA

ILIMSEL CURRENT LIMIT

OUT short circuit current limit (3)

IOS

Response time to OUT shortcircuit (2)

tIOS

240

275

625

680

VILIM_SEL = 0 V, RILIM_LO = 80.6 kΩ

575

VILIM_SEL = 0 V, RILIM_LO = 22.1 kΩ

2120

2275 2430

VILIM_SEL = VIN, RILIM_HI = 20 kΩ

2340

2510 2685

VILIM_SEL = VIN, RILIM_HI = 16.9 kΩ

2770

2970 3170

VIN = 5.0 V, R = 0.1Ω, lead length = 2 inches (see

Figure 27)

1.5

mA

µs

SUPPLY CURRENT

IIN_OFF

Disabled IN supply current

IIN_ON

Enabled IN supply current

VEN = 0 V, VOUT = 0 V, –40 ≤ TJ ≤ 85°C

2

VCTL1 = VCTL2 = VIN, VCTL3 = 0 V or VIN, VILIM_SEL = 0 V

155

210

VCTL1 = VCTL2 = VIN, VCTL3 = 0V, VILIM_SEL = VIN

175

230

VCTL1 = VCTL2 = VIN, VCTL3 = VIN, VILIM_SEL = VIN

185

240

VCTL1 = 0V, VCTL2 = VCTL3 = VIN

205

260

4.1

4.3

µA

µA

UNDERVOLTAGE LOCKOUT

VUVLO

IN rising UVLO threshold voltage

Hysteresis

3.9

(2)

100

V

mV

FAULT

Output low voltage

IFAULT = 1 mA

Off-state leakage

VFAULT = 6.5 V

Over current FAULT rising and

falling deglitch

5

8.2

100

mV

1

µA

12

ms

100

mV

1

µA

STATUS

Output low voltage

ISTATUS = 1 mA

Off-state leakage

VSTATUS = 6.5 V

THERMAL SHUTDOWN

Thermal shutdown threshold

155

Thermal shutdown threshold in

current-limit

135

Hysteresis (2)

(2)

(3)

4

°C

20

These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's

product warranty.

Pulse-testing techniques maintain junction temperature close to ambient temperature; Thermal effects must be taken into account

separately.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

ELECTRICAL CHARACTERISTICS, HIGH-BANDWIDTH SWITCH

Unless otherwise noted: –40 ≤ TJ ≤ 125°C, 4.5 V ≤ VIN ≤ 5.5 V, VEN = VIN, VILIM_SEL = VIN, VCTL1 = VCTL2 = VCTL3 = VIN. RFAULT =

RSTATUS = 10 kΩ, RILIM_HI = 20 kΩ, RILIM_LO = 80.6 kΩ, Positive currents are into pins. Typical values are at 25°C. All voltages

are with respect to GND.

PARAMETER

TEST CONDITIONS

MIN

TYP MAX

UNIT

HIGH-BANDWIDTH ANALOG SWITCH

DP/DM switch on resistance

VDP/DM_OUT = 0 V, IDP/DM_IN = 30 mA

2

4

VDP/DM_OUT = 2.4 V, IDP/DM_IN = –15 mA

3

6

Switch resistance mismatch between

DP / DM channels

VDP/DM_OUT = 0 V, IDP/DM_IN = 30 mA

0.05

0.15

VDP/DM_OUT = 2.4 V, IDP/DM_IN = –15 mA

0.05

0.15

DP/DM switch off-state capacitance (1)

VEN = 0 V, VDP/DM_IN = 0.3 V, Vac = 0.6 Vpk-pk,

f = 1 MHz

3

3.6

6.2

DP/DM switch on-state capacitance

(2)

Ω

Ω

pF

VDP/DM_IN = 0.3 V, Vac = 0.6 Vpk-pk, f = 1 MHz

5.4

OIRR

Off-state isolation (3)

VEN = 0 V, f = 250 MHz

33

dB

XTALK

On-state cross channel isolation (3)

f = 250 MHz

52

dB

Off state leakage current

VEN = 0 V, VDP/DM_IN = 3.6 V, VDP/DM_OUT = 0 V,

measure IDP/DM_OUT

0.1

BW

Bandwidth (–3dB) (3)

RL = 50 Ω

tpd

Propagation delay (3)

tSK

Skew between opposite transitions of the

same port (tPHL – tPLH)

(1)

(2)

(3)

1.5

pF

µA

2.6

GHz

0.25

ns

0.1

0.2

ns

The resistance in series with the parasitic capacitance to GND is typically 250 Ω.

The resistance in series with the parasitic capacitance to GND is typically 150 Ω

These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's

product warranty.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

5

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

ELECTRICAL CHARACTERISTICS, CHARGING CONTROLLER

Unless otherwise noted: –40 ≤ TJ ≤ 125°C, 4.5 V ≤ VIN ≤ 5.5 V, VEN = VIN, VILIM_SEL = VIN, VCTL1 = 0 V, VCTL2 = VCTL3 = VIN.

RFAULT = RSTATUS = 10 kΩ, RILIM_HI = 20 kΩ, RILIM_LO = 80.6 kΩ, Positive currents are into pins. Typical values are at 25°C. All

voltages are with respect to GND.

PARAMETER

TEST CONDITIONS

SHORTED MODE

MIN

TYP

MAX

UNIT

125

200

Ω

VCTL1 = VIN, VCTL2 = VCTL3 = 0V

DP_IN / DM_IN shorting resistance

DIVIDER1 MODE

DP_IN Divider1 output voltage

1.9

2.0

2.1

V

DM_IN Divider1 output voltage

2.57

2.7

2.84

V

DP_IN output impedance

8

10.5

12.5

kΩ

DM_IN output impedance

8

10.5

12.5

kΩ

DP_IN Divider2 output voltage

2.57

2.7

2.84

V

DM_IN Divider2 output voltage

DIVIDER2 MODE

IOUT = 1A

1.9

2.0

2.1

V

DP_IN output impedance

8

10.5

12.5

kΩ

DM_IN output impedance

8

10.5

12.5

kΩ

0.5

0.6

0.7

V

0.4

V

CHARGING DOWNSTREAM PORT

VCTL1 = VCTL2 = VCTL3 = VIN

VDP_IN = 0.6 V,

–250 µA < IDM_IN < 0 µA

VDM_SRC

DM_IN CDP output voltage

VDAT_REF

DP_IN rising lower window thresholdfor

VDM_SRC activation

Hysteresis

VLGC_SRC

0.25

(1)

50

DP_IN rising upper window thresholdfor

VDM_SRC de-activation

0.8

hysteresis (1)

IDP_SINK

VDP_IN = 0.6 V

70

100

µA

635

700

765

mA

50

Load detect set time

200

275

ms

1.9

3

4.2

s

Power wake short circuit current limit

32

55

78

mA

IOUT falling power wake reset current

detection threshold

23

45

67

mA

10.7

15

Load detect reset time

Reset current hysteresis

VCTL1 = VCTL2 = 0V, VCTL3 = VIN

(1)

5

Power wake reset time

6

mA

140

LOAD DETECT – POWER WAKE

(1)

mV

40

hysteresis (1)

IOS_PW

V

VCTL1 = VCTL2 = VCTL3 = VIN

IOUT rising load detect current threshold

tLD_SET

1

100

DP_IN sink current

LOAD DETECT – NON POWER WAKE

ILD

mV

mA

20.6

s

These parameters are provided for reference only and do not constitute part of TI's published device specifications for purposes of TI's

product warranty.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

TYPICAL CHARACTERISTICS

POWER SWITCH ON RESISTANCE

vs

TEMPERATURE

REVERSE LEAKAGE CURRENT

vs

TEMPERATURE

0.3

100

0.25

Reverse Leakage Current (µA)

On Resistance (mΩ)

90

80

70

60

0.2

0.15

0.1

0.05

50

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

0

−40 −25 −10

110 125

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

G001

G002

Figure 1.

Figure 2.

OUT DISCHARGE RESISTANCE

vs

TEMPERATURE

OUT SHORT CIRCUIT CURRENT LIMIT

vs

TEMPERATURE

580

3000

OUT Short Circuit Current Limit (mA)

OUT Discharge Resistance (Ω)

560

3500

VIN = 4.5 V

VIN = 5 V

VIN = 5.5 V

540

520

500

480

460

−40 −25 −10

2500

2000

1500

RILIM_LO = 210 kΩ

RILIM_LO = 80.6 kΩ

RILIM_HI = 20 kΩ

RILIM_HI = 16.9 kΩ

1000

500

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

0

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

G003

Figure 3.

G004

Figure 4.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

7

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

TYPICAL CHARACTERISTICS (continued)

DISABLED IN SUPPLY CURRENT

vs

TEMPERATURE

ENABLED IN SUPPLY CURRENT - SDP

vs

TEMPERATURE

1.2

190

VIN = 5.5 V

180

Enabled IN Supply Current (µA)

Disabled IN Supply Current (µA)

1

0.8

0.6

0.4

0.2

0

−40

VIN = 4.5 V

VIN = 5 V

VIN = 5.5 V

170

160

150

Device configured for SDP

VILIMSEL = 0 V

140

−20

0

20

40

60

Junction Temperature (°C)

80

130

−40 −25 −10

100

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

G005

G006

Figure 5.

Figure 6.

ENABLED IN SUPPLY CURRENT - CDP

vs

TEMPERATURE

ENABLED IN SUPPLY CURRENT - DCP AUTO

vs

TEMPERATURE

220

230

Enabled IN Supply Current (µA)

Enabled IN Supply Current (µA)

210

240

VIN = 4.5 V

VIN = 5 V

VIN = 5.5 V

200

190

180

170

VIN = 4.5 V

VIN = 5 V

VIN = 5.5 V

220

210

200

190

Device configured for CDP

160

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

Device configured for DCP AUTO

110 125

180

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

G007

Figure 7.

8

95

110 125

G008

Figure 8.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

TYPICAL CHARACTERISTICS (continued)

STATUS AND FAULT OUTPUT LOW VOLTAGE

vs

SINKING CURRENT

DATA TRANSMISSION CHARACTERISTICS

vs

FREQUENCY

0

700

TJ = −40°C

TJ = 25°C

TJ = 125°C

600

500

Transmission Gain - dB

Output Low Voltage (mV)

-5

400

300

200

-10

-15

-20

100

VIN = 4.5 V

0

0

1

2

3

4

5

6

7

Sinking Current (mA)

8

9

10

-20

0.01

G009

0.1

1

10

Frequency - GHz

Figure 9.

Figure 10.

OFF STATE DATA SWITCH ISOLATION

vs

FREQUENCY

ON STATE CROSS-CHANNEL ISOLATION

vs

FREQUENCY

60

XTALK - ON State Cross-Channel Isolation - dB

80

OIRR - Off State Isolation - dB

50

40

30

20

10

70

60

50

40

30

20

10

0

0

0.01

0.1

1

10

0.01

0.1

1

10

Frequency - GHz

Frequency - GHz

Figure 11.

Figure 12.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

9

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

TYPICAL CHARACTERISTICS (continued)

EYE DIAGRAM USING USB COMPLIANCE TEST PATTERN

(with data switch)

0.5

0.5

0.4

0.4

0.3

0.3

0.2

0.2

Differential Signal (V)

Differential Signal (V)

EYE DIAGRAM USING USB COMPLIANCE TEST PATTERN

(with no switch)

0.1

0

–0.1

–0.2

0.1

0

–0.1

–0.2

–0.3

–0.3

–0.4

–0.4

–0.5

–0.5

0

0.2

0.4

0.6

0.8

1 1.2

Time (ns)

1.4

1.6

1.8

0

2

0.2

0.4

G013

0.6

0.8

1 1.2

Time (ns)

1.4

1.6

Figure 13.

Figure 14.

IOUT RISING LOAD DETECT THRESHOLD

AND OUT SHORT CIRCUIT CURRENT LIMIT

vs

TEMPERATURE

LOAD DETECT SET TIME

vs

TEMPERATURE

1.8

2

G014

230

740

RILIM_LO = 80.6 kΩ

720

225

Load Detect Set Time (ms)

Current (mA)

700

680

660

640

220

215

210

205

620

IOS - OUT Short Circuit Current Limit

ILD - IOUT Rising Load Detect Threshold

600

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

95

110 125

200

−40 −25 −10

5

20 35 50 65 80

Junction Temperature (°C)

G015

Figure 15.

10

95

110 125

G016

Figure 16.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

TYPICAL CHARACTERISTICS (continued)

POWER WAKE CURRENT LIMIT

vs

TEMPERATURE

TURN-ON RESPONSE

59

Power Wake Current Limit (mA)

58

57

VOUT

2 V/div

56

VEN

5 V/div

55

54

53

52

−40 −25 −10

RLOAD = 5 Ω

CLOAD = 150 µF

IIN

500 mA/div

t - Time - 1 ms/div

5

20 35 50 65 80

Junction Temperature (°C)

95

G021

110 125

G017

Figure 17.

Figure 18.

TURN-OFF RESPONSE

DEVICE ENABLED INTO SHORT CIRCUIT

V/FAULT

5 V/div

VOUT

2 V/div

VEN

5 V/div

VEN

5 V/div

RLOAD = 5 Ω

CLOAD = 150 µF

RILM_LO = 80.6 kΩ

IIN

500 mA/div

IIN

500 mA/div

t - Time - 1 ms/div

Figure 19.

G022

t - Time - 2 ms/div

G023

Figure 20.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

11

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

TYPICAL CHARACTERISTICS (continued)

DEVICE ENABLED INTO SHORT CIRCUIT - THERMAL

CYCLING

RILM_HI = 20 kΩ

V/FAULT

5 V/div

SHORT CIRCUIT to FULL LOAD RECOVERY

V/FAULT

5 V/div

VEN

5 V/div

VOUT

2 V/div

IIN

1 A/div

IIN

2 A/div

t - Time - 5 ms/div

Figure 21.

12

RILIM_HI = 20 kΩ

RLOAD = 5 Ω

CLOAD = 150 µF

G024

Submit Documentation Feedback

t - Time - 2 ms/div

Figure 22.

G025

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

PARAMETER MEASUREMENT DESCRIPTION

OUT

RL

VOUT

CL

tr

tf

90%

10%

Figure 23. OUT Rise/Fall Test Load

Figure 24. Power-On and Off Timing

5V

VEN

50 %

50 %

VOUT

ton

tDCHG

toff

0V

90 %

VOUT

10 %

Figure 25. Enable Timing, Active High Enable

Figure 26. OUT Discharge During Mode Change

IOS

IOUT

tIOS

Figure 27. Output Short Circuit Parameters

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

13

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

DEVICE INFORMATION

IN

1

DM_OUT

2

ILIM_HI

ILIM_LO

GND

FAULT

TPS2543 RTE PACKAGE

(Top View)

16

15

14

13

12

OUT

11

DM_IN

DP_IN

Thermal Pad

4

9

5

6

7

8

CLT3

ILIM_SEL

CLT2

10

CLT1

3

EN

DP_OUT

STATUS

PIN FUNCTIONS

NO.

(1)

14

NAME

TYPE (1)

P

DESCRIPTION

Input voltage and supply voltage; connect 0.1 μF or greater ceramic capacitor from IN to GND as close

to the device as possible

1

IN

2

DM_OUT

I/O

D– data line to USB host controller

3

DP_OUT

I/O

D+ data line to USB host controller

4

ILIM_SEL

I

Logic-level input signal used to control the charging mode, current limit threshold, and load detection;

see the control truth table

5

EN

I

Logic-level input for turning the power switch and the signal switches on/off; logic low turns off the signal

and power switches and holds OUT in discharge.

6

CTL1

I

7

CTL2

I

8

CTL3

I

Logic-level inputs used to control the charging mode and the signal switches; see the control truth table

9

STATUS

O

Active-low open-drain output, asserted in load detection conditions

10

DP_IN

I/O

D+ data line to downstream connector

11

DM_IN

I/O

D– data line to downstream connector

12

OUT

P

Power-switch output

13

FAULT

O

Active-low open-drain output, asserted during over-temperature or current limit conditions

14

GND

P

Ground connection

15

ILIM_LO

I

External resistor used to set the low current-limit threshold and the load detection current threshold. A

resistor to ILIM_LO is optional; see Current-Limit Settings in DETAILED DESCRIPTION.

16

ILIM_HI

I

External resistor used to set the high current-limit threshold

NA

PowerPAD

Internally connected to GND; used to heat-sink the part to the circuit board traces. Connect to GND

plane.

G = Ground, I = Input, O = Output, P = Power

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

FUNCTIONAL BLOCK DIAGRAM

Current

Sense

CS

IN

OUT

Disable + UVLO+Discharge

ILIM_HI

Current

Limit

Current Limit

select

Charge

Pump

ILIM_LO

GND

OC

8-ms Deglitch

OTSD

Thermal

Sense

UVLO

ILIM_SEL

Driver

LD cur set

EN

discharge

FAULT

8-ms Deglitch

(falling edge)

DM_OUT

DM_IN

DP_OUT

DP_IN

ILIM_SEL

OC

CTL1

CTL2

Logic

control

CDP

Detection

DCP

Detection

Divider

Mode

Auto-Detection

LD cur set

Discharge

STATUS

CTL3

Discharge

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

15

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

DETAILED DESCRIPTION

Overview

The following overview references various industry standards. It is always recommended to consult the most upto-date standard to ensure the most recent and accurate information. Rechargeable portable equipment requires

an external power source to charge its batteries. USB ports are a convenient location for charging because of an

available 5 V power source. Universally accepted standards are required to make sure host and client-side

devices operate together in a system to ensure power management requirements are met. Traditionally, USB

host ports following the USB 2.0 specification must provide at least 500 mA to downstream client-side devices.

Because multiple USB devices can be attached to a single USB port through a bus-powered hub, it is the

responsibility of the client-side device to negotiate its power allotment from the host to ensure the total current

draw does not exceed 500 mA. In general, each USB device is granted 100 mA and may request more current in

100 mA unit steps up to 500 mA. The host may grant or deny based on the available current.

Additionally, the success of USB has made the mini-USB connector a popular choice for wall adapter cables.

This allows a portable device to charge from both a wall adapter and USB port with only one connector. One

common difficulty has resulted from this. As USB charging has gained popularity, the 500 mA minimum defined

by USB 2.0 or 900 mA for USB 3.0 has become insufficient for many handset and personal media players which

need a higher charging rate. Wall adapters can provide much more current than 500mA/900mA. Several new

standards have been introduced defining protocol handshaking methods that allow host and client devices to

acknowledge and draw additional current beyond the 500mA/900mA minimum defined by USB 2.0/3.0 while still

using a single micro-USB input connector.

The TPS2543 supports three of the most common protocols:

• USB Battery Charging Specification BC1.2

• Chinese Telecommunications Industry Standard YD/T 1591-2009

• Divider Mode

All three methods have similarities and differences, but the biggest commonality is that all three define three

types of charging ports that provide charging current to client-side devices. These charging ports are defined as:

• Standard Downstream Port (SDP)

• Charging Downstream Port (CDP)

• Dedicated Charging Port (DCP)

BC1.2 defines a Charging Port as a downstream facing USB port that provides power for charging portable

equipment.

Table 1 shows the differences between these ports according to BC1.2 .

Table 1. Operating Modes

PORT TYPE

SUPPORT USB

2.0 COMMUNICATION

MAX. ALLOWABLE CURRENT

DRAW BY PORTABLE DEVICE (A)

SDP (USB 2.0)

Yes

0.5

SDP (USB 3.0)

Yes

0.9

CDP

Yes

1.5

DCP

No

1.5

BC1.2 defines the protocol necessary to allow portable equipment to determine what type of port it is connected

to so that it can allot its maximum allowable current draw. The hand-shaking process has two steps. During step

one, the primary detection, the portable equipment outputs a nominal 0.6-V output on its D+ line and reads the

voltage input on its D- line. The portable device concludes it is connected to an SDP if the voltage is less than

the nominal data detect voltage of 0.3 V. The portable device concludes that it is connected to a Charging Port if

the D- voltage is greater than the nominal data detect voltage of 0.3 V and less than 0.8 V. The second step, the

secondary detection, is necessary for portable equipment to determine between a CDP and a DCP. The portable

device outputs a nominal 0.6 V output on its D- line and reads the voltage input on its D+ line. The portable

device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect

voltage of 0.3 V. The portable device concludes it is connected to a DCP if the data line being read is greater

than the nominal data detect voltage of 0.3V and less than 0.8 V.

16

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

Standard Downstream Port (SDP) USB 2.0/USB 3.0

An SDP is a traditional USB port that follows USB 2.0/3.0 protocol and supplies a minimum of 500 mA/900 mA

per port. USB 2.0/3.0 communications is supported, and the host controller must be active to allow charging.

Charging Downstream Port (CDP)

A CDP is a USB port that follows USB BC1.2 and supplies a minimum of 1.5 A per port. It provides power and

meets USB 2.0 requirements for device enumeration. USB 2.0 communications is supported, and the host

controller must be active to allow charging. What separates a CDP from an SDP is the host-charge handshaking

logic that identifies this port as a CDP. A CDP is identifiable by a compliant BC1.2 client device and allows for

additional current draw by the client device.

The CDP hand-shaking process is two steps. During step one the portable equipment outputs a nominal 0.6 V

output on its D+ line and reads the voltage input on its D- line. The portable device concludes it is connected to

an SDP if the voltage is less than the nominal data detect voltage of 0.3 V. The portable device concludes that it

is connected to a Charging Port if the D- voltage is greater than the nominal data detect voltage of 0.3V and less

than 0.8 V.

The second step is necessary for portable equipment to determine between a CDP and a DCP. The portable

device outputs a nominal 0.6 V output on its D- line and reads the voltage input on its D+ line. The portable

device concludes it is connected to a CDP if the data line being read remains less than the nominal data detect

voltage of 0.3 V. The portable device concludes it is connected to a DCP if the data line being read is greater

than the nominal data detect voltage of 0.3V and less than 0.8 V.

Dedicated Charging Port (DCP)

A DCP only provides power and does not provide data connection to an upstream port. A DCP is identified by

the electrical characteristics of its data lines. The TPS2543 emulates two common charging standards namely,

BC1.2 and Chinese Telecommunications Industry Standard YD/T 1591-2009, and one brand unique DCP

charging scheme which will be referred to as Divider scheme.

DCP BC 1.2 and YD/T 1591-2009

Both standards defines that the D+ and D- data lines should be shorted together with a maximum series

impedance of 200 Ω. This is shown in Figure 28.

D- Out

VBUS

TPS2543

D-

2V

750mA is measured by the TPS2543 it switches to Divider 2 scheme and test to see if the peripheral

device will still charge at a high current. If it does then it stays in Divider 2 scheme otherwise it will revert to

Divider 1 scheme.

TPS2543

To USB 2.0 Host

DCP Auto

BC1.2 CDP/SDP

D-

BC1.2 DCP

D+

From Charging

Peripheral

Divider 1/2

High BW Data Line SW

Controlled by CTL/EN pins

18

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

DCP Forced Shorted / DCP Forced Divider 1

In this mode the device is permanently set to one of the DCP schemes (BC 1.2/ YD/T 1591-2009 or Divider 1) as

commanded by its control pin setting per device truth table.

High-Bandwidth Data Line Switch

The TPS2543 passes the D+ and D- data lines through the device to enable monitoring and handshaking while

supporting charging operation. A wide bandwidth signal switch is used, allowing data to pass through the device

without corrupting signal integrity. The data line switches are turned on in any of CDP or SDP operating modes.

The EN input also needs to be at logic High for the data line switches to be enabled.

NOTE

1. While in CDP mode, the data switches are ON even while CDP handshaking is occurring.

2. The data line switches are OFF if EN or all CTL pins are held low, or if in DCP mode. They are not

automatically turned off if the power switch (IN to OUT) is in current limit.

3. The data switches are for USB 2.0 differential pair only. In the case of a USB 3.0 host, the super speed

differential pairs must be routed directly to the USB connector without passing through the TPS2543.

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

19

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

Device Operation

Please refer to the simplified device state diagram in Figure 31. Power-on-reset (POR) holds device in initial

state while output is held in discharge mode. Any POR event will take the device back to initial state. After POR

clears, device goes to the next state depending on the CTL lines as shown in Figure 31.

DCP_Auto

Reset

DCP_SHORT/

DCP_DIVIDER

Initial

DCP Forced

DCH/SDP/

CDP

DCH

Done

DCH

DCP_Auto

Discharge

(310 ms)

1111

1110

DCH/SDP

CDP

110X/

010X

Not SDP1

DCP Auto

SDP1

Not CDP

Note:

1) All shaded boxes are device charging modes

2) See below table for CTL settings corresponding to

flow line conditions

3) Mouse / keyboard wake function not shown

CDP

1111

Device Control Pins

Flow Line Condition CTL1

DCH

CDP

SDP2

1110

SDP1

SDP2

Not SDP2

DCP_SHORT

DCP_DIVIDER

DCP_Auto

CTL2

0

1

1

1

0

1

1

0

0

CTL3

0

1

1

1

1

0

0

1

0

0

1

1

0

0

0

1

1

1

ILIM_SEL

X

1

0

X

X

X

X

X

X

Figure 31. TPS2543 Charging States

Output Discharge

To allow a charging port to renegotiate current with a portable device, TPS2543 uses the OUT discharge

function. It proceeds by turning off the power switch while discharging OUT, then turning back on the power

switch to reassert the OUT voltage. This discharge function is automatically applied as shown in device state

diagram.

20

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

Mouse/Key Board Wake Function

The TPS2543 supports low speed HID (human interface device like mouse/key board) wake function. It does not

support Full Speed HID. There are two scenarios under which wake on mouse is supported by the TPS2543.

They are:

1. CDP/SDP2 (111X) to DCP/Auto (011X)

2. SDP1 (010X) to DCP/Auto (011X)

Below description illustrates wake on mouse operation for scenario 1, same holds true for scenario 2.

When a low speed compliant device is attached to the TPS2543, charging port D- line will be pulled high in its

idle state (mouse/keyboard not activated). TPS2543 will monitor D- data line continuously. When device is in

CDP (1111) or SDP2 (1110) or SDP1 (010X) mode and system is commanded to go to sleep state, the device

CTL setting is also changed. Assuming it is changed to DCP/Auto, 011X, having previously detected a HID

attachment the device will simply ignore the command to go to DCP/Auto mode and stay in CDP/SDP2 state to

support wake on mouse function. When the USB low speed HID is activated (clicked) while system is in S3

(sleep) mode the high speed switch within the TPS2543 allows the transfer of signal from the HID device to the

USB host. The USB host subsequently wakes the system and changes CTL setting of the TPS2543 back to

CDP/SDP2 mode. Activating (clicking) the low speed device makes the D- data line go back low momentarily,

this triggers an internal timer within the TPS2543 to count down. If after ~64ms the CTL lines are still set at 011X

(DCP/Auto) the device will immediately switch to DCP/Auto mode and disconnect the mouse from the host. To

prevent this, the CTL setting must be made in less then 64 ms after HID device activation otherwise mouse/KB

function will be lost. See Figure 32 scope plot for an event sequence where mouse connection is maintained at

wake.

Mouse Wake from Sleep

VOUT

DM_IN High

System in Sleep

CTL1 = 1 within 64ms of

sys wake, TPS2543 stays

in SDP/CDP and mouse

connection is maintained

VOUT

2 V/div

CTL1 = 0 TPS2543

detects mouse and

ignores going to DCP

VDM_IN

1 V/div

Mouse Clicked here

system wakes

VCTL1

1 V/div

Figure 32. Mouse Wake from Sleep Scope Plot

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

21

�TPS2543

SLVSBA6 – FEBRUARY 2012

www.ti.com

Device Truth Table (TT)

Device TT lists all valid bias combinations for the three control pins CTL1-3 and ILIM_SEL pin and their

corresponding charging mode. It is important to note that the TT purposely omits matching charging modes of the

TPS2543 with global power states (S0-S5) as device is agnostic to system power states. The TPS2543 monitors

its CTL inputs and will transition to whatever charging state it is commanded to go to (except when LS HID

device is detected). For example if sleep charging is desired when system is in standby or hibernate state then

user must set TPS2543 CTL pins to correspond to DCP_Auto charging mode per below table. When system is

put back to operation mode then set control pins to correspond to SDP or CDP mode and so on.

Table 2. Truth Table

CTL1

CTL2

CTL3

ILIM_SEL

MODE

CURRENT

LIMIT

SETTING

0

0

0

0

Discharge

NA

OFF

0

0

0

1

Discharge

NA

OFF

0

0

1

0

DCP_Auto

ILIM_HI

(1)

(2)

(3)

(4)

(5)

IOS_PW & ILIM_HI

STATUS OUTPUT

(Active low)

OUT held low

OFF

(1)

0

0

1

1

DCP_Auto

0

1

0

0

SDP

ILIM_LO

OFF

0

1

0

1

SDP

ILIM_HI

OFF

0

1

1

0

DCP_Auto

ILIM_HI

OFF

COMMENT

Data Lines Disconnected

DCP load present

(2)

Data Lines Disconnected and Load Detect

Function Active

Data Lines connected

Data Lines Disconnected

DCP load present

(3)

0

1

1

1

DCP_Auto

ILIM_HI

1

0

0

0

DCP _Shorted

ILIM_LO

OFF

1

0

0

1

DCP_Shorted

ILIM_HI

OFF

1

0

1

0

DCP / Divider1

ILIM_LO

OFF

1

0

1

1

DCP / Divider1

ILIM_HI

OFF

1

1

0

0

SDP

ILIM_LO

OFF

1

1

0

1

SDP

ILIM_HI

OFF

1

1

1

0

SDP (4)

ILIM_LO

OFF

1

1

1

1

CDP (4)

ILIM_HI

CDP load present (5)

Data Lines Disconnected and Load Detect

Function Active

Device Forced to stay in DCP BC 1.2 charging

mode

Device Forced to stay in DCP Divider 1

Charging Mode

Data Lines Connected

Data Lines Connected and Load Detect Active

TPS2543 : Current limit (IOS) is automatically switched between IOS_PW and the value set by ILIM_HI according to the Load Detect –

Power Wake functionality.

DCP Load present governed by the “Load Detection – Power Wake” limits.

DCP Load present governed by the “Load Detection – Non Power Wake” limits.

No OUT discharge when changing between 1111 and 1110.

CDP Load present governed by the “Load Detection – Non Power Wake” limits and BC 1.2 primary detection.

Table 3 can be used as an aid to program the TPS2543 per system states however not restricted to below

settings only.

Table 3. Control Pin Settings Matched to System Power States

SYSTEM

GLOBAL

POWER

STATE

CTL1

CTL2

CTL3

ILIM_SEL

CURRENT LIMIT

SETTING

S0

SDP

1

1

0

1 or 0

ILIM_HI / ILIM_LO

S0

SDP, no discharge to / from CDP

1

1

1

0

ILIM_LO

S0

CDP, load detection with ILIM_LO + 60mA thresholds or if a

BC1.2 primary detection occurs

1

1

1

1

ILIM_HI

Auto mode, load detection with power wake thresholds

0

0

1

1

ILIM_HI

Auto mode, no load detection

0

0

1

0

ILIM_HI

S3

Auto mode, keyboard/mouse wake up, load detection with

ILIM_LO + 60 mA thresholds

0

1

1

1

ILIM_HI

S3

Auto mode, keyboard/mouse wake-up, no load detection

0

1

1

0

ILIM_HI

S3

SDP, keyboard/mouse wake-up

0

1

0

1 or 0

ILIM_HI / ILIM_LO

S4/S5

S3/S4/S5

22

TPS2543 CHARGING MODE

Submit Documentation Feedback

Copyright © 2012, Texas Instruments Incorporated

Product Folder Link(s): TPS2543

�TPS2543

www.ti.com

SLVSBA6 – FEBRUARY 2012

Load Detect

TPS2543 offers system designers unique power management strategy not available in the industry from similar

devices. There are two power management schemes supported by the TPS5243 via the STATUS pin, they are:

1. Power Wake (PW)

2. Port Power Management (PPM)

Either feature may be implemented in a system depending on power savings goals for the system. In general

Power Wake feature is used mainly in mobile systems like a notebook where it is imperative to save battery

power when system is in deep sleep (S4/S5) state. On the other hand Port Power Management feature would be

implemented where multiple charging ports are supported in the same system and system power rating is not

capable of supporting full charging on multiple ports simultaneously.

Power Wake

Goal of power wake feature is to save system power when system is in S4/S5 state. In S4/S5 state system is in

deep sleep and typically running of the battery; so every “mW” in system power savings will translate to

extending battery life. In this state the TPS2543 will monitor charging current at the OUT pin and provide a

mechanism via the STATUS pin to switch-out the high power DC-DC controller and switch-in a low power LDO

when charging current requirement is