Sample &

Buy

Product

Folder

Support &

Community

Tools &

Software

Technical

Documents

TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

TPD1S414 USB Charger Overvoltage, Surge, and ESD Protection for VBUS Pin

1 Features

3 Description

•

The TPD1S414 device is a single-chip solution for a

USB connector’s VBUS line protection. The

bidirectional nFET switch ensures safe current flow in

both charging and host mode while protecting the

internal system circuits from any overvoltage

conditions at the VBUS_CON pin. On the VBUS_CON pin,

this device can handle overvoltage protection up to

30 V. After the EN pin toggles low, the TPD1S414

waits 20 ms before turning ON the nFET through a

soft-start delay. ACK pin indicates the FET is

completely turned ON.

1

•

•

•

•

•

•

•

Overvoltage Protection at VBUS_CON Up to 30-V

DC

Low RON nFET Switch Supports Host and

Charging Mode

Internal 15-ms Start-Up Delay

Internal 30-ms Soft-Start Delay to Minimize the

USB Inrush Current

Transient Protection for VBUS Line:

– IEC 61000-4-2 Contact Discharge ±15 kV

– IEC 61000-4-2 Air Gap Discharge ±15 kV

– IEC 61000-4-5 Open-Circuit Voltage 100 V

Integrated Input Enable and Status Output Signal

Thermal Shutdown (TSD) Feature

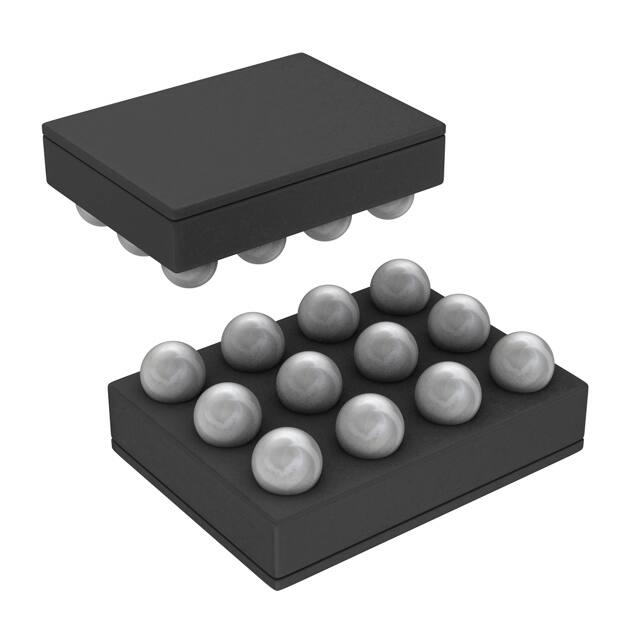

Space-Saving DSBGA Package: (1.4 mm × 1.89

mm)

The typical application interface for the TPD1S414 is

the VBUS line in USB connectors. Typical end

equipment for TPD1S414 are mobiles phones,

tablets, wearables, and electronic-point-of-sale

(EPOS). The TPD1S414 can also be applied to any

system using an interface with a 5-V power rail.

Device Information(1)

2 Applications

•

•

PART NUMBER

PACKAGE

TPD1S414

End Equipment

– Mobile Phones

– Tablets

– Wearables

– Electronic-Point-of-Sale (EPOS)

Interfaces

– USB 2.0

– USB 3.0

– USB Type C

BODY SIZE (NOM)

DSBGA (12)

1.40 mm × 1.89 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Typical Application Schematic

VCC

TPD1S414

USB Type C Connector

VBUS

VBUS_CON

ACK

GPIO

EN

GPIO

VBUS_SYS

VBUS

VOUT

System Load

DD+

1 µF

GND

2.2 µF

BAT

CC1

CC2

+ Battery

DGND

D+

CC Logic & Port

Controller

I2C/GPIO

PMIC

TPD4E110

Copyright © 2016, Texas Instruments Incorporated

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

Table of Contents

1

2

3

4

5

6

7

Features ..................................................................

Applications ...........................................................

Description .............................................................

Revision History.....................................................

Pin Configuration and Functions .........................

Specifications.........................................................

1

1

1

2

3

4

6.1

6.2

6.3

6.4

6.5

6.6

6.7

6.8

6.9

6.10

6.11

4

4

4

5

5

5

6

6

6

6

8

Absolute Maximum Ratings .....................................

ESD Ratings..............................................................

Recommended Operating Conditions.......................

Thermal Information ..................................................

Electrical Characteristics (EN, ACK Pins).................

Electrical Characteristics (OVP Circuit) ....................

Timing Requirements ................................................

Switching Characteristics (nFET)..............................

Supply Current Consumption....................................

Thermal Shutdown Feature ....................................

Typical Characteristics ............................................

Detailed Description ............................................ 10

7.1

7.2

7.3

7.4

8

Overview .................................................................

Functional Block Diagram .......................................

Feature Description.................................................

Device Functional Modes........................................

10

10

10

11

Application and Implementation ........................ 13

8.1 Application Information............................................ 13

8.2 Typical Application ................................................. 13

9 Power Supply Recommendations...................... 15

10 Layout................................................................... 15

10.1 Layout Guidelines ................................................. 15

10.2 Layout Example .................................................... 15

11 Device and Documentation Support ................. 16

11.1

11.2

11.3

11.4

11.5

Receiving Notification of Documentation Updates

Community Resource............................................

Trademarks ...........................................................

Electrostatic Discharge Caution ............................

Glossary ................................................................

16

16

16

16

16

12 Mechanical, Packaging, and Orderable

Information ........................................................... 16

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Revision A (October 2013) to Revision B

•

Page

Added ESD Ratings table, Detailed Description section, Application and Implementation section, Power Supply

Recommendations section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable

Information section ................................................................................................................................................................. 1

Changes from Original (October 2013) to Revision A

Page

•

Changed text in the DESCRIPTION From: TPD1S414 waits 15 ms before turning ON the nFET To: TPD1S414

waits 20 ms before turning ON the nFET ............................................................................................................................... 1

•

Deleted Continuous forward current through the FET body diode, IDIODE from the ABSOLUTE MAXIMUM RATINGS

table ........................................................................................................................................................................................ 4

•

Deleted Peak input current on VBUS_CON pin, IBUS from the ABSOLUTE MAXIMUM RATINGS table .................................... 4

•

Added Voltage on ACK pin to the ABSOLUTE MAXIMUM RATINGS table.......................................................................... 4

•

Added Continuous current on VBUS_CON and VBUS_SYS pins to the RECOMMENDED OPERATING CONDITIONS table ..... 4

•

Added Continuous forward current through the FET body diode, IDIODE to the RECOMMENDED OPERATING

CONDITIONS table ................................................................................................................................................................ 4

•

Added values to the THERMAL INFORMATION table .......................................................................................................... 5

•

Changed the IHOST_LEAK MAX value From: 160 To: 200 µA in the SUPPLY CURRENT CONSUMPTION table ................... 6

•

Deleted graphs: Enabling the Load Switch, Connecting VBUS_CON, and OVP Operation from the TIMING DIAGRAMS

section .................................................................................................................................................................................... 7

•

Changed horizontal axis labeling on Figure 7 ........................................................................................................................ 8

•

Changed Figure 10............................................................................................................................................................... 14

•

Added text to the APPLICATION INFORMATION section................................................................................................... 14

2

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

�TPD1S414

www.ti.com

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

5 Pin Configuration and Functions

YZ Package

12-Pin DSBGA

Top View - See Through

GND

VBUS_SYS

VBUS_SYS

GND

ACK

VBUS_SYS

VBUS_CON

GND

EN

VBUS_CON

VBUS_CON

GND

Pin Functions

PIN

TYPE

DESCRIPTION

NAME

NO.

ACK

B1

O

Open-Drain Acknowledge pin. See Table 2.

EN

C1

I

Enable Active-Low Input. Drive EN low to enable the switch. Drive EN high to

disable the switch.

B3, C2, C3

I/O

Connect to USB connector VBUS pin;

IEC61000-4-2 ESD protection

IEC61000-4-5 Surge protection

A2, A3, B2

I/O

Connect to internal VBUS plane

A1, A4, B4, C4

Ground

Connect to PCB ground plane

VBUS_CON

VBUS_SYS

GND

Table 1. 12-YZ Pin Mapping

1

2

3

4

A

GND

VBUS_SYS

VBUS_SYS

GND

B

ACK

VBUS_SYS

VBUS_CON

GND

C

EN

VBUS_CON

VBUS_CON

GND

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

3

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2)

MIN

MAX

UNIT

Supply voltage from USB connector, VBUS_CON

–0.3

30

V

Internal supply DC voltage rail on the PCB, VBUS_SYS

–0.5

7

V

Voltage on EN pin

–0.5

7

V

Voltage on ACK pin

–0.5

7

V

Output load capacitance, CLOAD

VBUS_SYS pin

0.1

50

µF

Input capacitance, CON

VBUS_CON pin

0.1

50

µF

Operating free-air temperature, TA

–40

85

°C

Storage temperature, Tstg

–40

150

°C

(1)

(2)

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

6.2 ESD Ratings

VALUE

Electrostatic

discharge

V(ESD)

(1)

(2)

UNIT

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)

±2000

Charged-device model (CDM), per JEDEC specification JESD22-C101 (2)

±1000

IEC 61000-4-2 contact discharge

±15000

V

±15000

V

IEC 61000-4-2 air-gap discharge

V

IEC 61000-4-5 Peak Pulse Current (tp = 8/20 µs)

VBUS_CON pin

21

A

IEC 61000-4-5 Peak Pulse Power (tp = 8/20 µs)

VBUS_CON pin

700

W

IEC 61000-4-5 Open circuit voltage (tp = 1.2/50 µs)

VBUS_CON pin

100

V

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as

±2000 V may actually have higher performance.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as

±1000 V may actually have higher performance.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

PARAMETER

MIN

NOM

MAX

5.9

UNIT

VBUS_CON

Supply voltage from USB connector

VBUS_SYS

Internal supply DC voltage rail on the PCB

CLOAD

Output load capacitance

VBUS_SYS pin

2.2

µF

CIN

Input capacitance

VBUS_CON pin

1

µF

RPULLUP

Pullup resistor

ACK pin

VBUS_CON

and VBUS_SYS pins

VBUS_SYS

IVBUS

Continuous current on VBUS_CON

IDIODE

Continuous current through the FET body diode

4

5.9

Submit Documentation Feedback

4.3

V

V

100

kΩ

3.5

A

1

A

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

�TPD1S414

www.ti.com

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

6.4 Thermal Information

TPD1S414

THERMAL METRIC (1)

YZ (DSBGA)

UNIT

12 PINS

RθJA

Junction-to-ambient thermal resistance

89

°C/W

RθJC(top)

RθJB

Junction-to-case(top) thermal resistance

0.6

°C/W

Junction-to-board thermal resistance

16.3

°C/W

ψJT

Junction-to-top characterization parameter

2.7

°C/W

ψJB

Junction-to-board characterization parameter

16.2

°C/W

RθJC(bot)

Junction-to-case(bottom) thermal resistance

n/A

°C/W

(1)

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

6.5 Electrical Characteristics (EN, ACK Pins)

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

VIH

High-level input voltage, EN

VIL

Low-level input voltage, EN

IIL

Input leakage current EN

VI = 3.3 V

VOL

Low-level output voltage, ACK

IOL = 3 mA

MIN

TYP

1.2

MAX

UNIT

6

V

0.8

V

1

µA

0.4

V

UNIT

6.6 Electrical Characteristics (OVP Circuit)

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

6

6.2

6.4

VOVP_RISING

Input overvoltage protection

threshold, VBUS_CON

VBUS_CON increasing from 5 V

VHYS_OVP

Hysteresis on OVP, VBUS_CON

VBUS_CON decreasing from 7 V to

5V

VOVP_FALLING

Input overvoltage protection

threshold, VBUS_CON

VBUS_CON decreasing from 7 V to

5V

5.93

VUVLO

Input undervoltage lockout,

VBUS_CON

VBUS_CON voltage rising from 0 V

to 5 V

3.1

VHYS_UVLO

Hysteresis on UVLO, VBUS_CON

Difference between rising and

falling UVLO thresholds

VUVLO_FALLING

Input undervoltage lockout,

VBUS_CON

VBUS_CON voltage rising from 5 V

to 0 V

3

3.2

3.4

V

VUVLO_SYS

VBUS_SYS undervoltage lockout,

VBUS_SYS

VBUS_SYS voltage rising from 0 V

to 5 V

3.1

3.6

4.3

V

VHYS_UVLO_SYS

VBUS_SYS UVLO Hysteresis,

VBUS_SYS

Difference between rising and

falling UVLO thresholds on

VBUS_SYS

VUVLO_SYS_FALL

VBUS_SYS undervoltage lockout,

VBUS_SYS

VBUS_SYS voltage falling from 7 V

to 5 V

50

3.3

mV

6.37

V

3.5

V

100

mV

480

3

3.2

mV

3.4

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

V

V

5

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

6.7 Timing Requirements

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

tDELAY

USB charging turnon delay

Measured from EN asserted LOW to

nFET beginning to Turn ON (1)

excluding soft-start time

20

ms

tSS

USB charging rise time (soft-start

delay)

Measure from VBUS_SYS rises above

25% (with 1-MΩ load/ NO CLOAD) until

ACK goes Low (10%)

25

ms

tOFF_DELAY

USB charging turnoff time

Measured from EN asserted High to

VBUS_SYS falling to 10% with RLOAD =

10 Ω and No CLOAD on VBUS_SYS

4

µs

OVERVOLTAGE PROTECTION

tOVP_response

OVP response time

Measured from OVP Condition to FET

Turn OFF (2). VBUS_CON rises at 1V /

100 ns

tOVP_Recov

Recovery time

Measured from OVP Clear to FET Turn

ON (3)

(1)

(2)

(3)

100

20

ns

ms

Shown in Figure 1.

Parameters provided for reference only, and do not constitute part of TI's published device specifications for purposes of TI's product

warranty.

Excludes soft-start time

6.8 Switching Characteristics (nFET)

over operating free-air temperature range (unless otherwise noted)

PARAMETER

RDS(on)

Switch ON-resistance

TEST CONDITIONS

MIN

VBUS_CON = 5 V, IOUT = 1 A,

TA = 25˚C

TYP

MAX

39

50

UNIT

mΩ

6.9 Supply Current Consumption

over operating free-air temperature range (unless otherwise noted)

PARAMETER

IVBUS_SLEEP

IVBUS

VBUS_CON operating current

consumption

TEST CONDITIONS

MIN

TYP

MAX

30

70

µA

Measured at VBUS_CON pin,

VBUS_CON = 5 V, EN 0 V and no load

175

373

µA

175

373

µA

200

µA

Measured at VBUS_CON pin,

VBUS_CON = 5 V, EN =5V

IVBUS_SYS

VBUS_CON operating current

consumption

Measured at VBUS_SYS pin,

VBUS_SYS = 5 V, EN = 0 V and

VBUS_CON = Hi Z

IHOST_LEAK

Host mode leakage current

Measured at VBUS_SYS,

VBUS_CON = Hi Z, EN = 5 V,

VBUS_SYS = 5 V

90

UNIT

6.10 Thermal Shutdown Feature

over operating free-air temperature range (unless otherwise noted)

PARAMETER

TSHDN

6

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Thermal shutdown

Junction temperature

145

°C

Thermal-shutdown hysteresis

Junction temperature

35

°C

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

�TPD1S414

www.ti.com

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

Overtemperature

Condition

VOVP

VBUS_CON

VUVLO

tDELAY

EN

tOFF_DELAY

tSS

VBUS_SYS

Figure 1. Thermal Shutdown Operation

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

7

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

6.11 Typical Characteristics

800

700

1.8

1.6

Normalized RDS(ON)

600

Input Current (uA)

2.0

-30

TAT==t30ƒC

25

TAT==25ƒC

TAT==85ƒC

85

500

400

300

200

1.4

1.2

1.0

0.8

0.6

0.4

100

0.2

0.0

0

0

5

10

15

20

25

30

Input Voltage (V)

35

±40

±20

0

20

40

60

80

Temperature (ƒC)

C001

Figure 2. Input Supply Current vs Supply Voltage

100

C002

Figure 3. Normalized RDS(ON) vs Temperature

1.10

3.0

1.05

Normalized VOVP

Normalized RDS(ON)

2.5

2.0

1.5

1.0

1.00

0.95

0.5

0.0

0.90

0.1

0.6

1.1

1.6

2.1

2.6

Output Current (A)

±40

±20

0

20

40

60

80

Temperature (ƒC)

C003

Figure 4. Normalized RDS(ON) vs Output Current

100

C004

Figure 5. Normalized VOVP

14

2.00

1.80

12

10

1.40

Voltage (V)

Normalized TDELAY

1.60

1.20

1.00

0.80

0.60

8

6

4

0.40

VBUS_SYS

2

0.20

VBUS_CON

0

0.00

±40

±20

0

20

40

60

Temperature (ƒC)

80

100

0

C005

Figure 6. Normalized TDELAY

8

200

400

600

800

1000

Time (ns)

1200

1400

C006

Figure 7. VOVP Response Time

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

�TPD1S414

www.ti.com

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

Typical Characteristics (continued)

6

50

3

2

VBUS_SYS

VBUS_CON

1

I_VBUS_CON

0

Voltage (V) and Current (A)

Amplitude (V)

4

Vsys (V)

TPD1S414YZ

8/20 Surge Waveforms

100 V (into an open), Powered Down

45

5

40

Vcon (V)

Icon (A)

35

30

25

20

15

10

5

0

±1

±5

±15

±10

±5

0

5

10

15

20

25

30

Time (ms)

35

±10

C007

Figure 8. Power Up With 2.2 µF on VBUS_SYS

0

10

20

30

40

50

60

70

80

Time (µs)

Product Folder Links: TPD1S414

C008

Figure 9. Response to a 100-V Surge

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

90

9

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

7 Detailed Description

7.1 Overview

The TPD1S414 provides a single-chip ESD protection, surge protection, and overvoltage protection solution for

portable USB charging and Host interfaces. It offers overvoltage protection at the VBUS_CON pin up to 30 V. The

TPD1S414 also provides a ACK pin that indicates to the system if a fault condition has occurred. The TPD1S414

offers an ESD clamp and a surge clamp for VBUS_CON pin, thus eliminating the need for external TVS clamp

circuits in the application.

The TPD1S414 has an internal oscillator and charge pump that controls the turnon of the internal nFET switch.

The internal oscillator controls the timers that enable the charge pump and resets the open-drain ACK output. If

VBUS_CON is less than VOVP, the internal charge pump is enabled. After a 15-ms internal delay, the charge-pump

starts up, and turns on the internal nFET switch through a soft start. Once the nFET is completely turned ON,

TPD1S414 asserts ACK pin LOW. At any time, if VBUS_CON rises above VOVP, the ACK pin is in High-Z and is

pulled HIGH through external resistors. The nFET switch is turned OFF.

7.2 Functional Block Diagram

VBUS_CON

VBUS_SYS

Precision

Surge

Clamping

Circuit

Internal Bandgap

Reference

/ACK

Control Logic

and Charge

Pump

/EN

GND

Copyright © 2016, Texas Instruments Incorporated

7.3 Feature Description

7.3.1 Overvoltage Protection on VBUS_CON up to 30-V DC

When the VBUS_CON voltage rises above VOVP, the internal nFET switch is turned off, removing power from the

system side. VBUS_CON can tolerate up to 30-V DC. The response to overvoltage is very rapid, with the nFET

switch turning off in less than 100 ns. When the VBUS_CON voltage returns back to below VOVP – VHYS_OVP, the

nFET switch is turned on again after an internal delay of tOVP_RECOV (tDELAY). This time delay ensures that the

VBUS_CON supply has stabilized before turning the switch back on. After tOVP_RECOV, the TPD1S414 turns on the

nFET through a soft start. Once the OVP condition is cleared the nFET is turned completely on.

7.3.2 Low RON nFET Switch Supports Host and Charging Mode

The nFET switch has a total ON-resistance (RON) of 39 mΩ. This equates to a voltage drop of less than 140 mV

when charging at the maximum 3.5-A current level. Such low RON helps provide maximum potential to the

system as provided by an external charger or by the system when in host mode.

7.3.3 ±15-kV IEC 61000-4-2 Level 4 ESD Protection

The VBUS_CON pin can withstand ESD events up to ±15-kV Contact and Air-Gap. An ESD clamp diverts the

current to ground.

10

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

�TPD1S414

www.ti.com

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

Feature Description (continued)

7.3.4 100-V IEC 61000-4-5 µs Surge Protection

The VBUS_CON pin can withstand surge events up to 100-V open-circuit voltage (VPP), and 700 W. A precision

clamp diverts the current to ground and active circuitry switches OFF the nFET earlier than 100 ns before an

overvoltage can get through to VBUS_SYS.

7.3.5 Start-Up and OVP Recovery Delay

The TPD1S414 has a built-in start-up delay. Once the device has been enabled, a time tDELAY elapses before the

charge pump is enabled which turns on the nFET. A manufactured preprogrammed soft start, tSS, is used when

turning on the nFET with the charge pump. Once the device is enabled, these start delays, tDELAY + tSS, work

together to meet the USB inrush current compliance. Similarly, after an OVP event has occurred, the device

waits a time tOVP_RECOV before enabling the charge pump to turn on the nFET. The soft-start, tSS, is still used

when turning on the nFET with the charge pump after an OVP event, making the total time for the nFET switch to

turn on after the OVP event tOVP_RECOV + tSS.

7.3.6 Integrated Input Enable and Status Output Signal

The TPD1S414 integrates an enable signal to control the ON and OFF state of its nFET. The device also

integrates an status output signal through the ACK pin which indicates whether or not a fault is occurring on the

device. See the Table 2 table to understand the functionality of these pins in all of the TPD1S414's states.

7.3.7 Thermal Shutdown

The TPD1S414 family has an overtemperature protection circuit to protect against system faults or improper use.

The basic function of the thermal shutdown (TSD) circuit is to sense when the junction temperature has

exceeded the absolute maximum rating and shuts down the device until the junction temperature has cooled to a

safe level. When in the thermal shutdown condition, the device asserts a fault by setting the ACK pin to High-Z.

7.4 Device Functional Modes

7.4.1 VBUS_CON < VUVLO

When VBUS_CON is less than VUVLO, the device is in its unpowered state. The nFET is OFF and the ACK pin is

High-Z. In this state, TPD1S414 still provides IEC 61000-4-2 ±15-kV Contact/±15-kV air-gap protection and IEC

61000-4-5 100-V open-circuit surge protection.

7.4.2 VUVLO < VBUS_CON < VOVP

When VBUS_CON is greater than VUVLO and less than VOVP, the device is in its powered state. In this state, the

nFET can be controlled ON and OFF through the enable pin. When the EN pin is Low, the nFET is ON and can

be used for both charging and host or OTG mode. While the nFET switch is ON, the ACK pin is held Low. When

the enable pin is high, the nFET switch is held OFF and the ACK pin is High-Z. In both the enable and disabled

states, the TPD1S414 provides IEC 61000-4-2 ±15-kV contact/±15-kV air-gap protection and IEC 61000-4-5 100V open-circuit surge protection.

7.4.3 VBUS_CON > VOVP

When VBUS_CON is greater than VOVP, the device is in the overvoltage protection sate. In this state, the nFET

switch is forced OFF regardless of the state of the enable pin and ACK is set High-Z. VBUS_CON can handle

overvoltage protection up to 30 V.

7.4.4 OVP Operation

When the VBUS_CON voltage rises above VOVP, the internal nFET switch is turned off, removing power from the

system. The response is rapid, with the FET switch turning off in less than 100 ns. The ACK pin is set to High-Z

when an overvoltage condition is detected and the nFET is turned OFF. This pin can be pulled up through

external resistors to indicate an OVP condition. When the VBUS_CON voltage returns below VOVP – VHYS-OVP, the

nFET switch is turned on again after the internal delay of tOVP_Recov. This delay time ensures that the VBUS_CON

supply has stabilized before turning the switch back on. After tOVP_Recov, the TPD1S414 turns on the nFET

through a soft start to ensure that the USB Inrush current compliance is met. When the OVP condition is cleared

and the nFET is completely turned on, the ACK is reset LOW.

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

Product Folder Links: TPD1S414

11

�TPD1S414

SLLSEH9B – OCTOBER 2013 – REVISED JULY 2016

www.ti.com

Device Functional Modes (continued)

7.4.5 Host/OTG Mode

The TPD1S414's UVLO and OVP voltages are referenced to VBUS_CON voltage. In OTG mode, VBUS_SYS is driving

the VBUS_CON. Under this situation, initially VBUS_CON is powered through the body diode of the nFET by VBUS_SYS.

Once the UVLO threshold on VBUS_CON is met, the nFET turns on. If there is a short to ground on VBUS_CON the

OTG supply is expected to limit the current.

Table 2. Device Operation

VOLTAGE CONDITION

12

CURRENT CONDITION

VBUS_CON

VBUS_SYS

EN

CURRENT FLOW

COMMENT

ACK PIN

X

VBUS_CON

High

VBUS_SYS to VBUS_CON

Switch off, current flows through the body diode

High-Z

Low

VBUS_CON

Low

VBUS_SYS to VBUS_CON

Switch off, current flows through the body diode

High-Z

X

X

X

No Flow/ Current

through Body Diode

Thermal shutdown condition

High-Z