CY7C168A

4 K × 4 RAM

4 K × 4 RAM

Features

Functional Description

■

Automatic power-down when deselected

■

Complementary metal oxide semiconductor (CMOS) for

optimum speed/power

■

High speed

❐ tAA = 20 ns

The CY7C168A is a high-performance CMOS static RAM

organized as 4096 by 4-bits. Easy memory expansion is

provided by an active LOW chip enable (CE) and three-state

drivers. The CY7C168A has an automatic power-down feature,

reducing the power consumption by 77% when deselected.

Writing to the device is accomplished when the chip select (CE)

and write enable (WE) inputs are both LOW. Data on the four

data input/output pins (I/O0 through I/O3) is written into the

memory location specified on the address pins (A0 through A11).

■

Low active power

❐ 495 mW

■

Low standby power

❐ 110 mW

■

TTL-compatible inputs and outputs

■

VIH of 2.2 V

Reading the device is accomplished by taking the chip enable

(CE) LOW, while write enable (WE) remains HIGH. Under these

conditions, the contents of the location specified on the address

pins will appear on the four data input/output pins (I/O0 through

I/O3).

■

Capable of withstanding greater than 2001 V electrostatic

discharge

The input/output pins remain in a high-impedance state when

chip enable (CE) is HIGH or write enable (WE) is LOW.

A die coat is used to insure alpha immunity.

Logic Block Diagram

INPUTBUFFER

SENSE AMP

I/O0

ROW DECODER

A0

A1

A2

A3

A4

A5

A6

128 x 128

ARRAY

I/O1

I/O2

I/O3

CE

POWER

DOWN

(7C168A)

COLUMN

DECODER

WE

A7 A8 A9 A10 A11

C168A-1

Cypress Semiconductor Corporation

Document Number: 38-05029 Rev. *C

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised November 30, 2010

[+] Feedback

�CY7C168A

Contents

Pin Configuration ............................................................. 3

Selection Guide ................................................................ 3

Maximum Ratings ............................................................. 4

Operating Range ............................................................... 4

Electrical Characteristics ................................................. 4

Capacitance ...................................................................... 5

AC Test Loads and Waveforms ....................................... 5

Switching Characteristics ................................................ 6

Switching Waveforms ...................................................... 6

Typical DC and AC Characteristics ................................ 8

Document Number: 38-05029 Rev. *C

Ordering Information ........................................................ 9

Ordering Code Definitions ........................................... 9

Package Diagram .............................................................. 9

Acronyms ........................................................................ 10

Document Conventions ................................................. 10

Units of Measure ....................................................... 10

Document History Page ................................................. 11

Sales, Solutions, and Legal Information ...................... 12

Worldwide Sales and Design Support ....................... 12

Products .................................................................... 12

PSoC Solutions ......................................................... 12

Page 2 of 12

[+] Feedback

�CY7C168A

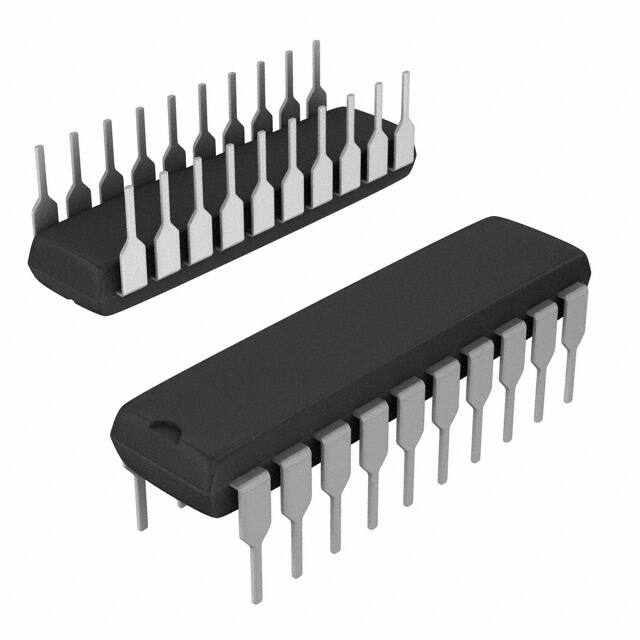

Pin Configuration

Figure 1. DIP Top View

A4

A5

A6

A7

A8

A9

A10

A11

CE

GND

1

20

2

19

3

18

4

17

5

7C168A 16

6

15

7

14

8

13

9

12

10

11

VCC

A3

A2

A1

A0

I/O 0

I/O 1

I/O 2

I/O 3

WE

C168A-2

Selection Guide

7C168A-20

Maximum access time (ns)

Maximum operating current (mA)

Document Number: 38-05029 Rev. *C

20

Commercial

90

Military

100

Page 3 of 12

[+] Feedback

�CY7C168A

Maximum Ratings

Output current into outputs (low) ................................. 20 mA

Exceeding maximum ratings may impair the useful life of the

device. These user guidelines are not tested.

Storage temperature 65 C to +150 C

Ambient temperature with

power applied 55 C to +125 C

Static discharge voltage........................................... > 2001 V

(per MIL-STD-883, method 3015)

Latch-up current ..................................................... > 200 mA

Operating Range

Supply voltage to ground potential

(pin 20 to pin 10) 0.5 V to +7.0 V

DC voltage applied to outputs

in high Z state 0.5 V to +7.0 V

Range

Ambient

Temperature

VCC

Commercial

0 C to +70 C

5 V 10%

DC input voltage 3.0 V to +7.0 V

Electrical Characteristics

Over the Operating Range

7C168A-20

Parameter

Description

Test Conditions

VOH

Output HIGH voltage

VCC = Min, IOH = 4.0 mA

VCC = Min, IOL = 8.0 mA

Min

Max

Unit

2.4

–

V

VOL

Output LOW voltage

–

0.4

V

VIH

Input HIGH voltage

2.2

VCC

V

VIL

Input LOW voltage[1]

0.5

0.8

V

IIX

Input load current

GND < VI < VCC

10

+10

µA

IOZ

Output leakage current

GND < VO < VCC, output disabled

10

+10

µA

IOS

Output short circuit current[2]

VCC = Max, VOUT = GND

–

350

mA

ICC

VCC operating supply current

VCC = Max, IOUT = 0 mA

–

90

mA

ISB1

Automatic CE power-down current

Max VCC, CE > VIH

–

40

mA

ISB2

Automatic CE power-down current

Max VCC, CE > VCC 0.3 V

–

20

mA

Notes

1. VIL min = 3.0 V for pulse durations less than 30 ns.

2. Not more than 1 output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

Document Number: 38-05029 Rev. *C

Page 4 of 12

[+] Feedback

�CY7C168A

Capacitance[3]

Parameter

Description

CIN

Input capacitance

COUT

Output capacitance

Test Conditions

Max

Unit

TA = 25 C, f = 1 MHz, VCC = 5.0 V

10

pF

10

pF

AC Test Loads and Waveforms

R1 481

5V

OUTPUT

R1 481

5V

OUTPUT

R2

255

30 pF

INCLUDING

JIG AND

SCOPE

Equivalent to:

3.0 V

R2

255

5 pF

INCLUDING

JIG AND

SCOPE

(a)

(b)

C168A-3

GND

< 5 ns

ALL INPUT PULSES

90%

10%

90%

10%

< 5 ns

C168A-4

THÉVENIN EQUIVALENT

167

OUTPUT

1.73 V

Note

3. Tested initially and after any design or process changes that may affect these parameters.

Document Number: 38-05029 Rev. *C

Page 5 of 12

[+] Feedback

�CY7C168A

Switching Characteristics

Over the Operating Range[4]

Parameter

7C168A-20

Description

Min.

Max.

Unit

READ CYCLE

tRC

Read cycle time

20

–

ns

tAA

Address to data valid

–

20

ns

tOHA

Output hold from address change

5

–

ns

tACE

CE LOW to data valid

–

20

ns

5

–

ns

tLZCE

[5]

CE LOW to low Z

[5, 6]

tHZCE

CE HIGH to high Z

–

8

ns

tPU

CE LOW to power-up

0

–

ns

tPD

CE HIGH to power-down

–

20

ns

tRCS

Read command set-up

0

–

ns

tRCH

Read command hold

0

–

ns

WRITE CYCLE[7]

tWC

Write cycle time

20

–

ns

tSCE

CE LOW to write end

15

–

ns

tAW

Address set-up to write end

15

–

ns

tHA

Address hold from write end

0

–

ns

tSA

Address set-up to write start

0

–

ns

tPWE

WE pulse width

15

–

ns

tSD

Data set-up to write end

10

–

ns

tHD

Data hold from write end

0

–

ns

WE HIGH to low

Z[5]

7

–

ns

WE LOW to high

Z[5, 6]

5

–

ns

tLZWE

tHZWE

Switching Waveforms

Figure 2. Read Cycle No.1

[8, 9]

tRC

ADDRESS

tOHA

DATA OUT

PREVIOUS DATA VALID

tAA

DATA VALID

C168A-5

Notes

4. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and output loading of the specified

IOL/IOH and 30 pF load capacitance.

5. At any given temperature and voltage condition, tHZ is less than tLZ for all devices. Transition is measured 500 mV from steady state voltage with specified loading in part (b)

of AC Test Loads and Waveforms.

6. tHZCE and tHZWE are tested with CL = 5 pF as in part (a) of Test Loads and Waveforms. Transition is measured 500 mV from steady state voltage.

7. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signal must be LOW to initiate a write and either signal can terminate a

write by going high. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

8. WE is HIGH for read cycle.

9. Device is continuously selected, CE = VIL.

Document Number: 38-05029 Rev. *C

Page 6 of 12

[+] Feedback

�CY7C168A

Switching Waveforms

(continued)

Figure 3. Read Cycle[10, 11]

tRC

CE

tACE

tLZCE

DATA OUT

VCC

SUPPLY

CURRENT

WE

tHZCE

HIGH IMPEDANCE

HIGH

IMPEDANCE

DATA VALID

tPD

tPU

50%

50%

tRCH

tRCS

ICC

ISB

C168A-6

[12]

Figure 4. Write Cycle No.1 (WE Controlled)

tWC

ADDRESS

tSCE

CE

tAW

tSA

tHA

tPWE

WE

tSD

DATA IN

tHD

DATAIN VALID

tHZWE

DATA I/O

tLZWE

HIGH IMPEDANCE

DATA UNDEFINED

C168A-7

Figure 5. Write Cycle No. 2 (CS Controlled)[12, 13]

tWC

ADDRESS

tSA

tSCE

CE

tHA

tAW

tPWE

WE

tSD

DATA IN

DATA IN VALID

tHZWE

DATA I/O

tHD

DATA UNDEFINED

HIGH IMPEDANCE

C168A-8

Notes

10. WE is HIGH for read cycle.

11. Address valid prior to or coincident with CE transition LOW.

12. The internal write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signal must be LOW to initiate a write and either signal can terminate a

write by going high. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

13. If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state.

Document Number: 38-05029 Rev. *C

Page 7 of 12

[+] Feedback

�CY7C168A

1.2

ICC

VIN = 5.0V

TA = 25°C

0.6

0.4

0.2

0.0

4.0

0.8

0.6

0.4

VCC = 5.0V

VIN = 5.0V

0.2

ISB

4.5

5.0

5.5

ISB

0.0

55

6.0

NORMALIZED ACCESS TIME

vs. AMBIENT TEMPERATURE

1.4

1.6

1.3

1.4

NORMALIZED tAA

NORMALIZED t AA

NORMALIZED ACCESS TIME

vs. SUPPLY VOLTAGE

1.2

TA = 25°C

1.0

1.2

1.0

VCC = 5.0V

0.8

0.9

0.8

4.0

4.5

5.0

5.5

0.6

55

6.0

25

2.5

25.0

DELTA tAA (ns)

TYPICAL ACCESS TIME CHANGE

vs. OUTPUT LOADING

30.0

2.0

1.5

1.0

20.0

15.0

10.0

VCC = 4.5V

TA = 25°C

5.0

0.5

1.0

2.0

3.0

4.0

100

80

VCC = 5.0V

TA = 25°C

60

40

20

0

0.0

5.0

SUPPLY VOLTAGE (V)

Document Number: 38-05029 Rev. *C

0.0

0

200

400

600

800 1000

CAPACITANCE (pF)

1.0

2.0

3.0

4.0

OUTPUT VOLTAGE (V)

140

OUTPUT SINK CURRENT

vs. OUTPUT VOLTAGE

120

100

80

60

VCC = 5.0V

TA = 25°C

40

20

0

0.0

125

TYPICAL POWER-ON CURRENT

vs. SUPPLY VOLTAGE

3.0

0.0

0.0

120

1.0

2.0

3.0

4.0

OUTPUT VOLTAGE (V)

AMBIENT TEMPERATURE (°C)

SUPPLY VOLTAGE (V)

NORMALIZED I PO

125

OUTPUT SOURCE CURRENT

vs. OUTPUT VOLTAGE

AMBIENT TEMPERATURE (°C)

SUPPLY VOLTAGE (V)

1.1

25

OUTPUT SINK CURRENT (mA)

0.8

ICC

1.0

NORMALIZED I CC vs.CYCLE TIME

1.1

NORMALIZED I CC

1.0

1.2

NORMALIZED I CC , I SB

NORMALIZED I CC, I SB

1.4

NORMALIZED SUPPLY CURRENT

vs. AMBIENT TEMPERATURE

NORMALIZED SUPPLY CURRENT

vs. SUPPLY VOLTAGE

OUTPUT SOURCE CURRENT (mA)

Typical DC and AC Characteristics

1.0

0.9

0.8

10

20

30

40

CYCLE FREQUENCY (MHz)

Page 8 of 12

[+] Feedback

�CY7C168A

Ordering Information

Speed

(ns)

20

Ordering Code

CY7C168A-20PXC

Package

Name

P5

Package Type

20-Lead Molded DIP

Operating

Range

Commercial

Ordering Code Definitions

CY 7C 168A - 20 PX C

C = Temperature range (Commercial)

PX = 20-lead molded DIP (Pb-free)

20 = Speed grade

168A = 4 K × 4 architecture

Family: 7C = Fast asynchronous SRAM

Company ID: CY = Cypress

Package Diagram

Figure 6. 20-Lead (300-Mil) Molded DIP P5

51-85011 *B

Document Number: 38-05029 Rev. *C

Page 9 of 12

[+] Feedback

�CY7C168A

Acronyms

Document Conventions

Acronym

Description

CMOS

complementary metal oxide semiconductor

CE

chip enable

DIP

dual inline package

I/O

input/output

SRAM

static random access memory

TTL

transistor-transistor logic

WE

write enable

Document Number: 38-05029 Rev. *C

Units of Measure

Symbol

Unit of Measure

ns

nano seconds

V

Volts

µA

micro Amperes

mA

milli Amperes

mV

milli Volts

mW

milli Watts

pF

pico Farad

°C

degree Celcius

W

Watts

%

percent

Page 10 of 12

[+] Feedback

�CY7C168A

Document History Page

Document Title: CY7C168A 4 K × 4 RAM

Document Number: 38-05029

REV.

ECN NO.

Issue Date

Orig. of

Change

Description of Change

**

106815

09/10/01

SZV

Change from Spec number: 38-00095 to 38-05029

*A

3008799

08/19/2010

AJU

Updated tAA to 20 ns under High Speed, 495 mW under Low active power in

Features section

Updated Figure caption to DIP Top View in Pin Configuration section

Updated Selection Guide section with only 7C168A-20 values

Updated Operating Range section with only Commercial temperature range

Updated Electrical Characteristics section with only 7C168A-20 values

Updated Switching Characteristics section with only 7C168A-20 values

Updated Ordering Information section with only CY7C168A-20PXC Ordering

Code

Updated Package Diagram with only the latest revision of “20-Lead (300-Mil)

Molded DIP P5” (Figure 6 in page 8)

Minor edits and updated in new template

*B

3090588

11/19/2010

AJU

Post to external web.

*C

3097955

11/30/2010

PRAS

No technical updates.

Sunset review.

Document Number: 38-05029 Rev. *C

Page 11 of 12

[+] Feedback

�CY7C168A

Sales, Solutions, and Legal Information

Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer’s representatives, and distributors. To find the office

closest to you, visit us at Cypress Locations.

Products

Automotive

Clocks & Buffers

Interface

Lighting & Power Control

PSoC Solutions

cypress.com/go/automotive

cypress.com/go/clocks

psoc.cypress.com/solutions

cypress.com/go/interface

PSoC 1 | PSoC 3 | PSoC 5

cypress.com/go/powerpsoc

cypress.com/go/plc

Memory

Optical & Image Sensing

cypress.com/go/memory

cypress.com/go/image

PSoC

cypress.com/go/psoc

Touch Sensing

cypress.com/go/touch

USB Controllers

Wireless/RF

cypress.com/go/USB

cypress.com/go/wireless

© Cypress Semiconductor Corporation, 2001-2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of

any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for

medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as

critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems

application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign),

United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of,

and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress

integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without

the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES

OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not

assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where

a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress’ product in a life-support systems application implies that the manufacturer

assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 38-05029 Rev. *C

Revised November 30, 2010

Page 12 of 12

All products and company names mentioned in this document may be the trademarks of their respective holders.

[+] Feedback

�