IQE046N08LM5

MOSFET

OptiMOSTM�5�Power-Transistor,�80�V

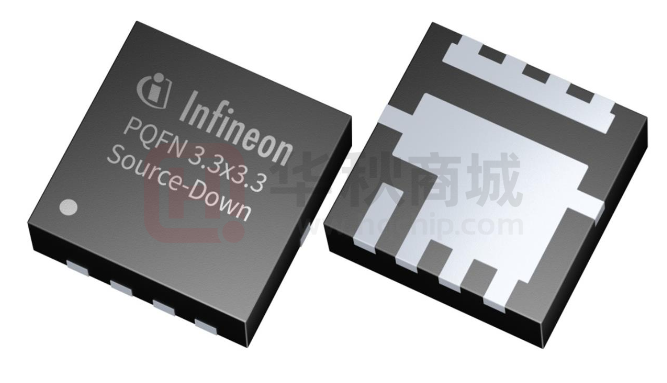

PG-TSON-8

5

Features

•�Optimized�for�high�performance�SMPS,�e.g.�synchronous�rectification

•�N-channel,�logic�level

•�Very�low�on-resistance�RDS(on)

•�Superior�thermal�resistance

•�100%�avalanche�tested

•�Pb-free�lead�plating;�RoHS�compliant

•�Halogen-free�according�to�IEC61249-2-21

4

3

6

2

7

8

1

Product�validation

Fully�qualified�according�to�JEDEC�for�Industrial�Applications

Drain

Pin 5-8

Table�1�����Key�Performance�Parameters

Parameter

Value

Unit

VDS

80

V

RDS(on),max@10V

4.6

mΩ

RDS(on),max@4.5V

5.9

mΩ

ID

99

A

Qoss

39

nC

QG�(0V...4.5V)

19

nC

Gate

Pin 4

Source

Pin 1-3

Type�/�Ordering�Code

Package

Marking

Related�Links

IQE046N08LM5

PG-TSON-8

046N8L5

-

Final Data Sheet

1

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Table�of�Contents

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Electrical characteristics diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Trademarks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Disclaimer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Final Data Sheet

2

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

1�����Maximum�ratings

at�TA=25�°C,�unless�otherwise�specified

Table�2�����Maximum�ratings

Parameter

Symbol

Values

Unit

Note�/�Test�Condition

99

70

62

15.6

A

VGS=10�V,�TC=25�°C

VGS=10�V,�TC=100�°C

VGS=4.5�V,�TC=100�°C

VGS=10�V,�TA=25°C,RthJA=60°C/W2)

-

396

A

TA=25�°C

-

-

170

mJ

ID=20�A,�RGS=25�Ω

VGS

-20

-

20

V

-

Power dissipation

Ptot

-

-

100

2.5

W

TC=25�°C

TA=25�°C,�RthJA=60�°C/W2)

Operating and storage temperature

Tj,�Tstg

-55

-

175

°C

-

Unit

Note�/�Test�Condition

Min.

Typ.

Max.

ID

-

-

ID,pulse

-

Avalanche energy, single pulse

EAS

Gate source voltage

1)

Continuous drain current

Pulsed drain current3)

4)

2�����Thermal�characteristics

Table�3�����Thermal�characteristics

Parameter

Symbol

Thermal resistance, junction - case

Values

Min.

Typ.

Max.

RthJC

-

0.9

1.5

°C/W -

Thermal resistance, junction - ambient,

RthJA

6 cm² cooling area2)

-

-

60

°C/W -

1)

Rating refers to the product only with datasheet specified absolute maximum values, maintaining case temperature

as specified. For other case temperatures please refer to Diagram 2. De-rating will be required based on the actual

environmental conditions.

2)

Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 µm thick) copper area for drain

connection. PCB is vertical in still air.

3)

See Diagram 3 for more detailed information

4)

See Diagram 13 for more detailed information

Final Data Sheet

3

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

3�����Electrical�characteristics

at�Tj=25�°C,�unless�otherwise�specified

Table�4�����Static�characteristics

Parameter

Symbol

Drain-source breakdown voltage

Values

Unit

Note�/�Test�Condition

-

V

VGS=0�V,�ID=1�mA

1.7

2.3

V

VDS=VGS,�ID=47�µA

-

0.1

10

1

100

µA

VDS=80�V,�VGS=0�V,�Tj=25�°C

VDS=80�V,�VGS=0�V,�Tj=125�°C

IGSS

-

10

100

nA

VGS=20�V,�VDS=0�V

Drain-source on-state resistance

RDS(on)

-

4.0

5.2

4.6

5.9

mΩ

VGS=10�V,�ID=20�A

VGS=4.5�V,�ID=10�A

Gate resistance

RG

-

0.6

0.9

Ω

-

gfs

-

62

-

S

|VDS|≥2|ID|RDS(on)max,�ID=20�A

Unit

Note�/�Test�Condition

Min.

Typ.

Max.

V(BR)DSS

80

-

Gate threshold voltage

VGS(th)

1.1

Zero gate voltage drain current

IDSS

Gate-source leakage current

1)

Transconductance

Table�5�����Dynamic�characteristics

Parameter

Symbol

Input capacitance1)

Values

Min.

Typ.

Max.

Ciss

-

2500

3250

pF

VGS=0�V,�VDS=40�V,�f=1�MHz

Coss

-

390

507

pF

VGS=0�V,�VDS=40�V,�f=1�MHz

Reverse transfer capacitance

Crss

-

26

47

pF

VGS=0�V,�VDS=40�V,�f=1�MHz

Turn-on delay time

td(on)

-

5.2

-

ns

VDD=40�V,�VGS=10�V,�ID=20�A,

RG,ext=1.6�Ω

Rise time

tr

-

2.6

-

ns

VDD=40�V,�VGS=10�V,�ID=20�A,

RG,ext=1.6�Ω

Turn-off delay time

td(off)

-

18

-

ns

VDD=40�V,�VGS=10�V,�ID=20�A,

RG,ext=1.6�Ω

Fall time

tf

-

4.4

-

ns

VDD=40�V,�VGS=10�V,�ID=20�A,

RG,ext=1.6�Ω

Unit

Note�/�Test�Condition

Output capacitance1)

1)

Table�6�����Gate�charge�characteristics2)�

Parameter

Symbol

Gate to source charge

Gate charge at threshold

Values

Min.

Typ.

Max.

Qgs

-

7

-

nC

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Qg(th)

-

4.3

-

nC

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Gate to drain charge

Qgd

-

6.4

9.6

nC

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Switching charge

Qsw

-

9.1

-

nC

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Gate charge total

Qg

-

19

24

nC

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Gate plateau voltage

Vplateau

-

2.8

-

V

VDD=40�V,�ID=20�A,�VGS=0�to�4.5�V

Gate charge total

Qg

-

38

-

nC

VDD=40�V,�ID=20�A,�VGS=0�to�10�V

Qoss

-

39

51

nC

VDS=40�V,�VGS=0�V

1)

1)

1)

Output charge

1)

2)

Defined by design. Not subject to production test.

See ″Gate charge waveforms″ for parameter definition

Final Data Sheet

4

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Table�7�����Reverse�diode

Parameter

Symbol

Diode continuous forward current

Diode pulse current

Diode forward voltage

1)

Reverse recovery time

1)

Reverse recovery charge

1)

Reverse recovery time

1)

Reverse recovery charge

1)

Values

Unit

Note�/�Test�Condition

83

A

TC=25�°C

-

396

A

TC=25�°C

-

0.83

1.0

V

VGS=0�V,�IF=20�A,�Tj=25�°C

trr

-

32

64

ns

VR=40�V,�IF=20�A,�diF/dt=100�A/µs

Qrr

-

26

52

nC

VR=40�V,�IF=20�A,�diF/dt=100�A/µs

trr

-

18

36

ns

VR=40�V,�IF=20�A,�diF/dt=1000�A/µs

Qrr

-

129

258

nC

VR=40�V,�IF=20�A,�diF/dt=1000�A/µs

Min.

Typ.

Max.

IS

-

-

IS,pulse

-

VSD

Defined by design. Not subject to production test.

Final Data Sheet

5

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

4�����Electrical�characteristics�diagrams

Diagram�2:�Drain�current

120

120

100

100

80

80

ID�[A]

Ptot�[W]

Diagram�1:�Power�dissipation

60

60

40

40

20

20

0

0

25

50

75

100

125

150

175

0

200

0

25

50

75

TC�[°C]

100

125

150

175

200

TC�[°C]

Ptot=f(TC)

ID=f(TC);�VGS≥10�V

Diagram�3:�Safe�operating�area

Diagram�4:�Max.�transient�thermal�impedance

3

102

10

1 µs

10 µs

102

101

single pulse

0.01

0.02

0.05

0.1

0.2

0.5

100 µs

ZthJC�[K/W]

ID�[A]

101

1 ms

DC

100

100

10-1

10 ms

10-1

10-2

10-2

10-1

100

101

102

10-3

10-6

10-5

10-4

VDS�[V]

10-2

10-1

100

tp�[s]

ID=f(VDS);�TC=25�°C;�D=0;�parameter:�tp

Final Data Sheet

10-3

ZthJC=f(tp);�parameter:�D=tp/T

6

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Diagram�5:�Typ.�output�characteristics

Diagram�6:�Typ.�drain-source�on�resistance

400

12

10 V

2.8 V

5V

350

10

3V

4V

3.5 V

300

8

4.5 V

RDS(on)�[mΩ]

ID�[A]

250

200

150

4V

100

3.5 V

50

3V

4.5 V

6

5V

4

10 V

2

0

2.8 V

0

1

2

3

4

0

5

0

25

50

75

VDS�[V]

100

125

150

175

200

ID�[A]

ID=f(VDS),�Tj=25�°C;�parameter:�VGS

RDS(on)=f(ID),�Tj=25�°C;�parameter:�VGS

Diagram�7:�Typ.�transfer�characteristics

Diagram�8:�Typ.�drain-source�on�resistance

400

12

350

10

300

25 °C

8

175 °C

RDS(on)�[mΩ]

ID�[A]

250

175 °C

200

150

6

4

25 °C

100

2

50

0

0

1

2

3

4

5

6

VGS�[V]

0

2

4

6

8

10

12

14

16

VGS�[V]

ID=f(VGS),�|VDS|>2|ID|RDS(on)max;�parameter:�Tj

Final Data Sheet

0

RDS(on)=f(VGS),�ID=20�A;�parameter:�Tj

7

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Diagram�10:�Typ.�gate�threshold�voltage

2.4

2.4

2.0

2.0

1.6

1.6

VGS(th)�[V]

RDS(on)�(normalized�to�25�°C)

Diagram�9:�Normalized�drain-source�on�resistance

1.2

1.2

47 µA

0.8

0.8

0.4

0.4

0.0

-75

-50

-25

0

25

50

75

470 µA

0.0

-75

100 125 150 175 200

-50

-25

0

25

Tj�[°C]

50

75

100 125 150 175 200

Tj�[°C]

RDS(on)=f(Tj),�ID=20�A,�VGS=10�V

VGS(th=f(Tj),�VGS=VDS;�parameter:�ID

Diagram�11:�Typ.�capacitances

Diagram�12:�Forward�characteristics�of�reverse�diode

4

103

10

25 °C

25 °C, max

175 °C

175 °C, max

Ciss

3

102

IF�[A]

C�[pF]

10

Coss

102

101

Crss

1

10

0

10

20

30

40

50

60

70

80

100

0.0

0.4

VDS�[V]

1.2

1.6

2.0

2.4

VSD�[V]

C=f(VDS);�VGS=0�V;�f=1�MHz

Final Data Sheet

0.8

IF=f(VSD);�parameter:�Tj

8

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Diagram�13:�Avalanche�characteristics

Diagram�14:�Typ.�gate�charge

2

10

10

16 V

40 V

64 V

8

101

25 °C

6

VGS�[V]

IAV�[A]

100 °C

150 °C

4

0

10

2

10-1

100

101

102

103

tAV�[µs]

0

0

5

10

15

20

25

30

35

40

Qgate�[nC]

IAS=f(tAV);�RGS=25�Ω;�parameter:�Tj,start

VGS=f(Qgate),�ID=20�A�pulsed,�Tj=25�°C;�parameter:�VDD

Diagram�15:�Drain-source�breakdown�voltage

Diagram Gate charge waveforms

88

86

VBR(DSS)�[V]

84

82

80

78

76

-75

-50

-25

0

25

50

75

100 125 150 175 200

Tj�[°C]

VBR(DSS)=f(Tj);�ID=1�mA

Final Data Sheet

9

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

5�����Package�Outlines

DIMENSION

A

A1

b

c

D

D1

E

e

L

L1

L2

L3

L4

L5

L6

MILLIMETERS

MIN.

MAX.

1.10

0.05

0.20

0.40

0.20

3.30

2.31

2.51

3.30

0.65

0.35

0.55

0.10

0.30

0.40

0.60

1.35

1.55

0.26

0.46

0.84

1.04

0.77

0.97

DOCUMENT NO.

Z8B00198723

REVISION

01

SCALE 10:1

0

2mm

1

EUROPEAN PROJECTION

ISSUE DATE

06.11.2019

Figure�1�����Outline�PG-TSON-8,�dimensions�in�mm

Final Data Sheet

10

Rev.�2.0,��2023-01-12

�OptiMOSTM�5�Power-Transistor,�80�V

IQE046N08LM5

Revision�History

IQE046N08LM5

Revision:�2023-01-12,�Rev.�2.0

Previous Revision

Revision

Date

Subjects (major changes since last revision)

2.0

2023-01-12

Release of final version

Trademarks

All�referenced�product�or�service�names�and�trademarks�are�the�property�of�their�respective�owners.

We�Listen�to�Your�Comments

Any�information�within�this�document�that�you�feel�is�wrong,�unclear�or�missing�at�all?�Your�feedback�will�help�us�to�continuously

improve�the�quality�of�this�document.�Please�send�your�proposal�(including�a�reference�to�this�document)�to:

erratum@infineon.com

Published�by

Infineon�Technologies�AG

81726�München,�Germany

©�2023�Infineon�Technologies�AG

All�Rights�Reserved.

Legal�Disclaimer

The�information�given�in�this�document�shall�in�no�event�be�regarded�as�a�guarantee�of�conditions�or�characteristics�

(“Beschaffenheitsgarantie”)�.

With�respect�to�any�examples,�hints�or�any�typical�values�stated�herein�and/or�any�information�regarding�the�application�of�the

product,�Infineon�Technologies�hereby�disclaims�any�and�all�warranties�and�liabilities�of�any�kind,�including�without�limitation

warranties�of�non-infringement�of�intellectual�property�rights�of�any�third�party.

In�addition,�any�information�given�in�this�document�is�subject�to�customer’s�compliance�with�its�obligations�stated�in�this

document�and�any�applicable�legal�requirements,�norms�and�standards�concerning�customer’s�products�and�any�use�of�the

product�of�Infineon�Technologies�in�customer’s�applications.

The�data�contained�in�this�document�is�exclusively�intended�for�technically�trained�staff.�It�is�the�responsibility�of�customer’s

technical�departments�to�evaluate�the�suitability�of�the�product�for�the�intended�application�and�the�completeness�of�the�product

information�given�in�this�document�with�respect�to�such�application.

Information

For�further�information�on�technology,�delivery�terms�and�conditions�and�prices�please�contact�your�nearest�Infineon

Technologies�Office�(www.infineon.com).

Warnings

Due�to�technical�requirements,�components�may�contain�dangerous�substances.�For�information�on�the�types�in�question,

please�contact�the�nearest�Infineon�Technologies�Office.

The�Infineon�Technologies�component�described�in�this�Data�Sheet�may�be�used�in�life-support�devices�or�systems�and/or

automotive,�aviation�and�aerospace�applications�or�systems�only�with�the�express�written�approval�of�Infineon�Technologies,�if�a

failure�of�such�components�can�reasonably�be�expected�to�cause�the�failure�of�that�life-support,�automotive,�aviation�and

aerospace�device�or�system�or�to�affect�the�safety�or�effectiveness�of�that�device�or�system.�Life�support�devices�or�systems�are

intended�to�be�implanted�in�the�human�body�or�to�support�and/or�maintain�and�sustain�and/or�protect�human�life.�If�they�fail,�it�is

reasonable�to�assume�that�the�health�of�the�user�or�other�persons�may�be�endangered.

Final Data Sheet

11

Rev.�2.0,��2023-01-12

�Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Infineon:

IQE046N08LM5ATMA1

�