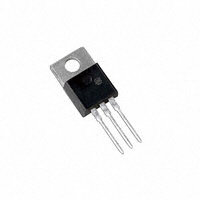

MJE13007

Switch-mode NPN Bipolar

Power Transistor

For Switching Power Supply Applications

The MJE13007 is designed for high−voltage, high−speed power

switching inductive circuits where fall time is critical. It is particularly

suited for 115 and 220 V switch−mode applications such as Switching

Regulators, Inverters, Motor Controls, Solenoid/Relay drivers and

Deflection circuits.

Features

•

•

•

•

www.onsemi.com

POWER TRANSISTOR

8.0 AMPERES

400 VOLTS − 80 WATTS

SOA and Switching Applications Information

Standard TO−220

These Devices are Pb−Free and are RoHS Compliant*

Complementary to the MJE5850 through MJE5852 Series

COLLECTOR

2,4

1

BASE

MAXIMUM RATINGS

Rating

Symbol

Value

Unit

Collector−Emitter Sustaining Voltage

VCEO

400

Vdc

Collector−Base Breakdown Voltage

VCES

700

Vdc

Emitter−Base Voltage

VEBO

9.0

Vdc

IC

8.0

Adc

ICM

16

Adc

IB

4.0

Adc

IBM

8.0

Adc

IE

12

Adc

IEM

24

Adc

PD

80

0.64

W

W/_C

−65 to 150

_C

Collector Current

− Continuous

Collector Current

− Peak (Note 1)

Base Current

− Continuous

Base Current

− Peak (Note 1)

Emitter Current

− Continuous

Emitter Current

− Peak (Note 1)

Total Device Dissipation @ TC = 25_C

Derate above 25°C

Operating and Storage Temperature

TJ, Tstg

3

EMITTER

4

TO−220AB

CASE 221A−09

STYLE 1

1

2

3

MARKING DIAGRAM

Stresses exceeding those listed in the Maximum Ratings table may damage the

device. If any of these limits are exceeded, device functionality should not be

assumed, damage may occur and reliability may be affected.

1. Pulse Test: Pulse Width = 5 ms, Duty Cycle ≤ 10%.

MJE13007G

AY WW

THERMAL CHARACTERISTICS

Symbol

Max

Unit

Thermal Resistance, Junction−to−Case

Characteristics

RqJC

1.56

_C/W

Thermal Resistance, Junction−to−Ambient

RqJA

62.5

_C/W

Maximum Lead Temperature for Soldering

Purposes 1/8″ from Case for 5 Seconds

TL

260

_C

A

Y

WW

G

*Measurement made with thermocouple contacting the bottom insulated mounting

surface of the package (in a location beneath the die), the device mounted on a

heatsink with thermal grease applied at a mounting torque of 6 to 8lbs.

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

© Semiconductor Components Industries, LLC, 2015

January, 2015 − Rev. 9

1

= Assembly Location

= Year

= Work Week

= Pb−Free Package

ORDERING INFORMATION

Device

MJE13007G

Package

Shipping

TO−220

(Pb−Free)

50 Units / Rail

Publication Order Number:

MJE13007/D

�MJE13007

ELECTRICAL CHARACTERISTICS (TC = 25°C unless otherwise noted)

Characteristic

Symbol

Min

Typ

Max

Unit

VCEO(sus)

400

−

−

Vdc

−

−

−

−

0.1

1.0

−

−

100

OFF CHARACTERISTICS (Note 2)

Collector−Emitter Sustaining Voltage

(IC = 10 mA, IB = 0)

Collector Cutoff Current

(VCES = 700 Vdc)

(VCES = 700 Vdc, TC = 125°C)

ICES

Emitter Cutoff Current

(VEB = 9.0 Vdc, IC = 0)

IEBO

mAdc

mAdc

SECOND BREAKDOWN

Second Breakdown Collector Current with Base Forward Biased

Clamped Inductive SOA with Base Reverse Biased

IS/b

See Figure 6

−

See Figure 7

ON CHARACTERISTICS (Note 2)

DC Current Gain

(IC = 2.0 Adc, VCE = 5.0 Vdc)

(IC = 5.0 Adc, VCE = 5.0 Vdc)

hFE

−

8.0

5.0

−

−

40

30

−

−

−

−

−

−

−

−

1.0

2.0

3.0

3.0

−

−

−

−

−

−

1.2

1.6

1.5

fT

4.0

14

−

MHz

Cob

−

80

−

pF

td

−

0.025

0.1

ms

tr

−

0.5

1.5

ts

−

1.8

3.0

tf

−

0.23

0.7

Collector−Emitter Saturation Voltage

(IC = 2.0 Adc, IB = 0.4 Adc)

(IC = 5.0 Adc, IB = 1.0 Adc)

(IC = 8.0 Adc, IB = 2.0 Adc)

(IC = 5.0 Adc, IB = 1.0 Adc, TC = 100°C)

VCE(sat)

Base−Emitter Saturation Voltage

(IC = 2.0 Adc, IB = 0.4 Adc)

(IC = 5.0 Adc, IB = 1.0 Adc)

(IC = 5.0 Adc, IB = 1.0 Adc, TC = 100°C)

VBE(sat)

Vdc

Vdc

DYNAMIC CHARACTERISTICS

Current−Gain − Bandwidth Product

(IC = 500 mAdc, VCE = 10 Vdc, f = 1.0 MHz)

Output Capacitance

(VCB = 10 Vdc, IE = 0, f = 0.1 MHz)

SWITCHING CHARACTERISTICS

Resistive Load (Table 1)

Delay Time

Rise Time

Storage Time

(VCC = 125 Vdc, IC = 5.0 A,

IB1 = IB2 = 1.0 A, tp = 25 ms,

Duty Cycle ≤ 1.0%)

Fall Time

Inductive Load, Clamped (Table 1)

Voltage Storage Time

VCC = 15 Vdc, IC = 5.0 A

Vclamp = 300 Vdc

TC = 25°C

TC = 100°C

tsv

−

−

1.2

1.6

2.0

3.0

ms

Crossover Time

IB(on) = 1.0 A, IB(off) = 2.5 A

LC = 200 mH

TC = 25°C

TC = 100°C

tc

−

−

0.15

0.21

0.30

0.50

ms

TC = 25°C

TC = 100°C

tfi

−

−

0.04

0.10

0.12

0.20

ms

Fall Time

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Pulse Test: Pulse Width ≤ 300 ms, Duty Cycle ≤ 2.0%.

www.onsemi.com

2

�MJE13007

VCE(sat), COLLECTOR-EMITTER SATURATION

VOLTAGE (VOLTS)

TYPICAL CHARACTERISTICS

VBE(sat), BASE-EMITTER SATURATION

VOLTAGE (VOLTS)

1.4

IC/IB = 5

1.2

1

0.8

TC = - 40°C

25°C

0.6

5

IC/IB = 5

2

1

0.5

0.2

TC = - 40°C

0.1

25°C

0.05

100°C

0.4

0.01 0.02

10

0.05

0.1

0.2

0.5

1

2

5

0.02

0.01

0.01 0.02

10

100°C

0.05

0.1

0.2

0.5

1

2

5

10

IC, COLLECTOR CURRENT (AMPS)

IC, COLLECTOR CURRENT (AMPS)

Figure 1. Base−Emitter Saturation Voltage

Figure 2. Collector−Emitter Saturation Voltage

VCE, COLLECTOR-EMITTER VOLTAGE (VOLTS)

3

TJ = 25°C

2.5

2

1.5

IC = 8 A

IC = 5 A

1

IC = 3 A

IC = 1 A

0.5

0

0.01 0.02

0.05

0.1

0.2

0.5

1

2

3

5

10

IB, BASE CURRENT (AMPS)

Figure 3. Collector Saturation Region

100

10000

C, CAPACITANCE (pF)

hFE , DC CURRENT GAIN

25°C

10

40°C

VCE = 5 V

1

0.01

TJ = 25°C

Cib

TJ = 100°C

0.1

1

10

1000

Cob

100

10

0.1

1

10

100

IC, COLLECTOR CURRENT (AMPS)

VR, REVERSE VOLTAGE (VOLTS)

Figure 4. DC Current Gain

Figure 5. Capacitance

www.onsemi.com

3

1000

�MJE13007

10

Extended SOA @ 1 ms, 10 ms

20

10

5

IC, COLLECTOR CURRENT (AMPS)

IC, COLLECTOR CURRENT (AMPS)

100

50

1 ms

10 ms

TC = 25°C

2

1

0.5

DC

1 ms

5 ms

0.2

0.1

0.05

BONDING WIRE LIMIT

THERMAL LIMIT

SECOND BREAKDOWN LIMIT

CURVES APPLY BELOW

RATED VCEO

0.02

0.01

10

8

TC ≤ 100°C

GAIN ≥ 4

LC = 500 mH

6

4

VBE(off)

-5 V

2

0

50 70 100 200 300 500 1000

20 30

VCE, COLLECTOR-EMITTER VOLTAGE (VOLTS)

Figure 7. Maximum Reverse Bias Switching

Safe Operating Area

Figure 6. Maximum Forward Bias

Safe Operating Area

POWER DERATING FACTOR

1

There are two limitations on the power handling ability of

a transistor: average junction temperature and second

breakdown. Safe operating area curves indicate IC − VCE

limits of the transistor that must be observed for reliable

operation; i.e., the transistor must not be subjected to greater

dissipation than the curves indicate.

The data of Figure 6 is based on TC = 25°C; TJ(pk) is

variable depending on power level. Second breakdown pulse

limits are valid for duty cycles to 10% but must be derated

when TC ≥ 25°C. Second breakdown limitations do not

derate the same as thermal limitations. Allowable current at

the voltages shown on Figure 6 may be found at any case

temperature by using the appropriate curve on Figure 8.

At high case temperatures, thermal limitations will reduce

the power that can be handled to values less than the

limitations imposed by second breakdown.

Use of reverse biased safe operating area data (Figure 7)

is discussed in the applications information section.

SECOND BREAKDOWN

DERATING

0.8

0.6

THERMAL

DERATING

0.4

0.2

0

20

40

60

80

100

120

140

160

TC, CASE TEMPERATURE (°C)

Figure 8. Forward Bias Power Derating

r(t), TRANSIENT THERMAL RESISTANCE (NORMALIZED)

0V

-2 V

100 200

300

400

500

600

700

800

VCEV, COLLECTOR-EMITTER CLAMP VOLTAGE (VOLTS)

0

1

0.7

0.5

D = 0.5

D = 0.2

0.2

D = 0.1

0.1

0.07

0.05

P(pk)

D = 0.05

t1

D = 0.02

t2

0.02

DUTY CYCLE, D = t1/t2

D = 0.01

0.01

0.01

RqJC(t) = r(t) RqJC

RqJC = 1.56°C/W MAX

D CURVES APPLY FOR POWER

PULSE TRAIN SHOWN

READ TIME AT t1

TJ(pk) - TC = P(pk) RqJC(t)

SINGLE PULSE

0.02

0.05

0.1

0.2

0.5

1

2

5

10

20

t, TIME (msec)

Figure 9. Typical Thermal Response for MJE13007

www.onsemi.com

4

50

100

200

500

10�k

�MJE13007

SPECIFICATION INFORMATION FOR SWITCHMODE APPLICATIONS

INTRODUCTION

at 25°C and 100°C. Increasing the reverse bias will give

some improvement in device blocking capability.

The sustaining or active region voltage requirements in

switching applications occur during turn−on and turn−off. If

the load contains a significant capacitive component, high

current and voltage can exist simultaneously during turn−on

and the pulsed forward bias SOA curves (Figure 6) are the

proper design limits.

For inductive loads, high voltage and current must be

sustained simultaneously during turn−off, in most cases,

with the base to emitter junction reverse biased. Under these

conditions the collector voltage must be held to a safe level

at or below a specific value of collector current. This can be

accomplished by several means such as active clamping, RC

snubbing, load line shaping, etc. The safe level for these

devices is specified as a Reverse Bias Safe Operating Area

(Figure 7) which represents voltage−current conditions that

can be sustained during reverse biased turn−off. This rating

is verified under clamped conditions so that the device is

never subjected to an avalanche mode.

The primary considerations when selecting a power

transistor for SWITCHMODE applications are voltage and

current ratings, switching speed, and energy handling

capability. In this section, these specifications will be

discussed and related to the circuit examples illustrated in

Table 2. (Note 1)

VOLTAGE REQUIREMENTS

Both blocking voltage and sustaining voltage are

important in SWITCHMODE applications.

Circuits B and C in Table 2 illustrate applications that

require high blocking voltage capability. In both circuits the

switching transistor is subjected to voltages substantially

higher than VCC after the device is completely off (see load

line diagrams at IC = Ileakage ≈ 0 in Table 2). The blocking

capability at this point depends on the base to emitter

conditions and the device junction temperature. Since the

highest device capability occurs when the base to emitter

junction is reverse biased (VCEV), this is the recommended

and specified use condition. Maximum ICEV at rated VCEV

is specified at a relatively low reverse bias (1.5 Volts) both

NOTE: 1. For detailed information on specific switching applications,

see ON Semiconductor Application Note AN719, AN873,

AN875, AN951.

www.onsemi.com

5

�MJE13007

Table 1. Test Conditions For Dynamic Performance

RESISTIVE

SWITCHING

REVERSE BIAS SAFE OPERATING AREA AND INDUCTIVE SWITCHING

TEST CIRCUITS

+15�

V

VCC

1 mF

150�W

3�W

MTP8P10

MTP8P10

100�W

3�W

100 mF

MUR8100E

MPF930

MUR105

MPF930

+10�V

RC

RB1

IC

MJE210

A

RB2

50�W

COMMON

IB

TUT

RB

SCOPE

5.1 k

D

1

VCE

TUT

51

MTP12N10

-�4 V

Voff

1 mF

V(BR)CEO(sus)

CIRCUIT

VALUES

TEST WAVEFORMS

Vclamp = 300 Vdc

IB

150�W

3�W

500 mF

+125

V

L

L = 10 mH

RB2 = 8

VCC = 20 Volts

IC(pk) = 100 mA

Inductive

Switching

tf CLAMPED

tf UNCLAMPED ≈ t2

IC

ICM

RBSOA

L = 200 mH

RB2 = 0

VCC = 15 Volts

RB1 selected for

desired IB1

VCC = 125 V

RC = 25

D1 = 1N5820 OR

W

EQUIV.

L = 500 mH

RB2 = 0

VCC = 15 Volts

RB1 selected for

desired IB1

TYPICAL

WAVEFORMS

t1 ADJUSTED TO

OBTAIN IC

Lcoil (ICM)

t1 ≈

VCC

VCE PEAK

t

t1

tf

t2 ≈

VCE

VCEM

TIME

0

VCE

IB1

Vclamp

t

t2

Lcoil (ICM)

Vclamp

TEST EQUIPMENT

SCOPE — TEKTRONIX

475 OR EQUIVALENT

www.onsemi.com

6

25 ms

+11 V

IB

IB2

9V

tr, tf < 10 ns

DUTY CYCLE = 1.0%

RB AND RC ADJUSTED

FOR DESIRED IB AND IC

�MJE13007

VOLTAGE REQUIREMENTS (continued)

SWITCHING TIME NOTES

In resistive switching circuits, rise, fall, and storage times

have been defined and apply to both current and voltage

waveforms since they are in phase. However, for inductive

loads which are common to SWITCHMODE power

supplies and any coil driver, current and voltage waveforms

are not in phase. Therefore, separate measurements must be

made on each waveform to determine the total switching

time. For this reason, the following new terms have been

defined.

tsv = Voltage Storage Time, 90% IB1 to 10% Vclamp

trv = Voltage Rise Time, 10−90% Vclamp

tfi = Current Fall Time, 90−10% IC

tti = Current Tail, 10−2% IC

tc = Crossover Time, 10% Vclamp to 10% IC

An enlarged portion of the turn−off waveforms is shown

in Figure 12 to aid in the visual identity of these terms. For

the designer, there is minimal switching loss during storage

time and the predominant switching power losses occur

during the crossover interval and can be obtained using the

standard equation from AN222A:

PSWT = 1/2 VCCIC(tc) f

Typical inductive switching times are shown in Figure 13.

In general, trv + tfi ≅ tc. However, at lower test currents this

relationship may not be valid.

As is common with most switching transistors, resistive

switching is specified at 25°C and has become a benchmark

for designers. However, for designers of high frequency

converter circuits, the user oriented specifications which

make this a “SWITCHMODE” transistor are the inductive

switching speeds (tc and tsv) which are guaranteed at 100°C.

In the four application examples (Table 2) load lines are

shown in relation to the pulsed forward and reverse biased

SOA curves.

In circuits A and D, inductive reactance is clamped by the

diodes shown. In circuits B and C the voltage is clamped by

the output rectifiers, however, the voltage induced in the

primary leakage inductance is not clamped by these diodes

and could be large enough to destroy the device. A snubber

network or an additional clamp may be required to keep the

turn−off load line within the Reverse Bias SOA curve.

Load lines that fall within the pulsed forward biased SOA

curve during turn−on and within the reverse bias SOA curve

during turn−off are considered safe, with the following

assumptions:

1. The device thermal limitations are not exceeded.

2. The turn−on time does not exceed 10 ms

(see standard pulsed forward SOA curves in Figure 6).

3. The base drive conditions are within the specified

limits shown on the Reverse Bias SOA curve (Figure 7).

CURRENT REQUIREMENTS

An efficient switching transistor must operate at the

required current level with good fall time, high energy

handling capability and low saturation voltage. On this data

sheet, these parameters have been specified at 5.0 amperes

which represents typical design conditions for these devices.

The current drive requirements are usually dictated by the

VCE(sat) specification because the maximum saturation

voltage is specified at a forced gain condition which must be

duplicated or exceeded in the application to control the

saturation voltage.

SWITCHING REQUIREMENTS

In many switching applications, a major portion of the

transistor power dissipation occurs during the fall time (tfi).

For this reason considerable effort is usually devoted to

reducing the fall time. The recommended way to accomplish

this is to reverse bias the base−emitter junction during

turn−off. The reverse biased switching characteristics for

inductive loads are shown in Figures 12 and 13 and resistive

loads in Figures 10 and 11. Usually the inductive load

components will be the dominant factor in SWITCHMODE

applications and the inductive switching data will more

closely represent the device performance in actual

application. The inductive switching characteristics are

derived from the same circuit used to specify the reverse

biased SOA curves, (see Table 1) providing correlation

between test procedures and actual use conditions.

www.onsemi.com

7

�MJE13007

SWITCHING PERFORMANCE

10000

7000

5000

VCC = 125 V

IC/IB = 5

IB(on) = IB(off)

TJ = 25°C

PW = 25 ms

tr

VCC = 125 V

IC/IB = 5

IB(on) = IB(off)

TJ = 25°C

PW = 25 ms

ts

2000

t, TIME (ns)

1000

1000

700

500

100

tf

200

td

10

100

1

2

3

4

5

6

IC, COLLECTOR CURRENT (AMP)

7

8 9 10

1

2

3

4

5

6

IC, COLLECTOR CURRENT (AMP)

Figure 10. Turn−On Time (Resistive Load)

10000

IC

90% Vclamp

tsv

90% IC

tfi

trv

Vclamp

Vclamp

10%

Vclamp

90% IB1

10%

IC

IC/IB = 5

IB(off) = IC/2

Vclamp = 300 V

LC = 200 mH

VCC = 15 V

TJ = 25°C

5000

2000

tti

tc

IB

7 8 9 10

Figure 11. Turn−Off Time (Resistive Load)

t, TIME (ns)

t, TIME (ns)

10000

2%

IC

1000

500

tsv

tc

200

100

tfi

50

20

10

0.1

TIME

0.2

0.3

0.5 0.7

1

2

3

5

7

IC, COLLECTOR CURRENT (AMP)

Figure 12. Inductive Switching

Measurements

Figure 13. Typical Inductive Switching Times

www.onsemi.com

8

10

�MJE13007

Table 2. Applications Examples of Switching Circuits

CIRCUIT

LOAD LINE DIAGRAMS

SERIES SWITCHING

REGULATOR

TURN-ON (FORWARD BIAS) SOA

ton ≤ 10 ms

VO

VCC

COLLECTOR CURRENT

16 A

A

TIME DIAGRAMS

IC

DUTY CYCLE ≤ 10%

TC = 100°C

PD = 3200 W 2

300 V

ton

TURN-OFF (REVERSE BIAS) SOA

1.5 V ≤ VBE(off) ≤ 9 V

8A

toff

DUTY CYCLE ≤ 10%

TURN-ON

t

TIME

VCE

TURN-OFF

VCC

700 V 1

400 V 1

+

VCC

COLLECTOR VOLTAGE

Notes:

FLYBACK

INVERTER

IC

VO

N

COLLECTOR CURRENT

DUTY CYCLE ≤ 10%

VCC

B

TURN-ON (FORWARD BIAS) SOA

ton ≤ 10 ms

16 A

PD = 3200 W 2

TC = 100°C

300 V

DUTY CYCLE ≤ 10%

TURN-OFF

+ VCC

VCC + N (Vo)

Notes:

VCC + N (Vo)

+ LEAKAGE

SPIKE

VCE

VCC +

N (Vo)

VCC

400 V 1

700 V 1

COLLECTOR VOLTAGE

t

16 A

TURN-ON (FORWARD BIAS) SOA

ton ≤ 10 ms

TC = 100°C

PD = 3200 W 2

IC

VO

VCC

COLLECTOR CURRENT

DUTY CYCLE ≤ 10%

C

t

LEAKAGE SPIKE

See AN569 for Pulse Power Derating Procedure.

1

PUSH−PULL

INVERTER/CONVERTER

toff

ton

TURN-OFF (REVERSE BIAS) SOA

1.5 V ≤ VBE(off) ≤ 9 V

8A

TURN-ON

t

TIME

See AN569 for Pulse Power Derating Procedure.

1

toff

ton

t

TURN-OFF (REVERSE BIAS) SOA

1.5 V ≤ VBE(off) ≤ 9 V

300 V

8A

VCE

DUTY CYCLE ≤ 10%

TURN-ON

2 VCC

VCC

+

2 VCC

TURN-OFF

VCC

400 V 1

700 V 1

t

COLLECTOR VOLTAGE

Notes:

1

SOLENOID DRIVER

See AN569 for Pulse Power Derating Procedure.

TURN-ON (FORWARD BIAS) SOA

ton ≤ 10 ms

16 A

IC

DUTY CYCLE ≤ 10%

D

SOLENOID

COLLECTOR CURRENT

TC = 100°C

VCC

toff

PD = 3200 W 2

300 V

8A

ton

TURN-OFF (REVERSE BIAS) SOA

1.5 V ≤ VBE(off) ≤ 9 V

DUTY CYCLE ≤ 10%

t

VCE

TURN-OFF

VCC

TURN-ON

+

VCC

400 V 1

700 V 1

COLLECTOR VOLTAGE

Notes:

1

See AN569 for Pulse Power Derating Procedure.

www.onsemi.com

9

t

�MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

TO−220

CASE 221A

ISSUE AK

DATE 13 JAN 2022

SCALE 1:1

STYLE 1:

PIN 1.

2.

3.

4.

BASE

COLLECTOR

EMITTER

COLLECTOR

STYLE 2:

PIN 1.

2.

3.

4.

BASE

EMITTER

COLLECTOR

EMITTER

STYLE 3:

PIN 1.

2.

3.

4.

CATHODE

ANODE

GATE

ANODE

STYLE 4:

PIN 1.

2.

3.

4.

MAIN TERMINAL 1

MAIN TERMINAL 2

GATE

MAIN TERMINAL 2

STYLE 5:

PIN 1.

2.

3.

4.

GATE

DRAIN

SOURCE

DRAIN

STYLE 6:

PIN 1.

2.

3.

4.

ANODE

CATHODE

ANODE

CATHODE

STYLE 7:

PIN 1.

2.

3.

4.

CATHODE

ANODE

CATHODE

ANODE

STYLE 8:

PIN 1.

2.

3.

4.

CATHODE

ANODE

EXTERNAL TRIP/DELAY

ANODE

STYLE 9:

PIN 1.

2.

3.

4.

GATE

COLLECTOR

EMITTER

COLLECTOR

STYLE 10:

PIN 1.

2.

3.

4.

GATE

SOURCE

DRAIN

SOURCE

STYLE 11:

PIN 1.

2.

3.

4.

DRAIN

SOURCE

GATE

SOURCE

STYLE 12:

PIN 1.

2.

3.

4.

MAIN TERMINAL 1

MAIN TERMINAL 2

GATE

NOT CONNECTED

DOCUMENT NUMBER:

DESCRIPTION:

98ASB42148B

TO−220

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

Printed versions are uncontrolled except when stamped “CONTROLLED COPY” in red.

PAGE 1 OF 1

onsemi and

are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves

the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular

purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation

special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

© Semiconductor Components Industries, LLC, 2019

www.onsemi.com

�onsemi,

, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba “onsemi” or its affiliates

and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property.

A listing of onsemi’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. onsemi reserves the right to make changes at any time to any

products or information herein, without notice. The information herein is provided “as−is” and onsemi makes no warranty, representation or guarantee regarding the accuracy of the

information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use

of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products

and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information

provided by onsemi. “Typical” parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may

vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. onsemi does not convey any license

under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems

or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should

Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates,

and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that onsemi was negligent regarding the design or manufacture of the part. onsemi is an Equal

Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

◊

TECHNICAL SUPPORT

North American Technical Support:

Voice Mail: 1 800−282−9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

�